- ASIC

- バッテリー マネージメントIC

- クロックとタイミングソリューション

- ESDおよびサージ保護デバイス

- 自動車用イーサネット

- 評価ボード

- 高信頼性(HiRel)

- アイソレーター

- メモリ

- マイクロコントローラー

- パワー

- RF

- セキュリティ ソリューションおよびスマートカードソリューション

- センサー技術

- 小信号トランジスタおよびダイオード

- トランシーバー

- ユニバーサル シリアル バス(USB)

- ワイヤレス接続

- Search Tools

- Technology

- Packages

- Product Information

- ご注文

- 概要

- 組込みフラッシュIPソリューション

- フラッシュプラスRAM MCPソリューション

- F-RAM (強誘電体RAM)

- NORフラッシュ

- nvSRAM (不揮発性 SRAM)

- PSRAM – 擬似スタティックRAM

- 耐放射線・高信頼性メモリ

- SRAM (スタティック RAM)

- ウェーハおよびダイメモリソリューション

- 概要

- 32ビットFM Arm® Cortex® マイクロコントローラー

- 32ビットAURIX™ TriCore™マイクロコントローラー

- 32ビットPSOC™ Arm® Cortex® マイクロコントローラー

- 32ビット TRAVEO™ T2G Arm® Cortex® マイクロコントローラー

- 32ビットXMC™産業用マイクロコントローラー Arm® Cortex®-M

- レガシー マイクロコントローラー

- モーター制御SoC/SiP

- センシングコントローラー

- 概要

- AC-DC電力変換

- 従来型の車載パワートレインIC

- クラスD オーディオアンプIC

- 非接触パワー&センシングIC

- DC/DCコンバーター

- ダイオードとサイリスタ (Si/SiC)

- 窒化ガリウム(GaN)

- ゲートドライバIC

- IGBT – 絶縁ゲート型バイポーラトランジスタ

- インテリジェント パワーモジュール (IPM)

- LEDドライバIC

- モータードライバ

- MOSFET

- パワーモジュール

- 電源IC

- 保護および監視IC

- シリコンカーバイド (SiC)

- スマート パワー スイッチ

- ソリッドステートリレー (SSR)

- ワイヤレス充電IC

- 概要

- アンテナクロススイッチ

- アンテナチューナー

- バイアスと制御

- カプラ

- ドライバアンプ

- 耐放射線マイクロ波とRF

- ローノイズアンプ (LNA)

- 高周波ダイオード

- RFスイッチ

- RFトランジスタ

- ワイヤレス制御向けレシーバー

- 概要

- Calypso®製品

- CIPURSE™ 製品

- 非接触メモリ

- OPTIGA™の組込みセキュリティ ソリューションの詳細

- SECORA™セキュリティソリューション

- セキュリ ティコントローラー

- スマートカードモジュール

- 政府ID向けスマートソリューション

- 概要

- USB 2.0 ペリフェラル コントローラー

- USB 3.2 ペリフェラル コントローラー

- USB ハブ コントローラー

- USB PD高電圧マイクロコントローラー

- USB-C AC-DC および DC-DC 充電ソリューション

- USB-C充電ポートコントローラー

- USB-Cパワーデリバリー コントローラー

- 概要

- AIROC™ オートモーティブワイヤレス

- AIROC™ Bluetooth®およびマルチプロトコル

- AIROC™ コネクトテッドMCU

- AIROC™ Wi-Fi + Bluetooth®コンボ

- 概要

- FM0+ 32ビット Arm® Cortex®-M0+ マイクロコントローラー (MCU)

-

FM3 32ビットArm® Cortex-M3®マイクロコントローラー (MCU) ファミリー

- 概要

- FM3 CY9AFx1xKシリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFx1xL/M/N シリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFx2xK/L シリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFx3xK/L シリーズ 超低リーク Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFx4xL/M/N シリーズ 低消費電力 Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFx5xM/N/Rシリーズ 低消費電力 Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFxAxL/M/N シリーズ 超低リーク Arm® Cortex®-M3 マイクロコントローラー (MCU)

- FM3 CY9BFx1xN/R 高性能シリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9BFx1xS/T 高性能シリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9BFx2xJシリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9BFx2xK/L/Mシリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9BFx2xS/Tシリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM4 32ビットArm® Cortex-M4®マイクロコントローラー (MCU) ファミリー

- 概要

-

32 ビット TriCore™ AURIX™ – TC2x

- 概要

- AURIX™ ファミリー – TC21xL

- AURIX™ファミリー – TC21xSC (ワイヤレス充電)

- AURIX™ ファミリー – TC22xL

- AURIX™ ファミリー – TC23xL

- AURIX™ ファミリー – TC23xLA (ADAS)

- AURIX™ ファミリー – TC23xLX

- AURIX™ ファミリー – TC264DA (ADAS)

- AURIX™ ファミリー – TC26xD

- AURIX™ ファミリー – TC27xT

- AURIX™ ファミリー – TC297TA (ADAS)

- AURIX™ ファミリー – TC29xT

- AURIX™ファミリー – TC29xTT (ADAS)

- AURIX™ ファミリー – TC29xTX

- AURIX™ TC2xx (エミュレーションデバイス)

-

32 ビット TriCore™ AURIX™ – TC3x

- 概要

- AURIX™ ファミリー TC32xLP

- AURIX™ ファミリー – TC33xDA

- AURIX™ ファミリー - TC33xLP

- AURIX™ ファミリー – TC35xTA (ADAS)

- AURIX™ ファミリー – TC36xDP

- AURIX™ ファミリー – TC37xTP

- AURIX™ ファミリー – TC37xTX

- AURIX™ ファミリー – TC38xQP

- AURIX™ ファミリー – TC39xXA (ADAS)

- AURIX™ ファミリー – TC39xXX

- AURIX™ ファミリー – TC3Ex

- AURIX™ TC37xTE (エミュレーションデバイス)

- AURIX™ TC39xXE (エミュレーションデバイス)

- 32 ビット TriCore™ AURIX™ - TC4x

- 概要

- PSOC™ 4 Arm® Cortex® -M0/M0+

- PSOC™ 4 HV Arm® Cortex® -M0+

- PSOC™ 5 LP Arm® Cortex® -M3

- PSOC™ 6 Arm® Cortex®-M4 / M0+

- PSOC™マルチタッチタッチスクリーンコントローラー

- PSOC™ Control C3 Arm® Cortex®-M33

- 自動車用PSOC™ 4 Arm® Cortex®-M0/M0+

- PSOC™ Edge Arm® Cortex® M55/M33

- 概要

- ボディ用32ビットTRAVEO™T2G Arm® Cortex®

- クラスター用の 32 ビット TRAVEO™ T2G Arm® Cortex®

- 概要

- 32ビットXMC1000産業用マイクロコントローラー Arm® Cortex®-M0

- Cortex-M4® Arm® 32ビットXMC4000産業用マイクロコントローラー

- XMC5000産業用マイクロコントローラーArm® Cortex® -M4F

- 32ビットXMC7000産業用マイクロコントローラー Arm® Cortex®-M7®

- 概要

- 整流ブリッジおよびACスイッチ

- CoolSiC™ ショットキーダイオード

- ダイオードベアダイ

- Si ダイオード

- サイリスタ/ダイオード パワーモジュール

- サイリスタソフトスタータモジュール

- サイリスタ / ダイオードディスク

- 概要

- 車載ゲートドライバ IC

- SiC MOSFET用EiceDRIVER™ゲートドライバIC

- ガルバニック絶縁型ゲートドライバ

- GaN HEMT用ゲートドライバIC

- ハイサイドゲートドライバ

- レベルシフト

- ローサイド ドライバ

- トランスドライバIC

- 概要

- BLDCモータードライバ

- BDCモータードライバ

- ステッピングモーターおよびサーボモーター ドライバ

- MCU搭載モータードライバ

- MOSFETを使用したブリッジドライバ

- ゲートドライバIC

- 概要

- 車載用MOSFET

- デュアルMOSFET

- MOSFET(Si&SiC)モジュール

- NチャネルデプレッションモードMOSFET

- NチャネルMOSFET

- PチャネルMOSFET

- CoolSiC™ MOSFET

- 小信号/小電力MOSFET

- 概要

- IGBT モジュール

- MOSFET(Si&SiC)モジュール

- インテリジェント パワーモジュール (IPM)

- ダイオードとサイリスタ (Si/SiC)

- 車載用 IGBT および CoolSiC™ MOSFET モジュール

- 高密度パワーモジュール

- 概要

- 車載用トランシーバー

- OPTIREG™リニア電圧レギュレーター (LDO)

- OPTIREG™ PMIC

- OPTIREG™スイッチャー

- OPTIREG™ システム ベーシス チップ (SBC)

- 概要

- EZ-USB™ CX3 MIPI CSI-2 to USB 5 Gbps カメラ コントローラー

- EZ-USB™ FX10 & FX5N USB 10Gbpsペリフェラルコントローラ

- EZ-USB™ FX20 USB 20 Gbpsペリフェラルコントローラー

- EZ-USB™ FX3 USB 5 Gbps ペリフェラル コントローラー

- EZ-USB™ FX3S USB 5 Gbps ペリフェラル コントローラー (ストレージ インターフェース付き)

- EZ-USB™ FX5 USB 5 Gbpsペリフェラルコントローラー

- EZ-USB™ SD3 USB 5 Gbps ストレージコントローラー

- EZ-USB™ SX3: FIFOインターフェースの USB 5 Gbps ペリフェラル コントローラー

- 概要

- EZ-PD™ CCG3 USB Type-Cポート コントローラーPD

- EZ-PD™ CCG3PA USB-C および PD

- EZ-PD™ CCG3PA-NFET USB-C PD コントローラー

- EZ-PD™ CCG7x シングルポート USB-Cパワーデリバリーおよび DC-DC コントローラー

- EZ-PD™ PAG1: 第 1 世代電源アダプター

- EZ-PD™ PAG2: 第 2 世代電源アダプター

- EZ-PD™ PAG2-PD USB-C PD コントローラー

- 概要

- EZ-PD™ ACG1F 1ポートUSB-Cコントローラー

- EZ-PD™ CCG2 USB Type-Cポート コントローラー

- EZ-PD™ CCG3PA車載用USB-Cおよびパワーデリバリーコントローラー

- EZ-PD™ CCG4 2 ポートUSB-CおよびPD

- EZ-PD™ CCG5デュアルポートおよび CCG5C シングルポート USB-C PDコントローラー

- EZ-PD™ CCG6 1ポート USB-C & PDコントローラー

- EZ-PD™ CCG6_CFP および EZ-PD™ CCG8_CFPデュアルシングルポート USB-C PD

- EZ-PD™ CCG6DFデュアルポートおよびCCG6SFシングルポートUSB-C PDコントローラー

- EZ-PD™ CCG7D車載用デュアルポートUSB-C PD + DC-DCコントローラー

- EZ-PD™ CCG7S車載用シングルポートUSB-C PDソリューション (DC-DCコントローラーおよびFET内蔵)

- EZ-PD™ CCG8デュアル シングル ポートUSB-C PD

- EZ-PD™ CMG1 USB-C EMCAコントローラー

- 拡張パワーレンジ (EPR) 搭載EZ-PD™ CMG2 USB-C EMCA

- 最新情報

- 航空宇宙および防衛

- AIとデータセンター

- 自動車

- 通信

- 民生用電子機器

- ヘルスケアとライフスタイル

- 家電製品

- 産業用アプリケーション

- 再生可能エネルギー

- セキュリティソリューション

- スマートホームとスマートビルディング

- ソリューション

- 概要

- 電源アダプターと充電器

- スマートテレビ向けの完全なシステムソリューション

- モバイルデバイスとスマートフォンソリューション

- 電動工具

- ホームエンターテインメント アプリケーション向けの半導体ソリューション

- スマート会議システム

- マルチコプターとドローン

- 概要

- 電源アダプターと充電器

- 資産管理の追跡

- バッテリーの形成とテスト

- 電動フォークリフト

- バッテリー蓄電 (BESS)

- EV充電

- 高電圧ソリッドステート配電

- 産業用オートメーション

- 産業用モータードライブおよび制御

- 産業用ロボット

- LED 照明システムの設計

- 小型電気自動車ソリューション

- 電動工具

- 送配電

- トラクション

- 無停電電源装置 (UPS)

- Digital health

- ロボティックス

- 風力

- 水電解槽

- 概要

- デバイス認証とブランド保護

- モノのインターネット (IoT) 向けの組み込みセキュリティ

- eSIM アプリケーション

- 公的身分証明書

- モバイルセキュリティ

- 決済ソリューション

- アクセス管理および発券ソリューション

- 概要

- 家庭用ロボット

- 空調システム (HVAC)

- ホームオートメーションとビルオートメーション

- PCアクセサリ

- ホームエンターテインメント アプリケーション向けの半導体ソリューション

- 概要

- 車載用補助システム

- 車載ゲートウェイ

- 車載用パワー分配システム

- ボディコントロールモジュール(BCM)

- コンフォート&コンビニエンス エレクトロニクス

- ゾーンDC-DCコンバーター 48 V~12 V

- ゾーンコントロールユニット

- 概要

- アクティブサスペンションコントロール

- 車載用ブレーキング ソリューション

- 車載用ステアリング ソリューション

- シャーシ ドメイン制御

- 最新情報

- デジタル ドキュメンテーション

- 評価ボード

- ファインダー & セレクション ツール

- プラットフォーム

- サービス

- インフィニオン オンライン パワー シミュレーション プラットフォーム

- ソフトウェア

- ツール

- パートナー

- インフィニオン フォー メーカーズ

- ユニバーシティ アライアンス プログラム

- 概要

- AIROC™ ソフトウェアとツール

- AURIX™のツールとソフトウェア

- 自動車ソフトウェア開発用のDRIVECORE

- iMOTION™ ツールとソフトウェア

- インフィニオンのスマートパワースイッチおよびゲートドライバ ツールスイート

- MOTIX™ ソフトウェア&ツール

- OPTIGA™ ツールとソフトウェア

- PSOC™ ソフトウェアとツール

- TRAVEO™ ソフトウェアとツール

- XENSIV™ツールおよびソフトウェア

- XMC™ ツールとソフトウェア

- 概要

- IPOSIM オンライン パワー シミュレーション プラットフォーム

- CoolGaN™シミュレーションツール(PLECS)

- HiRel フィット レート ツール

- IPOSIM オンライン パワー シミュレーション プラットフォーム

- インフィニオン デザイナー

- インタラクティブな製品シート

- IPOSIM オンライン パワー シミュレーション プラットフォーム

- InfineonSpiceオフラインシミュレーションツール

- OPTIREG™ 車載電源IC シミュレーションツール (PLECS)

- パワーMOSFETシミュレーション モデル

- PowerEsimスイッチモード電源設計ツール

- ソリューションファインダー

- XENSIV™磁気センサー シミュレーション ツール

- 概要

- AURIX™認証

- AURIX™開発ツール

- AURIX™組込みソフトウェア

- AURIX™マイクロコントローラーキット

- 概要

- CAPSENSE™コントローラー コンフィギュレーション ツール EZ-Click

- DC-DC統合POL電圧レギュレーター設定ツール – PowIRCenter

- EZ-USB™ SX3コンフィギュレーション ユーティリティ

- FM+ コンフィギュレーション ツール

- FMx設定ツール

- トランシーバーICコンフィギュレーション ツール

- USB EZ-PD™コンフィギュレーション ユーティリティ

- USB EZ-PD™コンフィギュレーション ユーティリティ

- USB EZ-USB™ HX3C Blaster Plusコンフィギュレーション ユーティリティ

- USB UARTコンフィギュレーション ユーティリティ

- XENSIV™タイヤ空気圧センサーのプログラミング

- 概要

- EZ-PD™ CCGx Dock ソフトウェア開発キット

- FMx Softune IDE

- ModusToolbox™ ソフトウェア

- PSOC™ ソフトウェア

- レーダー開発キット

- 錆

- USBコントローラーSDK

- ワイヤレス接続 Bluetooth メッシュヘルパー アプリケーション

- XMC™ DAVE™ソフトウェア

- 概要

- AIROC™ Bluetooth® Connect Appアーカイブ

- Cypress™ Programmerのアーカイブ

- EZ-PD™ CCGx 電力ソフトウェア開発キットのアーカイブ

- ModusToolbox™ ソフトウェアのアーカイブ

- PSOC™ Creatorのアーカイブ

- PSOC™ Designerのアーカイブ

- PSOC™ Programmerのアーカイブ

- USB EZ-PD™コンフィギュレーション ユーティリティ アーカイブ

- USB EZ-PD™ホストSDKのアーカイブ

- USB EZ-USB™ FX3のアーカイブ

- EZ-USB™ HX3PD コンフィギュレーション ユーティリティ

- WICED™ Smart SDKのアーカイブ

- WICED™ Studioのアーカイブ

- 最新情報

- サポート

- トレーニング

- 開発者コミュニティ

- News

ビジネス&財務プレス

2026/04/23

ビジネス&財務プレス

2026/04/15

ビジネス&財務プレス

2026/04/14

ビジネス&財務プレス

2026/04/07

- 会社概要

- 私たちのストーリー

- イベント

- プレス

- 投資家向け情報

- 採用情報

- 品質

- 最新ニュース

ビジネス&財務プレス

2026/04/23

ビジネス&財務プレス

2026/04/15

ビジネス&財務プレス

2026/04/14

ビジネス&財務プレス

2026/04/07

これは機械翻訳されたコンテンツです。 詳しくは こちらをご覧ください。

AURIX™ - XILINX FPGA リンク

最適化されたAURIX™とXILINX FPGAのリンクで性能を最大化

-

このページでは

概要

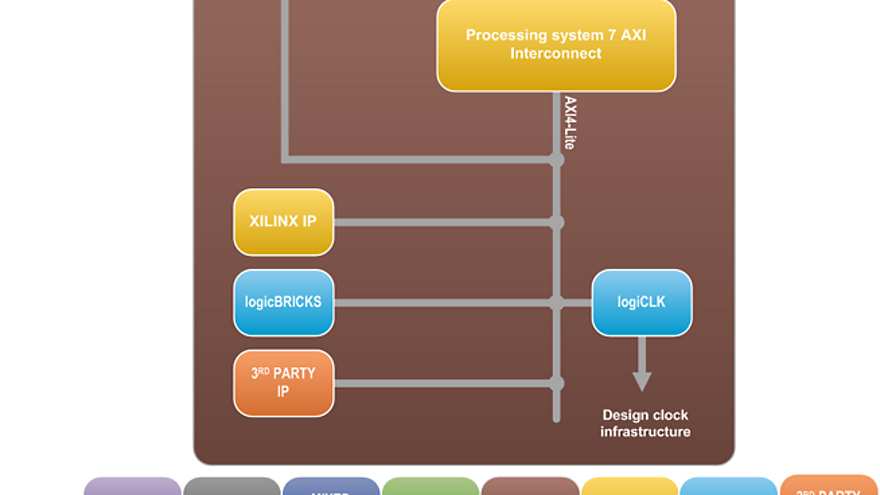

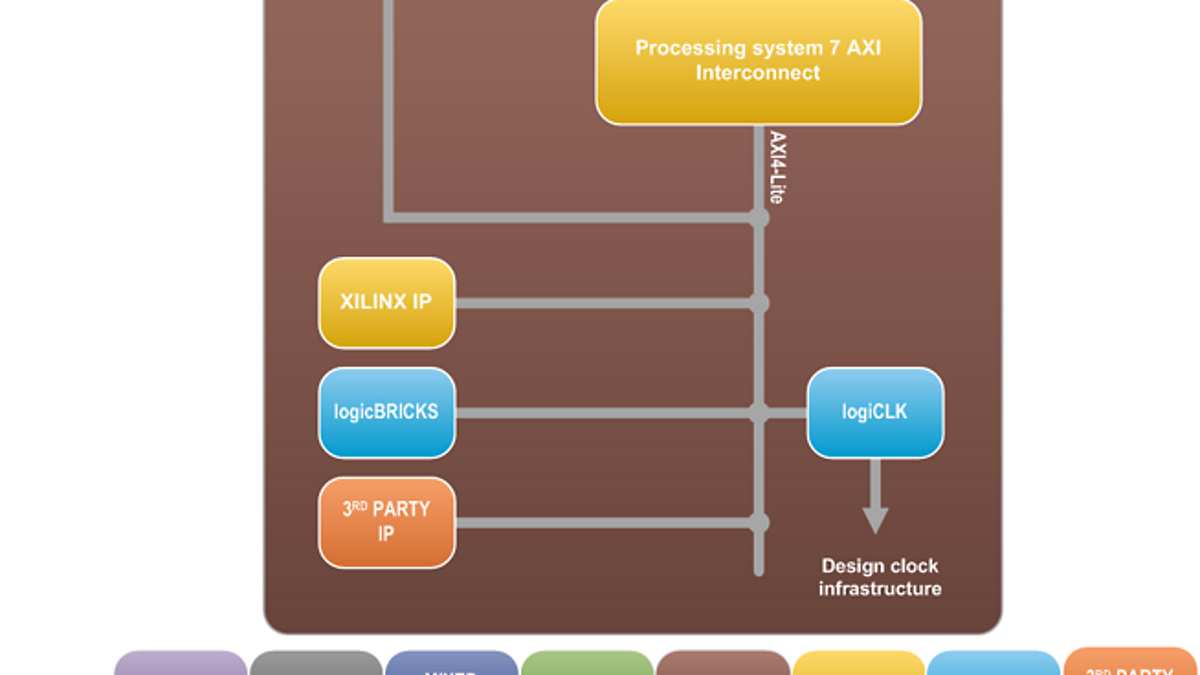

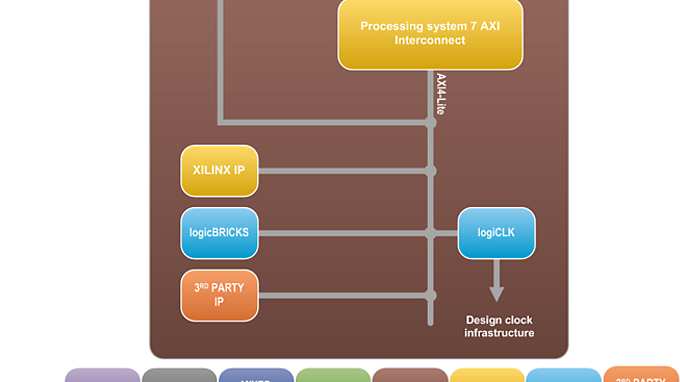

インフィニオンテクノロジーズ、ザイリンクス、 Xylon社は、車載用および産業用アプリケーションでの安全マイクロコントローラの使用の柔軟性を高めるために協力します。Xylonの新しいIPコアは、インフィニオンのAURIXファミリー (TC2xx および TC3xx) のマイクロコントローラとXilinx SoC (System-on-Chip)、MPSoC (MultiProcessor SoC)、およびFPGA (Field Programmable Gate Arrays) デバイス間の高速通信を、Infineon High Speed Serial Link (HSSL) を介して可能にします。このシリアル リンクは、最大 320 Mbaud のボー レートをサポートし、最大 84% の正味ペイロード データ レートをサポートします。

この新しいIPコアにより、システム開発者は、AURIX™が提供する機能安全およびセキュリティを、ザイリンクス製デバイスが提供する幅広い機能の可能性と組み合わせることができます。リンクされたデバイスは、HSSL を介して互いの内部リソースと接続されたリソースにアクセスし、制御できます。

- 現在、ザイリンクス 7 シリーズおよび Zynq-7000 SoC デバイス ファミリをサポート

- Xilinx UltraScale、UltraScale+ FPGA デバイス、Zynq UltraScale+ MPSoC のサポートは近い将来に予定されています。

- HSSLスレーブデバイス

- 最大320 Mbaud/sのボーレート

- スレーブデバイスとしてARM AMBA AXI4-Liteバスプロトコルに準拠

- マスターデバイスとしてARM AMBA AXI4バスプロトコルに準拠

- 3.25 GBのアドレス指定可能なスペースは、以下へのアクセスをカバーします。

- FPGAファブリックレジスタとRAM

- PSセクションレジスタスペースとOCM

- リニア・アドレス指定可能なFLASHデバイス搭載

- オンボードDDRメモリ

キットの説明

logiHSSL-ZU FPGA HSSLスターターキットのデザインは、インフィニオンのAURIX™マイクロコントローラとザイリンクスのAll Programmable FPGAおよびSoCデバイスをインフィニオンの高速シリアルリンク(HSSL)を介して迅速に相互接続するために必要なすべてのものをシステム設計者に提供します。これらのデバイスを組み合わせることで、新しい自動車および工業デザインにおける安全性と性能の要件の高まりを解決します。

キット内容

- インフィニオンのAURIX™マイクロコントローラとザイリンクスのUltraScale+ MPSoCプログラマブルデバイスを組み合わせ

- Xilinx FPGA実装用に最適化されたInfineon High Speed Serial Link(HSSL)を統合

- 評価版 logiHSSL IP コアを含む完全なリファレンス デザインが付属

- デザインはザイリンクス Vivado® Design Suite 用に準備されています

- リンクされたデバイスは、互いのリソースにアクセスして制御できます

- 完全なハードウェアプラットフォームには、次のものが含まれます。

- 1 x Xilinx Zynq UltraScale+ MPSoC ZCU104評価キット

- 1 x Infineon Aurix 評価ボードキット KIT_A2G_TC397_5V_TRB_S

- 1 x Xylon FMCボード(ケーブル接続用)

- 1 x FireWireケーブル

- HSSL IP コア (HSSL #0) は、PS 7 AXI インターコネクトを介してすべての SoC IP コアのレジスタ セットにアクセスできます

- HSSL 制御モジュールは、同じ AXI インフラストラクチャを介して内部 HSCT、HSSL、および BCU レジスタ空間にアクセスできます

- HSSL IP コアは、PL-PS インターフェイスの GP ポートと HP AXI3 ポートを介して PS レジスタ空間とオンボード メモリにアクセスできます

- プログラマブルな logiCLK IP コアにより、クロッキングをオンザフライで変更し、HSSL IP コアを必要なボー レートにセットアップ可能

インフィニオンのテクニカルサポート

- myinfineon.com(ハイパーリンク)の下に会社のメールアドレスで登録してください

- ログイン名の送信先: AURIX@infineon.com

- 登録後、新しいドキュメントに対して自動更新サービスが提供されます

- 完全な登録プロセスが完了するまでに最大24時間かかる場合があります(タイムゾーンが異なるため)。

インフィニオンテクノロジーズ、ザイリンクス、 Xylon社は、車載用および産業用アプリケーションでの安全マイクロコントローラの使用の柔軟性を高めるために協力します。Xylonの新しいIPコアは、インフィニオンのAURIXファミリー (TC2xx および TC3xx) のマイクロコントローラとXilinx SoC (System-on-Chip)、MPSoC (MultiProcessor SoC)、およびFPGA (Field Programmable Gate Arrays) デバイス間の高速通信を、Infineon High Speed Serial Link (HSSL) を介して可能にします。このシリアル リンクは、最大 320 Mbaud のボー レートをサポートし、最大 84% の正味ペイロード データ レートをサポートします。

この新しいIPコアにより、システム開発者は、AURIX™が提供する機能安全およびセキュリティを、ザイリンクス製デバイスが提供する幅広い機能の可能性と組み合わせることができます。リンクされたデバイスは、HSSL を介して互いの内部リソースと接続されたリソースにアクセスし、制御できます。

- 現在、ザイリンクス 7 シリーズおよび Zynq-7000 SoC デバイス ファミリをサポート

- Xilinx UltraScale、UltraScale+ FPGA デバイス、Zynq UltraScale+ MPSoC のサポートは近い将来に予定されています。

- HSSLスレーブデバイス

- 最大320 Mbaud/sのボーレート

- スレーブデバイスとしてARM AMBA AXI4-Liteバスプロトコルに準拠

- マスターデバイスとしてARM AMBA AXI4バスプロトコルに準拠

- 3.25 GBのアドレス指定可能なスペースは、以下へのアクセスをカバーします。

- FPGAファブリックレジスタとRAM

- PSセクションレジスタスペースとOCM

- リニア・アドレス指定可能なFLASHデバイス搭載

- オンボードDDRメモリ

キットの説明

logiHSSL-ZU FPGA HSSLスターターキットのデザインは、インフィニオンのAURIX™マイクロコントローラとザイリンクスのAll Programmable FPGAおよびSoCデバイスをインフィニオンの高速シリアルリンク(HSSL)を介して迅速に相互接続するために必要なすべてのものをシステム設計者に提供します。これらのデバイスを組み合わせることで、新しい自動車および工業デザインにおける安全性と性能の要件の高まりを解決します。

キット内容

- インフィニオンのAURIX™マイクロコントローラとザイリンクスのUltraScale+ MPSoCプログラマブルデバイスを組み合わせ

- Xilinx FPGA実装用に最適化されたInfineon High Speed Serial Link(HSSL)を統合

- 評価版 logiHSSL IP コアを含む完全なリファレンス デザインが付属

- デザインはザイリンクス Vivado® Design Suite 用に準備されています

- リンクされたデバイスは、互いのリソースにアクセスして制御できます

- 完全なハードウェアプラットフォームには、次のものが含まれます。

- 1 x Xilinx Zynq UltraScale+ MPSoC ZCU104評価キット

- 1 x Infineon Aurix 評価ボードキット KIT_A2G_TC397_5V_TRB_S

- 1 x Xylon FMCボード(ケーブル接続用)

- 1 x FireWireケーブル

- HSSL IP コア (HSSL #0) は、PS 7 AXI インターコネクトを介してすべての SoC IP コアのレジスタ セットにアクセスできます

- HSSL 制御モジュールは、同じ AXI インフラストラクチャを介して内部 HSCT、HSSL、および BCU レジスタ空間にアクセスできます

- HSSL IP コアは、PL-PS インターフェイスの GP ポートと HP AXI3 ポートを介して PS レジスタ空間とオンボード メモリにアクセスできます

- プログラマブルな logiCLK IP コアにより、クロッキングをオンザフライで変更し、HSSL IP コアを必要なボー レートにセットアップ可能

インフィニオンのテクニカルサポート

- myinfineon.com(ハイパーリンク)の下に会社のメールアドレスで登録してください

- ログイン名の送信先: AURIX@infineon.com

- 登録後、新しいドキュメントに対して自動更新サービスが提供されます

- 完全な登録プロセスが完了するまでに最大24時間かかる場合があります(タイムゾーンが異なるため)。

イメージギャラリー