- ASIC

- バッテリー マネージメントIC

- クロックとタイミングソリューション

- ESDおよびサージ保護デバイス

- 自動車用イーサネット

- 評価ボード

- 高信頼性(HiRel)

- アイソレーター

- メモリ

- マイクロコントローラー

- パワー

- RF

- セキュリティ ソリューションおよびスマートカードソリューション

- センサー技術

- 小信号トランジスタおよびダイオード

- トランシーバー

- ユニバーサル シリアル バス(USB)

- ワイヤレス接続

- Search Tools

- Technology

- Packages

- Product Information

- ご注文

- 概要

- 組込みフラッシュIPソリューション

- フラッシュプラスRAM MCPソリューション

- F-RAM (強誘電体RAM)

- NORフラッシュ

- nvSRAM (不揮発性 SRAM)

- PSRAM (擬似スタティック RAM)

- 耐放射線・高信頼性メモリ

- SRAM (スタティック RAM)

- ウェーハおよびダイメモリソリューション

- 概要

- 32ビットFM Arm® Cortex® マイクロコントローラー

- 32ビットAURIX™ TriCore™マイクロコントローラー

- 32ビットPSOC™ Arm® Cortex® マイクロコントローラー

- 32ビット TRAVEO™ T2G Arm® Cortex® マイクロコントローラー

- 32ビットXMC™産業用マイクロコントローラー Arm® Cortex®-M

- レガシー マイクロコントローラー

- モーター制御SoC/SiP

- センシングコントローラー

- 概要

- AC-DC電力変換

- 従来型の車載パワートレインIC

- クラスD オーディオアンプIC

- 非接触パワー&センシングIC

- DC/DCコンバーター

- ダイオードとサイリスタ (Si/SiC)

- 窒化ガリウム(GaN)

- ゲートドライバIC

- IGBT – 絶縁ゲート型バイポーラトランジスタ

- インテリジェント パワーモジュール (IPM)

- LEDドライバIC

- モータードライバ

- MOSFET

- パワーモジュール

- 電源IC

- 保護および監視IC

- シリコンカーバイド (SiC)

- スマート パワー スイッチ

- ソリッドステートリレー (SSR)

- ワイヤレス充電IC

- 概要

- アンテナクロススイッチ

- アンテナチューナー

- バイアスと制御

- カプラ

- ドライバアンプ

- 耐放射線マイクロ波とRF

- ローノイズアンプ (LNA)

- 高周波ダイオード

- RFスイッチ

- RFトランジスタ

- ワイヤレス制御向けレシーバー

- 概要

- Calypso®製品

- CIPURSE™ 製品

- 非接触メモリ

- OPTIGA™の組込みセキュリティ ソリューションの詳細

- SECORA™セキュリティソリューション

- セキュリ ティコントローラー

- スマートカードモジュール

- 政府ID向けスマートソリューション

- 概要

- USB 2.0 ペリフェラル コントローラー

- USB 3.2 ペリフェラル コントローラー

- USB ハブ コントローラー

- USB PD高電圧マイクロコントローラー

- USB-C AC-DC および DC-DC 充電ソリューション

- USB-C充電ポートコントローラー

- USB-Cパワーデリバリー コントローラー

- 概要

- AIROC™ オートモーティブワイヤレス

- AIROC™ Bluetooth®およびマルチプロトコル

- AIROC™ コネクトテッドMCU

- AIROC™ Wi-Fi + Bluetooth®コンボ

- 概要

- FM0+ 32ビット Arm® Cortex®-M0+ マイクロコントローラー (MCU)

-

FM3 32ビットArm® Cortex-M3®マイクロコントローラー (MCU) ファミリー

- 概要

- FM3 CY9AFx1xKシリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFx1xL/M/N シリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFx2xK/L シリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFx3xK/L シリーズ 超低リーク Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFx4xL/M/N シリーズ 低消費電力 Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFx5xM/N/Rシリーズ 低消費電力 Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9AFxAxL/M/N シリーズ 超低リーク Arm® Cortex®-M3 マイクロコントローラー (MCU)

- FM3 CY9BFx1xN/R 高性能シリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9BFx1xS/T 高性能シリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9BFx2xJシリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9BFx2xK/L/Mシリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM3 CY9BFx2xS/Tシリーズ Arm® Cortex®-M3マイクロコントローラー (MCU)

- FM4 32ビットArm® Cortex-M4®マイクロコントローラー (MCU) ファミリー

- 概要

-

32 ビット TriCore™ AURIX™ – TC2x

- 概要

- AURIX™ ファミリー – TC21xL

- AURIX™ファミリー – TC21xSC (ワイヤレス充電)

- AURIX™ ファミリー – TC22xL

- AURIX™ ファミリー – TC23xL

- AURIX™ ファミリー – TC23xLA (ADAS)

- AURIX™ ファミリー – TC23xLX

- AURIX™ ファミリー – TC264DA (ADAS)

- AURIX™ ファミリー – TC26xD

- AURIX™ ファミリー – TC27xT

- AURIX™ ファミリー – TC297TA (ADAS)

- AURIX™ ファミリー – TC29xT

- AURIX™ファミリー – TC29xTT (ADAS)

- AURIX™ ファミリー – TC29xTX

- AURIX™ TC2xx (エミュレーションデバイス)

-

32 ビット TriCore™ AURIX™ – TC3x

- 概要

- AURIX™ ファミリー TC32xLP

- AURIX™ ファミリー – TC33xDA

- AURIX™ ファミリー - TC33xLP

- AURIX™ ファミリー – TC35xTA (ADAS)

- AURIX™ ファミリー – TC36xDP

- AURIX™ ファミリー – TC37xTP

- AURIX™ ファミリー – TC37xTX

- AURIX™ ファミリー – TC38xQP

- AURIX™ ファミリー – TC39xXA (ADAS)

- AURIX™ ファミリー – TC39xXX

- AURIX™ ファミリー – TC3Ex

- AURIX™ TC37xTE (エミュレーションデバイス)

- AURIX™ TC39xXE (エミュレーションデバイス)

- 32 ビット TriCore™ AURIX™ - TC4x

- 概要

- PSOC™ 4 Arm® Cortex® -M0/M0+

- PSOC™ 4 HV Arm® Cortex® -M0+

- PSOC™ 5 LP Arm® Cortex® -M3

- PSOC™ 6 Arm® Cortex®-M4 / M0+

- PSOC™マルチタッチタッチスクリーンコントローラー

- PSOC™ Control C3 Arm® Cortex®-M33

- 自動車用PSOC™ 4 Arm® Cortex®-M0/M0+

- PSOC™ Edge Arm® Cortex® M55/M33

- 概要

- ボディ用32ビットTRAVEO™T2G Arm® Cortex®

- クラスター用の 32 ビット TRAVEO™ T2G Arm® Cortex®

- 概要

- 32ビットXMC1000産業用マイクロコントローラー Arm® Cortex®-M0

- Cortex-M4® Arm® 32ビットXMC4000産業用マイクロコントローラー

- XMC5000産業用マイクロコントローラーArm® Cortex® -M4F

- 32ビットXMC7000産業用マイクロコントローラー Arm® Cortex®-M7®

- 概要

- 整流ブリッジおよびACスイッチ

- CoolSiC™ ショットキーダイオード

- ダイオードベアダイ

- Si ダイオード

- サイリスタ/ダイオード パワーモジュール

- サイリスタソフトスタータモジュール

- サイリスタ / ダイオードディスク

- 概要

- PSOC™ Control C3 Arm® Cortex®-M33

- モーター制御SoC/SiP

- BLDCモータードライバ

- BDCモータードライバ

- ステッピングモーターおよびサーボモーター ドライバ

- MCU搭載モータードライバ

- MOSFETを使用したブリッジドライバ

- ゲートドライバIC

- 概要

- 車載用MOSFET

- デュアルMOSFET

- MOSFET(Si&SiC)モジュール

- NチャネルデプレッションモードMOSFET

- NチャネルMOSFET

- PチャネルMOSFET

- CoolSiC™ MOSFET

- 小信号/小電力MOSFET

- 概要

- IGBT モジュール

- MOSFET(Si&SiC)モジュール

- インテリジェント パワーモジュール (IPM)

- ダイオードとサイリスタ (Si/SiC)

- 車載用 IGBT および CoolSiC™ MOSFET モジュール

- 高密度パワーモジュール

- 概要

- 車載用トランシーバー

- OPTIREG™リニア電圧レギュレーター (LDO)

- OPTIREG™ PMIC

- OPTIREG™スイッチャー

- OPTIREG™ システム ベーシス チップ (SBC)

- 概要

- EZ-USB™ CX3 MIPI CSI-2 to USB 5 Gbps カメラ コントローラー

- EZ-USB™ FX10 & FX5N USB 10Gbpsペリフェラルコントローラ

- EZ-USB™ FX20 USB 20 Gbpsペリフェラルコントローラー

- EZ-USB™ FX3 USB 5 Gbps ペリフェラル コントローラー

- EZ-USB™ FX3S USB 5 Gbps ペリフェラル コントローラー (ストレージ インターフェース付き)

- EZ-USB™ FX5 USB 5 Gbpsペリフェラルコントローラー

- EZ-USB™ SD3 USB 5 Gbps ストレージコントローラー

- EZ-USB™ SX3: FIFOインターフェースの USB 5 Gbps ペリフェラル コントローラー

- 概要

- EZ-PD™ CCG3 USB Type-Cポート コントローラーPD

- EZ-PD™ CCG3PA USB-C および PD

- EZ-PD™ CCG3PA-NFET USB-C PD コントローラー

- EZ-PD™ CCG7x シングルポート USB-Cパワーデリバリーおよび DC-DC コントローラー

- EZ-PD™ PAG1: 第 1 世代電源アダプター

- EZ-PD™ PAG2: 第 2 世代電源アダプター

- EZ-PD™ PAG2-PD USB-C PD コントローラー

- 概要

- EZ-PD™ ACG1F 1ポートUSB-Cコントローラー

- EZ-PD™ CCG2 USB Type-Cポート コントローラー

- EZ-PD™ CCG3PA車載用USB-Cおよびパワーデリバリーコントローラー

- EZ-PD™ CCG4 2 ポートUSB-CおよびPD

- EZ-PD™ CCG5デュアルポートおよび CCG5C シングルポート USB-C PDコントローラー

- EZ-PD™ CCG6 1ポート USB-C & PDコントローラー

- EZ-PD™ CCG6_CFP および EZ-PD™ CCG8_CFPデュアルシングルポート USB-C PD

- EZ-PD™ CCG6DFデュアルポートおよびCCG6SFシングルポートUSB-C PDコントローラー

- EZ-PD™ CCG7D車載用デュアルポートUSB-C PD + DC-DCコントローラー

- EZ-PD™ CCG7S車載用シングルポートUSB-C PDソリューション (DC-DCコントローラーおよびFET内蔵)

- EZ-PD™ CCG7SAF車載用シングルポートUSB-C PD + DC-DCコントローラー + FET

- EZ-PD™ CCG8デュアル シングル ポートUSB-C PD

- EZ-PD™ CMG1 USB-C EMCAコントローラー

- 拡張パワーレンジ (EPR) 搭載EZ-PD™ CMG2 USB-C EMCA

- 最新情報

- 航空宇宙および防衛

- 自動車

- 民生用電子機器

- ヘルスケアとライフスタイル

- 家電製品

- 産業用アプリケーション

- 情報通信技術

- 再生可能エネルギー

- ロボティックス

- セキュリティソリューション

- スマートホームとスマートビルディング

- ソリューション

- 概要

- 電源アダプターと充電器

- スマートテレビ向けの完全なシステムソリューション

- モバイルデバイスとスマートフォンソリューション

- マルチコプターとドローン

- 電動工具

- ホームエンターテインメント アプリケーション向けの半導体ソリューション

- スマート会議システム

- 概要

- 電源アダプターと充電器

- 資産管理の追跡

- バッテリーの形成とテスト

- 電動フォークリフト

- バッテリー蓄電 (BESS)

- EV充電

- 高電圧ソリッドステート配電

- 産業用オートメーション

- 産業用モータードライブおよび制御

- インダストリー4.0向けの産業用ロボットシステムソリューション

- LED 照明システムの設計

- 小型電気自動車ソリューション

- 電動工具

- 送配電

- トラクション

- 無停電電源装置 (UPS)

- 概要

- バッテリーの形成とテスト

- EV充電

- 水素

- 太陽光発電

- 風力

- ソリッドステート サーキット ブレーカー (SSCB)

- バッテリー蓄電 (BESS)

- 概要

- デバイス認証とブランド保護

- モノのインターネット (IoT) 向けの組み込みセキュリティ

- eSIM アプリケーション

- 公的身分証明書

- モバイルセキュリティ

- 決済ソリューション

- アクセス管理および発券ソリューション

- 概要

- 家庭用ロボット

- 空調システム (HVAC)

- ホームオートメーションとビルオートメーション

- PCアクセサリ

- ホームエンターテインメント アプリケーション向けの半導体ソリューション

- 概要

- 車載用補助システム

- 車載ゲートウェイ

- 車載用パワー分配システム

- ボディコントロールモジュール(BCM)

- コンフォート&コンビニエンス エレクトロニクス

- ゾーンDC-DCコンバーター 48 V~12 V

- ゾーンコントロールユニット

- 概要

- アクティブサスペンションコントロール

- 車載用ブレーキング ソリューション

- 車載用ステアリング ソリューション

- シャーシ ドメイン制御

- 最新情報

- デジタル ドキュメンテーション

- 評価ボード

- ファインダー & セレクション ツール

- プラットフォーム

- サービス

- インフィニオン オンライン パワー シミュレーション プラットフォーム

- ソフトウェア

- ツール

- パートナー

- インフィニオン フォー メーカーズ

- ユニバーシティ アライアンス プログラム

- 概要

- AIROC™ ソフトウェアとツール

- AURIX™のツールとソフトウェア

- 自動車ソフトウェア開発用のDRIVECORE

- iMOTION™ ツールとソフトウェア

- インフィニオンのスマートパワースイッチおよびゲートドライバ ツールスイート

- MOTIX™ ソフトウェア&ツール

- OPTIGA™ ツールとソフトウェア

- PSOC™ ソフトウェアとツール

- TRAVEO™ ソフトウェアとツール

- XENSIV™ツールおよびソフトウェア

- XMC™ ツールとソフトウェア

- 概要

- IPOSIM オンライン パワー シミュレーション プラットフォーム

- CoolGaN™シミュレーションツール(PLECS)

- HiRel フィット レート ツール

- IPOSIM オンライン パワー シミュレーション プラットフォーム

- インフィニオン デザイナー

- インタラクティブな製品シート

- IPOSIM オンライン パワー シミュレーション プラットフォーム

- InfineonSpiceオフラインシミュレーションツール

- OPTIREG™ 車載電源IC シミュレーションツール (PLECS)

- パワーMOSFETシミュレーション モデル

- PowerEsimスイッチモード電源設計ツール

- ソリューションファインダー

- XENSIV™磁気センサー シミュレーション ツール

- 概要

- AURIX™認証

- AURIX™開発ツール

- AURIX™組込みソフトウェア

- AURIX™マイクロコントローラーキット

- 概要

- CAPSENSE™コントローラー コンフィギュレーション ツール EZ-Click

- DC-DC統合POL電圧レギュレーター設定ツール – PowIRCenter

- EZ-USB™ SX3コンフィギュレーション ユーティリティ

- FM+ コンフィギュレーション ツール

- FMx設定ツール

- トランシーバーICコンフィギュレーション ツール

- USB EZ-PD™コンフィギュレーション ユーティリティ

- USB EZ-PD™コンフィギュレーション ユーティリティ

- USB EZ-USB™ HX3C Blaster Plusコンフィギュレーション ユーティリティ

- USB UARTコンフィギュレーション ユーティリティ

- XENSIV™タイヤ空気圧センサーのプログラミング

- 概要

- EZ-PD™ CCGx Dock ソフトウェア開発キット

- FMx Softune IDE

- ModusToolbox™ ソフトウェア

- PSOC™ ソフトウェア

- レーダー開発キット

- 錆

- USBコントローラーSDK

- ワイヤレス接続 Bluetooth メッシュヘルパー アプリケーション

- XMC™ DAVE™ソフトウェア

- 概要

- AIROC™ Bluetooth® Connect Appアーカイブ

- Cypress™ Programmerのアーカイブ

- EZ-PD™ CCGx 電力ソフトウェア開発キットのアーカイブ

- ModusToolbox™ ソフトウェアのアーカイブ

- PSOC™ Creatorのアーカイブ

- PSOC™ Designerのアーカイブ

- PSOC™ Programmerのアーカイブ

- USB EZ-PD™コンフィギュレーション ユーティリティ アーカイブ

- USB EZ-PD™ホストSDKのアーカイブ

- USB EZ-USB™ FX3のアーカイブ

- EZ-USB™ HX3PD コンフィギュレーション ユーティリティ

- WICED™ Smart SDKのアーカイブ

- WICED™ Studioのアーカイブ

- 最新情報

- サポート

- トレーニング

- 開発者コミュニティ

- News

ビジネス&財務プレス

2026/03/10

ビジネス&財務プレス

2026/03/09

ビジネス&財務プレス

2026/03/04

ビジネス&財務プレス

2026/02/19

- 会社概要

- 私たちのストーリー

- イベント

- プレス

- 投資家向け情報

- 採用情報

- 品質

- 最新ニュース

ビジネス&財務プレス

2026/03/10

ビジネス&財務プレス

2026/03/09

ビジネス&財務プレス

2026/03/04

ビジネス&財務プレス

2026/02/19

これは機械翻訳されたコンテンツです。 詳しくは こちらをご覧ください。

AURIX-XILINX-FPGA-LINK

-

このページでは

About

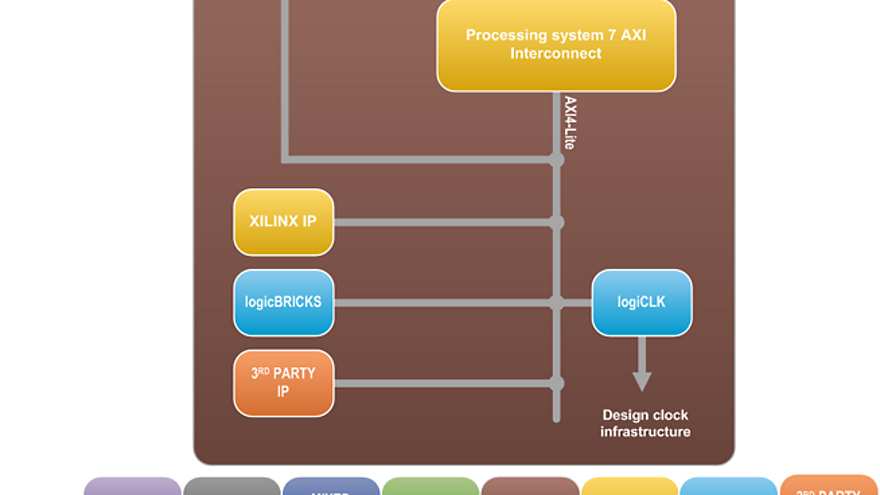

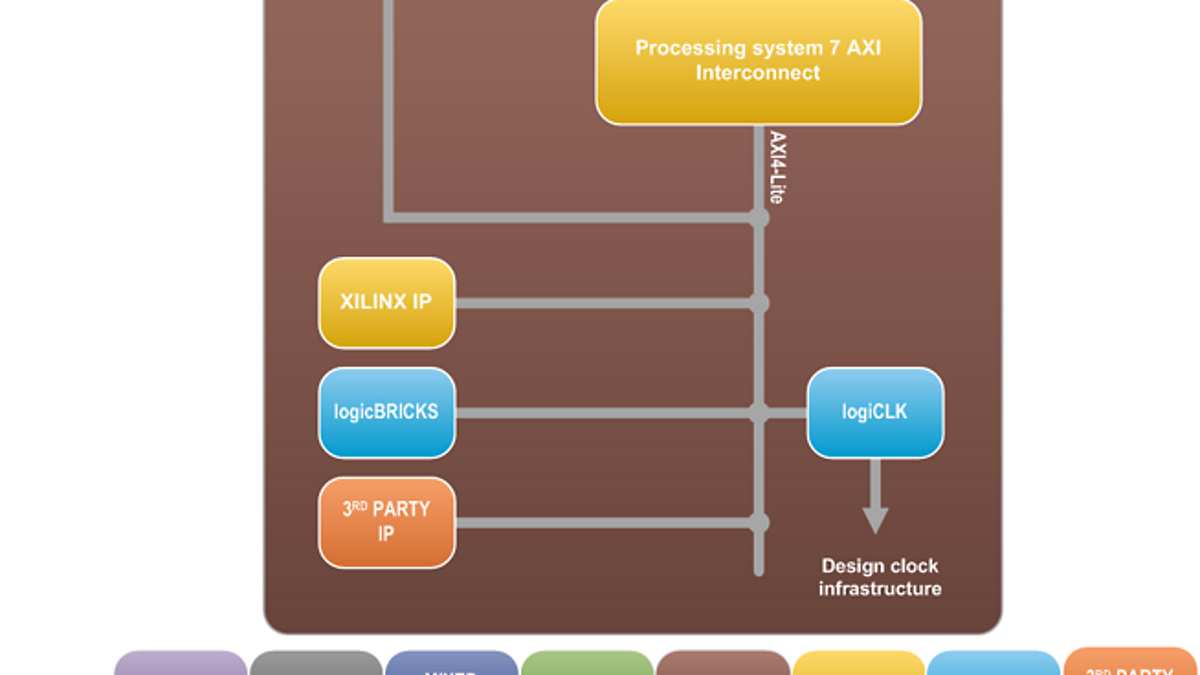

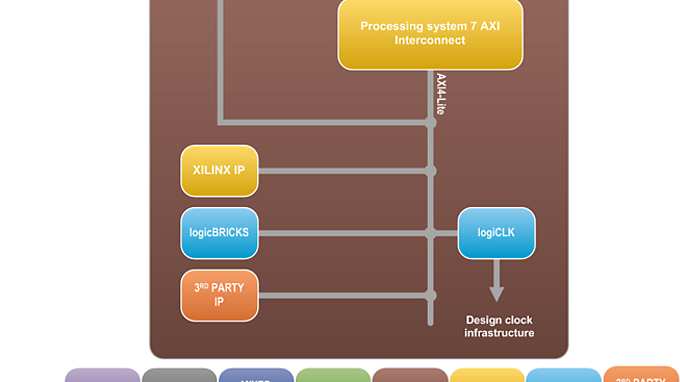

Infineon Technologies AG, Xilinx, Inc. and Xylon, d.o.o. cooperate for more flexibility in using safety microcontrollers in automotive and industrial applications. The new IP-Core of Xylon enables high-speed communication between microcontrollers of Infineon's AURIX family (TC2xx and TC3xx) and Xilinx SoC (System-on-Chip), MPSoC (MultiProcessor SoC) and FPGA (Field Programmable Gate Arrays) devices via the Infineon High Speed Serial Link (HSSL). This serial link supports baud rates of up to 320 Mbaud at a net payload data-rate of up to 84%.

The new IP core will allow system developers to combine functional safety and security provided by AURIX™ with the wide range of functional possibilities brought to the table by the Xilinx devices. Linked devices can access and control each other’s internal and connected resources through the HSSL.

- Currently supports Xilinx 7 Series and Zynq-7000 SoC device families

- Support for Xilinx UltraScale, UltraScale+ FPGA devices, and Zynq UltraScale+ MPSoC planned for the near future.

- HSSL slave device

- Up to 320 Mbaud/s baud rate

- ARM AMBA AXI4-Lite bus protocol compliant as a slave device

- ARM AMBA AXI4 bus protocol compliant as a master device

- 3.25 GB of addressable space covers accesses to:

- FPGA fabric registers and RAM

- PS section register space and OCM

- On-board linearly addressable FLASH devices

- On-board DDR memory

Infineon Technologies AG, Xilinx, Inc. and Xylon, d.o.o. cooperate for more flexibility in using safety microcontrollers in automotive and industrial applications. The new IP-Core of Xylon enables high-speed communication between microcontrollers of Infineon's AURIX family (TC2xx and TC3xx) and Xilinx SoC (System-on-Chip), MPSoC (MultiProcessor SoC) and FPGA (Field Programmable Gate Arrays) devices via the Infineon High Speed Serial Link (HSSL). This serial link supports baud rates of up to 320 Mbaud at a net payload data-rate of up to 84%.

The new IP core will allow system developers to combine functional safety and security provided by AURIX™ with the wide range of functional possibilities brought to the table by the Xilinx devices. Linked devices can access and control each other’s internal and connected resources through the HSSL.

- Currently supports Xilinx 7 Series and Zynq-7000 SoC device families

- Support for Xilinx UltraScale, UltraScale+ FPGA devices, and Zynq UltraScale+ MPSoC planned for the near future.

- HSSL slave device

- Up to 320 Mbaud/s baud rate

- ARM AMBA AXI4-Lite bus protocol compliant as a slave device

- ARM AMBA AXI4 bus protocol compliant as a master device

- 3.25 GB of addressable space covers accesses to:

- FPGA fabric registers and RAM

- PS section register space and OCM

- On-board linearly addressable FLASH devices

- On-board DDR memory

Documents

Documents

デザイン リソース

Image gallery