# **CANXL Controller Area Network XL interface**

AURIX™ TC4xx Microcontroller V1.0.0 2024-09

Please read the Important Notice and Warnings at the end of this document

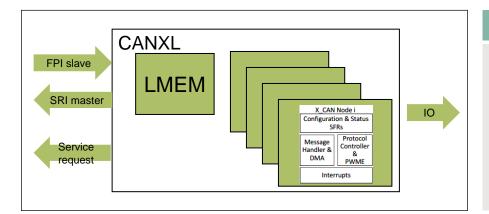

#### Controller Area Network XL interface

#### **Highlights**

- Classical CAN and CAN FD communication according to ISO11898-1:2015

- CAN XL communication according to CiA 610-1

- Compatible to existing CAN, CAN FD and CAN SIC transceiver

- Up to 4 CAN XL nodes

#### **Key Features**

Local Memory (LMEM) stores up to 255 RX filter elements

8 TX FIFO Queues and one TX Priority Queue, 8 RX FIFO Queues

Integrated DMA for message transfers without CPU load

#### **Customer Benefits**

- Data rates up to 15Mbit/s

- Large payload up to 2048 byte enables the use of higher layer protocols and enhanced security

- Interoperability with CAN FD for mixed FD/XL networks

### Local Memory (LMEM) stores up to 255 RX filter elements

- Up to 16 Kbyte shared by the CANXL nodes

- Local RAM

- buffers part of RX/TX messages during transfer from/to system memory

- holds acceptance filter elements

- holds active descriptors for DMA transfer to system memory

### 8 TX FIFO Queues and one TX Priority Queue, 8 RX FIFO Queues

- Usage of queues makes multiple message transmission easier to manage and to prioritize

- > 1 transmit priority queue with maximum of 32 slots for ID-based priority transmission of CAN frames

- The controller will first compare the message ID value for all messages that are in the priority queue and prioritize the transmission of the message with the lowest message ID

- Maximum 8 TX FIFO queues, each with up to 1024 messages

- The controller will transmit the messages in the order they were placed in the FIFO

- The selection of the TX message is done by looking at the gueues in the following order, TX Priority Queue slots from 0 to 31, then the TX FIFO Queues are scanned from 0 to 7

- Maximum 8 RX FIFO queues, each with up to 1024 messages

- The controller will place the received message into the appropriate RX FIFO based on the filter settings.

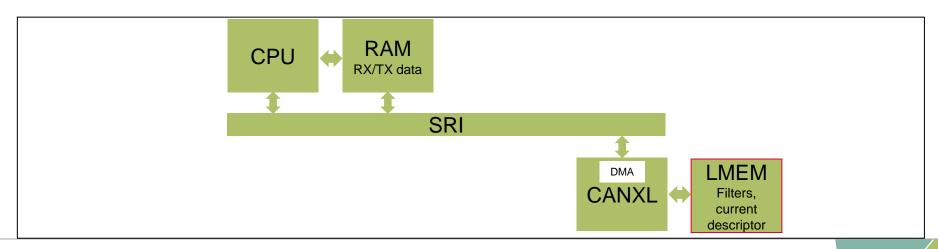

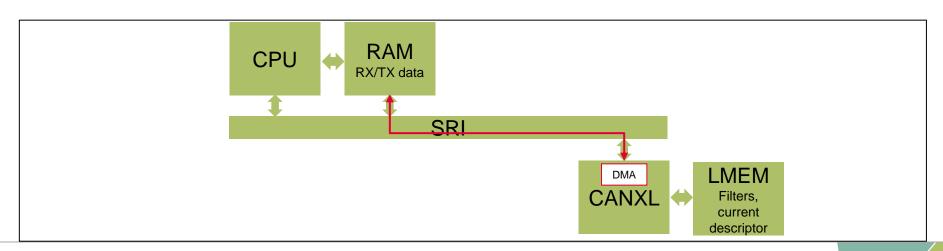

### Integrated DMA for message transfers without CPU load

- CANXL acts as DMA master in the SRI bus for message handling

- > Received data and data to be transmitted is stored in system memory

- Transfer of payload handled by DMA descriptors

- Reduced interrupt load for processor core

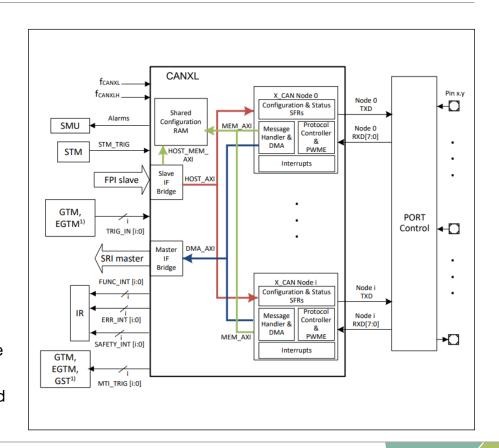

### System integration

#### Clock

- fCANXLH (max. fSRI/2): Clock for message handler, DMA, LMEM

- fCANXL (max 160MHz): reference clock to configure bit timings (Protocol controller)

#### Service requests per node

- CANXL\_IR\_FUNC\_INT: functional events

- CANXL\_IR\_ERR\_INT: error events

- CANXL\_IR\_SAFETY\_INT: safety error events

#### > Time stamp time base clock sources

fCANXLH clock, STM trigger, GTM or eGTM trigger

#### ) IO interface per node

- PORTS\_CANXL\_RXD[7:0]: Multiplexer selecting receive input signal of the CANXL node from available pins

- CANXL\_PORTS\_TXD: Transmit output signal connected to a selection of pins

## Application example Interoperability with CAN FD for mixed FD/XL networks

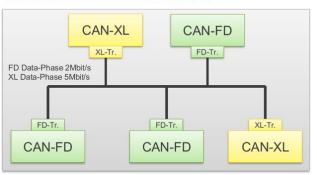

#### Mixed CAN FD / CAN XL Network

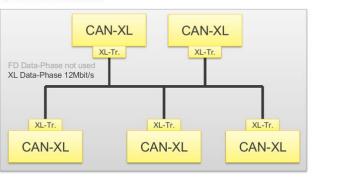

#### **CAN XL Network**

#### **Overview**

- Mixed CAN FD / CAN XL Network: 2 data bit rates on the same bus

- The CAN-XL node can receive the data of the CAN-FD nodes

- The CAN-FD node will ignore the CAN-XL data (limited to SIC mode and Error Signaling enabled)

#### **Advantages**

- Simple migration path for existing CAN FD networks

- CANXL large payload size

- Higher speed

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2024-09 Published by Infineon Technologies AG 81726 Munich, Germany

© 2024 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

Document reference AURIX\_3\_Controller\_Area\_ Network\_XL\_Interface

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics

("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### **WARNINGS**

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.