Microcontrollers

Never stop thinking.

#### **Edition 2004-03**

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 2004.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# **XC164CM**

16-Bit Single-Chip Microcontroller

# Microcontrollers

#### **XC164CM**

| Revision History: Previous Version: |                                                                                                                                                                                                                                     | 2004-03                                      |                           | V1.0D3                                                                      |  |  |  |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------|-----------------------------------------------------------------------------|--|--|--|--|

|                                     |                                                                                                                                                                                                                                     | 2003-02                                      | V1.0D2                    |                                                                             |  |  |  |  |

| Page                                | Subjects                                                                                                                                                                                                                            | Subjects (major changes since last revision) |                           |                                                                             |  |  |  |  |

|                                     | marked w                                                                                                                                                                                                                            | rith change bars                             | •                         | to previous version are re listed below. Especially                         |  |  |  |  |

| 3-4                                 | Setting reset configurations: depending on used to select a reset configuration. Pin P1H5 setting reset configurations. All configuration up. No integrated pull down any more. The corrising edge of RSTIN. Please read pages 3 to |                                              |                           | additionally used for shave an integrated pull guration is latched with the |  |  |  |  |

| 8                                   | There wa                                                                                                                                                                                                                            | s a line mismat                              | ch in the table of Port3. |                                                                             |  |  |  |  |

|                                     |                                                                                                                                                                                                                                     |                                              |                           |                                                                             |  |  |  |  |

Controller Area Network (CAN): License of Robert Bosch GmbH

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

# 1 Delta Sheet XC164CM-8FF to XC164CS-16FF

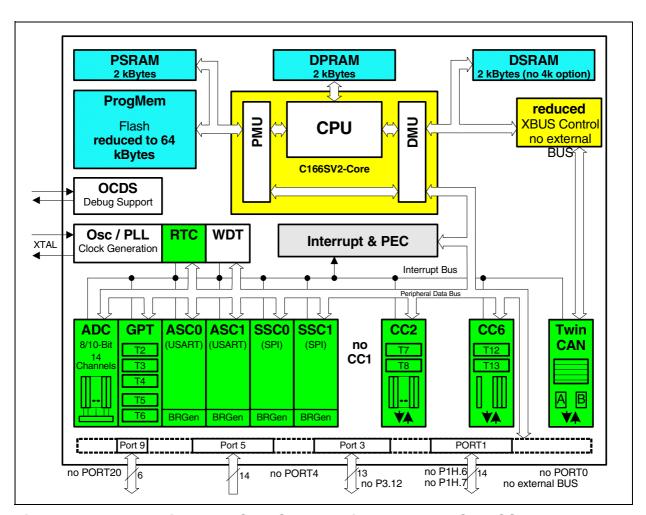

# 1.1 Blockdiagram XC164CM-8F

Figure 1 Blockdiagram XC164CM-8FF with deltas to XC164CS-16FF

# 1.2 Delta Feature Table XC164CS-16FF to XC164CM-8FF

# Table 1 List of feature differences

| Feature       | XC164CS-16FF     | intermediate EES | XC164CM-8FF   |

|---------------|------------------|------------------|---------------|

| Program Flash | 128kB            | 128kB            | 64kB          |

| Memory        | C00000-C1FFFF    | C00000-C1FFFF    | C00000-C0FFFF |

| Program SRAM  | 2kB              | 2kB              | 2kB           |

|               | E00000-E07FFF    | E00000-E07FFF    | E00000-E07FFF |

| Data SRAM     | 2kB (4kB option) | 4kB              | 2kB           |

|               | 00C000-00C7FF    | 00C000-00CFFF    | 00C000-00C7FF |

Draft Delta Sheet 1 V1.0D3, 2004-03

Table 1 List of feature differences

| Feature      | XC164CS-16FF                                                                                               | intermediate EES                                                                                           | XC164CM-8FF                                                                                                |

|--------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Package      | TQFP100                                                                                                    | TQFP64                                                                                                     | TQFP64                                                                                                     |

| CAPCOM1      | on chip available, no IOs, for interrupt generation only                                                   | on chip available, no IOs, for interrupt generation only                                                   | no CAPCOM1<br>module on chip                                                                               |

| CAPCOM2      | fully available with all<br>16 channels, 12 IOs<br>CC16-27IO, Double-<br>register-compare on 8<br>channels | fully available with all<br>16 channels, 10 IOs<br>CC16-25IO, Double-<br>register-compare on 8<br>channels | fully available with all<br>16 channels, 10 IOs<br>CC16-25IO, Double-<br>register-compare on 8<br>channels |

| CAN          | IO pins on port 9 or 4 alternatively                                                                       | IO pins on port9 only                                                                                      | IO pins on port9 only                                                                                      |

| External BUS | available                                                                                                  | not available, single chip mode only                                                                       | not available, single chip mode only                                                                       |

| Port0        | P0L.0-7, P0H0-7                                                                                            | no Port0 pins,<br>no reset configuration<br>with port0 functions<br>possible                               | no Port0 pins, reset configurations via P9, P1 and TRST                                                    |

| Port1        | P1L.0-7, P1H0-7                                                                                            | P1L.0-7, P1H0-5, no<br>P1H6-7, no external<br>bus functions                                                | P1L.0-7, P1H0-5, no<br>P1H6-7, no external<br>bus functions                                                |

| Port3        | P3.1-13, P3.15                                                                                             | P3.1-11, P3.13,<br>P3.15, no pin P3.12                                                                     | P3.1-11, P3.13,<br>P3.15, no pin P3.12                                                                     |

| Port4        | P4.0-7                                                                                                     | no Port 4 pins                                                                                             | no Port 4 pins                                                                                             |

| Port5        | P5.0-7, P5.10-15                                                                                           | all pins available, no changes on Port5                                                                    | all pins available, no changes on Port5                                                                    |

| Port20       | P20.0-5, P20.12                                                                                            | no Port 20 pins, reset<br>configurations via P9<br>possible                                                | no Port 20 pins, reset configurations via P9, P1 and TRST                                                  |

| TRST         | enables JTAG                                                                                               | enables JTAG                                                                                               | enables JTAG and configuration pins sensing during reset                                                   |

Table 2 List of differences in setting configuration modes during reset

| Feature                                               | XC164CS-16FF                                      | intermediate EES                                 | XC164CM-8FF                                                         |

|-------------------------------------------------------|---------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------|

| integrated pull up<br>(PU) /down (PD)<br>during reset | EA PU, RD PU,<br>ALE PD                           | P9.5 PU, P9.4 PD                                 | P1H5 PU, P1H4 PU<br>P9.5 PU, P9.4 PU                                |

| Standard start from internal memory at C00000         | EA=1,RD=1,ALE=0<br>default                        | P9.5=1, P9.4=0<br>(EA is always 1)<br>default    | TRST=1 <sup>1)</sup> P1H5=x, P1H4=x P9.5 =1, P9.4=1 default         |

| Bootstrap loader<br>ASC                               | EA=1,RD= <b>0</b> ,<br>ALE=0<br>EA=0, P0.5-2=1011 | P9.5= <b>0</b> , P9.4=0 (EA is always 1)         | TRST = <b>1</b><br>P1H5=x, P1H4=x<br>P9.5= <b>0</b> , P9.4=1        |

| Bootstrap loader<br>CAN                               | EA=1,RD=0,ALE=1<br>EA=0, P0.5-2=1001              | P9.5= <b>0</b> , P9.4= <b>1</b> (EA is always 1) | TRST = <b>1</b><br>P1H5=x, P1H4=1<br>P9.5=1, P9.4= <b>0</b>         |

| Adapt mode                                            | EA= <b>0</b><br>P0.1= <b>0</b>                    | not possible                                     | TRST = <b>1</b><br>P1H5=1, P1H4=1<br>P9.5= <b>0,</b> P9.4= <b>0</b> |

| Alternate start internal from C10000                  | EA=1,RD=1,ALE=1                                   | P9.5=1, P9.4= <b>1</b><br>(EA is always 1)       | not supported                                                       |

<sup>1)</sup> In XC164CM this mode is used for start from internal memory at C00000 in conjunction with OCDS. Standard start from internal memory at C00000 is always performed if TRST=0 during reset.

Note: Bold means: to be set with external pull resistor.

Draft Delta Sheet 3 V1.0D3, 2004-03

# 1.3 Bootstrap Loader, Adapt Mode, and Test Mode Settings XC164CM

All system start up configurations are locked or enabled by TRST. If pin TRST is pulled low for all the time, then OCDS (including JTAG) and all non standard system start up configurations are always disabled.

For all applications it is recommended to have TRST pulled low for normal operation.

# 1.3.1 Enabling Non Standard System Start Up Configurations

If at the end of reset pin  $\overline{TRST}$  is getting high, then pins P1H.5 (pin 6), P1H.4 (5), P9.5 (48), and P9.4 (47) are used to select one of the non standard system start up configurations. This setting is latched with the rising edge of  $\overline{RSTIN}$ .

Table 3 Mode Selection Overview

| P1H | P1H | P9. | P9. | Selected Mode                                                                                                                                                |

|-----|-----|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .5  | .4  | 5   | 4   |                                                                                                                                                              |

| X   | X   | 1   | 1   | Start internal: default setting, internal start from address C00000 . To be used for internal start from C00000 with OCDS debuggers (0011, 0111, 1011, 1111) |

| Х   | х   | 0   | 1   | BSL-ASC: Bootstrap loader ASC                                                                                                                                |

| Х   | 1   | 1   | 0   | BSL-CAN: Bootstrap loader CAN                                                                                                                                |

| 1   | 1   | 0   | 0   | Adapt Mode: all pins are tristate used for connecting an incircuit emulator                                                                                  |

| 0   | 0   | 0   | 0   | Test modes                                                                                                                                                   |

| 0   | 0   | 1   | 0   | do not use any of these settings.                                                                                                                            |

| 0   | 1   | 0   | 0   | In order to avoid such settings do not pull down P1H4 or P1H5 during reset and TRST=1                                                                        |

| 1   | 0   | 0   | 0   |                                                                                                                                                              |

| 1   | 0   | 1   | 0   |                                                                                                                                                              |

# 1.3.2 Enabling Normal Operation

If at the end of reset  $\overline{TRST}$  is low, then always the default system start up configuration is selected and the configuration 1111 is latched. Code execution is starting from address C0 0000. For safety aspects keep  $\overline{TRST}$  low for normal operation.

# 1.3.3 Enabling OCDS During Normal Operation

If only TRST is getting high while RSTIN remains low, then the microcontroller does not perform a reset but the JTAG interface is getting enabled.

Draft Delta Sheet 4 V1.0D3, 2004-03

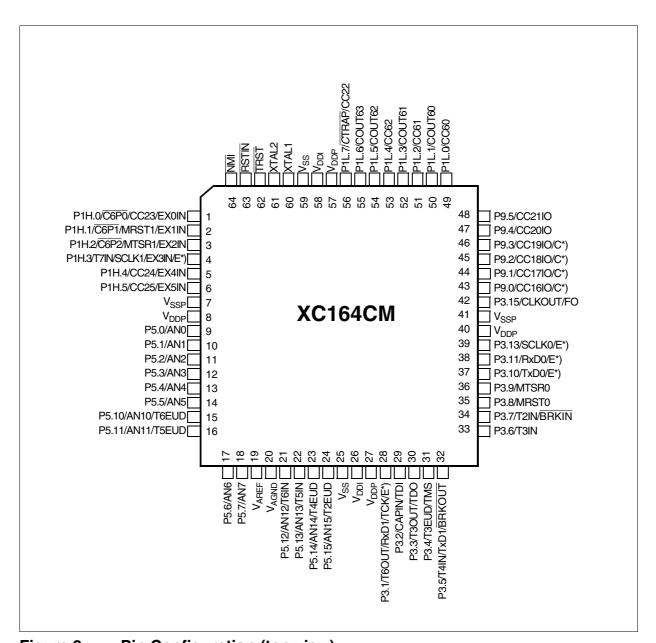

### 1.4 Pin Configuration and Definition

The pins of the XC164CM are described in detail in **Table 4**, including all their alternate functions. **Figure 2** summarizes all pins in a condensed way, showing their location on the 4 sides of the package. E\*) and C\*) mark pins to be used as alternate external interrupt inputs, C\*) marks pins that can have CAN interface lines assigned to them.

Figure 2 Pin Configuration (top view)

Draft Delta Sheet 5 V1.0D3, 2004-03

Table 4 Pin Definitions and Functions

| Symbol       | Pin<br>Num. | Input<br>Outp.          |                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|--------------|-------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RSTIN        | 63          | I                       | Reset Input with Schmitt-Trigger characteristics. A low level at this pin while the oscillator is running resets the XC164CM. A spike filter suppresses input pulses <10 ns. Input pulses >100 ns safely pass the filter. The minimum duration for a safe recognition should be 100 ns + 2 CPU clock cycles.                                                                                       |  |  |

|              |             |                         | Note: The reset duration must be sufficient to let the hardware configuration signals settle.  External circuitry must guarantee low level at the RSTIN pin at least until both power supply voltages have reached the operating range.                                                                                                                                                            |  |  |

| NMI          | 64          | 1                       | Non-Maskable Interrupt Input. A high to low transition at this pin causes the CPU to vector to the NMI trap routine. When the PWRDN (power down) instruction is executed, the NMI pin must be low in order to force the XC164CM into power down mode. If NMI is high, when PWRDN is executed, the part will continue to run in normal mode. If not used, pin NMI should be pulled high externally. |  |  |

| P9           | 43-48       | Ю                       | Port 9 is a 6-bit bidirectional I/O port. Each pin can be programmed for input (output driver in high-impedance state) or output (configurable as push/pull or open drain driver). The input threshold of Port 9 is selectable (standard or special). The following Port 9 pins also serve for alternate functions: <sup>1)</sup>                                                                  |  |  |

| P9.0         | 43          | I/O<br>I                | CC16IO CAPCOM2: CC16 Capture Inp./Compare Outp., CAN2_RxD CAN Node 2 Receive Data Input, EX7IN Fast External Interrupt 7 Input (alternate pin B)                                                                                                                                                                                                                                                   |  |  |

| P9.1         | 44          | I/O<br>O                | CC17IO CAPCOM2: CC17 Capture Inp./Compare Outp., CAN2_TxD CAN Node 2 Transmit Data Output, EX6IN Fast External Interrupt 6 Input (alternate pin B)                                                                                                                                                                                                                                                 |  |  |

| P9.2         | 45          | I/O<br>I                | CC18IO CAPCOM2: CC18 Capture Inp./Compare Outp., CAN1_RxD CAN Node 1 Receive Data Input,                                                                                                                                                                                                                                                                                                           |  |  |

| P9.3         | 46          | <br>  I/O<br>  O<br>  I | EX7IN Fast External Interrupt 7 Input (alternate pin A) CC19IO CAPCOM2: CC19 Capture Inp./Compare Outp., CAN1_TxD CAN Node 1 Transmit Data Output, EX6IN Fast External Interrupt 6 Input (alternate pin A)                                                                                                                                                                                         |  |  |

| P9.4<br>P9.5 | 47<br>48    | I/O<br>I/O              | CC20IO CAPCOM2: CC20 Capture Inp./Compare Outp. <sup>2)</sup> CC21IO CAPCOM2: CC21 Capture Inp./Compare Outp. <sup>2)</sup>                                                                                                                                                                                                                                                                        |  |  |

Table 4

Pin Definitions and Functions (cont'd)

| Symbol   | Pin<br>Num. | Input<br>Outp. | Function                                                  |                                                                                                                                 |  |

|----------|-------------|----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| PORT1    |             | Ю              | and P1H. E<br>in high-imp                                 | nsists of the two 8-bit bidirectional I/O ports P1L ach pin can be programmed for input (output driver edance state) or output. |  |

|          |             |                |                                                           | 1 pins serve for the following functions:                                                                                       |  |

| P1L.0    | 49          | I/O            | CC60                                                      | CAPCOM6: Input / Output of Channel 0                                                                                            |  |

| P1L.1    | 50          | 0              | COUT60                                                    | CAPCOM6: Output of Channel 0                                                                                                    |  |

| P1L.2    | 51          | I/O            | CC61                                                      | CAPCOM6: Input / Output of Channel 1                                                                                            |  |

| P1L.3    | 52          | 0              | COUT61                                                    | CAPCOM6: Output of Channel 1                                                                                                    |  |

| P1L.4    | 53          | I/O            | CC62                                                      | CAPCOM6: Input / Output of Channel 2                                                                                            |  |

| P1L.5    | 54          | 0              | COUT62                                                    | CAPCOM6: Output of Channel 2                                                                                                    |  |

| P1L.6    | 55          | 0              | COUT63                                                    | Output of 10-bit Compare Channel                                                                                                |  |

| P1L.7    | 56          | I              | CTRAP                                                     | CAPCOM6: Trap Input                                                                                                             |  |

|          |             |                |                                                           | an input pin with an internal pullup resistor. A low                                                                            |  |

|          |             |                |                                                           | s pin switches the CAPCOM6 compare outputs to                                                                                   |  |

|          |             |                | _                                                         | vel defined by software (if enabled).                                                                                           |  |

|          |             | I/O            | CC22IO                                                    | CAPCOM2: CC22 Capture Inp./Compare Outp.                                                                                        |  |

| P1H.0    | 1           | I              | CC6POS0                                                   | CAPCOM6: Position 0 Input,                                                                                                      |  |

|          |             |                | EX0IN                                                     | Fast External Interrupt 0 Input (default pin),                                                                                  |  |

|          |             | I/O            | CC23IO                                                    | CAPCOM2: CC23 Capture Inp./Compare Outp.                                                                                        |  |

| P1H.1    | 2           | I              | CC6POS1                                                   | CAPCOM6: Position 1 Input,                                                                                                      |  |

|          |             |                | EX1IN                                                     | Fast External Interrupt 1 Input (default pin),                                                                                  |  |

|          | _           | I/O            | MRST1                                                     | SSC1 Master-Receive/Slave-Transmit In/Out.                                                                                      |  |

| P1H.2    | 3           | 1              | CC6POS2                                                   | CAPCOM6: Position 2 Input,                                                                                                      |  |

|          |             |                | EX2IN                                                     | Fast External Interrupt 2 Input (default pin),                                                                                  |  |

|          |             | I/O            | MTSR1                                                     | SSC1 Master-Transmit/Slave-Receive Out/Inp.                                                                                     |  |

| P1H.3    | 4           |                | T7IN                                                      | CAPCOM2: Timer T7 Count Input,                                                                                                  |  |

|          |             | I/O            | SCLK1                                                     | SSC1 Master Clock Output / Slave Clock Input,                                                                                   |  |

| <b>5</b> | _           |                | EX3IN                                                     | Fast External Interrupt 3 Input (default pin),                                                                                  |  |

| P1H.4    | 5           | I/O            | CC24IO                                                    | CAPCOM2: CC24 Capture Inp./Compare Outp.,                                                                                       |  |

|          |             |                | EX4IN                                                     | Fast External Interrupt 4 Input (default pin) <sup>2)</sup>                                                                     |  |

| P1H.5    | 6           | I/O            | CC25IO                                                    | CAPCOM2: CC25 Capture Inp./Compare Outp.,                                                                                       |  |

|          |             | <u> </u>       | EX5IN                                                     | Fast External Interrupt 5 Input (default pin) <sup>2)</sup>                                                                     |  |

| XTAL2    | 61          | 0              | XTAL2:                                                    | Output of the oscillator amplifier circuit                                                                                      |  |

| XTAL1    | 60          | I              | XTAL1:                                                    | Input to the oscillator amplifier and input to                                                                                  |  |

|          |             |                | T1: -1 **                                                 | the internal clock generator                                                                                                    |  |

|          |             |                | To clock the device from an external source, drive XTAL1, |                                                                                                                                 |  |

|          |             |                | while leaving XTAL2 unconnected. Minimum and maximum      |                                                                                                                                 |  |

|          |             |                | _                                                         | d rise/fall times specified in the AC Characteristics                                                                           |  |

|          |             |                | must be ob                                                | SEIVEU.                                                                                                                         |  |

Draft Delta Sheet 7 V1.0D3, 2004-03

Table 4

Pin Definitions and Functions (cont'd)

| Symbol | Pin<br>Num. | Input<br>Outp. | Function            |                                                                                                                                                                              |

|--------|-------------|----------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3     |             | Ю              | programme           | 13-bit bidirectional I/O port. Each pin can be ed for input (output driver in high-impedance state) configurable as push/pull or open drain driver). The                     |

|        |             |                |                     | hold of Port 3 is selectable (standard or special).                                                                                                                          |

|        |             |                | •                   | ing Port 3 pins also serve for alternate functions:                                                                                                                          |

| P3.1   | 28          | 0              | T6OUT               | GPT2 Timer T6 Toggle Latch Output,                                                                                                                                           |

|        |             | I/O            | RxD1                | ASC1 Data Input (Async.) or Inp./Outp. (Sync.),                                                                                                                              |

|        |             | I              | EX1IN               | Fast External Interrupt 1 Input (alternate pin A),                                                                                                                           |

|        |             | 1              | TCK                 | Debug System: JTAG Clock Input                                                                                                                                               |

| P3.2   | 29          | 1              | CAPIN               | GPT2 Register CAPREL Capture Input,                                                                                                                                          |

|        |             | 1              | TDI                 | Debug System: JTAG Data In                                                                                                                                                   |

| P3.3   | 30          | 0              | T3OUT               | GPT1 Timer T3 Toggle Latch Output,                                                                                                                                           |

|        |             | 0              | TDO                 | Debug System: JTAG Data Out                                                                                                                                                  |

| P3.4   | 31          | 1              | T3EUD               | GPT1 Timer T3 External Up/Down Control Input,                                                                                                                                |

|        |             | I              | TMS                 | Debug System: JTAG Test Mode Selection                                                                                                                                       |

| P3.5   | 32          | I              | T4IN                | GPT1 Timer T4 Count/Gate/Reload/Capture Inp                                                                                                                                  |

|        |             | 0              | TxD1                | ASC1 Clock/Data Output (Async./Sync.),                                                                                                                                       |

|        |             | 0              | BRKOUT              | Debug System: Break Out                                                                                                                                                      |

| P3.6   | 33          | I              | T3IN                | GPT1 Timer T3 Count/Gate Input                                                                                                                                               |

| P3.7   | 34          | I              | T2IN                | GPT1 Timer T2 Count/Gate/Reload/Capture Inp                                                                                                                                  |

|        |             | I              | BRKIN               | Debug System: Break In                                                                                                                                                       |

| P3.8   | 35          | I/O            | MRST0               | SSC0 Master-Receive/Slave-Transmit In/Out.                                                                                                                                   |

| P3.9   | 36          | I/O            | MTSR0               | SSC0 Master-Transmit/Slave-Receive Out/In.                                                                                                                                   |

| P3.10  | 37          | 0              | TxD0                | ASC0 Clock/Data Output (Async./Sync.),                                                                                                                                       |

|        |             | 1              | EX2IN               | Fast External Interrupt 2 Input (alternate pin B)                                                                                                                            |

| P3.11  | 38          | I/O            | RxD0                | ASC0 Data Input (Async.) or Inp./Outp. (Sync.),                                                                                                                              |

|        |             | l<br>          | EX2IN               | Fast External Interrupt 2 Input (alternate pin A)                                                                                                                            |

| P3.13  | 39          | I/O            | SCLK0               | SSC0 Master Clock Output / Slave Clock Input.,                                                                                                                               |

| D0 45  | 4.0         | I              | EX3IN               | Fast External Interrupt 3 Input (alternate pin A)                                                                                                                            |

| P3.15  | 42          | 0              | CLKOUT              | System Clock Output (=CPU Clock),                                                                                                                                            |

|        |             | 0              | FOUT                | Programmable Frequency Output                                                                                                                                                |

| TRST   | 62          | I              | XC164CM configurati | om Reset Input. A high level at this pin activates the s's debug system and/or the non default on functions on ports 1 and 9. For normal system pin TRST should be held low. |

Draft Delta Sheet 8 V1.0D3, 2004-03

Table 4

Pin Definitions and Functions (cont'd)

| Symbol                | Pin<br>Num.      | Input<br>Outp. | Function                                                                                                                                                                                           |           |                                       |  |

|-----------------------|------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|--|

| P5                    |                  | 1              | Port 5 is a 14-bit input-only port.  The pins of Port 5 also serve as analog input channels for the A/D converter, or they serve as timer inputs:                                                  |           |                                       |  |

| P5.0                  | 9                | 1              | AN0                                                                                                                                                                                                |           |                                       |  |

| P5.1                  | 10               | I              | AN1                                                                                                                                                                                                |           |                                       |  |

| P5.2                  | 11               | 1              | AN2                                                                                                                                                                                                |           |                                       |  |

| P5.3                  | 12               | 1              | AN3                                                                                                                                                                                                |           |                                       |  |

| P5.4                  | 13               | 1              | AN4                                                                                                                                                                                                |           |                                       |  |

| P5.5                  | 14               | 1              | AN5                                                                                                                                                                                                |           |                                       |  |

| P5.10                 | 15               | I              | AN10, T                                                                                                                                                                                            | Γ6EUD     | GPT2 Timer T6 Ext. Up/Down Ctrl. Inp. |  |

| P5.11                 | 16               | I              | AN11, T                                                                                                                                                                                            | Γ5EUD     | GPT2 Timer T5 Ext. Up/Down Ctrl. Inp. |  |

| P5.6                  | 17               | 1              | AN6                                                                                                                                                                                                |           |                                       |  |

| P5.7                  | 18               | I              | AN7                                                                                                                                                                                                |           |                                       |  |

| P5.12                 | 21               | 1              | AN12, T                                                                                                                                                                                            | Γ6ΙΝ      | GPT2 Timer T6 Count/Gate Input        |  |

| P5.13                 | 22               | I              | AN13, T                                                                                                                                                                                            | Γ5ΙΝ      | GPT2 Timer T5 Count/Gate Input        |  |

| P5.14                 | 23               | 1              | AN14, T                                                                                                                                                                                            | Γ4EUD     | GPT1 Timer T4 Ext. Up/Down Ctrl. Inp. |  |

| P5.15                 | 24               | 1              | AN15, T                                                                                                                                                                                            | Γ2EUD     | GPT1 Timer T2 Ext. Up/Down Ctrl. Inp. |  |

| $\overline{V_{AREF}}$ | 19               | -              | Reference vo                                                                                                                                                                                       | oltage fo | r the A/D converter.                  |  |

| $\overline{V_{AGND}}$ | 20               | -              | Reference gr                                                                                                                                                                                       | ound fo   | r the A/D converter.                  |  |

| $\overline{V_{DDI}}$  | 26, 58           | -              | Core Supply Voltage (On-Chip Modules): +2.5 V during normal operation and idle mode. Please refer to the Operating Conditions                                                                      |           |                                       |  |

| $\overline{V_{DDP}}$  | 8, 27,<br>40, 57 | -              | Pad Supply Voltage (Pin Output Drivers): +5 V during normal operation and idle mode. Please refer to the Operating Conditions                                                                      |           |                                       |  |

| $\overline{V_{SS}}$   | 7, 25,<br>41, 59 | -              | Ground. Connect decoupling capacitors to adjacent $V_{\rm DDx}/V_{\rm SS}$ pin pairs as close as possible to the pins. All $V_{\rm SS}$ pins must be connected to the ground-line or ground-plane. |           |                                       |  |

<sup>1)</sup> The CAN interface lines are assigned to port P9 under software control.

Draft Delta Sheet 9 V1.0D3, 2004-03

<sup>&</sup>lt;sup>2)</sup> If at the end of an external reset TRST was high these pins are used for sensing configuration settings and integrated pull up devices are activated during reset.