# Universal Digital Block (UDB) Editor Guide

Document Number 001-94131, Rev. \*\*, 9/24/2014

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone): 408.943.2600 http://www.cypress.com

#### Copyrights

Copyright © 2014 Cypress Semiconductor Corporation. All rights reserved.

"Programmable System-on-Chip," PSoC, PSoC Designer, and PSoC Express are trademarks of Cypress Semiconductor Corporation (Cypress), along with Cypress® and Cypress Semiconductor™. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

The information in this document is subject to change without notice and should not be construed as a commitment by Cypress. While reasonable precautions have been taken, Cypress assumes no responsibility for any errors that may appear in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Cypress. Made in the U.S.A.

#### Disclaimer

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

#### Flash Code Protection

Cypress products meet the specifications contained in their particular Cypress PSoC Data Sheets. Cypress believes that its family of PSoC products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# Contents

| Introduction                                                                                                                                        | 4              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| What is a UDB?                                                                                                                                      | 4              |

| Conventions                                                                                                                                         | 6              |

| Acronyms and Abbreviations                                                                                                                          | 6              |

| References                                                                                                                                          | 6              |

| Revision History                                                                                                                                    | 6              |

| UDB Editor Overview                                                                                                                                 | 7              |

| Opening the UDB Editor                                                                                                                              | 8              |

| UDB Editor Elements                                                                                                                                 | 9              |

| Datapath                                                                                                                                            | 10             |

| Control Register                                                                                                                                    | 18             |

| Status Register                                                                                                                                     | 19             |

| Status Interrupt Register                                                                                                                           | 20             |

| Count7 Counter                                                                                                                                      | 21             |

| State Machine                                                                                                                                       | 22             |

| UDB Editor APIs                                                                                                                                     | 25             |

| Example UDB Editor Design                                                                                                                           | 27             |

| Step 1: Create a Custom Component                                                                                                                   | 28             |

| Step 2: Define the Component Inputs and Outputs                                                                                                     | 29             |

| Step 3: Create a State Machine to Control the Datapath Inputs                                                                                       |                |

| Step 4: Configure the Datapath                                                                                                                      | 34             |

| Otom F. Oranta the Orange and Orankal                                                                                                               | 41             |

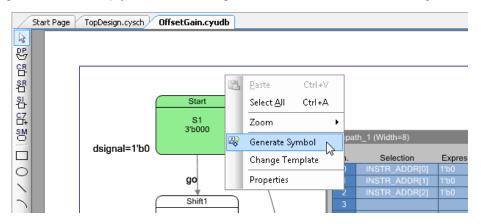

| Step 5: Create the Component Symbol                                                                                                                 | 42             |

| Step 5: Create the Component Symbol                                                                                                                 |                |

|                                                                                                                                                     |                |

| Step 6: Build the Component APIs                                                                                                                    | 44             |

| Step 6: Build the Component APIs<br>Step 7: Use the New Component                                                                                   | 44<br>46       |

| Step 6: Build the Component APIs<br>Step 7: Use the New Component<br>Additional projects                                                            | 44<br>46<br>47 |

| Step 6: Build the Component APIs<br>Step 7: Use the New Component<br>Additional projects<br>Appendix A: Datapath Operation                          |                |

| Step 6: Build the Component APIs<br>Step 7: Use the New Component<br>Additional projects<br>Appendix A: Datapath Operation<br>Datapath Instructions |                |

| Step 6: Build the Component APIs                                                                                                                    |                |

# Introduction

This document provides a guide to learn about and use the PSoC Creator Universal Digital Block (UDB) Editor. It provides basic information about UDBs, an overview and description of the UDB Editor, and an example UDB Editor design. The appendices provide more detailed information about UDB elements and expressions.

## What is a UDB?

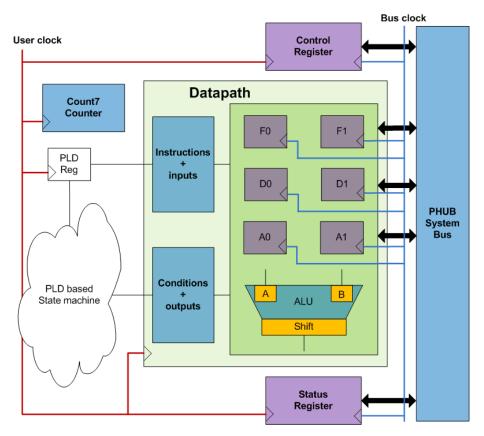

A UDB is a flexible, programmable digital block inside a PSoC device that is designed to realize synchronous State Machines. The following figure shows the main blocks in a UDB from a high level. For detailed information about the UDB architecture of a specific device, refer to that device *Technical Reference Manual (TRM)*.

A UDB is capable of an array of functions including:

- Cascading multiple UDBs to make a wider than 8-bit function

- Communication components (like SPI, I<sup>2</sup>C, and UART)

- Flexible logic machines (like PWMs)

Each 8-bit wide UDB has five elements:

- A Datapath element is an 8-bit wide processor that can be used to perform simple arithmetic and bitwise operations on data words. It can be chained to form 16-, 24-, and 32-bit wide processors. It can have up to 8 user-defined instructions that are often driven using the programmable logic device (PLD) based State Machine. Datapaths form the core of many UDB designs and should be used in preference over PLD designs when 8-bit words or larger are used. A DP element has:

- □ A programmable 8-bit wide Arithmetic Logic Unit (ALU)

- □ Two 8-bit accumulator registers (A0, A1)

- □ Two 8-bit data registers (D0, D1)

- □ Two 8-bit wide, 4 deep FIFOs (F0, F1)

- □ A shifting function

- □ A masking function

See Datapath Registers for more details about registers.

- Two 12C4 PLDs (used to create State Machines). These are most often used to create logic to control the other structured resources available in a UDB. PLD-based designs are composed of both combinational logic and sequential logic. The sequential logic is driven with the user clock. Although PLDs are the most flexible element in a UDB, it is also relatively limited resource. Therefore it is recommended to use the other structured blocks as much as possible when implementing large designs.

- An 8-bit wide Control Register (accessible from the processor and the PSoC hardware). A Control Register is used in a UDB to control the digital hardware with the CPU. Using a Control Register, it is possible for the CPU to directly send logic values to the UDB hardware. The reading and writing of the Control Register from the CPU is performed at the bus clock, unless it is in sync or pulse mode with the user defined clock. In this case, it will run at the clock rate of the UDB Editor component (specified by the "clock" input of the component).

- An 8-bit wide Status Register (accessible from the processor and the PSoC hardware). A Status Register is used to read logic values from the UDB and CPLD logic into the CPU. The rate at which the Status Register reads the digital logic is controlled by the bus clock. Status registers also have the ability to mask 7 bits in the status register for generating an interrupt. This is accomplished by using one pin for the interrupt output and the other 7 bits as the maskable triggers for the interrupt.

- A 7-bit down counter (Count7) that can be used instead of implementing a counter in a State Machine/Verilog or a Datapath. This uses the same resource as a Control Register. The terminal count of the counter can then be used throughout your design.

These elements can be used to form many types of logic and can be chained together to form large designs. A design may communicate with the CPU, with other hardware blocks in a PSoC device, or both. This flexibility allows the UDB to form logic that links other hardware in your design, or can be a stand-alone block that performs a new function.

UDBs can be divided into uncommitted logic and structured logic. The structured logic includes the Datapath, Control Register, Status Register (Status Interrupt Register if enabled), and Count7 counter. These can be controlled by the CPU through the Control Register and Status Register. Alternatively, the uncommitted PLD logic can be used to design State Machines that can generate control signals for these blocks.

UDBs are driven with a user clock and the bus clock. The bus clock synchronizes reads from and writes to the registers in the Datapath and the Control Register and Status Register. These data words travel through the Peripheral Hub (PHUB) system bus. The user clock drives the blocks in the UDB. Signals in a UDB can be routed to form a hardware output in a component or can be used to drive the inputs of the structured blocks in a UDB.

## Conventions

| Convention         | Usage                                                                       |

|--------------------|-----------------------------------------------------------------------------|

| Courier New        | Displays file locations and source code:                                    |

|                    | C:\cd\icc user entered text                                                 |

| Italics            | Displays file names and reference documentation:                            |

|                    | sourcefile.hex                                                              |

| [bracketed, bold]  | Displays keyboard commands in procedures:                                   |

|                    | [Enter] or [Ctrl] [C]                                                       |

| File > New Project | Represents menu paths:                                                      |

|                    | File > New Project > Clone                                                  |

| Bold               | Displays commands, menu paths and selections, and icon names in procedures: |

|                    | Click the <b>Debugger</b> icon, and then click <b>Next</b> .                |

The following table lists the conventions used throughout this guide:

## Acronyms and Abbreviations

This guide contains the following acronyms and abbreviations:

- ALU Arithmetic Logic Unit

- API Application Programming Interface

- FIFO First In, First Out

- HDL Hardware Description Language

- PHUB Peripheral Hub

- TRM Technical Reference Manual

- UDB Universal Digital Block

## References

This guide is one of a set of documents pertaining to UDBs. Refer to the following other documents as needed:

- PSoC Creator Help

- PSoC Creator Component Datasheets

- PSoC Creator Component Author Guide

- PSoC Technical Reference Manual (TRM)

- Application Note AN82156: Designing PSoC Creator Components with UDB Datapaths

## **Revision History**

| Document Title: PSoC® Creator™ UDB Editor Guide |                            |                       |  |  |  |  |

|-------------------------------------------------|----------------------------|-----------------------|--|--|--|--|

| Document Number: 0                              | Document Number: 001-94131 |                       |  |  |  |  |

| Revision                                        | Date                       | Description of Change |  |  |  |  |

| **                                              | 9/24/14                    | New document.         |  |  |  |  |

# UDB Editor Overview

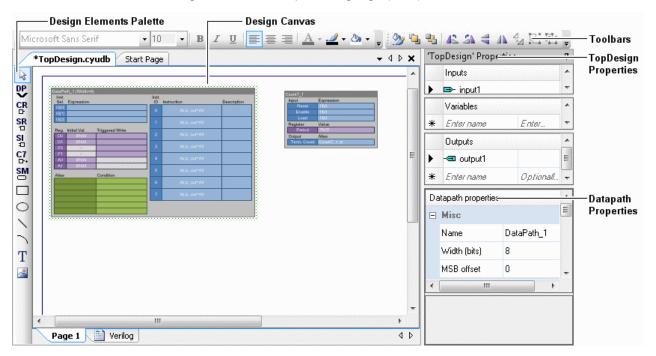

The UDB Editor allows you to create UDB-based designs with very little knowledge of digital logic or Verilog code. Using this graphical tool, you drag, drop, and then configure your hardware without having to write Verilog code. The UDB Editor takes care of many internal configuration details simply by specifying the parameters of the UDB blocks on the design canvas. The tool translates your design to Verilog in real time, allowing you to see how the UDB blocks translate to Verilog hardware description language (HDL).

**Note** The UDB Editor allows you to construct UDB-based designs without the need of writing Verilog or using the more advanced Datapath Configuration Tool. However, using this tool sacrifices some flexibility and fine-grained control over the hardware as a result of simplifying abstractions. It also does not incorporate some of the more advanced UDB functionality, and this may be limiting for complex designs. For more information about using Verilog and the Datapath Configuration Tool, refer to the *PSoC Creator Component Author Guide*, as well as *Application Note AN82156: Designing PSoC Creator Components with UDB Datapaths*.

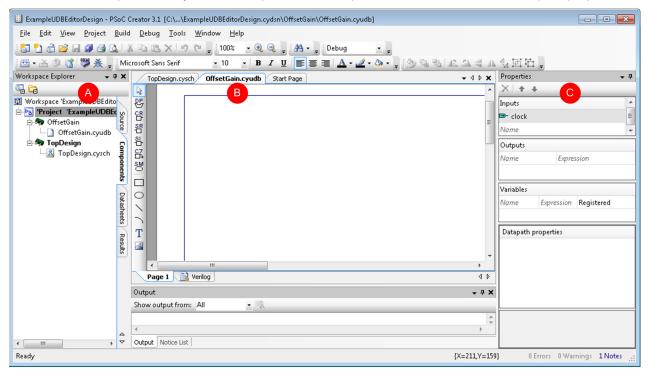

The main areas of the UDB Editor include:

- Design Elements Palette The design elements palette is a menu used to choose the UDB elements to include in your design. See <u>UDB Editor Elements</u>.

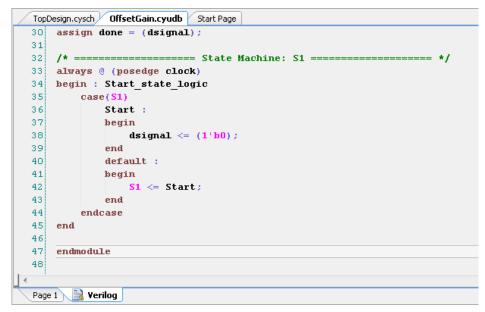

- Design Canvas Pages Once you open a UDB Editor document, you will see an editable page like a schematic page. This is your design canvas, used to place and configure your UDB elements. Additional UDB Editor pages may be added by right-clicking on the Page 1 tab. These pages then are translated to Verilog as a single unit. Verilog Next to the Page tab, you can find the Verilog tab. This is a read-only view of the translated HDL for your design. It is dynamically updated so whenever a change is made in

your design, it will also update the code. This code is not editable, and you cannot delete it; any desired changes must be made in the design canvas. You may also copy and paste this code to a Verilog file if you wish to edit your design using Verilog. Refer to Application Note AN82156: Designing PSoC Creator Components with UDB Datapaths for more details.

Design Properties – Located to the right of the design canvas, the design properties allow you to configure the inputs, outputs, and variables used in your design. The inputs and outputs will then form your symbol terminals when your design is complete. The design properties window is also used to set the global Datapath configuration when a Datapath is selected in your design.

## **Opening the UDB Editor**

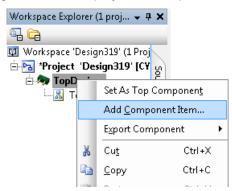

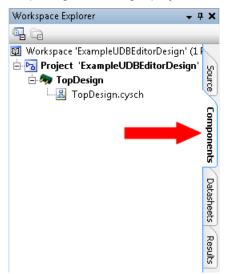

The UDB Editor is used to create a custom UDB-based component, which you then use in a design. So, to open and use the UDB Editor, you have to create a component. For more detailed information about creating components, refer to the *PSoC Creator Component Author Guide*.

- 1. Create a new project or open an existing project.

- 2. In the Workspace Explorer, click the Components tab.

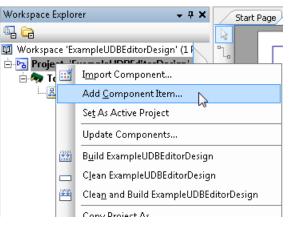

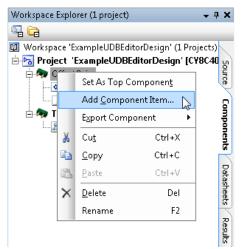

3. Right-click on the project or component, and select Add Component Item...

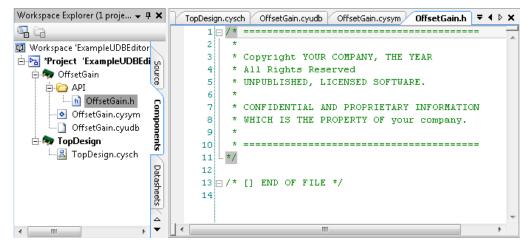

**Note** If you add a component item to a Project, you will create a new component; if you add the item to an existing component, the component item will inherit properties from that component.

4. On the Add Component Item dialog, select the UDB document template under the Implementation

#### category.

| 🖃 Symbol                                        |                               |                          |  |

|-------------------------------------------------|-------------------------------|--------------------------|--|

| 🔯 Empty Symbol                                  | Creates a blank               | symbol.                  |  |

| 🔯 Symbol Wizard                                 | Creates a symbo               | ol using a wizard.       |  |

| Implementation                                  |                               |                          |  |

| 🛃 Schematic                                     | Creates a blank               | schematic.               |  |

| Schematic Macro Creates a blank Schematic Macro |                               |                          |  |

| 🤯 UDB document                                  | Creates a new fi<br>elements. | le to add/configure UDB  |  |

| 📝 Target generic device                         | Component name:               | component01              |  |

|                                                 | ] Item name:                  | component01.cyudb        |  |

| Architecture:                                   |                               | Both (Debug/Release)     |  |

| Architecture:                                   | Configuration:                | ( sear ( searght search) |  |

**Note** For a new component, enter a **Component name**. If desired, you can also specify target options by unselecting **Target generic device** and choosing a specific **Architecture**, **Family**, and/or **Device**.

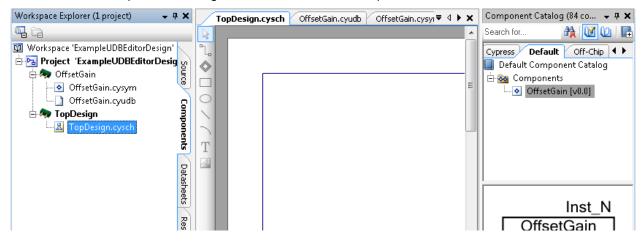

5. Click **Create New** and PSoC Creator opens the UDB Editor.

## **UDB Editor Elements**

UDB Editor elements are the graphical versions of UDB elements. These are available to drag and drop from the Design Elements Palette. They include:

- Datapath (DP)

- Control Register (CR)

- Status Register (SR)

- Status Interrupt Register (SI)

- Count7 counter (C7)

- <u>State Machine (SM)</u>

When placed on the design canvas, an element becomes an instance in your design. Each of these elements/instances is described in the following sections.

### Datapath

The following shows an instance of a Datapath element in the design canvas of the UDB Editor. It contains six inputs and six outputs shown in blue, six registers shown in purple, and eight instructions shown in green.

| Datapatl | h_1 (Width=8) |               |              |                                                                                           |                      |

|----------|---------------|---------------|--------------|-------------------------------------------------------------------------------------------|----------------------|

|          | 0.1           | -             | Inst.        | 1                                                                                         | <u> </u>             |

| In.      | Selection     | Expression    | Addr.        | Instruction                                                                               | Comment              |

| 0        | INSTR_ADDR[0] | 1'b0          | 3'b000       | ALUout=(A0)                                                                               |                      |

| 1        | INSTR_ADDR[1] | 1'b0          |              |                                                                                           |                      |

| 2        | INSTR_ADDR[2] | 1'b0          | 2%001        |                                                                                           |                      |

| 3        |               |               | З'ЬОО1       | ALUout=(A0)                                                                               |                      |

| 4        |               |               |              |                                                                                           |                      |

| 5        |               |               | 3'b010       | ALUout=(A0)                                                                               |                      |

| Reg.     | Load          | Initial Value |              |                                                                                           |                      |

| A0       | Not supported | 8'h00         | 3'b011       | ALUout=(A0)                                                                               |                      |

| A1       | Not supported | 8'h00         |              |                                                                                           |                      |

| D0       | Unused        | 8'h00         | 3'b100       | ALUout=(A0)                                                                               |                      |

| D1       | Unused        | 8'h00         |              |                                                                                           |                      |

| F0       | Unused        | Not supported | 3'b101       | ALUout=(A0)                                                                               |                      |

| F1       | Unused        | Not supported |              |                                                                                           |                      |

| Out.     | Selection     | Name          | 3'b110       | ALUout=(A0)                                                                               |                      |

| 0        |               |               |              |                                                                                           |                      |

| 1        |               |               | 3'b111       | ALUout=(A0)                                                                               |                      |

|          |               |               |              |                                                                                           |                      |

| 2        |               |               | In.          | Datapath inputs: 6 signals that control data selection, shift in, and register loads.     | path instruction     |

| 3        |               |               | Reg.         | Datapath registers: 2 accumulators, 2 data<br>FIFOs.                                      | registers, and 2     |

| 4        |               |               | Out.         | Datapath outputs: 6 signals that provide ac<br>the datapath to the rest of the component. | cess to signals from |

| 5        |               |               | Instructions | Datapaths support up to 8 pre-configured i addition and subtraction.                      | nstructions, like    |

Each UDB block contains an 8-bit Datapath; therefore, chaining these or using multiple Datapaths consumes multiple UDB blocks. Designing with the UDB Editor allows the chaining of these Datapaths to be done automatically, so you do not need to do anything special beyond selecting the datawidth.

When using the UDB Editor, the input/output direction of the FIFO is automatically detected based on the Datapath input configuration. If one of the inputs is set as a load trigger for a FIFO, then that FIFO will be configured as output. Otherwise, it is set to input.

Of the six available input bits, up to three bits can be used to control the Datapath instructions for that clock cycle. If not all three instruction bits are driven, then those instruction bits that are not used will be driven with 1'b0. Note that in this case, not all of the eight available instructions will be usable. For more information on the available instructions, see <u>Datapath Instructions</u>.

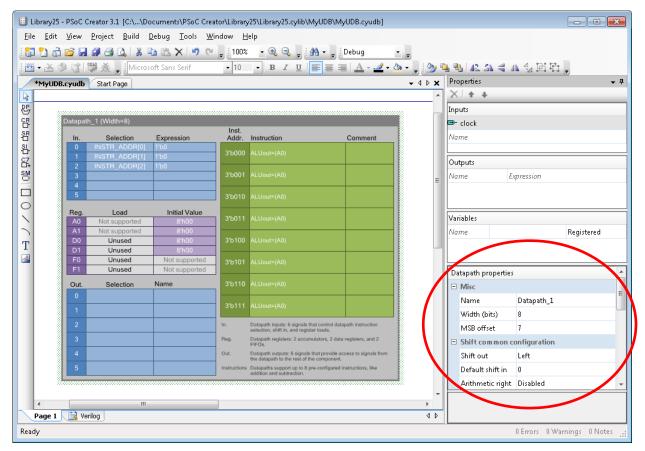

### Datapath Properties

Clicking on the Datapath will also show the Datapath properties in the UDB Editor window. This allows the global Datapath settings to be specified.

Datapath properties globally affect the selected Datapath instance. These include the bit width size of the Datapath, its shift configurations, compare operation configurations, mask definitions and FIFO modes. Once these are set, all the specific properties of the Datapath follow these global settings. The Datapath properties appear in the Properties panel. The configuration properties available include:

| Category                      | Property         | Description                                                                                                                                                                                                                     |

|-------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Misc                          | Name             | Instance name of the Datapath.                                                                                                                                                                                                  |

|                               | Width (bits)     | The bit width of the Datapath (8/16/24/32).                                                                                                                                                                                     |

|                               | MSB offset       | Selects the most significant bit in the Datapath. Used in functions that utilize words that are not multiples of 8. This only impacts Carry Out and Shift Out.                                                                  |

| Shift Common<br>Configuration | Shift out        | Selects whether shift out left or shift out right is routed to the dedicated shift out output (not one of the 6 configurable outputs).                                                                                          |

|                               | Default shift in | Determines the value shifted in when Default is chosen as the Shift source in the Shift Configuration A/B.                                                                                                                      |

|                               | Arithmetic right | Enables arithmetic right shifting when a right shift is selected / used (the value shifted into the MSb is maintained. That is, 1000000 shifted to the right by 1 bit would become 1100000, and 0111111 would become 00111111). |

| Shift                         | Shift direction  | Chooses the direction in which the shift will occur.                                                                                                                                                                            |

| Category                             | Property          | Description                                                                                                                                                                                                   |

|--------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration<br>A/B                 | Shift in source   | Chooses whether to use the dedicated route Shift-in or Default Shift-in expression.                                                                                                                           |

| Configurable<br>comparator<br>inputs | Config A          | Selects the type of comparison to be made if Compare Config A is selected in an instruction. This comparison is made by comparator 1 at each instruction cycle. Compare operations are $A == B$ and $A < B$ . |

|                                      | Config B          | Selects the type of comparison to be made if Compare Config B is selected in an instruction. This comparison is made by comparator 1 at each instruction cycle. Compare operations are $A == B$ and $A < B$ . |

| Masks                                | amask             | Mask value that is applied to the output of the ALU. The mask is used only if amask check box is checked. When enabled, the output of the ALU is <b>always</b> ANDed with the mask value.                     |

|                                      | cmask0            | Mask value that is applied to the A (first) input of the comparator. The mask is ANDed with the register then compared. The mask is always applied when checked.                                              |

|                                      | cmask1            | Mask value that is applied to the A (first) input of the comparator, the mask is ANDed with the register then compared. The mask is always applied when checked.                                              |

| FIFOs                                | FIFO sync<br>mode | Determines how the FIFO block status signal is synchronized to the datapath clock.                                                                                                                            |

|                                      | Capture mode      | Specifies whether a read from the accumulator registers is direct or if it also triggers a capture into the FIFOs.                                                                                            |

|                                      | Edge mode         | Specifies whether a FIFO write trigger is level sensitive or rising edge sensitive.                                                                                                                           |

|                                      | Fast mode         | Specifies the clocking source for the FIFO capture. Can be captured using the Datapath clock or can use the bus clock for a faster performance.                                                               |

### Datapath Inputs

Double-clicking on any of the input fields in the Datapath will open the Configure Datapath Inputs dialog for specific configuration of each input.

| In.        |            | ection<br>ADDR[0] | Expression      | Inst.<br>Addr. | Instruction                                  | Comment                                                              |

|------------|------------|-------------------|-----------------|----------------|----------------------------------------------|----------------------------------------------------------------------|

| 1          |            |                   | 1'60            | 3'b000         | ALUout=(A0)                                  |                                                                      |

| 2          | INSTE      |                   | Datapath Inputs |                |                                              | ?                                                                    |

| 4          |            |                   | Selection:      |                |                                              | Expression:                                                          |

| 5          |            | Input 0:          | INSTR_ADDI      | R[0]           | •                                            | 1'60                                                                 |

| Reg.<br>A0 | Not s      | Input 1:          | INSTR_ADDI      | R[1]           | •                                            | 1њ0                                                                  |

| A1<br>D0   | Not s<br>U | Input 2:          | INSTR_ADDI      | R[2]           | •                                            | 1њ0                                                                  |

| D1<br>F0   | U          | Input 3:          | None            |                | •                                            |                                                                      |

| F1         | U          | Input 4:          | None            |                | •                                            |                                                                      |

| Out.       | S€         | Input 5:          | None            |                | •                                            |                                                                      |

| 1          |            |                   |                 |                |                                              | OK Cancel                                                            |

| 2          |            |                   |                 |                |                                              |                                                                      |

| 3          | L          |                   |                 | Heg.           | Datapath registers: 2<br>FIFOs.              | accumulators, 2 data registers, and 2                                |

| 4          |            |                   |                 | Out.           |                                              | signals that provide access to signals from<br>est of the component. |

| 5          |            |                   |                 | Instructions   | Datapaths support u<br>addition and subtract | p to 8 pre-configured instructions, like                             |

Datapath inputs can be used to: control the execution of the instructions, control the loading of the FIFOs/Data/Accumulator registers, or route in a value for the shift in from the DSI. The inputs are also used to define the serial input into the shifter and for controlling the state of the instructions in the Datapath. The following are the available inputs from the UDB Editor.

| Selection           | Name                                                                                                      |

|---------------------|-----------------------------------------------------------------------------------------------------------|

| INSTR_ADDR[0]       | LSB of the instruction select bits                                                                        |

| INSTR_ADDR[1]       | Middle bit of the instruction select bits                                                                 |

| INSTR_ADDR[2]       | MSB of the instruction select bits                                                                        |

| Load D0 with F0     | Loads the first element of F0 in D0 at the rising edge of the clock                                       |

| Load D1 with F1     | Loads the first element of F1 in D1 at the rising edge of the clock                                       |

| Load F0 with A0     | Loads the content of A0 to F0 at the rising edge of the clock                                             |

| Load F0 with A1     | Loads the content of A1 to F1 at the rising edge of the clock                                             |

| Load F0 with ALUout | Loads the content of ALU output to F0 at the rising edge of the clock                                     |

| Load F1 with A0     | Loads the content of A0 to F0 at the rising edge of the clock                                             |

| Load F1 with A1     | Loads the content of A1 to F1 at the rising edge of the clock                                             |

| Load F1 with ALUout | Loads the content of ALU output to F1 at the rising edge of the clock                                     |

| Shift In            | The expression to use when 'Routed Shift-in' is selected as the shift source for Shift Configuration A/B. |

Of the six available inputs, up to three inputs can be used to define which Datapath instruction will be executed. The instruction input is not synchronized to the Datapath clock, it is combinatorial and the Datapath will immediately execute whatever instruction is selected on the Datapath instruction line. These are shown by default in the inputs section: INSTR\_ADDR[2:0]. The expressions for these inputs default to 1'b0 (logic low). For each instruction bit that is used, generally the expression for that bit will correspond to a signal being driven by a separate state machine placed into the UDB Editor document.

For example, a variable named myInstr[1:0] in a State Machine is being assigned various values to control the instructions in the Datapath. Then INSTR\_ADDR[1] and INSTR\_ADDR[0] should assign myInstr[1] and myInstr[0] respectively in its expression fields. Similarly if a "Load F0 with A0" signal is used in the Datapath and the signal used to control this is called loadF0, then loadF0 should be placed in the expression field next to the "Load F0 with A0" input. For more information, see <u>State Machine</u>.

#### Datapath Registers

| atapat | h_1 (Width=8) |       |        |        |                |                                                     |                            |                                          |

|--------|---------------|-------|--------|--------|----------------|-----------------------------------------------------|----------------------------|------------------------------------------|

| In.    | Selection     | Expre | ession |        | Inst.<br>Addr. | Instruction                                         |                            | Comment                                  |

| 0      | INSTR_ADDR[0] | 1'b0  |        |        | 3'b000         | ALUout=(A0)                                         |                            |                                          |

| 1      | INSTR_ADDR[1] | 1'b0  |        |        | 3 0000         | ALUOU(=(AU)                                         |                            |                                          |

| 2      | INSTR_ADDR[2] | 1'b0  |        |        |                |                                                     |                            |                                          |

| 3      |               |       | Config | jure D | atapath R      | egisters                                            |                            | ? <mark>-</mark> >                       |

| 5      |               |       |        | Load:  |                | -                                                   | 1                          | al value:                                |

|        |               |       |        | Load   |                |                                                     | Inia                       |                                          |

| Reg.   | Load          | In    | A0:    | Not    | supported      |                                                     |                            | 8'h00                                    |

| A0     | Not supported |       | A1:    | bl-s   |                |                                                     | _                          | 8'h00                                    |

| A1     | Not supported |       | AL.    | INOL   | supported      |                                                     |                            | onuu                                     |

| D0     | Unused        |       | D0:    | Unu    | sed            |                                                     |                            | 8'h00                                    |

| D1     | Unused        |       |        |        |                |                                                     |                            |                                          |

| F0     | Unused        | No    | D1:    | Unu    | sed            |                                                     |                            | 8'h00                                    |

| F1     | Unused        | No    | FO:    |        |                |                                                     | _                          |                                          |

| Out.   | Selection     | Name  |        | Unu    |                |                                                     |                            | Not supported                            |

| 0      |               |       | F1:    | Unu    | sed            |                                                     |                            | Not supported                            |

| 1      |               |       |        |        |                |                                                     | 0K                         |                                          |

| 2      |               |       |        |        |                |                                                     | ОК                         | Cancel                                   |

| 3      |               |       |        |        |                | FIFUS.                                              | _                          |                                          |

| 4      |               |       |        |        | Out.           |                                                     | nals that pr<br>of the com | rovide access to signals from<br>ponent. |

| 5      |               |       |        |        | Instructions   | Datapaths support up to<br>addition and subtraction | 8 pre-con                  |                                          |

Double-clicking on any of the registers fields will open the Configure Datapath Registers dialog.

This dialog is used to set the initial values of the registers at start-up of the PSoC during boot initialization. If the register does not support an initial value in its current configuration, then it will be grayed out. For reference, the load expression (if any) is shown for each register. This is a read-only display; load expressions must be edited via the Configure Datapath Inputs dialog. For more information, see <u>Datapath Inputs</u>. See also <u>Datapath Registers</u>.

### Datapath Outputs

Double-clicking on any of the output fields in the Datapath will open the Configure Datapath Outputs dialog for specific configuration of each output.

|      |    |               |               | Inst. |                                                                           |                              |

|------|----|---------------|---------------|-------|---------------------------------------------------------------------------|------------------------------|

| In.  | IN | Configure Dat | apath Outputs |       |                                                                           | ? -                          |

| 1    | IN |               |               |       |                                                                           |                              |

| 2    | IN |               | Selection:    |       |                                                                           | Name:                        |

| 3    |    | Output 0:     | None          |       | •                                                                         |                              |

| 4    |    |               |               |       |                                                                           |                              |

| 5    |    | Output 1:     | None          |       | •                                                                         |                              |

| Reg. |    | Output 2:     | None          |       | •                                                                         |                              |

| A0   | N  | output 2.     | None          |       | •                                                                         |                              |

| A1   | N  | Output 3:     | None          |       | •                                                                         |                              |

| D0   |    |               |               |       |                                                                           |                              |

| D1   |    | Output 4:     | None          |       | •                                                                         |                              |

| F0   |    | Output 5:     | None          |       | •                                                                         |                              |

| F1   |    | output 5.     | NONE          |       | •                                                                         |                              |

| Dut. |    |               |               |       |                                                                           |                              |

| 0    |    |               |               |       | OK                                                                        | Cancel                       |

| 1    |    |               |               |       |                                                                           |                              |

|      |    |               |               |       |                                                                           |                              |

| 2    |    |               | In.           |       | Datapath inputs: 6 signals that c<br>selection, shift in, and register lo |                              |

| 3    |    |               | Re            |       | Datapath registers: 2 accumulat<br>FIFOs.                                 | ors, 2 data registers, and 2 |

| 4    |    |               | Ou            |       | Datapath outputs: 6 signals that<br>the datapath to the rest of the co    |                              |

| 5    |    |               | Ins           |       | Datapaths support up to 8 pre-co<br>addition and subtraction.             | onfigured instructions, like |

Datapath outputs include various comparator status values, FIFO status values, shift output, and various overflows. The following is a list of available outputs from the UDB Editor.

| Selection                                      | Name                                                                                       |

|------------------------------------------------|--------------------------------------------------------------------------------------------|

| A0 == D0                                       | Status of A0 equals D0 performed by comparator 0                                           |

| A0 < D0                                        | Status of A0 less than D0 performed by comparator 0                                        |

| A0 == 0                                        | A0 equal to 0 comparison.                                                                  |

| A0 == 0xFF                                     | A0 equal to 0xFF comparison.                                                               |

| Config A: "equal"<br>Config B: "equal"         | Status for equality comparison for comparator 1.                                           |

| Config A: "less than"<br>Config B: "less than" | Status for less than comparison for comparator 1.                                          |

| A1 == 0                                        | A1 equal to 0 comparison.                                                                  |

| A1 == 0xFF                                     | A1 equal to 0xFF comparison.                                                               |

| Overflow                                       | This is used to monitor whether an overflow has occurred in the most recent ALU operation. |

| Carry out                                      | Carry out of the ALU arithmetic operation                                                  |

| CRC MSB                                        | CRC feedback out                                                                           |

| Selection                   | Name                                                                                                                         |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Shift out                   | Shift out bit. This can be either shift out left or shift out right. This is the option selected in the Datapath Properties. |

| F0 bus status (not full)    | FIFO 0 bus status used to flag whether the FIFO 0 is full or not.                                                            |

| F0 block status (not empty) | FIFO 0 block status to flag whether FIFO 0 is empty.                                                                         |

| F1 bus status (not full)    | FIFO 1 bus status used to flag whether the FIFO 1 is full or not.                                                            |

| F1 block status (not empty) | FIFO 1 block status to flag whether FIFO 1 is empty.                                                                         |

Note For more information about F0 and F1 bus/clock status, refer to Appendix A: Datapath Operation.

Outputs from the Datapath can be used in a State Machine to control transitions (for example, to change the instruction code for the next cycle) or can be directly linked to the output terminal to be used by other hardware blocks (for example DMA or an interrupt). These signals can also be routed internally to other hardware blocks such as another Datapath, a Status Register, or a Count7 counter. For more information on how a State Machine interacts with a Datapath, see <u>Controlling Datapath Instructions</u>.

Note A maximum of six outputs are available per Datapath.

#### Datapath Instructions

Individual configurations for the eight available Datapath instructions can be set by double-clicking each specific instruction field to open the Configure Instruction dialog.

| ln.  | Selecti                   | on     | Expression         | Inst.<br>Addr. | Instr | ruction          | Comment |

|------|---------------------------|--------|--------------------|----------------|-------|------------------|---------|

| 0    | INSTR_AD                  |        | 1'b0<br>1'b0       | З'ЬООО         | ALU   |                  |         |

| Conf | figure Instru             |        |                    |                |       |                  |         |

| Co   | mment:                    | 1      |                    |                |       |                  |         |

|      |                           |        |                    |                |       | De sister unites |         |

|      | LU operation<br>Junction: |        |                    |                |       | Register writes  |         |

| F    | unction:                  | A0     | ▼ No-op            |                |       | No-op            | •       |

| S    | ihift:                    | No-op  |                    |                | •     | No-op            | •       |

| A    | LU_out:                   | (A0)   |                    |                |       |                  |         |

| - C  | ompare optio              | ns     |                    |                |       |                  |         |

| 0    | )ption 0:                 | A0 con | npare to D0        |                |       |                  |         |

| 0    | )ption 1:                 | Config | A: A0 compare to D | 1              |       |                  | •       |

|      |                           |        |                    |                |       |                  |         |

|      |                           |        |                    |                |       |                  |         |

|      |                           |        |                    |                |       | ОК               | Cancel  |

Each instruction is divided into three parts: ALU operation, Register Writes, and Compare options. For a full list of operations, see <u>Datapath Instructions</u>.

The ALU operation determines what arithmetic or Boolean operation is performed for that instruction cycle.

- The ALU accepts data from two register sources and performs a function on them. The first input (A) is limited to either A0 or A1 whereas the second input (B) can also accept D0, D1 and can internally provide a 1 as an input. The result is then passed to ALUout.

- ALUout can be shifted by 1 bit before being placed at the output. Specify the shift operation if the result should be shifted by a single bit. The shift properties are controlled by the global shift configuration in the Datapath properties window.

- □ The expression for ALUout will be shown once you've completed the function and shift definitions. Use this to check whether the ALU operation is correct.

- Register Writes are used to load A0 and A1 with values for the next Datapath clock cycle. These can be used as a feedback from ALUout or to accept new data from the data register or the FIFO.

- □ A0 can either be left as it is, or can be over written by D0 or F0. It can also be over written with ALUout to form a feedback.

- □ Similarly, A1 can either be left as it is, or can be over written by D1 or F1. It can also be over written with ALUout to form a feedback.

- □ If ALUout is not assigned to any registers after an instruction cycle, the result will be overwritten by the result of the next instruction. Therefore it is advised that ALUout be written to either of the accumulators or loaded to a FIFO through the "load FIFO" signals in the Datapath inputs section.

- Compare Options are used to set the comparisons being made using comparator 0 and comparator1. Comparator 0 is always set to compare A0 with D0, and this is shown in option 0. Comparator 1 on the other hand is chosen by specifying whether to use Config A or Config B specified in the Configurable comparator inputs properties located in the Datapath properties window. The status of these comparisons can then be determined by monitoring the comparator outputs in the Datapath output.

### **Control Register**

The following shows an instance of a Control Register element in the design canvas of the UDB Editor.

| Bit | Name   | Init. Val. | Mode |

|-----|--------|------------|------|

| 0   | ctrl_0 | 1'b0       | Sync |

| 1   | ctrl_1 | 1'b0       | Sync |

| 2   | ctrl_2 | 1'b0       | Sync |

| 3   | ctrl_3 | 1'b0       | Sync |

| 4   | ctrl_4 | 1'b0       | Sync |

| 5   | ctrl_5 | 1'b0       | Sync |

| 6   | ctrl_6 | 1'b0       | Sync |

| 7   | ctrl_7 | 1'b0       | Sync |

Control Registers are used by the CPU to send commands to the digital logic. Each Control Register has eight available bits that can be used throughout the design to control the various aspects of the component operation.

Double-click on the instance to open the Configure Control Register dialog.

| C | CtrlReg  | 1_1          |                |      |         |

|---|----------|--------------|----------------|------|---------|

|   | Bit<br>0 | Configure Co | ntrol Register |      | ? 🗙     |

|   | 1        | Name:        | CtrlReg_1      |      |         |

|   | 3        | Nam          |                | Init | Mode    |

|   | 5        | ▶ 0 ctrl_(   |                | 0    | Sync    |

|   | 6        | 1 ctrl_      | 1              | 0    | Sync    |

|   |          | 2 ctrl_      | 2              | 0    | Sync    |

|   |          | 3 ctrl_      | 3              | 0    | Sync    |

|   |          | 4 ctrl_      | 4              | 0    | Sync    |

|   |          | 5 ctrl_      | 5              | 0    | Sync    |

|   |          | 6 ctrl_      | 6              | 0    | Sync    |

|   |          | 7 ctrl_      | 7              | 0    | Sync    |

|   |          |              |                |      |         |

|   |          | + ×          | +              |      |         |

|   |          |              | ОК             |      | Cancel  |

|   |          |              |                |      | 03.1301 |

A Control Register has a name for each of the bits. These are the signal names that can be used throughout the design. It also has initial values that can be set to either 1'b1 or 1'b0. These values are set during device start-up and will be lost if the device goes to sleep / hibernate. The mode of each of the bits in the Control Register can be set to Direct, Sync or Pulse. The clock used for the Sync and Pulse modes is the component clock. Refer to the Control Register component datasheet (from the separate Control Register component in the PSoC Creator Component Catalog) and the *TRM* for more information.

#### **Status Register**

The following shows an instance of a Status Register element in the design canvas of the UDB Editor.

| Bit | Expression | Mode   |

|-----|------------|--------|

| 0   | 1'b0       | Sticky |

| 1   | 1'b0       | Sticky |

| 2   | 1'b0       | Sticky |

| 3   | 1'b0       | Sticky |

| 4   | 1'b0       | Sticky |

| 5   | 1'b0       | Sticky |

| 6   | 1'b0       | Sticky |

| 7   | 1'b0       | Sticky |

Status Registers are used by the CPU to read hardware signals. Eight bits are available in a single Status Register and allows signals from the component to be seen by the CPU.

Double-click on the instance to open the Configure Status Register dialog.

| StatusReg<br>Bit E                   | _1                   | Mada        |                        |

|--------------------------------------|----------------------|-------------|------------------------|

|                                      | Configure Status Reg | gister      | ? 💌                    |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Register name:       | StatusReg_1 |                        |

| 4                                    | Expression           |             | Mode                   |

| 5                                    | 0 1'b0               |             | Sticky (clear on read) |

|                                      | 1 1'b0               |             | Sticky (clear on read) |

|                                      | 2 1'b0               |             | Sticky (clear on read) |

|                                      | 3 1'b0               |             | Sticky (clear on read) |

|                                      | 4 1'b0               |             | Sticky (clear on read) |

|                                      | 5 1'b0               |             | Sticky (clear on read) |

|                                      | 6 1'b0               |             | Sticky (clear on read) |

|                                      | 7 1'b0               |             | Sticky (clear on read) |

|                                      |                      |             |                        |

|                                      | + × +                | +           |                        |

|                                      |                      | (           | OK Cancel              |

The expression field of the Status Register bits allows several signals to go through PLD logic to form one signal before being placed in the register. This allows for some usage of PLDs without the use of State Machines. For example, two signals from the Datapath output called "lessComp0" and "equalComp0" may be combined together at the status expression field as "lessComp0 | equalComp0". Note that the expressions follow the Verilog syntax. The mode of the status bits can be set to either Transparent or Sticky. Status registers in the UDB Editor are always clocked at bus clock. Refer to the Status Register component datasheet (from the separate Status Register component in the PSoC Creator Component Catalog) and the *TRM* for more information.

### Status Interrupt Register

The following shows an instance of a Status Interrupt Register element in the design canvas of the UDB Editor. This element consumes the same resources as a Status Register.

| Statusl | ntReg_1    |                    |      |

|---------|------------|--------------------|------|

| Bit     | Expression | Mode               | Mask |

| 0       | 1'b0       | Sticky             | 1    |

| 1       | 1'b0       | Sticky             | 1    |

| 2       | 1'b0       | Sticky             | 1    |

| 3       | 1'b0       | Sticky             | 1    |

| 4       | 1'b0       | Sticky             | 1    |

| 5       | 1'b0       | Sticky             | 1    |

| 6       | 1'b0       | Sticky             | 1    |

| Outpu   | ut N       | lame               |      |

| Intern  | upt S      | StatusIntReg_1_int |      |

|         |            |                    |      |

Status Interrupt Registers are used to generate a maskable interrupt from the status bits. Seven bits are used as the inputs and one bit is used as the interrupt output.

Double-click on the instance to open the Configure Status Reg. with Interrupt dialog.

| Bit         | Configure Status Re | g. with Interrupt |           | ?      |

|-------------|---------------------|-------------------|-----------|--------|

| 1<br>2<br>3 | Register name:      | <b>p</b> tatusInt | Reg_1     |        |

| 4           | Interrupt name:     | StatusInt         | Reg_1_int |        |

| 5           | Expression          | 1                 | Mode      | Mask   |

| Outpu       | 0 1'b0              |                   | Sticky    | 1      |

| Interru     | 1 1'b0              |                   | Sticky    | 1      |

|             | 2 1'b0              |                   | Sticky    | 1      |

|             | 3 1'b0              |                   | Sticky    | 1      |

|             | 4 1'b0              |                   | Sticky    | 1      |

|             | 5 1'b0              |                   | Sticky    | 1      |

|             | 6 1'b0              |                   | Sticky    | 1      |

|             | <b>₽</b> ו          | ] 🔹               | ОК        | Cancel |

Like the Status Register, each bit has an expression field that can be used to form logic for that bit. The mode of the bits can be set to either Transparent or Sticky. The mask field determines whether that bit should be masked to generate the interrupt.

**Note** Only one interrupt per instance can be used when using the Status Interrupt Register. Refer to the Status Register component datasheet and the *TRM* for more information.

### **Count7 Counter**

The following shows an instance of a Count7 counter element in the design canvas of the UDB Editor. This element consumes the same resources as a Control Register.

| Count7_1       |             |

|----------------|-------------|

| Input          | Expression  |

| Reset          | 1'b0        |

| Enable         | 1'b1        |

| Load           | 1'b0        |

| Register       | Value       |

| Period         | 7'h7F       |

| Output         | Name        |

| Terminal Count | Count7_1_tc |

|                |             |

The Count7 counter is a 7-bit down counter that should be used when a counter of up to seven bits is needed. It can be more efficient to use PLD logic for counters of less than 3 bits. This gives savings compared to PLDs or Datapath-based counter designs.

Double-click on the instance to open the Configure Count7 dialog.

| Count7                | _1              |             |

|-----------------------|-----------------|-------------|

| Input<br>Rese         | Configure Count | 3 ? 💌       |

| Enab<br>Load<br>Regis | Name:           | þount7_1    |

| Perio                 | Inputs          |             |

| Outpu                 | Reset:          | 1'60        |

| Termi                 | Enable:         | 1'61        |

|                       | Load:           | 1'60        |

|                       | Period:         | 7'h7F       |

|                       | Terminal count: | Count7_1_to |

|                       |                 | OK Cancel   |

The Count7 counter has three inputs: Reset, Enable, and Load. These are used to reset the counter, enable the counter, and to load the counter with the period value during counter operation. The period value is set to 7'h7F by default. The counter has one output called terminal count, and this is driven high when the counter reaches 0. The counter is driven by the component clock. Refer to the Counter component datasheet and the *TRM* for more information.

#### **State Machine**

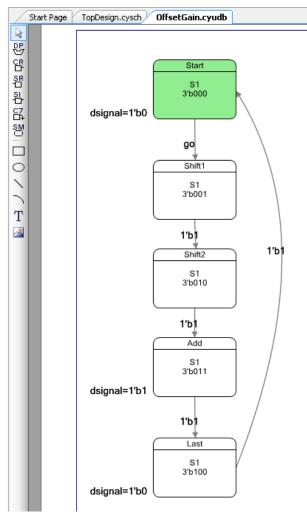

A State Machine contains one or more states that implement control logic using PLDs. A State Machine is used to send control signals to the UDB elements in your design and to keep track of the operations happening in your hardware. Once a condition is achieved, the State Machine will transition to another state.

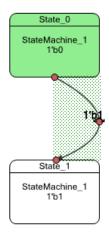

The following shows an instance of a State Machine element in the design canvas of the UDB Editor.

| $\square$ | State_0                      |  |

|-----------|------------------------------|--|

|           | <unknown><br/>1'b0</unknown> |  |

Double-click on the instance to open the Configure State dialog.

| State  | settings                 |                                                           | Is start state                               |                      |

|--------|--------------------------|-----------------------------------------------------------|----------------------------------------------|----------------------|

| Name   | e: Btate                 | _0                                                        | Machine name:                                |                      |

| Enco   | ding: 1'ЬО               |                                                           | Reset condition:                             |                      |

|        | ien die nigher phony     | rransition will be preferred.                             |                                              |                      |

|        | ble assignments:         | ✓ Display on sheet.                                       | Outbound transition prio                     | rity order:          |

|        |                          | · · · · · · · · · · · · · · · · · · ·                     | Outbound transition prio<br>Transition Expr. | rity order:<br>State |

| Variat | ble assignments:         | ✓ Display on sheet.                                       | · · ·                                        | -                    |

| Variat | ble assignments:<br>Name | <ul> <li>Display on sheet.</li> <li>Expression</li> </ul> | · · ·                                        | -                    |

This dialog contains four sections: **State settings**, **Is start state** settings, **Variable assignments**, and **Outbound transition priority order**. Depending on the state operation and type, it may not be necessary to define all sections.

- State settings specify the Name of the state and its corresponding Encoding state value. Each state within the current State Machine must have unique Name and Encoding values. These should correspond to a specific operation performed by the target block(s). Therefore the generated control signals in a state should be unique.

- A state can be a starting state or some other state in the State Machine. Every State Machine requires a starting state, and there can only be one starting state with a State Machine.

- Select the **Is start state** box to turn a State Machine instance into a start state. This changes the instance color from white to green and sets the encoding to zero (this is the reset state). The State Machine will be reset to this state when returning from sleep / hibernate.

- Define a unique Machine name and its Reset condition. In most cases the reset would be triggered using a "not enable" or a separate "reset" input signal. The Reset condition allows all states in a State Machine to transition back to the start state upon reaching a reset condition.

- Variable assignments are used to define variables that are internal to the State Machine. They can then be used to control other elements, such as a Datapath or a Count7 counter in the UDB design.

- □ A variable can be read from anywhere in the UDB Editor design, but it may only be *written* from within one State Machine.

- □ Design-wide variables and outputs may not be *written* from within a State Machine, but they may derive their value from a State Machine variable.

- Outbound transition expressions can be used to set the priority of transitions in cases where more than

one condition is true. This field will be populated as transitions are added to the state (see the <u>State</u>

<u>Machine Transitions</u> section).

- □ Moving a transition expression higher in the order gives it higher priority over those below.

- □ However, it is generally a good practice to make transition expressions mutually exclusive.

#### State Machine Transitions

To add a transition from one State Machine instance to another:

- 1. Configure the first instance as a start state.

- 2. Hover the mouse on the edge of the start State Machine instance to show the anchor points.

- 3. Then, click the mouse and drag from one state to the edge of another.

- 4. Release the mouse button and the Configure Transition dialog opens.

| State_0<br>StateMachine_1<br>1'b0       | State_0<br>StateMach<br>1'b0 |          |      | Fransitio<br>1: | т<br>1'Б1 |                  | ? 💌    |

|-----------------------------------------|------------------------------|----------|------|-----------------|-----------|------------------|--------|

| 1'b1                                    |                              |          | Na   | ame             |           | Expression       |        |

|                                         | 1'b]                         | *        | 0 En | iter nan        | ne        | Enter expression |        |

| State_1<br><unknown><br/>1'b1</unknown> | State<br>StateMact<br>1'b1   | l        |      |                 |           |                  |        |

|                                         |                              | <b>+</b> | ×    | <               | •         | ОК               | Cancel |

In the dialog, use the Expression field to set the transition expression. Whenever this expression is true, the

transition will occur in the State Machine. If more than one transition condition is true, then the higher priority transition will be followed. The Configure Transition dialog also permits assignments to be specified. These are similar to Variable assignments specified in the Configure State dialog, but they only take place when the specific transition is followed, rather than when the state is entered (via any transition).

**Note** Linking a new state to an existing State Machine will cause propagation of the existing State Machine name. The encoding on the other hand must be unique and does not propagate.

To adjust the shape of the transition arc, click and drag the anchor points on the transition to the desired shape.

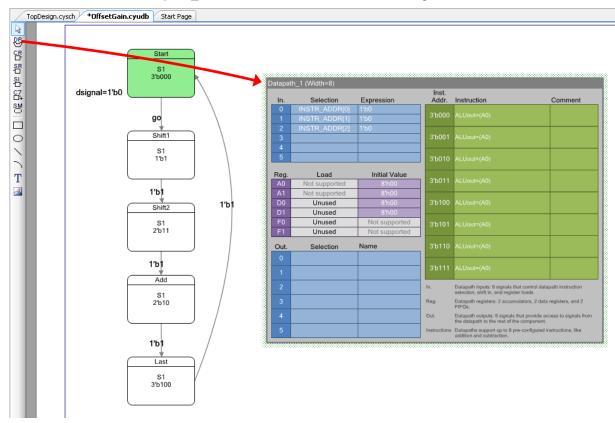

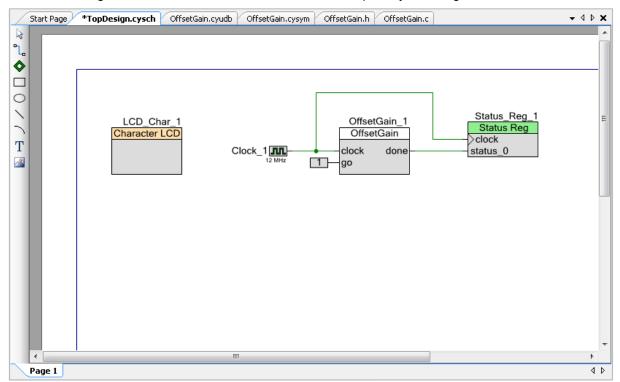

#### Controlling Datapath Instructions

State Machines are often used to control the INSTR\_ADDR bits for the Datapath instructions. These are also referred to as the "dynamic configuration" bits in the *TRM*. They are accessed by mapping signals to the INSTR\_ADDR bits in the inputs section of the Datapath. The following shows how a State Machine controls a Datapath.

| ln.    | Selection                      | Expression                | Inst.<br>Addr. | Instruction                                                                   | Comment                                 |                   |

|--------|--------------------------------|---------------------------|----------------|-------------------------------------------------------------------------------|-----------------------------------------|-------------------|

| 0<br>1 | INSTR_ADDR[0]<br>INSTR_ADDR[1] | StateMachine_1[0]<br>1'b0 | З'ЬООО         | ALUout=(A0 ^ A0)<br>A0=ALUout                                                 | Reset<br>Instruction                    |                   |

| 2<br>3 | INSTR_ADDR[2]                  | 1'b0                      | З'ЬОО1         | ALUout=(A0 + A1)<br>A0=ALUout                                                 | Count<br>Instruction                    | Reset             |

| 4<br>5 |                                |                           | З'Ь010         | ALUout=(A0)                                                                   |                                         | StateMach<br>1'b0 |

| Reg.   | Load                           | Initial Value             | 21-011         | AU 11                                                                         |                                         |                   |

| A0     | Not supported                  | 8'h00                     | 3'6011         | ALUout=(A0)                                                                   |                                         |                   |

| A1     | Not supported                  | 8'h00                     |                |                                                                               |                                         |                   |

| D0     | Unused                         | 8'h00                     | 3'b100         | ALUout=(A0)                                                                   |                                         |                   |

| D1     | Unused                         | 8'h00                     |                |                                                                               |                                         |                   |

| F0     | Unused                         | Not supported             | 3'b101         | ALUout=(A0)                                                                   |                                         | enab              |

| F1     | Unused                         | Not supported             |                |                                                                               |                                         | enab              |

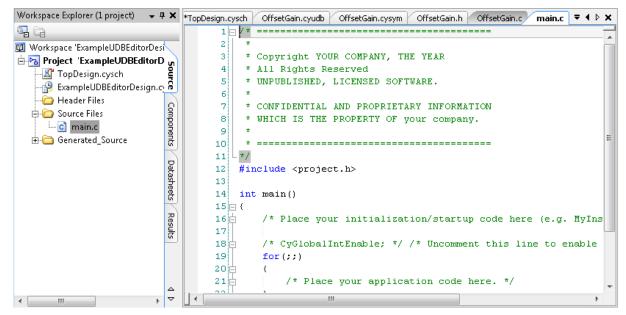

| Dut.   | Selection                      | Name                      | 3'b110         | ALUout=(A0)                                                                   |                                         |                   |