## Customer Training Workshop Traveo™ II Timer/Counter/Pulse-Width Modulator (TCPWM)

#### **Target Products**

> Target product list for this training material:

| Family Category                             | Series            | Code Flash Memory Size |

|---------------------------------------------|-------------------|------------------------|

| Traveo™ II Automotive Body Controller Entry | CYT2B6            | Up to 576 KB           |

| Traveo II Automotive Body Controller Entry  | CYT2B7            | Up to 1088 KB          |

| Traveo II Automotive Body Controller Entry  | CYT2B9            | Up to 2112 KB          |

| Traveo II Automotive Body Controller Entry  | CYT2BL            | Up to 4160 KB          |

| Traveo II Automotive Body Controller High   | CYT3BB/<br>CYT4BB | Up to 4160 KB          |

| Traveo II Automotive Body Controller High   | CYT4BF            | Up to 8384 KB          |

| Traveo II Automotive Cluster                | CYT3DL            | Up to 4160 KB          |

| Traveo II Automotive Cluster                | CYT4DN            | Up to 6336 KB          |

### Introduction to Traveo II Body Controller Entry

#### TCPWM in Traveo II is located in the peripheral blocks. > **Hint Bar CPU Subsystem Review TRM section 4.1** CYT2BL for additional details MXS40-HT SWJ/MTB/CTI SWJ/ETM/ITM/CTI CRYPTO eCT Flash M-DMA0 4 Channel P-DMA1 44 Channel P-DMA0 92 Channel ASIL-B Arm Cortex specific to the CPUSS SRAM0 SRAM1 ROM AES, SHA, CRC, 4160 KB Code-flash + Arm Cortex M4 256 KB 256 KB TRNG, RSA, M0+ 32 KB 128 KB Work-flash 160 MHz ECC 100 MHz 8 KB \$ 8 KB \$ System Resources SRAM Controller SRAM Controller Initiator/MMIO **ROM Controller** FPU, NVIC, MPU MUL, NVIC, MPU FLASH Controller Power 1 1 1 1 1 ſſ ĴĴ ר ר נ Sleep Control POR BOD System Interconnect (Multi Layer AHB, IPC, MPU/SMPU) OVD LVD RÉF 1[ PWRSYS-HT Peripheral Interconnect (MMIO, PPU) LDO PCLK ſ Clock ר Clock Control Prog. 2xILO WDT IMO ECO Analog FLL CSV EVTGEN Event Generator 8x CANFD CAN-FD Interface SAR 7x SCB I2C, SPI, UART 1xPLL 1x SCB I2C, SPI, UART 4x CXPI CXPI Interface ADC 12x LIN LIN/UART eFUSE 1024 bit Reset SSOI (12-bit) Reset Control XRES GPIO Test TestMode Entry x3 Digital DFT Analog DFT SARMUX WCO 64 ch RTC Power Modes High-Speed I/O Matrix, Smart I/O, Boundary Scan Active/Sleep 5x Smart I/O LowePowerActive/Sleep Up to 148x GPIO STD, 4x GPIO ENH DeepSleep I/O Subsystem Hibernate

**Hint Bar**

**Review TRM section 4.1**

for additional details

specific to the CPUSS

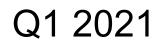

## Introduction to Traveo II Body Controller High

#### > TCPWM in Traveo II is located in the peripheral blocks.

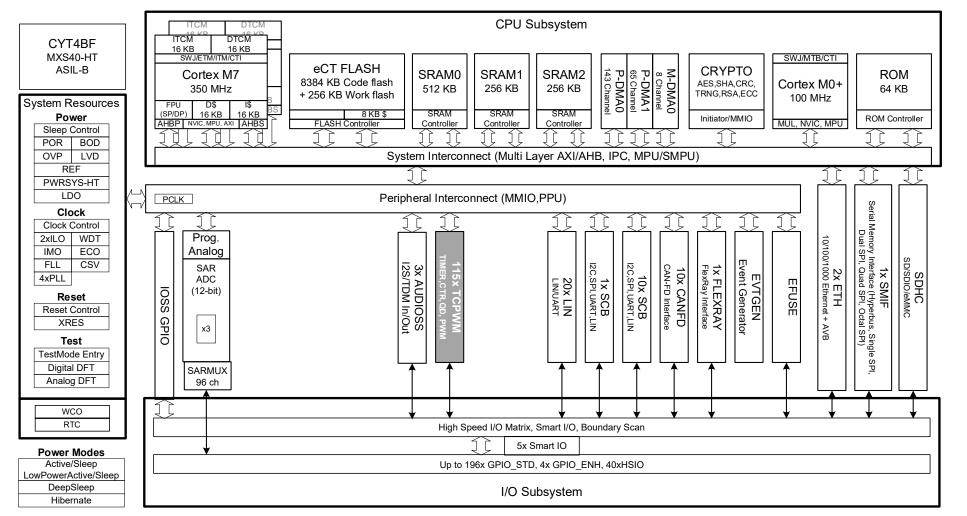

## Introduction to Traveo II Cluster

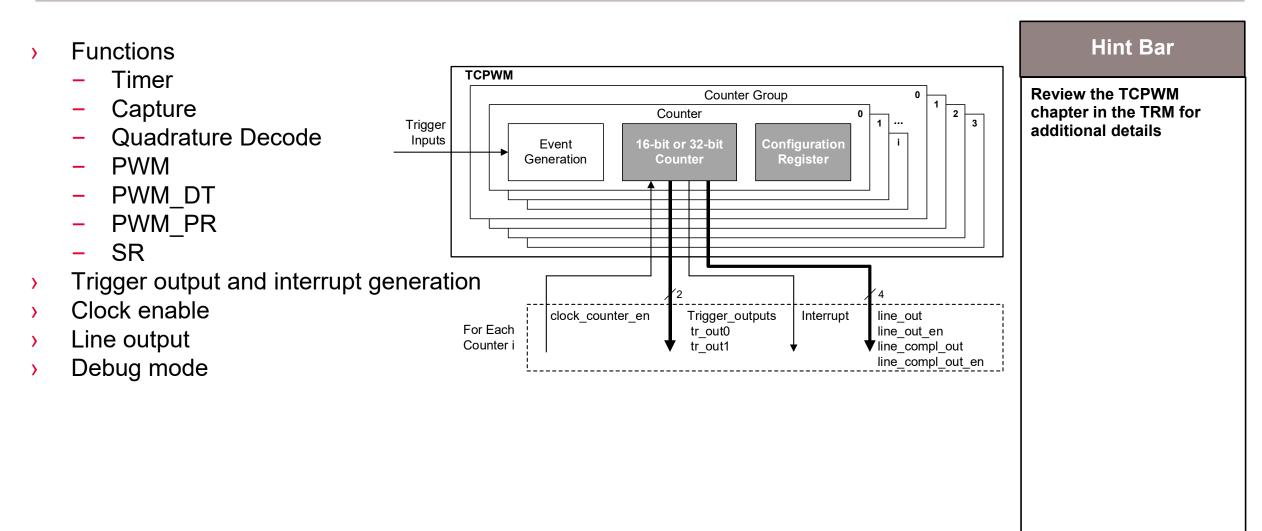

#### **TCPWM** Overview

- The Timer/Counter/Pulse-Width Modulator (TCPWM) block in Traveo II implements the following functionality:

- Timer

- Capture

- Quadrature Decoder

- Pulse-Width Modulation (PWM)

- PWM with Dead Time Insertion (PWM\_DT)

- PWM Pseudo-Random (PWM\_PR)

- Shift Register (SR)

**Hint Bar**

## TCPWM Features (1/2)

- > Counter specification

- Supports up to four counter groups (device-specific1)

- Each counter group consists of up to 256 counters (counter group-specific1)

- > Each counter

- Can run in one of the seven function modes

- Supports various counting modes

- One-shot mode and Continuous mode (Up/Down/Up-down)

- Selects input signals

- Start, Reload, Stop, Count, and two Capture event signals

- Generates output signals

- Two output triggers, PWM output, and interrupt

- Supports debug mode

#### **Hint Bar**

## TCPWM Features (2/2)

- Motor control functions are supported only in the "16-bit for motor" counter group

- > Asymmetric PWM output control

- This function has a different compare value when counting up and down

- > PWM output selection for stepper motor

- Two PWM output signals (line\_out and line\_compl\_out) can be output by selecting one of the following values:

- Constant low (0) or high (1)

- PWM signal/Inverted PWM signal

- Z (high impedance)

- > Extend dead time

- Dead time can be extended from 8 bits to 16 bits

| int | Por |

|-----|-----|

| ΠIU | Dal |

- Counter Group 0: Up to 63 ch (16 bit) - Counter Group 1: 12 ch (16 bit for motor)

- Counter Group 2: 4 ch (32 bit) - Counter Group 3: Not available

Copyright © Infineon Technologies AG 2020. All rights reserved.

<sup>1</sup> CYT2B5/B7 (176-pin) supports three counter groups. Refer to the respective device datasheet for the number of counter groups supported by each device.

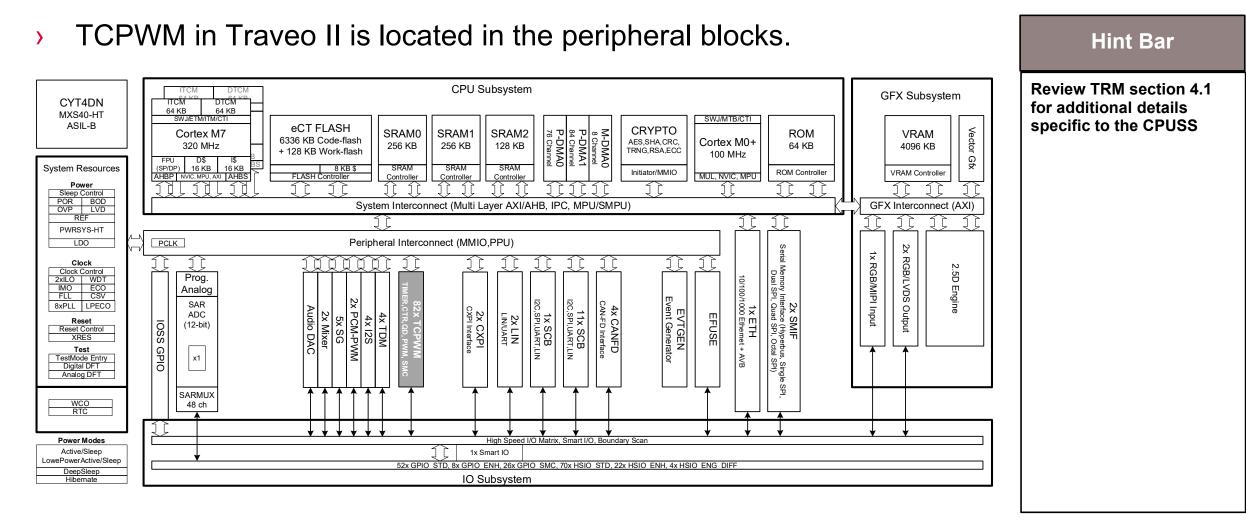

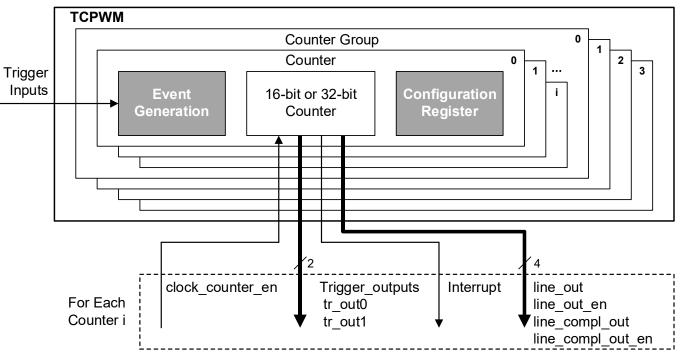

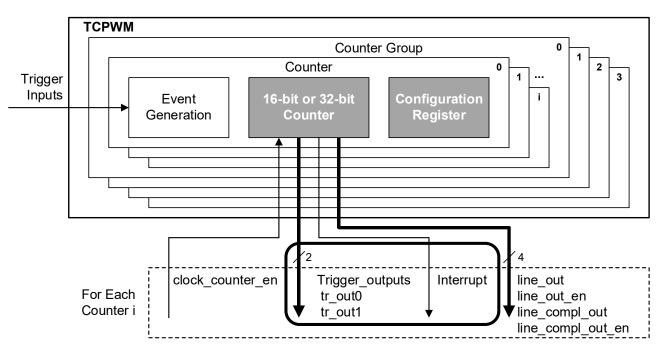

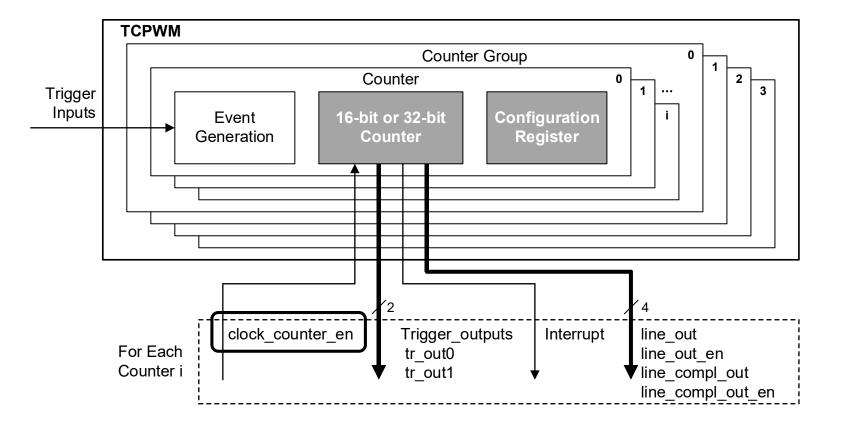

#### TCPWM Block Diagram

- > TCPWM components

- Event generation

- > 16-bit or 32-bit counter

Hint Bar

Review the TCPWM chapter in the TRM for additional details

Refer to the Features List in the datasheet for additional details

002-22211 \*D, 2021-02-01

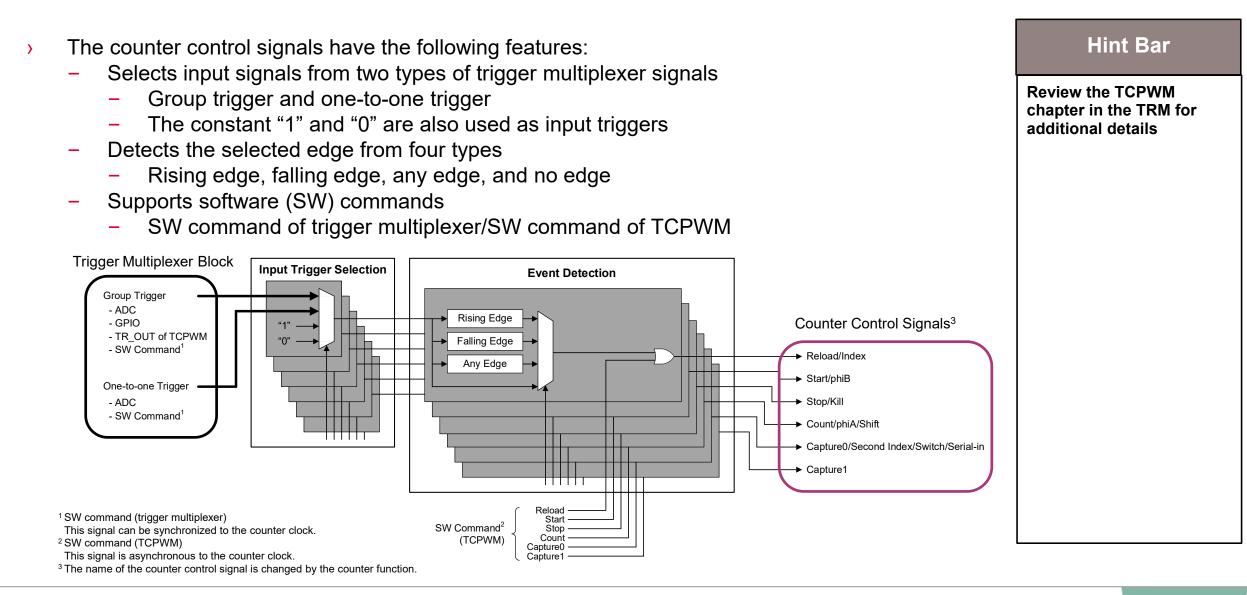

#### Event Generation

- > Event generation functions

- Input trigger selection

- Event detection

#### Hint Bar

#### Input Trigger Selection and Event Detection

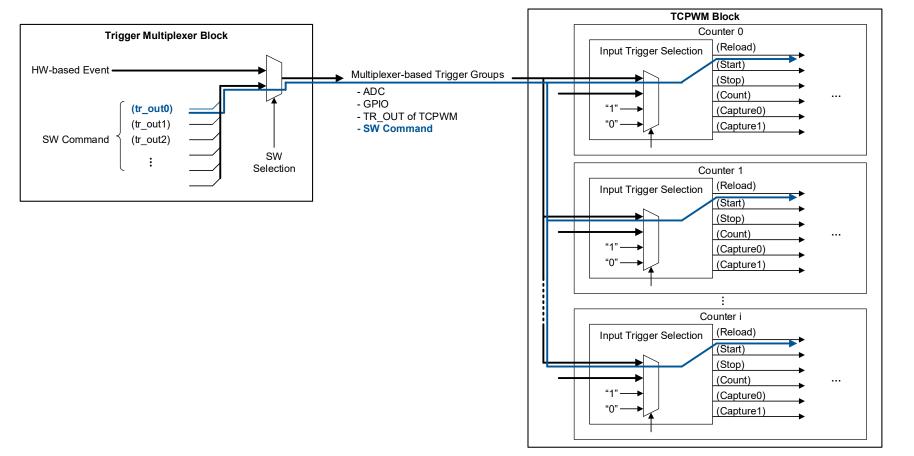

## Simultaneous Activation

- > Advantage

- When a trigger multiplexer block SW command is used, the TCPWM counters can also be activated at the same time

#### **Hint Bar**

### 16-bit or 32-bit Counter

#### **Trigger Output and Interrupt Generation Features**

- > Each counter has trigger outputs (TR\_OUT0/1) and an interrupt

- Overflow (OV)

- Underflow (UN)

- Terminal Count (TC)

- CC0/1\_MATCH

- LINE\_OUT

#### **Trigger Output and Interrupt Generation**

> TR\_OUT 0/1 and the interrupt are selected by SW

| Factor              | Description                                                                                                                                                                                                                                     | TR_OUT0/1 <sup>1</sup> | Interrupt |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------|

| Overflow (OV)       | An overflow event indicates that in an up counting mode,<br>COUNTER equals PERIOD register, and is changed to a<br>different value                                                                                                              | ✓                      | _         |

| Underflow (UN)      | An underflow event indicates that in a down counting mode,<br>COUNTER equals 0, and is changed to a different value                                                                                                                             | ~                      | —         |

| Terminal Count (TC) | A TC event is the logical OR of the underflow and overflow events                                                                                                                                                                               | ~                      | ~         |

| CC0/1_MATCH         | <ul> <li>This event is generated when the counter is running and one of the following conditions occur:</li> <li>Counter equals the compare value</li> <li>A capture event occurs and the CC0/1 and CC0/1_BUFF registers are updated</li> </ul> | ✓                      | ~         |

| LINE_OUT            | PWM output signal                                                                                                                                                                                                                               | ✓                      | _         |

Hint Bar

Review the TCPWM chapter in the TRM for additional details

> TR\_OUT can be routed through the trigger multiplexer to other peripherals on the device

<sup>1</sup> TR\_OUT0/1 can also be disabled.

#### **Clock Enable**

A counter increments or decrements by '1' for every counter clock cycle in which a count event is detected

Hint Bar

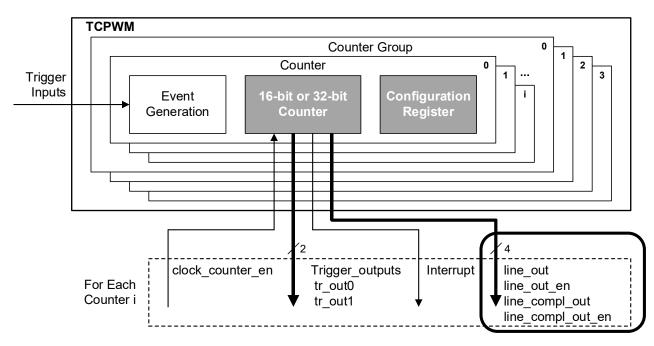

#### Line Output

- > Each counter can produce two output signals

- Line\_out

- Line\_compl\_out

- These signals are supported in PWM, PWM\_DT, PWM\_PR, and SR functionality

- > Output signal condition depends on two signals

- Line\_out\_en

- Line\_compl\_out\_en

Hint Bar

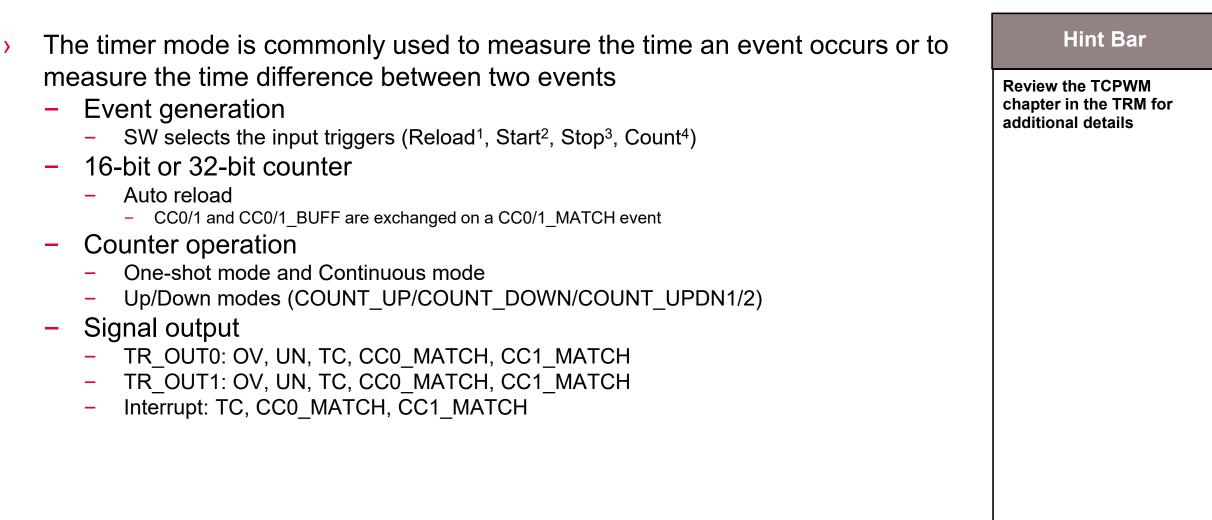

#### Timer

<sup>2</sup> Start: Starts the counter.

<sup>3</sup> Stop: Stops the counter.

<sup>4</sup> Count: Count event (increments/decrements the counter).

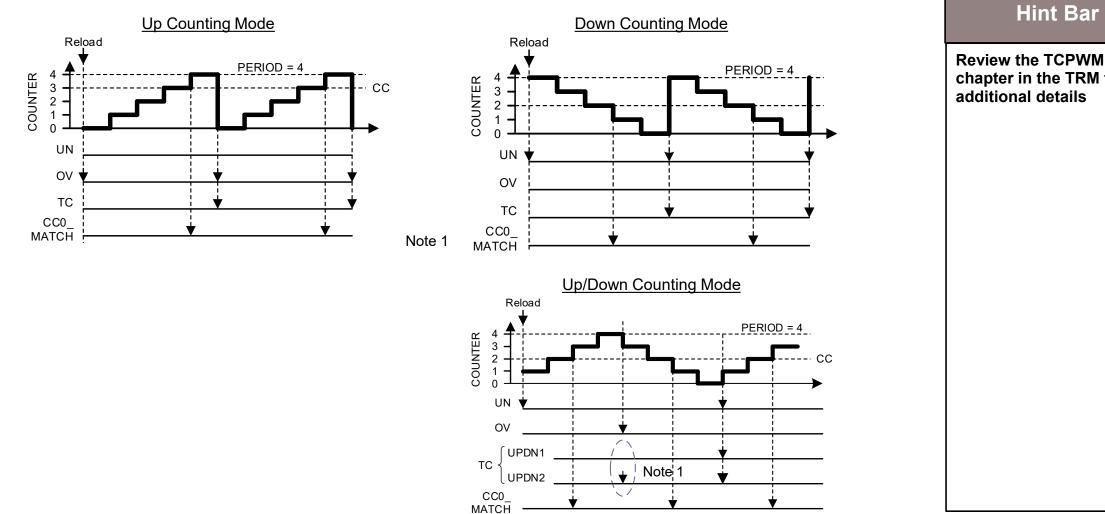

#### Timer Operation: One-shot Mode

**Hint Bar**

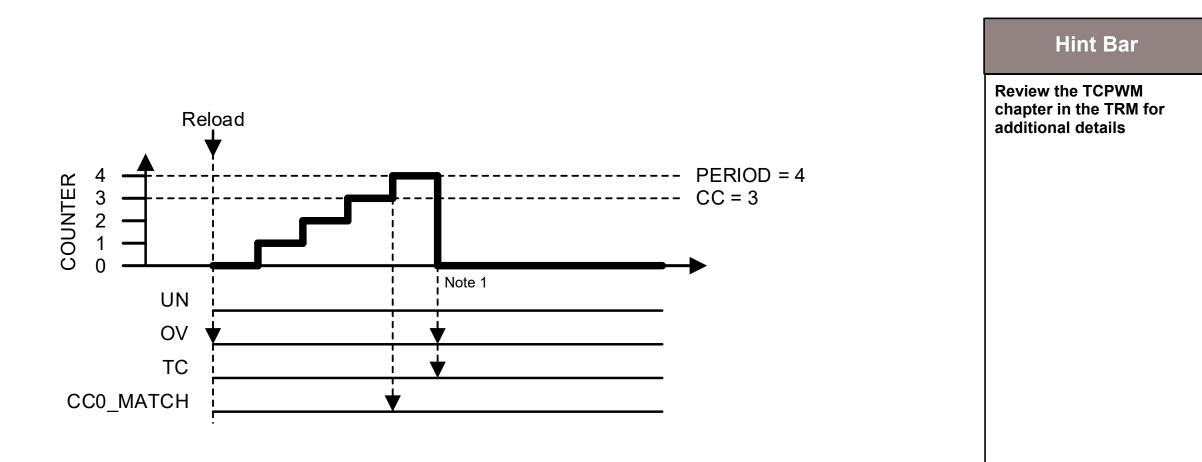

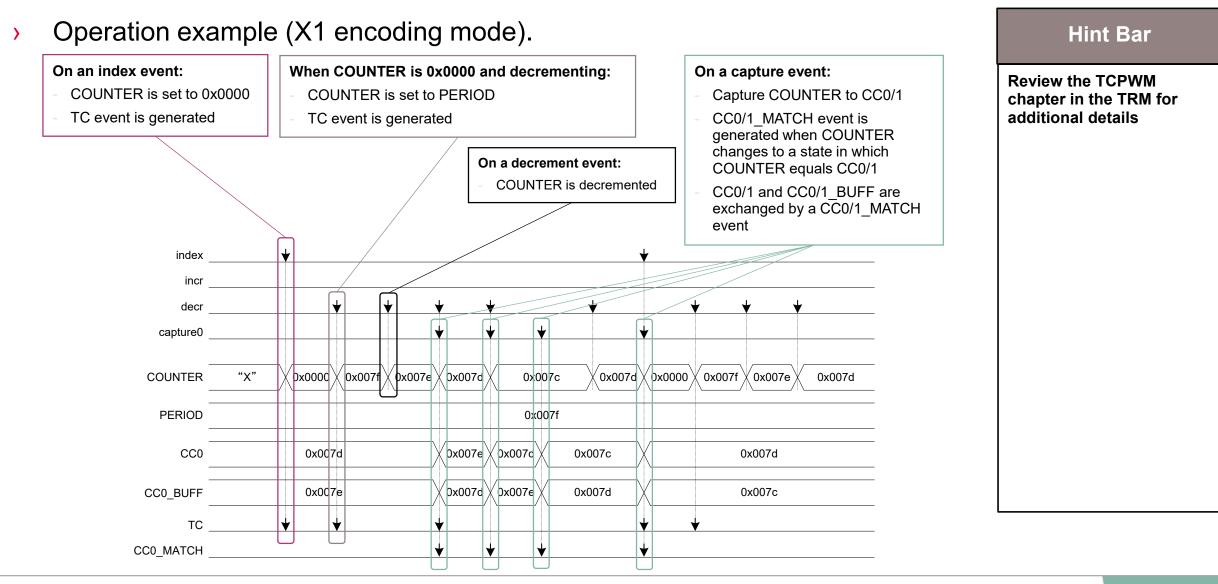

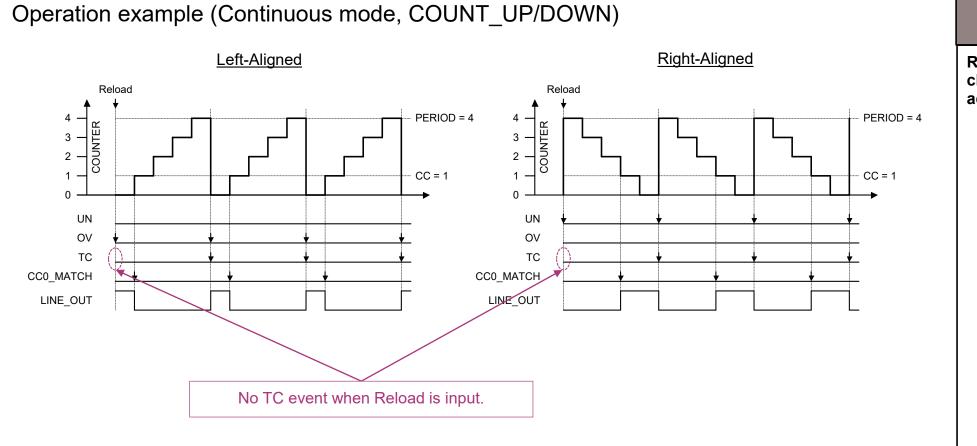

## Timer Operation: Up/Down modes (Continuous mode)

chapter in the TRM for additional details

<sup>1</sup> In COUNT UPDN2, TC is output when the counter overflows and underflows.

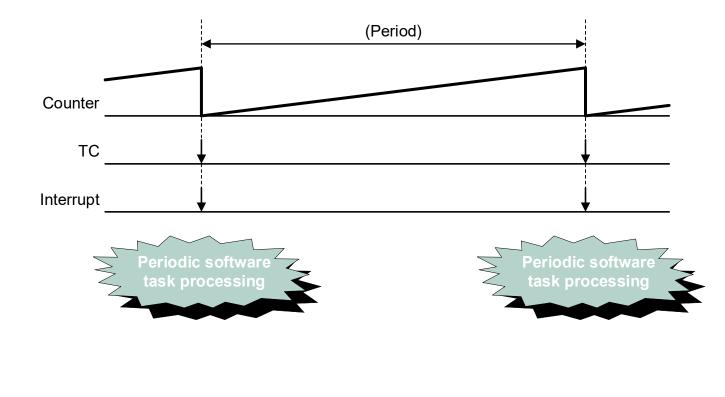

#### **Timer Use Case**

> Generate periodic interrupt for software task processing.

- Event generation

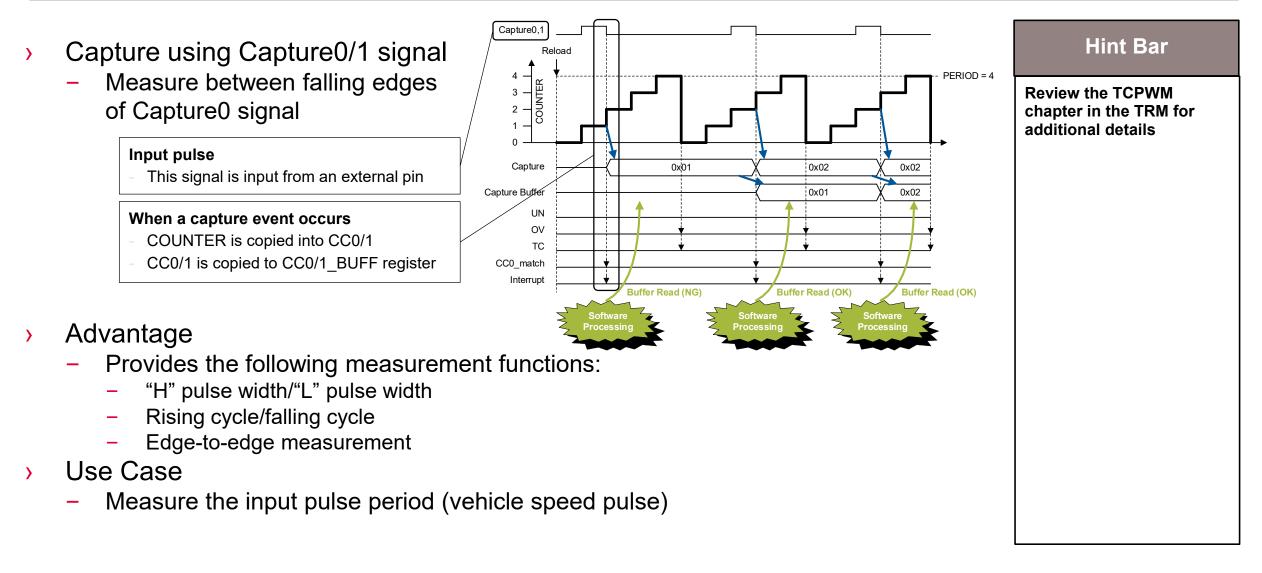

Capture

- SW selects input triggers (Reload<sup>1</sup>, Start<sup>2</sup>, Stop<sup>3</sup>, Count<sup>4</sup>, Capture0/1<sup>5</sup>)

- 16-bit or 32-bit counter

- Counter operation

- One-shot mode and Continuous mode

- Up/Down modes (COUNT\_UP/COUNT\_DOWN/COUNT\_UPDN1/2)

- Signal output

- TR\_OUT0: OV, UN, TC, CC0\_MATCH, CC1\_MATCH

- TR\_OUT1: OV, UN, TC, CC0\_MATCH, CC1\_MATCH

- Interrupt: TC, CC0\_MATCH, CC1\_MATCH

<sup>1</sup> Reload: Initializes and starts the counter.

<sup>2</sup> Start: Starts the counter.

<sup>3</sup> Stop: Stops the counter.

<sup>4</sup> Count: Count event increments/decrements the counter.

<sup>5</sup> Capture0/1: Copies the counter value to CC0/1 and CC0/1 to CC0/1 BUFF.

#### Hint Bar

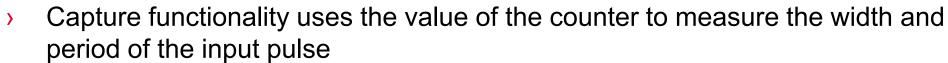

## **Capture Operation**

## Quadrature Decoder

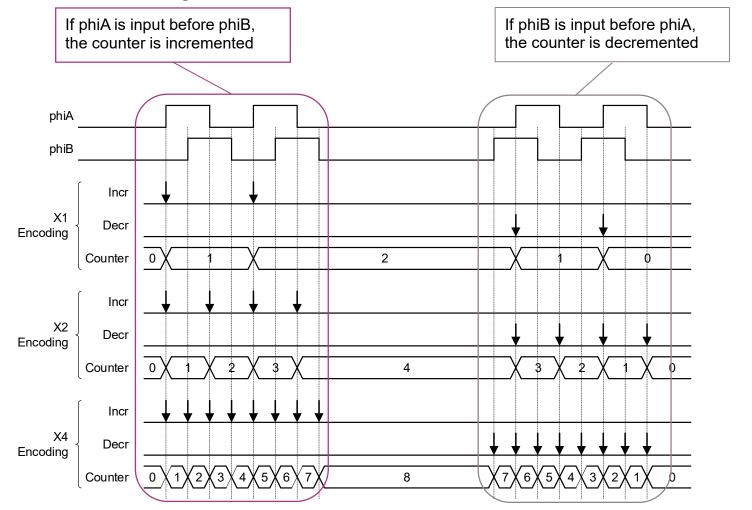

> The Quadrature Decoder has four Range modes and four Encoding modes

Copyright © Infineon Technologies AG 2020. All rights reserved.

- Range modes

- QUAD\_RANGE0

- QUAD\_RANGE0\_CMP

- QUAD\_RANGE1\_CMP

- QUAD\_RANGE1\_CAPT

- Encoding modes

- X1 encoding

- X2 encoding

- X4 encoding

- Up/down rotary count mode

- > Each Range mode has:

- Four encoding modes

- Different input trigger for each range mode

#### **Encoding Modes**

> X1, X2, and X4 encoding modes

#### Hint Bar

# infineon

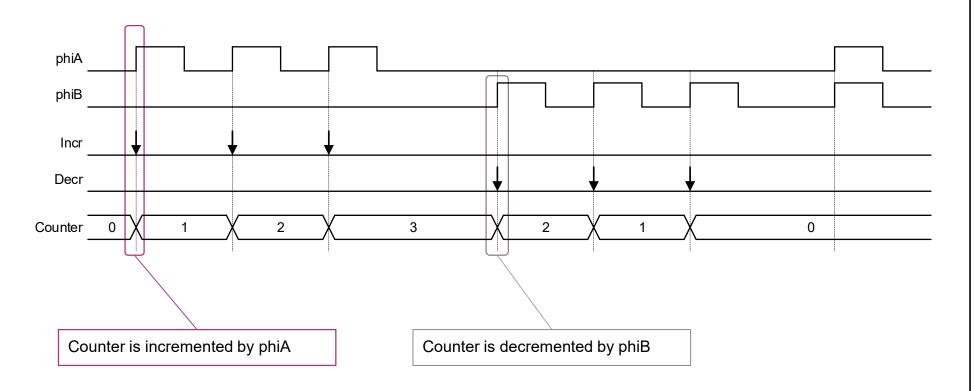

## **Encoding Modes**

> Up/Down rotary count mode

#### Range Modes

| Range Modes Supported         | Counter Range                  | Counter<br>Initial<br>Value | Copy the<br>Counter<br>Value <sup>1</sup> | Compare<br>Event <sup>1</sup> | Capture<br>Event¹ |

|-------------------------------|--------------------------------|-----------------------------|-------------------------------------------|-------------------------------|-------------------|

| QUAD_RANGE0                   | 0x0000 to<br>0xFFFF/0xFFFFFFFF | 0x8000                      | <b>~</b>                                  | -                             | _                 |

| QUAD_RANGE0_CMP               | 0x0000 to<br>0xFFFF/0xFFFFFFFF | 0x8000                      | <b>~</b>                                  | ~                             | _                 |

| QUAD_RANGE1_CMP               | 0x0000 to PERIOD               | 0x0000                      | _                                         | <b>~</b>                      | _                 |

| QUAD_RANGE1_CAPT <sup>2</sup> | 0x0000 to PERIOD               | 0x0000                      | _                                         | <b>~</b>                      | ✓                 |

#### Hint Bar

Review the TCPWM chapter in the TRM for additional details

- > Advantage

- Output of the quadrature encoder can be decoded without external circuits

<sup>1</sup> For details about each item, see the respective time chart on the following pages - <u>29</u>, <u>31</u>, <u>33</u>, <u>35</u>. <sup>2</sup> QUAD RANGE1 CAPT mode provides the same functionality as the QUAD RANGE1 CMP; the only difference is that capture functions are available.

<sup>1</sup> index: Initializes and starts the counter.

<sup>2</sup> phiB: Quadrature phiB input.

<sup>3</sup> Stop: Stops the quadrature functionality.

<sup>4</sup> phiA: Quadrature phiA input.

## QUAD\_RANGE0

- SW selects the input triggers (index<sup>1</sup>, phiB<sup>2</sup>, Stop<sup>3</sup>, phiA<sup>4</sup>)

- > 16-bit or 32-bit counter

- Counter operation

- Four encoding modes can be used (X1, X2, X4, and up/down rotary count mode)

- > Signal output

- TR\_OUT0: TC, CC0\_MATCH

- TR\_OUT1: TC, CC0\_MATCH

- Interrupt: TC, CC0\_MATCH

# infineon

### QUAD\_RANGE0 Operation

<sup>5</sup> Second index: This event acts as a second guadrature index input. It has the same function as the index event.

#### QUAD RANGE0 CMP

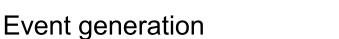

- **Event** generation >

- SW selects the input triggers (index<sup>1</sup>, phiB<sup>2</sup>, Stop<sup>3</sup>, phiA<sup>4</sup>, second index<sup>5</sup>)

- 16-bit or 32-bit counter

- Counter operation

- Four encoding modes can be used (X1, X2, X4, and up/down rotary count mode)

- Signal output >

- TR OUT0: TC, CC0 MATCH, CC1 MATCH

- TR OUT1: TC, CC0 MATCH, CC1 MATCH

- Interrupt: TC, CC0\_MATCH, CC1\_MATCH

<sup>1</sup> index: Initializes and starts the counter.

<sup>2</sup> phiB: Quadrature phiB input.

<sup>3</sup> Stop: Stops the guadrature functionality.

<sup>4</sup> phiA: Quadrature phiA input.

Hint Bar

**Review the TCPWM**

chapter in the TRM for additional details

#### QUAD\_RANGE0\_CMP Operation

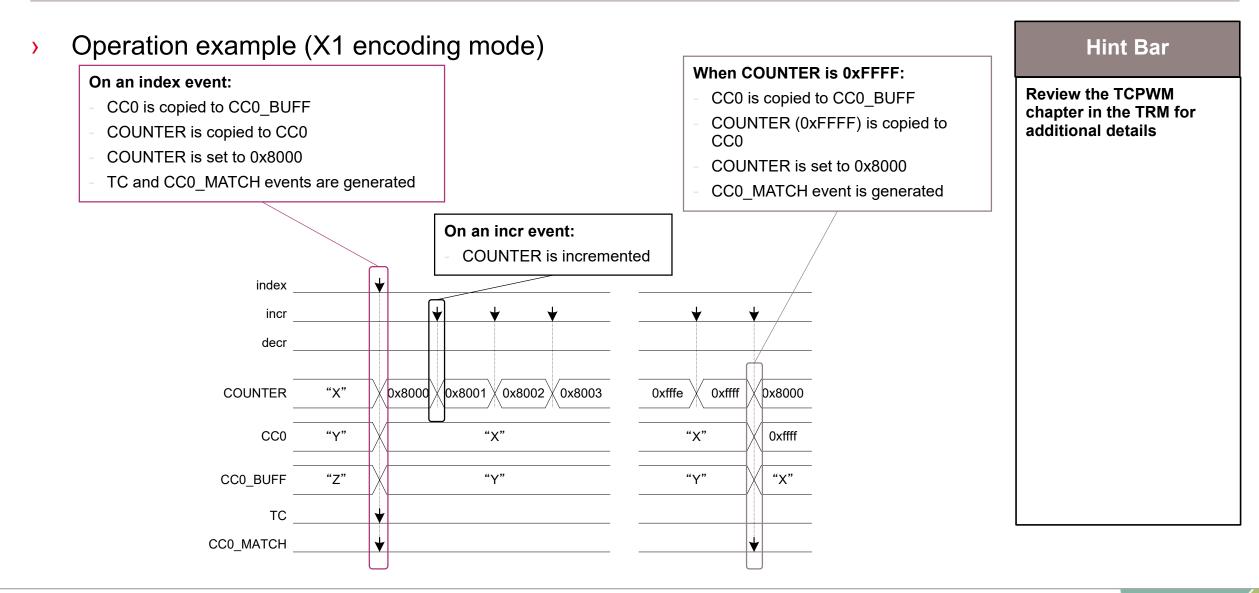

#### > Operation example (X1 encoding mode)

#### **Hint Bar**

<sup>1</sup> index: Initializes and starts the counter.

<sup>2</sup> phiB: Quadrature phiB input.

<sup>3</sup> Stop: Stops the guadrature functionality.

#### <sup>4</sup> phiA: This event acts as a quadrature phiA input.

## QUAD RANGE1 CMP

- **Event** generation >

- SW selects the input triggers (index<sup>1</sup>, phiB<sup>2</sup>, Stop<sup>3</sup>, phiA<sup>4</sup>)

- 16-bit or 32-bit counter

- Counter operation

- Four encoding modes can be used (X1, X2, X4, and up/down rotary count mode)

- Signal output >

- TR OUT0: OV, UN, TC, CC0 MATCH, CC1 MATCH

- TR OUT1: OV, UN, TC, CC0 MATCH, CC1 MATCH

- Interrupt: TC, CC0 MATCH, CC1 MATCH

Hint Bar

**Review the TCPWM**

chapter in the TRM for additional details

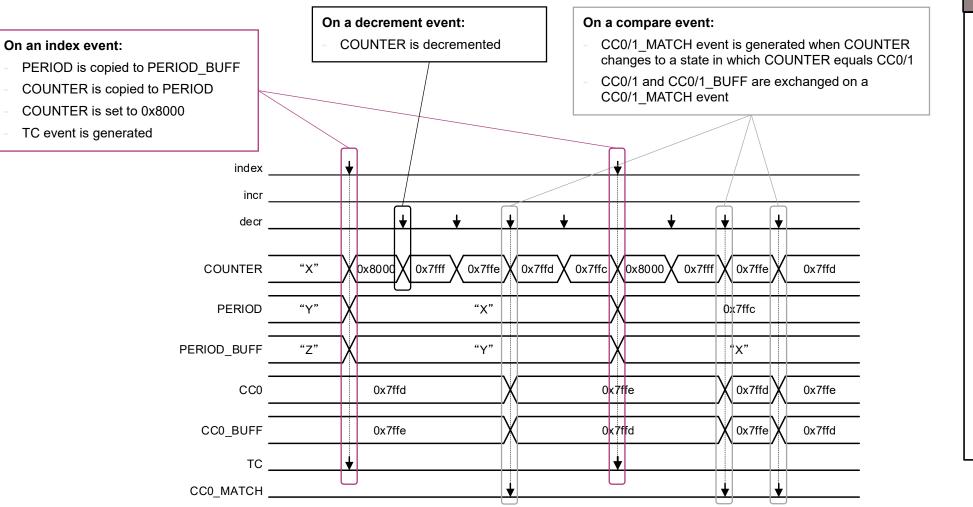

#### QUAD\_RANGE1\_CMP Operation

<sup>1</sup> index: Initializes and starts the counter.

- <sup>2</sup> phiB: Quadrature phiB input.

- <sup>3</sup> Stop: Stops the quadrature functionality. <sup>4</sup> phiA: This event acts as a quadrature phiA input.

<sup>5</sup> Capture0: Capture event to copy COUNTER to CC0, CC0 to CC0 BUFF. <sup>6</sup> Capture 1: Second capture event to copy COUNTER to CC1, CC1 to CC1 BUFF.

- - Interrupt: TC, CC0 MATCH, CC1 MATCH

- Signal output

>

- TR OUT0: OV, UN, TC, CC0 MATCH, CC1 MATCH

- TR OUT1: OV, UN, TC, CC0 MATCH, CC1 MATCH

QUAD RANGE1 CAPT

Counter operation

SW selects the input triggers (index<sup>1</sup>, phiB<sup>2</sup>, Stop<sup>3</sup>, phiA<sup>4</sup>, Capture $0^{5}/1^{6}$ )

Four encoding modes can be used (X1, X2, X4, and up/down rotary count mode)

## Hint Bar

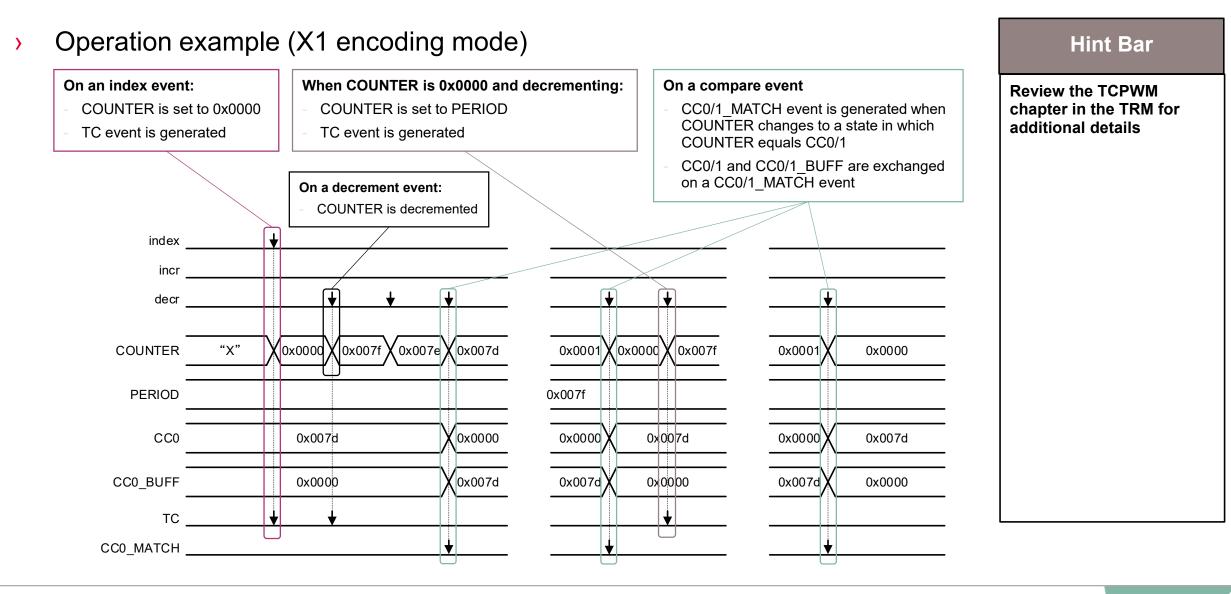

#### QUAD\_RANGE1\_CAPT Operation

The comparison output is a PWM signal whose period depends on the period register value and whose duty cycle depends on the compare and period register values

Event generation >

PWM

- SW selects the input triggers (Reload<sup>1</sup>, Start<sup>2</sup>, Stop/Kill<sup>3</sup>, Count<sup>4</sup>, Capture0<sup>5</sup>, Stop1/Kill1<sup>6</sup>)

- 16-bit or 32-bit counter

- Auto reload

- CC0/1 and CC0/1 BUFF are exchanged on a CC0/1 MATCH event

- PERIOD and PERIOD\_BUFF are exchanged on a switch event and TC event

- Counter operation —

- One-shot mode and Continuous mode

- Up/Down modes (COUNT UP/COUNT DOWN/COUNT UPDN1/2)

- Signal output

- TR\_OUT0: OV, UN, TC, CC0\_MATCH, CC1\_MATCH, LINE OUT<sup>7</sup>

- TR OUT1: OV, UN, TC, CC0 MATCH, CC1 MATCH, LINE OUT7

- Interrupt: TC, CC0 MATCH, CC1 MATCH

- <sup>1</sup> Reload: Sets the counter value and starts the counter.

- <sup>2</sup> Start: Starts the counter.

- <sup>3</sup> Stop/kill: Stops the counter. Different stop/kill modes exist.

- <sup>4</sup> Count: Count event incr/decr the counter.

- <sup>5</sup> Capture0: This event acts as a switch event.

- <sup>6</sup> Stop1/kill1: This event acts as a second stop/kill event.

#### Hint Bar

#### **PWM Operation**

>

#### Hint Bar

**Review the TCPWM** chapter in the TRM for additional details

#### **PWM** Operation

> Operation example (Continuous mode)

additional details

**Hint Bar**

# tineor

Hint Bar

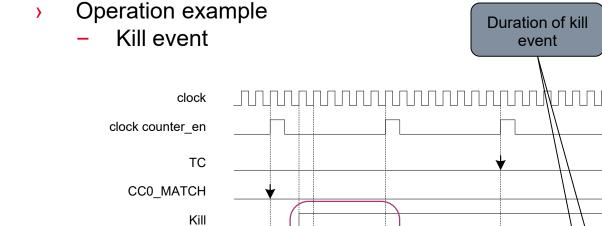

PWM outputs recover on the next clock

**PWM** Operation

<sup>&</sup>lt;sup>1</sup> line out is the signal when the kill event does not occur.

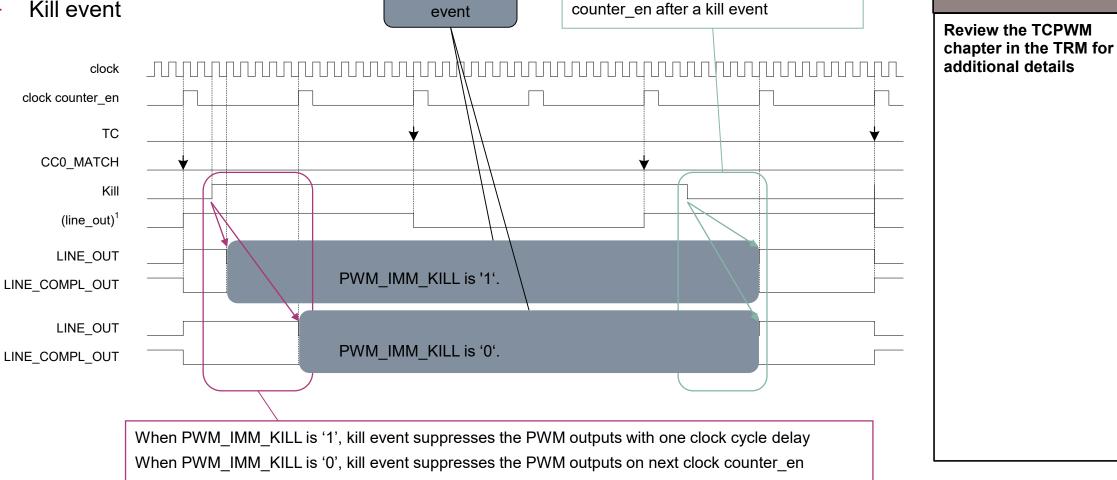

#### **PWM Use Case**

>

>

To get 0<sup>-7</sup>% duty cycle, CC0 must be set to a value higher than the period. If period is 0xFFFF (for 16-bit counter) or 0xFFFFFFFF (for 32-bit counter), 0% duty cycle cannot be achieved.

Hint Bar

**Review the TCPWM**

chapter in the TRM for additional details

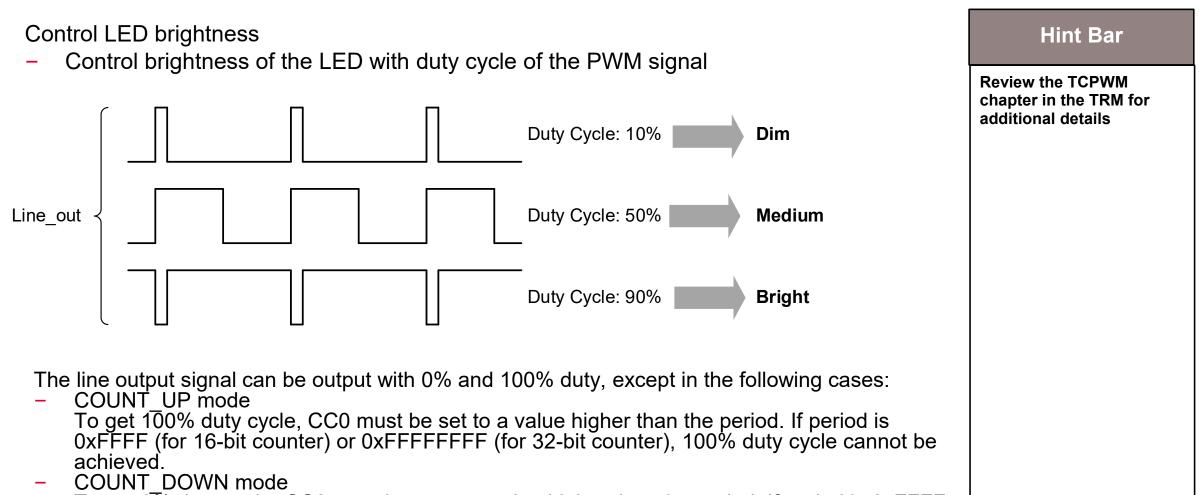

#### **PWM Use Case**

- Stepper Motor Control (SMC)

- TCPWM supports "PWM Output Selection" for stepper motors, including micro stepper control

- TCPWM (16 bit) #0: Generates the interrupt signal for motor control period

- TCPWM (16 bit for Motor) #0/1: Generates the SMC signals

- > Advantage

- TCPWM counter outputs can be connected to GPIO\_SMC<sup>1</sup> to support a drive strength of 30 mA for driving a stepper motor directly

<sup>1</sup> It is only supported by the Cluster device family.

#### <sup>1</sup> Reload: Sets the counter value and starts the counter. <sup>2</sup> Start: Starts the counter.

<sup>3</sup> Stop/kill: Stops the counter. Different stop/kill modes exist. <sup>4</sup> Count: Count event incr/decr the counter

<sup>5</sup> Capture0: This event acts as a switch event. <sup>6</sup> Stop1/kill1: This event acts as a second stop/kill event. <sup>7</sup> LINE OUT can be output with inverted polarity.

| Event generation                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - SW selects the input triggers (Reload <sup>1</sup> , Start <sup>2</sup> , Stop/kill <sup>3</sup> , Count <sup>4</sup> , Capture0 <sup>5</sup> , Stop1/kill <sup>6</sup> ) |

| 16-bit or 32-bit counter                                                                                                                                                    |

|                                                                                                                                                                             |

- 16-bit or 3 >

- Auto reload

PWM DT

>

- CC0/1 and CC0/1 BUFF are exchanged on a CC0/1 MATCH event

- PERIOD and PERIOD BUFF are exchanged on a switch event and TC event

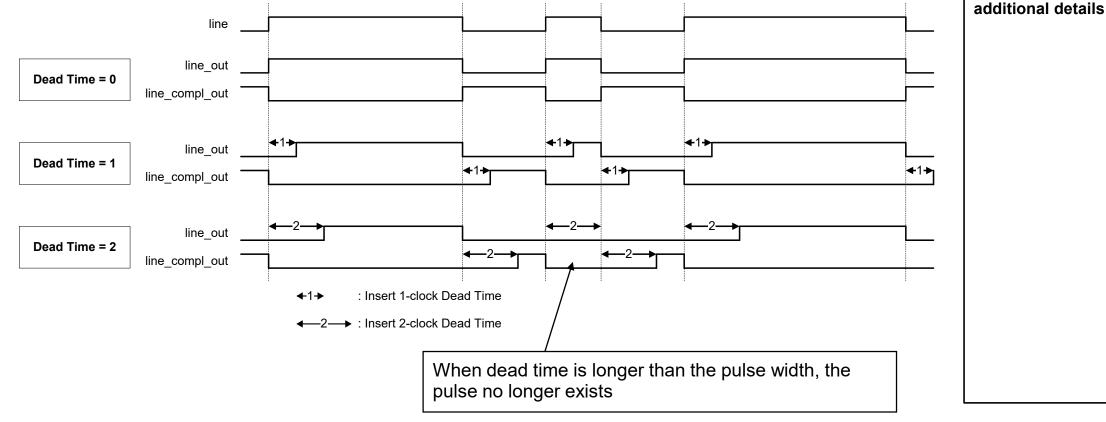

PWM DT functionality is the same as PWM functionality, except that dead time can be

- Counter operation

- One-shot mode and Continuous mode

inserted and clock pre-scaling is not provided

- Up/Down modes (COUNT UP/COUNT DOWN/COUNT UPDN1/2)

- Dead time insertion

- Range is 0 to 65535 counter clock cycles (16-bit, only for Counter Group 2)

- Range is 0 to 255 (8-bit)

- Signal output

- TR\_OUT0: OV, UN, TC, CC0\_MATCH, CC1\_MATCH, LINE OUT7

- TR OUT1: OV, UN, TC, CC0 MATCH, CC1 MATCH, LINE OUT7

- Interrupt: TC, CC0 MATCH, CC1 MATCH

Hint Bar

**Review the TCPWM**

additional details

chapter in the TRM for

42

>

To prevent a short circuit due to switching element delay, insert the dead time

#### **Dead Time Insertion**

Example (Dead time insertion: 0-clock, 1-clock, 2-clock)

**Hint Bar**

**Review the TCPWM** chapter in the TRM for

#### PWM\_DT Use Case

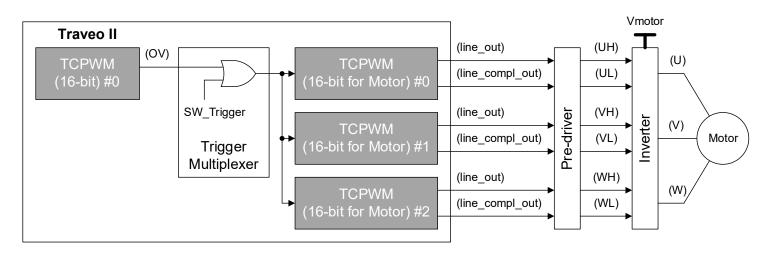

- > Three-phase motor control

- By using three TCPWMs, a three-phase motor can be controlled using a PWM signal with dead time

#### Hint Bar

Review the TCPWM chapter in the TRM for additional details

- TCPWM (16 bit) #0: Generates the motor control period

- TCPWM (16 bit for motor) #0/1/2: Generates the motor control signals

- Three TCPWMs can be activated simultaneously using overflow of TCPWM or SW command of trigger multiplexer

<sup>1</sup> Reload: Sets the counter value and starts the counter. <sup>2</sup> Start: Starts the counter. <sup>3</sup> Stop/kill: Stops the counter. Different stop/kill modes exist.

<sup>4</sup> Count: Count event incr/decr the counter.

<sup>5</sup> Capture0: This event acts as a switch event.

<sup>6</sup> Stop1/kill1: This event acts as a second stop/kill event.

<sup>7</sup> LINE\_OUT can be output with inverted polarity.

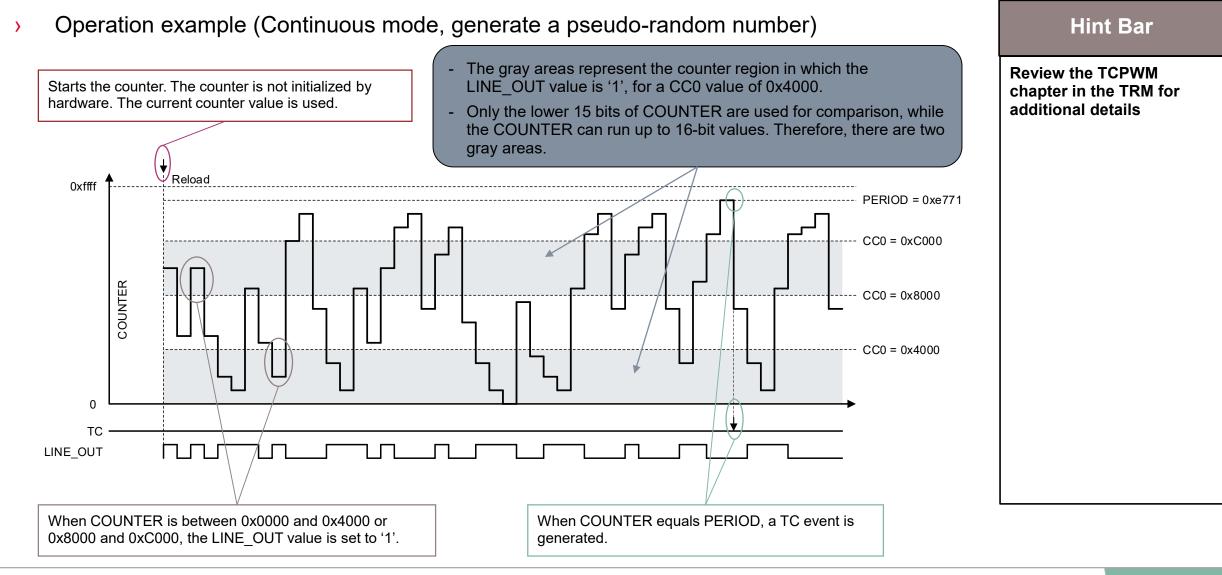

### PWM\_PR

- The PWM PR functionality changes the counter value using the linear feedback shift register (LFSR)

- > Event generation

- SW selects the input triggers (Reload<sup>1</sup>, Start<sup>2</sup>, Stop/kill<sup>3</sup>, Capture0<sup>4</sup>/1<sup>5</sup>)

- > 16-bit or 32-bit counter

- Auto reload

- CC0/1 and CC0/1\_BUFF are exchanged on a CC0/1\_MATCH event

- PERIOD and PERIOD\_BUFF are exchanged on a switch event and TC event

- LINE\_SEL and LINE\_SEL\_BUFF are exchanged on a switch event and TC event

- Counter operation

- One-shot mode and Continuous mode

- Generate a pseudo-random number sequence

- The generated signal has different frequency/noise characteristics than a regular PWM signal

- Programmable LFSR length

- Signal output

- TR\_OUT0: OV, UN, TC, CC0\_MATCH, CC1\_MATCH, LINE\_OUT<sup>6</sup>

- TR\_OUT1: OV, UN, TC, CC0\_MATCH, CC1\_MATCH, LINE\_OUT<sup>6</sup>

- Interrupt: TC, CC0\_MATCH, CC1\_MATCH

<sup>1</sup> Reload: Same behavior as start event.

<sup>2</sup> Start: Starts the counter.

<sup>3</sup> Stop/kill: Stops the counter. Different stop/kill modes exist <sup>4</sup> Capture0: Switch event. <sup>5</sup> Capture 1: Second stop/kill event.

<sup>6</sup> LINE\_OUT can be output with inverted polarity.

Hint Bar

Review the TCPWM chapter in the TRM for additional details

#### PWM\_PR Operation

## Shift Register

Hint Bar

**Review the TCPWM**

additional details

chapter in the TRM for

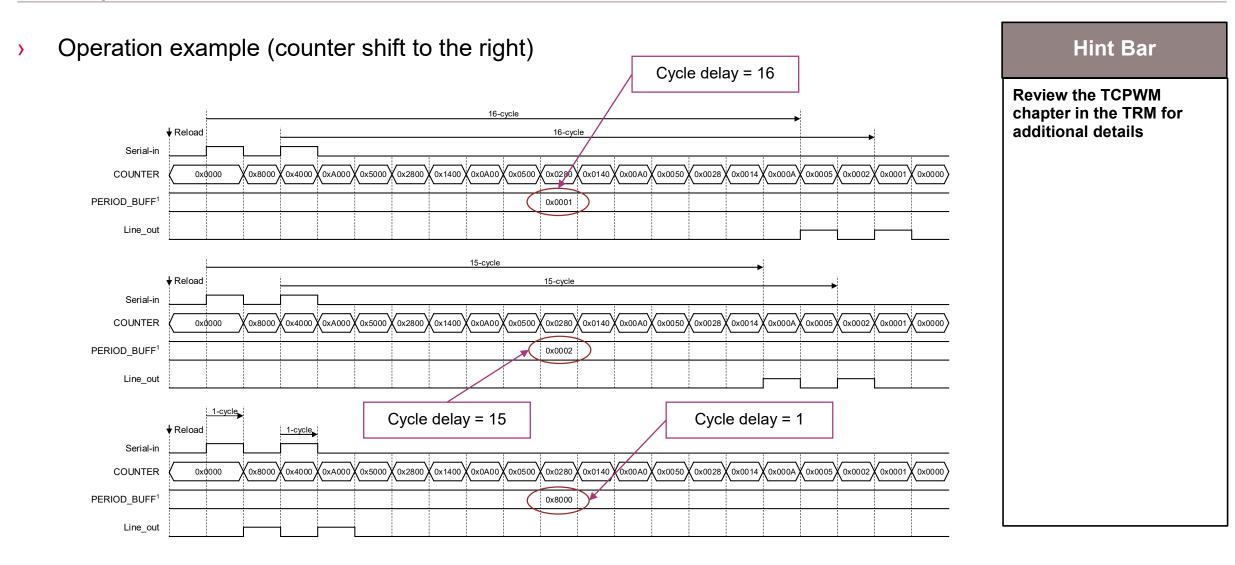

- > Shift Register (SR) functionality shifts the counter value to the right

- > Event generation

- SW selects the input triggers (Reload<sup>1</sup>, Start<sup>2</sup>, Stop<sup>3</sup>, Shift<sup>4</sup>, Serial-in<sup>5</sup>)

- > 16-bit or 32-bit counter

- Auto reload

- CC0/1 and CC0/1\_BUFF are exchanged on a CC0/1\_MATCH event

- Counter shift

- The counter value is shifted to the right

- Signal output

- TR\_OUT0: CC0\_MATCH, CC1\_MATCH, LINE\_OUT<sup>6</sup>

- TR\_OUT1: CC0\_MATCH, CC1\_MATCH, LINE\_OUT<sup>6</sup>

- Interrupt: CC0\_MATCH, CC1\_MATCH

| 1 | Reload: | Sets | the counter | value to | o "0" | and | starts the | counter | shift operation. |

|---|---------|------|-------------|----------|-------|-----|------------|---------|------------------|

|   |         |      |             |          |       |     |            |         |                  |

<sup>&</sup>lt;sup>2</sup> Start: Starts the counter shift operation.

<sup>&</sup>lt;sup>3</sup> Stop: Stops the counter.

<sup>&</sup>lt;sup>4</sup> Shift: Shifts the counter in right direction.

<sup>&</sup>lt;sup>5</sup> Serial-in: Serial input to the MSB of the counter.

$<sup>^{\</sup>rm 6}$  LINE\_OUT can be output with inverted polarity.

## **SR** Operation

<sup>1</sup> The set value of the PERIOD\_BUFF refers to the delay cycle number of the shift register. The period buffer needs to be set so that only one of the delay taps is valid.

**Hint Bar**

**Review the TCPWM**

additional details

chapter in the TRM for

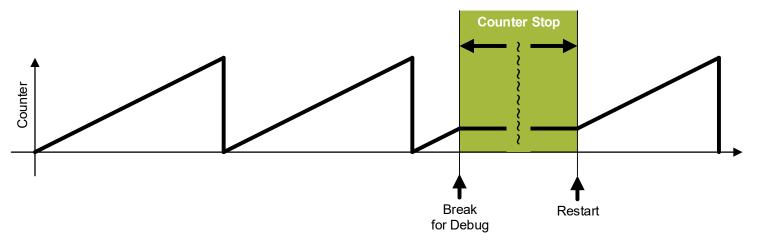

## Debug Mode

- > TCPWM counters support Debug mode

- Can be configured per counter if counter operation continues or pauses in debug state

- > Use Case

- Counter operation is paused

- > Advantage

- Even if you break for debugging, you can debug with the same counter operation as the actual operation

# Part of your life. Part of tomorrow.

Copyright © Infineon Technologies AG 2020. All rights reserved.

## **Revision History**

| Revision | ECN     | Submission<br>Date | Description of Change                                                                          |

|----------|---------|--------------------|------------------------------------------------------------------------------------------------|

| **       | 6151675 | 04/25/2018         | Initial release                                                                                |

| *A       | 6397021 | 10/24/2018         | Added page 2.<br>Updated pages 3, 4, 5, and 8.                                                 |

| *В       | 6715800 | 10/28/2019         | Added pages 5, 8, and 41.<br>Updated pages 2, 3, 4, 9, 10, 13, 14, 16, 17, 38, 40, 43, and 44. |

| *C       | 6822257 | 02/10/2019         | Updated figures on pages 37 and 38.<br>Updated Hint Bar on pages 6 to 49.                      |

| *D       | 7082696 | 02/01/2021         | Updated pages 2, 3, 4, 5.<br>Convert content to IFX format                                     |