# **Customer Training Workshop**

## Traveo<sup>™</sup> II Sound Generator

#### **Target Products**

> Target product list for this training material:

| Family Category               | Series | Code Flash Memory Size |

|-------------------------------|--------|------------------------|

| Traveo™ II Automotive Cluster | CYT3DL | Up to 4160KB           |

| Traveo™ II Automotive Cluster | CYT4DN | Up to 6336KB           |

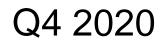

#### Introduction to Traveo II Cluster

#### Sound Generator (SG) Overview

- > SG produces PWM tone and amplitude signals

- Tone signal is used to generate sound frequencies

- Amplitude signal is used for volume control

- > Features

- PWM-modulated (amplitude, tone) sound generation

- Double-buffered segment structure control

- Two operating modes

- Separate volume and frequency control (two signals) format

- Combined volume-frequency control (one signal) format

- Programmable interface clock

| Review TRM section 33.5 for additional details |

|------------------------------------------------|

**Hint Bar**

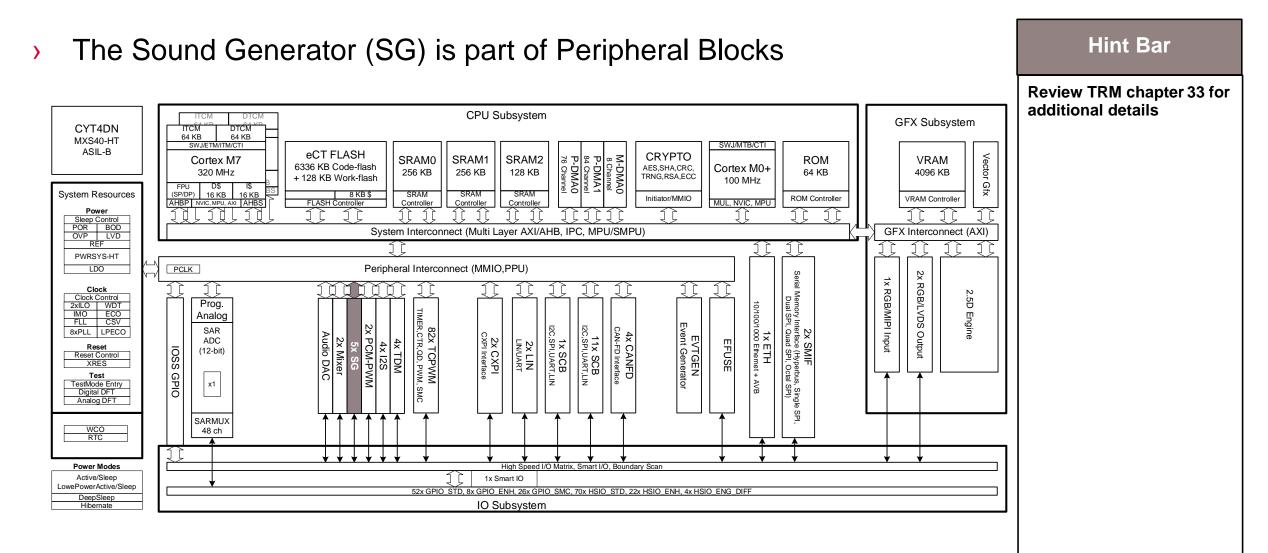

<sup>1</sup> Number of transmitters (n) varies by device

<sup>2</sup> See the device datasheet for assigned clocks to CLK\_IF\_SRSS[3:0] and CLK\_GRy

### SG Block Diagram

- SG components >

- Transmitter block

- Clock

- Output signals and segment structure

- Double buffering

- Audio waveform \_ composition

- Interrupt -

**Hint Bar**

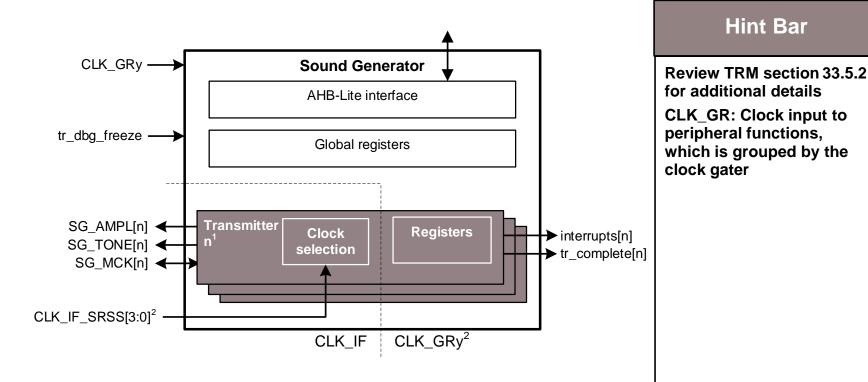

#### **PWM Interface Clock**

Hint Bar PWM interface clock can be derived from either of these clock signals Signal Description **Review TRM section 33.5.3** for additional details CLK IF SRSS[3:0]<sup>1</sup> SRSS clock SG AMPL OUT: Amplitude output SG MCK IN Master interface clock SG TONE OUT: Tone output An interface clock (CLK\_IF) is derived and then gated to derive the PWM clock **Review the Clock System** Training section for additional details about → SG\_MCK\_OUT → X high-frequency clocks CLK\_IF\_SRSS[0] CLK\_IF\_SRSS[1] -**Clock** gater →CLK IF "PWM clock" CLK IF\_SRSS[2] -CLK\_IF\_SRSS[3] - $\mathbb{N}$ SG MCK IN SGx\_SG\_STRUCTy\_IF\_CTL.CLOCK\_DIV SGx SG STRUCTy IF CTL.CLOCK SEL PWM clock drives the SG\_AMPL\_OUT and SG\_TONE\_OUT lines and its > resolution determines the amplitude PWM period frequency <sup>1</sup>See the device datasheet for assigned clocks to CLK IF SRSS[3:0]

#### Output Signals and Segment Structure (1/2)

| SG create<br>– Amplitu<br>– Tone d<br>To control<br>segment s          | Hint Bar<br>Review TRM section 33.5.4<br>for additional details<br>Review Registers TRM for<br>additional details |  |  |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Segment<br>Structure                                                   |                                                                                                                   |  |  |

| Amplitude                                                              | Amplitude Specifies the volume of the sound AMPL_CTL                                                              |  |  |

| Tone                                                                   | Tone Specifies the frequency of the sound TONE_CTL                                                                |  |  |

| Time                                                                   | Time Specifies how long a certain tone is played TIME_CTL                                                         |  |  |

| Step Specifies whether the volume is constant, decreasing, or STEP_CTL |                                                                                                                   |  |  |

>

>

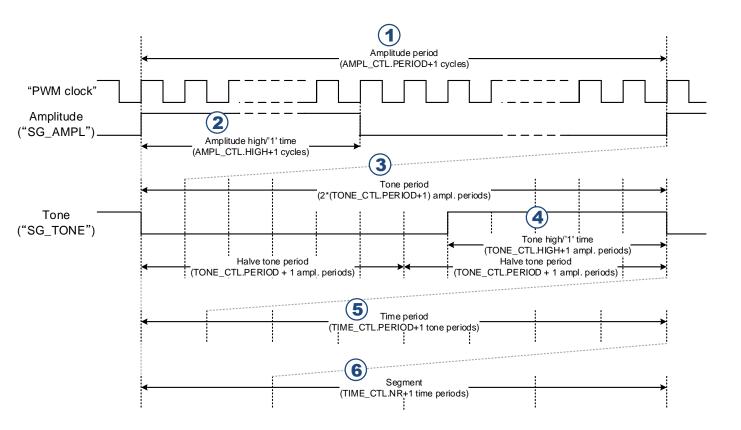

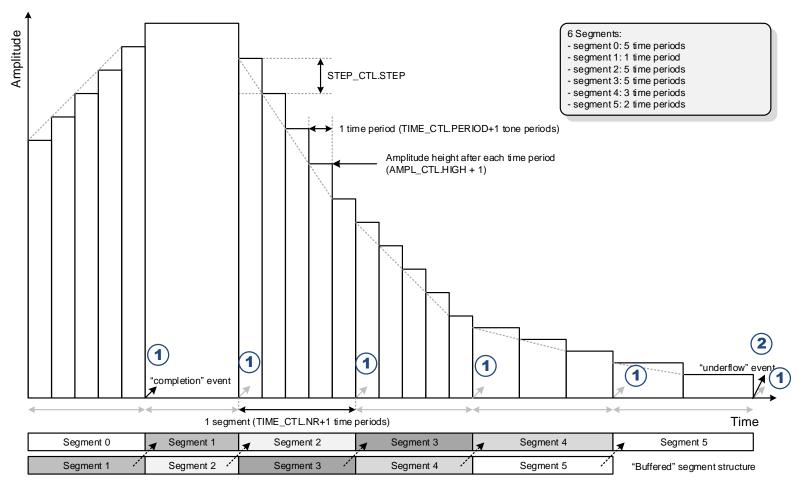

### Output Signals and Segment Structure (2/2)

- > Segment structure

- A single amplitude period is (AMPL\_CTL.PERIOD + 1) PWM clock cycles

- The high time of an amplitude period is specified by (AMPL\_CTL.HIGH + 1) PWM clock cycles

- ③ A single tone period is two times the (TONE\_CTL.PERIOD + 1) amplitude periods

- The high time of a tone period is defined by (TONE\_CTL.HIGH + 1) amplitude periods

- **(5)** A single time period is (TIME\_CTL.PERIOD

- + 1) tone periods

- 6 A single segment is (TIME\_CTL.NR + 1) time periods

**Hint Bar**

**Review TRM section 33.5.5**

for additional details

**Double Buffering**

> To generate sound continuously, double-buffered structures are used

- > Current structure can control the sound generation process

- > Buffered structure can be updated by a CPU or P-DMA

- When the current structure is complete, a completion event is activated, and the buffered structure is copied to the current structure

<sup>1</sup> Excluding Start bit or Stop bit

#### Audio Waveform Composition

- > In the diagram, multiple segments are used to describe a sound signal

- > After each segment, hardware

- Activates a completion event that

- Updates the current segment's structure with information of the buffered segment structure

- Activates tr\_complete trigger

- Activates INTR\_TX.COMPLETE interrupt cause

- 2 If the completion event is not followed by a buffered segment structure, it activates an underflow event and the sound generation ends

#### Audio Waveform Composition

Audio Waveform Composition Example

#### Interrupt

> A sound generator interrupt can be triggered by any of the following events

|  | Interrupt                         | Set Condition                                                                                                                                                                                                         |

|--|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | INTR_TX.COMPLETE                  | A segment descriptor is complete                                                                                                                                                                                      |

|  | INTR_TX.UNDERFLOW                 | A new segment structure is not available                                                                                                                                                                              |

|  | INTR_TX.IF_UNDERFLOW <sup>1</sup> | Sample pairs (amplitude, tone) are not generated in time for the interface logic.<br>It may indicate that the SG block system frequency is too low with respect to the interface frequency (a SW configuration error) |

Hint Bar

# Part of your life. Part of tomorrow.

Copyright © Infineon Technologies AG 2020. All rights reserved.

#### **Revision History**

| Revision | ECN     | Submission<br>Date | Description of Change                 |

|----------|---------|--------------------|---------------------------------------|

| **       | 6638977 | 07/29/2019         | Initial release                       |

| *A       | 6805395 | 02/12/2020         | Added note descriptions in each slide |

| *B       | 7053619 | 12/24/2020         | Updated page 2, 5, 6                  |