# Customer Training Workshop Traveo™ II Serial Memory Interface (SMIF)

> Target product list for this training material

| Family Category                            | Series     | Code Flash Memory Size |

|--------------------------------------------|------------|------------------------|

| Traveo™ II Automotive Body Controller High | CYT3BB/4BB | Up to 4160KB           |

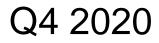

| Traveo II Automotive Body Controller High  | CYT4BF     | Up to 8384KB           |

| Traveo II Automotive Cluster               | CYT3DL     | Up to 4160KB           |

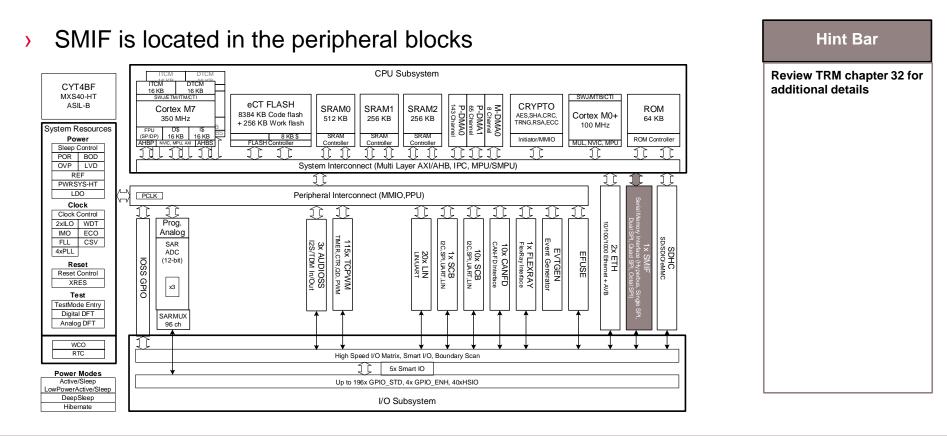

| Traveo II Automotive Cluster               | CYT4DN     | Up to 6336KB           |

### Introduction to Traveo II Cluster

## Serial Memory Interface (SMIF) Overview (1/2)

| SMIF provides an interface to memories with SPI and HyperBus IFs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Hint Bar                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Features</li> <li>SPI or HyperBus master functionality only</li> <li>SPI protocol <ul> <li>Mode 0 only, with configurable Master-In Slave-Out (MISO) sampling timing</li> <li>Single/Dual/Quad/Octal SPI transfer mode</li> <li>Dual-quad SPI mode (two devices sharing one address range)</li> <li>Single Data Rate (SDR) and Double Data Rate (DDR) transfer</li> </ul> </li> <li>Two operation modes <ul> <li>Memory Mapped I/O (MMIO) operation mode</li> <li>eXecute-In-Place (XIP) operation mode</li> <li>Read and write access</li> <li>Automatic transition access from dedicated internal memory address to SPI protocol</li> </ul> </li> </ul> | Review TRM section 32.1<br>for additional details<br>SPI Mode 0:<br>Data is driven on a falling<br>edge of SPIHB_CLK<br>Data is captured on a<br>rising edge of SPIHB_CLK |

| <ul> <li>On-the-fly encryption and decryption</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                           |

>

## Serial Memory Interface (SMIF) Overview (2/2)

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Hint Bar                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| <ul> <li>Memory Device</li> <li>Device capacity in the range of 64KB to 4GB (memory size: 2<sup>N</sup>) <ul> <li>(CYT4BF: 128MB area in XIP mode)</li> <li>(CYT4DN: 512MB x2 area in XIP mode)</li> </ul> </li> <li>Support for configurable external device capacities</li> <li>Up to two external memory devices sharing one address range (e.g. Dual-quad mode)</li> <li>Up to four chip selects available <ul> <li>(CYT4BF: 2 pcs)</li> <li>(CYT4DN: 2 pcs per channel)</li> </ul> </li> </ul> | Review TRM section 32.1<br>for additional details |

| <ul> <li>Memory Interface Logic</li> <li>Support stalling of transfers to address the back pressure on FIFOs</li> <li>Support read-write-data-strobe (RWDS)</li> <li>Support data signal connections between flexible external SPI memory devices</li> <li>Support delay line and data learning pattern (DLP)-based data capture (CYT4DN)</li> </ul>                                                                                                                                                |                                                   |

>

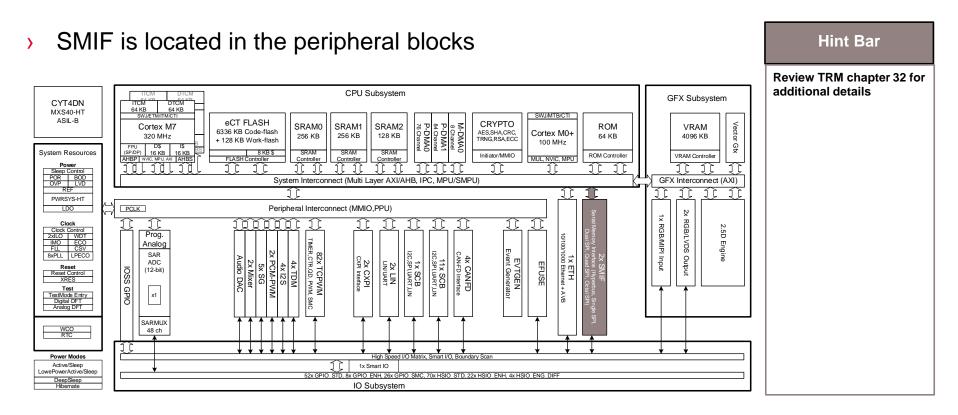

### Example of Using SMIF

- > External memory for code and data space

- > Directly mapped to internal memory map (XIP operation mode)

- > Encrypted/decrypted code or data in an external space

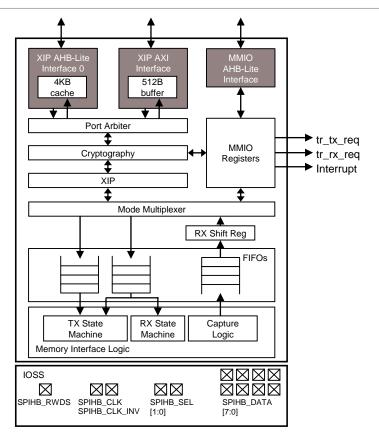

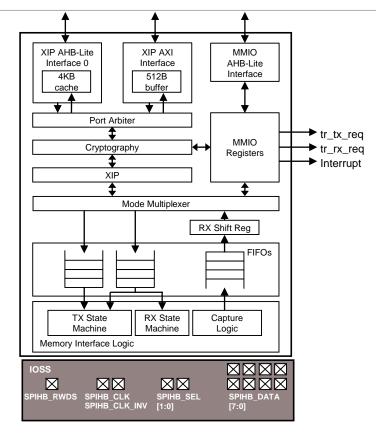

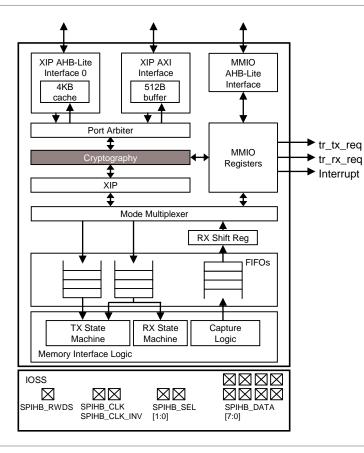

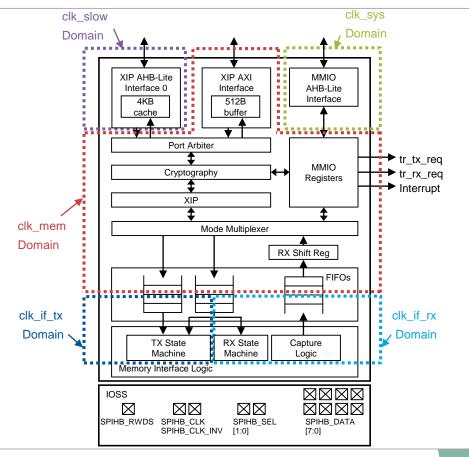

### SMIF Block Diagram

- > SMIF block components

- Bus interface

- MMIO AHB-Lite interface

- XIP AXI interface

- XIP AHB-Lite interface

#### **Bus Interface**

- > All bus interfaces provide access to external memories

- > Any of the three bus interfaces can access external memories at any time

- MMIO AHB-Lite interface

- Access to the MMIO registers

- Supports MMIO operation mode

- XIP AXI interface

- AXI interface for CPUSS fast domain<sup>1</sup>

- Supports XIP operation mode

- Fixed 512B buffer<sup>2</sup>

- XIP AHB-Lite interface

- AHB-Lite interface for CPUSS slow domain<sup>3</sup>

- Supports XIP operation mode

- 4KB read-only cache<sup>3</sup>

- The "hit" read transfers are processed by the cache

- Four-way set associative with an LRU replacement scheme

<sup>&</sup>lt;sup>1</sup> The CPUSS fast domain component is CM7 CPUs.

$<sup>^{2}</sup>$  Note that the cache and the AXI interface buffer are not retained in DeepSleep power mode.

<sup>&</sup>lt;sup>3</sup> The CPUSS slow domain components are CM0+ Crypto and P-DMA

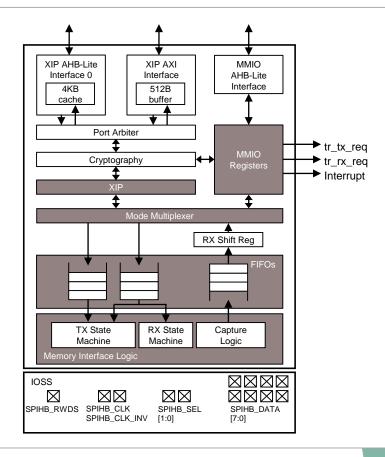

### SMIF Block Diagram

- SMIF block components

- FIFOs

- Two operation modes

- MMIO operation mode

- XIP operation mode

- Mode is switched by XIP\_MODE<sup>1</sup>

- Both modes are mutually exclusive

- Continuous transfer merging

<sup>1</sup> Refer to the Register TRM (SMIF\_CTL) for additional details.

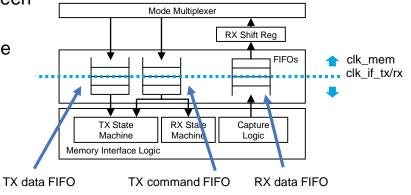

- SMIF has TX command FIFO, TX data FIFO, and RX data FIFO

- Provide an asynchronous clock domain transfer between clk\_mem and clk\_if\_tx/clk\_if\_rx

- Software<sup>1</sup> controls the FIFOs in MMIO operation mode

- MMIO registers<sup>2</sup> provide access to FIFOs

| FIFO            | Description                                                                                                   |

|-----------------|---------------------------------------------------------------------------------------------------------------|

| TX command FIFO | Transmit memory commands to the memory interface logic for memory transfer.<br>Support five types of commands |

| TX data FIFO    | Transmit write data to the memory interface logic                                                             |

| RX data FIFO    | Receive read data from the memory interface logic                                                             |

<sup>1</sup> In XIP operation mode, FIFOs are controlled by hardware. <sup>2</sup> Refer to the Register TRM for additional details.

### FIFOs (1/2)

- > TX command FIFO supports five command types

- TX command FIFO is controlled by the SMIF\_TX\_CMD\_FIFO\_WR.DATA27[26:0]<sup>1</sup> register

- DATA27[26:24] specifies the command and DATA[23:0] sets the command specification depending on command type

| Command:<br>DATA27[26:24] | Specification: DATA27[23:0]                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX: 0                     | <ul> <li>Width of the data transfer (single, dual, quad, or octal data transfer)</li> <li>Data transfer mode (SDR or DDR)</li> <li>External device select (multiple devices can be selected simultaneously)</li> <li>The command is for the last phase of memory transfer</li> <li>Transfer of 1-2 bytes</li> <li>A memory transfer must start with a TX command.</li> </ul> |

| TX_COUNT: 1               | <ul> <li>This command is used to transmit data from TX data FIFO to external memories</li> <li>Value of memory data to be transmitted</li> <li>Width of the data transfer</li> <li>Data transfer mode (SDR or DDR)</li> <li>Specifies if this command is for the last phase of the memory transfer</li> </ul>                                                                |

### FIFOs (2/2)

- > TX command FIFO supports five command types

- TX command FIFO is controlled by the SMIF\_TX\_CMD\_FIFO\_WR.DATA27[26:0]<sup>1</sup> register

- DATA27[26:24] specifies the command and DATA[23:0] sets the command specification depending on command type

| Command:<br>DATA27[26:24] | Specification: DATA27[23:0]                                                                                                                                                                                                                                                                             |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_COUNT: 2               | <ul> <li>This command is used by RX data FIFO to receive data from external memories</li> <li>Value of the memory data received</li> <li>Width of the data transfer</li> <li>Data transfer mode (SDR or DDR)</li> <li>Specifies if this command is for the last phase of the memory transfer</li> </ul> |

| DUMMY_COUNT: 3            | <ul> <li>Number of dummy cycles (used to implement turnaround time)</li> <li>If the variable latency mode for HyperRAM is enabled causing double the number of dummy cycles, this command never constitutes the last phase of the memory transfer</li> </ul>                                            |

| DESELECT: 4               | Finish a transfer and deselect the memory device<br>This command always constitutes the last phase of the memory transfer                                                                                                                                                                               |

**Hint Bar**

Review TRM section 32.1 for additional details

repeating the same type of

It can eliminate the overhead of SIO

instructions when

read command

Mode:

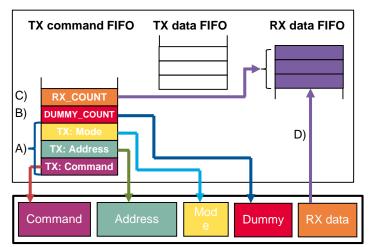

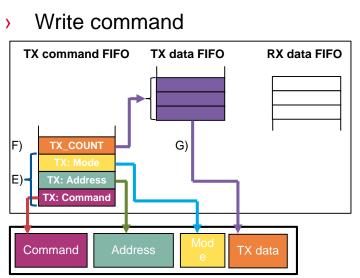

### Constructing a Read/Write Command

> Read command

- A) Set TX command FIFO in the order of Command, Address, and Mode using the "TX" command

- B) Set dummy cycle to the TX command FIFO using the "DUMMY\_COUNT" command

- C) Set number of reception data to the TX command FIFO using the "RX\_COUNT" command

- D) Receive the number of data set by RX\_COUNT in the RX data FIFO

- E) Set TX command FIFO in the order of Command, Address, and Mode using the "TX" command

- F) Set number of transmission data to the TX command FIFO using the "TX\_COUNT" command

- G) Transmit the number of data set by TX\_COUNT from the TX data FIFO

#### 002-25177 \*B 2020-12-03

#### **Operation Mode**

- MMIO Operation Mode >

- Active by writing "0" to XIP\_MODE1 \_

- Supports access through software using FIFOs \_

- Provides the flexibility to implement any SPI device transfer \_

#### MMIO Interface Write to Read from Command byte Address 0 Address 1 Address 2 Mode Byte DUMMY RX COUNT RX data (TX) (TX) (TX) (TX) (TX) DUMMY COUN (RX\_COUNT) FIFO (Command type) TX/RX FIFOs TX command TX comman TX command TX command TX command TX command **RX data FIFO** FIFO ... τх ТΧ ТΧ ΤХ ТΧ DUMMY RX\_ Memory Interface (command byte (address byte 0) (address byte 1 (address byte 2) (mode byte) COUNT COUNT Data Write example MMIO Interface Write to . . . Command byte Address 0 Address 1 Address 2 Mode Byte TX COUNT TX data FIFO TX data FIFO (TX) (TX) (TX) (TX) (TX) (TX COUNT) (Command type) TX command TX command TX command TX command TX command TX command TX data TX/RX FIFOs . . . TX data FIFO TX data FIFO FIFO FIFO FIFO FIFO FIFO . . . Memory Interface ΤХ ТΧ ТΧ ТΧ ТΧ ТΧ (address byte 0) address byte 1 address byte 2 (mode byte) COUNT (command byte) 1 XIP MODE default value is "0" in the MMIO mode.

#### **Data Read example**

**Hint Bar**

The software must ensure

that it generates correct

Read/write commands are specified by MMIO registers<sup>1</sup> for each device

#### **Data Read example**

\_

**Operation Mode**

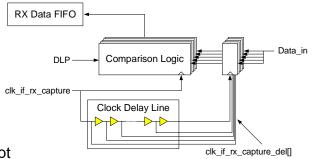

XIP Operation Mode

Active by writing "1" to XIP MODE

Supports read and write access

FIFOs are controlled by hardware

#### **XIP** Interface Read Read Request Request Addr. A (AXI/AHB-Lite) Addr. A+4 Issue read/write commands by hardware operation ТΧ ТΧ ТΧ ТΧ ТΧ DUMMY RX command (address (address (address (mode Memory Interface COUNT COUNT byte) byte 0) byte 1) byte 2) byte)

#### **Read/write commands** specification includes:

#### Presence and value of SPI or HyperBus command byte

**Hint Bar**

Number of address bytes

#### Presence and value of the mode byte

Number of dummy cycles

Data transfer widths and data transfer mode (SDR or DDR)

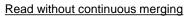

## **Continuous Transfer Merging**

- > The transfer can be merged to a single transfer at the memory interface<sup>1</sup> (MMIO and XIP modes)

- Background: Longer transactions split on the AXI bus due to arbitration and crypto support

- Avoid the overhead of multiple commands, addresses, modes, and dummy (latency) cycles

- > Advantage

- Improves performance of multiple continuous transfers

<sup>1</sup> Refer to the Register TRM (SMIF\_CTL.MERGE\_EN) for additional details.

τх

comman byte)

'last'=0

- A) 16-byte read transfer from address A involves command, address, and dummy cycle

- B) Read transfers from continuous addresses (A+16) also involves command, address, and dummy cycles

- C) 16-byte read transfer from address A involves command, address, and dummy cycle

- D) Read transfers from continuous addresses (A+16) do not require command, address, and dummy cycles

- E) When a new transfer is requested or start address is not a continuation (A+64), a DESELECT command is generated

The next read transfer requires a command, address, and dummy cycle

# infineon

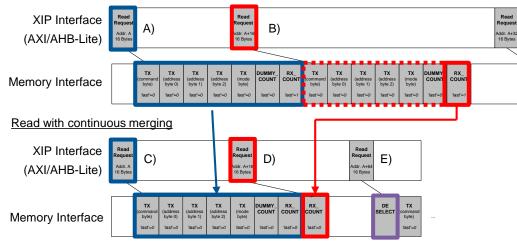

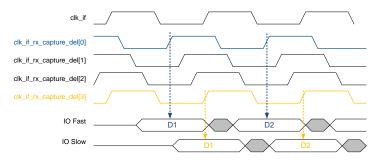

## Data Learning Pattern<sup>1</sup> (DLP)

- > SMIF supports delay line and DLP-based data capture

- Provides an optimal capture point within the data window

- Captures input data with different clocks generated by taps of a delay line

- Finds the delay tap for each data line by comparing the captured DLP with the expected one

- Memory device provides a known DLP on every data I/O pin before outputting read data

- No delay line tap resulting in a matching DLP, a data learning failed interrupt (in XIP/MMIO mode), and a bus error response (in XIP mode) being generated

- > Advantage

- Adjust signal delay easily due to wiring length, process, voltage, and temperature for each data line

- Maximize read data throughput

<sup>1</sup> DLP is available in CYT4DN.

#### **Bus Error Generation**

#### > External memory accesses cause bus error under the following conditions

| Interface        | Precondition                                                                                                                      | Bus Error Factor                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| ΜΜΙΟ             | - SMIF_CTL.BLOCK = $0^1$                                                                                                          | Software attempts to write an entry of a full TX command FIFO                        |

| (AHB-Lite)       |                                                                                                                                   | Software attempts to write more bytes than the available entries in the TX data FIFO |

|                  |                                                                                                                                   | Software attempts to read more bytes than the available entries in the RX data FIFO  |

| XIP<br>(AXI/AHB- | - SMIF_CTL.ENABLED = 0 <sup>1</sup><br>- Write or read access                                                                     | SMIF is disabled                                                                     |

| Lite)            | - SMIF_CTL.XIP_MODE = 0 <sup>1</sup><br>- Write or read access                                                                    | SMIF is not in XIP mode                                                              |

|                  | - XIP mode (SMIF_CTL.XIP_MODE = 1)<br>- Write or read access                                                                      | Transfer request is not in a memory region                                           |

|                  | - XIP mode (SMIF_CTL.XIP_MODE = 1)<br>- SMIF_DEVICE_CTL.WR_EN = 0 <sup>2</sup>                                                    | Write transfer to a region that does not support writes                              |

|                  | - XIP mode (SMIF_CTL.XIP_MODE = 1)                                                                                                | Transfer address is not a multiple of 2                                              |

|                  | <ul> <li>Write access</li> <li>Dual-quad SPI</li> <li>XIP mode (SMIF_CTL.XIP_MODE = 1)</li> </ul>                                 | Transfer size is not a multiple of 2                                                 |

|                  |                                                                                                                                   | Transfer address is not a multiple of 2                                              |

| - Octal SPI      | <ul> <li>Write access</li> <li>Octal SPI DDR mode or HyperBus mode</li> <li>Memory write byte masking is not supported</li> </ul> | Transfer size is not a multiple of 2                                                 |

|                  | - SMIF_CTL.INT_CLOCK_DL_ENABLED = 1                                                                                               | No delay line tap resulting in a matching data learning pattern                      |

<sup>1</sup> Refer to the Register TRM (SMIF\_CTL) for additional details. <sup>2</sup> Refer to the Register TRM (SMIF\_DEVICE\_CTL) for additional details.

#### SMIF Block Diagram

- > SMIF External Device Connection

- Single, dual, quad, and octal data transfer

- Maximum memory interface clock:

- Depends on memory and I/O type

|          |                       | Memory Type |         |          |

|----------|-----------------------|-------------|---------|----------|

| Products | I/O Type              | SDR         | DDR     | HyperBus |

| CYT4BF   | GPIO_STD <sup>1</sup> | 32 MHz      | 32 MHz  | 32 MHz   |

|          | HSIO_STD <sup>2</sup> | 100 MHz     | 100 MHz | 100 MHz  |

| CYT4DN   | HSIO_ENH <sup>3</sup> | 166 MHz     | 100 MHz | 200 MHz  |

- Can connect up to four devices

- Independent SPIHB\_CLK\_INV outputs

- Less latency, and no overlapping of SPIHB\_CLK

<sup>1</sup> Supports standard automotive GPIO. Refer to the device datasheet for additional details.

<sup>2</sup> Supports high-speed I/O standard for high-speed peripherals. Refer to the device datasheet for additional details.

<sup>3</sup> Supports high-speed I/O enhanced for high-speed peripherals. Refer to the device datasheet for additional details.

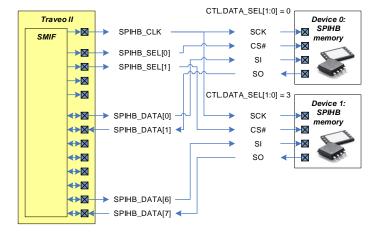

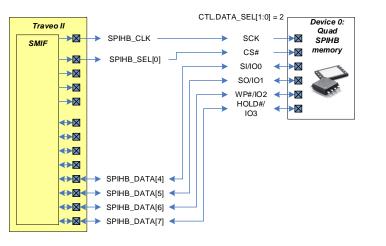

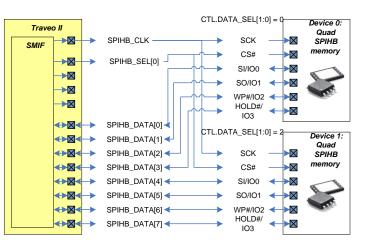

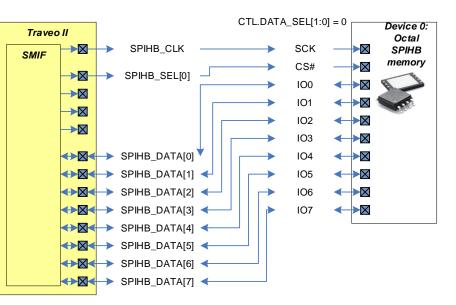

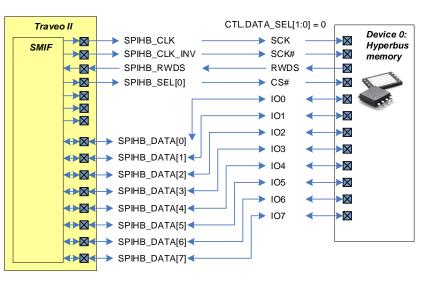

- > SPI Connection

- Support for single, dual, quad, and octal SPI protocol

- Data signal type configuration in the MMIO register1

- Can be set independently for each memory device (chip select)

| DATA_SEL[1:0] | Single SPI<br>(Full Duplex)                | Dual SPI<br>(Half Duplex)                    | Quad SPI<br>(Half Duplex)                         | Octal SPI<br>(Half Duplex)                        |

|---------------|--------------------------------------------|----------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| 0             | SPIHB_DATA [0] = SI<br>SPIHB_DATA [1] = SO | SPIHB_DATA [0] = IO0<br>SPIHB_DATA [1] = IO1 | SPIHB_DATA [0] = IO0<br>:<br>SPIHB_DATA [3] = IO3 | SPIHB_DATA [0] = IO0<br>:<br>SPIHB_DATA [7] = IO7 |

| 1             | SPIHB_DATA [2] = SI<br>SPIHB_DATA [3] = SO | SPIHB_DATA [2] = IO0<br>SPIHB_DATA [3] = IO1 | Illegal setting                                   | Illegal setting                                   |

| 2             | SPIHB_DATA [4] = SI<br>SPIHB_DATA [5] = SO | SPIHB_DATA [4] = IO0<br>SPIHB_DATA [5] = IO1 | SPIHB_DATA [4] = IO0<br>:<br>SPIHB_DATA [7] = IO3 | Illegal setting                                   |

| 3             | SPIHB_DATA [6] = SI<br>SPIHB_DATA [7] = SO | SPIHB_DATA [6] = IO0<br>SPIHB_DATA [7] = IO1 | Illegal setting                                   | Illegal setting                                   |

#### **Data Signal Connections**

<sup>1</sup> Refer to the Register TRM (SMIF\_DEVICE\_CTL) for additional details.

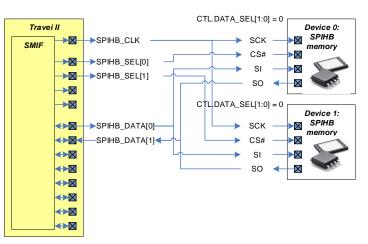

### **External Device Connection**

- SPI Connection

- The following diagrams show examples of a single SPI connection

- > Features

- Data signal connections are configured by DATA\_SEL

- Chip select signal setting is configured depending on the operation mode

| Operation Mode | Setting Register                                 | Chip Select                                        | Note            |

|----------------|--------------------------------------------------|----------------------------------------------------|-----------------|

| 1440           | MMIO TX command FIFO<br>DATA[23:20] <sup>1</sup> | DATA[21]: SPIHB0_SEL[1]<br>DATA[20]: SPIHB0_SEL[0] |                 |

| WIWIO          |                                                  | DATA[23]: SPIHB1_SEL[1]<br>DATA[22]: SPIHB1_SEL[0] | Supports CYT4DN |

| XIP            | SMIF0_DEVICE0 <sup>2</sup>                       | SPIHB0_SEL[0]                                      |                 |

|                | SMIF0_DEVICE1 <sup>2</sup>                       | SPIHB0_SEL[1]                                      |                 |

|                | SMIF1_DEVICE0 <sup>2</sup>                       | SPIHB1_SEL[0]                                      | Supports CVT4DN |

|                | SMIF1_DEVICE1 <sup>2</sup>                       | SPIHB1_SEL[1]                                      | Supports CYT4DN |

<sup>1</sup> Refer to the Register TRM (SMIF\_TX\_CMD\_FIFO\_WR) for additional details. Multi chip selects can be set at the same time in dual-quad mode. <sup>2</sup> Refer to Register TRM (SMIF\_DEVICE) for additional details.

**SPI** Connection

>

External Device Connection

#### Single SPI with Separate Data Signals

Single SPI with Shared Data Signals

### External Device Connection

- > SPI Connection

- The following diagrams show examples of quad and dual-quad SPI connections

- > Features

- Quad SPI can also use SPIHB\_DATA [4:7] by the DATA\_SEL configuration

#### **Quad SPI Connection**

Dual-Quad SPI Connection (Pseudo Octal)

#### External Device Connection

- > SPI Connection

- The following diagram shows an example of an octal SPI connection

- > Features

- The only valid setting for DATA\_SEL is "0"

- HyperBus Connection

- The following diagram shows an example of the HyperBus connection

- > Features

- Supports read-write-data-strobe (RWDS)

- Only valid setting for DATA\_SEL is "0"

#### HyperBus Connection

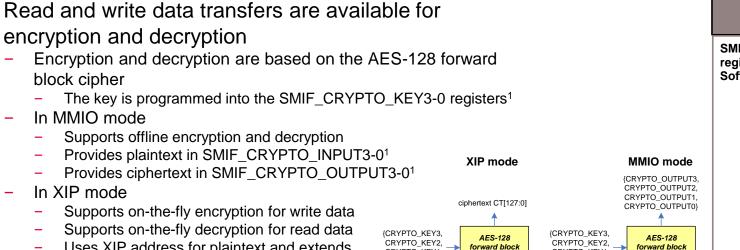

### SMIF Block Diagram

- > SMIF block component

- Cryptography

### Cryptography

block cipher

In XIP mode

In MMIO mode

cipher

(CRYPTO INPUT3,

CRYPTO INPUT2,

CRYPTO INPUT1

A[31:4], CRYPT0 INPUT0}

CRYPTO KEY1,

CRYPTO KEY0}

cipher

(CRYPTO INPUT3

CRYPTO INPUT2.

CRYPTO INPUT1.

CRYPTO INPUT0}

- Uses XIP address for plaintext and extends to SMIF CRYPTO INPUT3-0

- Advantage

\_

Storing data encrypted in external memory devices prevents leakage of sensitive data

CRYPTO KEY1,

CRYPTO KEY0}

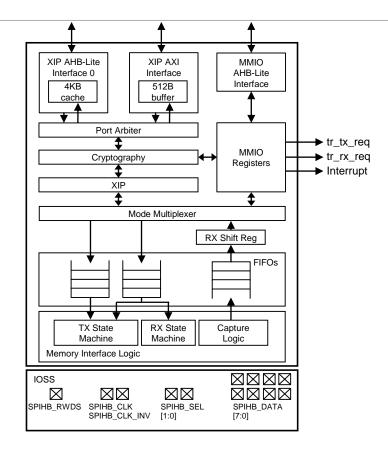

### SMIF Block Diagram

- SMIF block components

- Trigger and interrupt

- tr\_tx\_req

- tr\_rx\_req

- Interrupt

> SMIF has two triggers

| Trigger   | Condition                                                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| tr_tx_req | Active when the number of used TX data FIFO entries is smaller than or equal to the specified number <sup>1</sup> . Activated in MMIO operation mode |

| tr_rx_req | Active when the number of used RX data FIFO entries is greater than or equal to the specified number <sup>2</sup> . Activated in MMIO operation mode |

<sup>1</sup> Refer to the Register TRM (SMIF\_TX\_DATA\_MMIO\_FIFO\_CTL and SMIF\_TX\_DATA\_MMIO\_FIFO\_STATUS) for additional details. <sup>2</sup> Refer to the Register TRM (SMIF\_RX\_DATA\_MMIO\_FIFO\_CTL and SMIF\_RX\_DATA\_MMIO\_FIFO\_STATUS) for additional details.

#### > SMIF has one interrupt

| Interrupt Cause                  | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TR_TX_REQ                        | Active when the tr_tx_req trigger is activated.<br>Activated in MMIO operation mode                                                                                                                                                                                                                                                                                                                                                                        |

| TR_RX_REQ                        | Active when the tr_rx_req trigger is activated.<br>Activated in MMIO operation mode                                                                                                                                                                                                                                                                                                                                                                        |

| XIP_ALIGNMENT_ERROR <sup>1</sup> | <ul> <li>The XIP AHB-Lite/AXI bus transfer address is not a multiple of "2" or</li> <li>The requested XIP AHB-Lite/AXI bus transfer size is not a multiple of "2"</li> <li>In the above conditions <ul> <li>a) a write transfer is requested and</li> <li>b) Dual-Quad SPI mode is selected or</li> <li>Octal SPI DDR mode or HyperBus mode is selected without memory write byte masking</li> <li>Activated in XIP operation mode.</li> </ul> </li> </ul> |

| TX_CMD_FIFO_OVERFLOW             | Write transfer to TX command FIFO <sup>2</sup> with not enough free entries available.<br>Activated in MMIO operation mode                                                                                                                                                                                                                                                                                                                                 |

Refer to the Register TRM (SMIF\_INTR) for additional details.

Refer to the Register TRM (SMIF\_TX\_CMD\_FIFO\_WR) for additional details.

Refer to the Register TRM (SMIF\_TX\_DATA\_FIFO\_WR1,WR2,WR4) for additional details.

Refer to the Register TRM (SMIF\_RX\_DATA\_FIFO\_RD1,RD2,RD4) for additional details.

#### > SMIF has one interrupt

| Interrupt Cause       | Condition                                                                                                                                                                                                                                                                                |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TX_DATA_FIFO_OVERFLOW | Write transfer to TX data FIFO <sup>3</sup> with not enough free entries available.<br>Activated in MMIO operation mode                                                                                                                                                                  |  |

| RX_DATA_FIFO_OVERFLOW | Read transfer from RX data FIFO <sup>4</sup> with not enough entries available.<br>Activated in MMIO operation mode                                                                                                                                                                      |  |

| DL_FAIL               | Data Learning Failed (no DLP match found on at least one of the input data lines when CTL.INT_CLOCK_DL_ENABLED = 1)                                                                                                                                                                      |  |

| DL_WARNING            | Data Learning Warning (for at least one input data line less then<br>DLP.DL_WARNING_LEVEL delay line taps resulted in a correct DLP capturing when<br>CTL.INT_CLOCK_DL_ENABLED = 1).<br>This interrupt will be suppressed if DL_FAIL also occurs during the same DLP evaluation<br>cycle |  |

| CRC_ERROR             | CRC Error. A read transfer data CRC check failed                                                                                                                                                                                                                                         |  |

| FS_STATUS_ERROR       | Functional Safety Status Error. A read transfer Functional Safety Status check failed                                                                                                                                                                                                    |  |

### SMIF Block Diagram

- > SMIF block components

- Clock domains

- CLK\_MEM

- CLK\_SLOW

- CLK\_SYS

- clk\_if\_tx/rx

| ock |

|-----|

|     |

|     |

| > The fo     | Hint Bar                  |                                                                                                                                   |                                              |

|--------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Source       | Used Block                | Function                                                                                                                          | Review TRM chapter 18 for additional details |

| clk_mem      | SMIF Internal Block FIFOs | Used for the SMIF block; it is sourced from the mem clock The frequency range is up to 200 MHz                                    |                                              |

|              | AXI Master Interface      | Used by the XIP AXI master interface; it is sourced from<br>the mem clock<br>The frequency range is up to 200 MHz                 |                                              |

| clk_slow     | AHB Slave Interface       | Used by the XIP AHB-Lite master interface; it is sourced from the slow clock<br>The frequency range is up to 100 MHz              |                                              |

| clk_sys      | AHB Slave Interface       | Used by the MMIO AHB-Lite slave interface; it is clocked<br>by the PERI group clock<br>The frequency range is up to 100 MHz       |                                              |

| clk_if_tx/rx | Memory Interface FIFOs    | Used for memory interface of transmit and receive; it is<br>clocked by the CLK_HF6<br>clk_if_tx is the source clock for SPIHB_CLK |                                              |

# Part of your life. Part of tomorrow.

| Revision | ECN     | Submission<br>Data | Description of Change                                                                         |

|----------|---------|--------------------|-----------------------------------------------------------------------------------------------|

| **       | 6399119 | 12/3/2018          | Initial release                                                                               |

| *A       | 6633414 | 7/22/2019          | Change from mxsmif_ver2 to mxsmif_ver3<br>Updated slide 2, 6, 18, 19<br>Added slide 4, 17, 31 |

| *B       | 7039074 | 12/03/2020         | Updated page 2, 3, 4                                                                          |