# Customer Training Workshop Traveo™ II Inter-Processor Communication (IPC)

#### **Target Products**

#### > Target product list for this training material

| Family Category                             | Series     | Code Flash Memory Size |

|---------------------------------------------|------------|------------------------|

| Traveo™ II Automotive Body Controller Entry | CYT2B6     | Up to 576KB            |

| Traveo II Automotive Body Controller Entry  | CYT2B7     | Up to 1088KB           |

| Traveo II Automotive Body Controller Entry  | CYT2B9     | Up to 2112KB           |

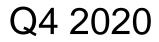

| Traveo II Automotive Body Controller Entry  | CYT2BL     | Up to 4160KB           |

| Traveo II Automotive Body Controller High   | CYT3BB/4BB | Up to 4160KB           |

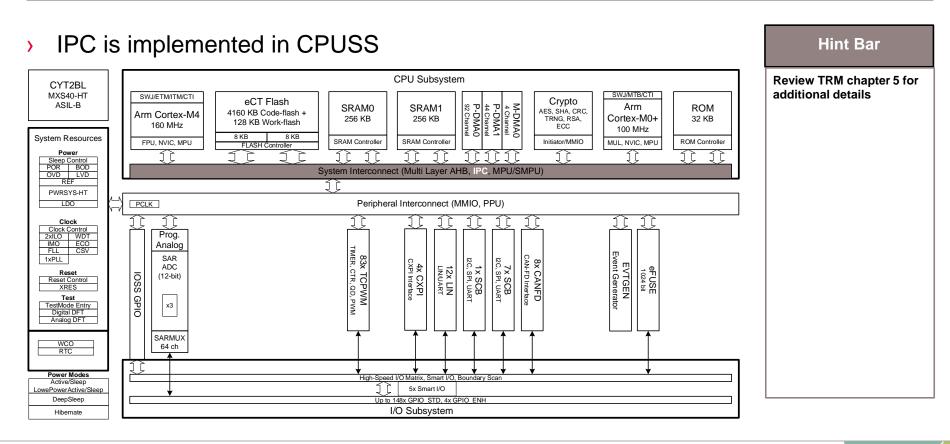

| Traveo II Automotive Body Controller High   | CYT4BF     | Up to 8384KB           |

| Traveo II Automotive Cluster                | CYT3DL     | Up to 4160KB           |

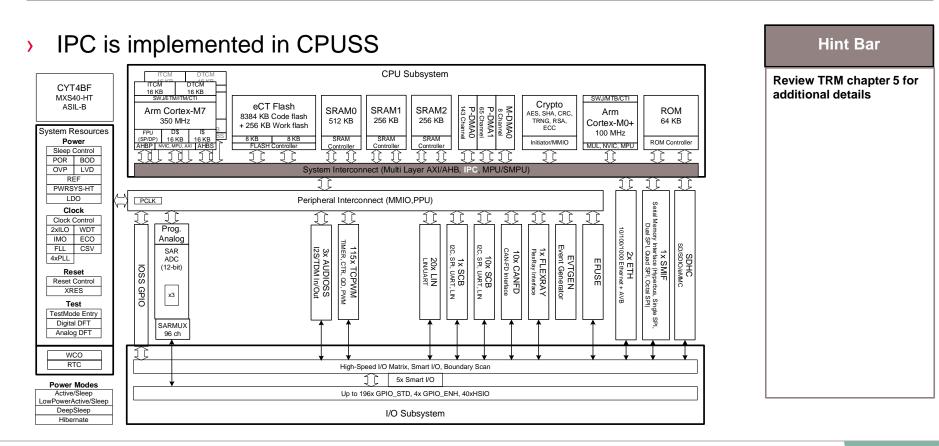

| Traveo II Automotive Cluster                | CYT4DN     | Up to 6336KB           |

### Introduction to Traveo II Body Controller Entry

### Introduction to Traveo II Body Controller High

### Inter-Processor Communication (IPC) Overview

| PC provides the functionality for multiple processors to                                                                                                                                                                                                                                                                                                           | Hint Bar                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>communicate and synchronize, and includes:</li> <li>Locks for mutual exclusion access</li> <li>Notification and release event generation</li> <li>Data communication</li> <li>Lock status indications</li> <li>Interrupt generation of event to each processor</li> <li>Some IPC channel and interrupt structures are reserved for API use (*)</li> </ul> | Review TRM sections 5.1.1<br>and 5.1.2 for additional<br>details<br>* Training section<br>reference for additional<br>details about API:<br><u>Nonvolatile Memory</u><br><u>Programming</u> |

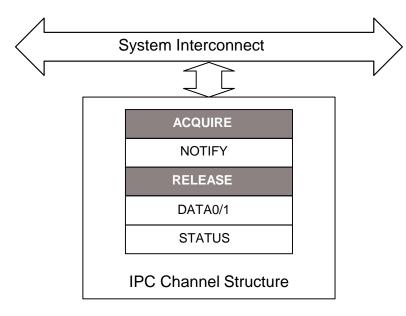

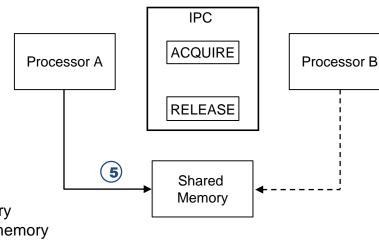

| <ul> <li>IPC has two structure types</li> <li>IPC channel</li> <li>IPC interrupt</li> </ul>                                                                                                                                                                                                                                                                        |                                                                                                                                                                                             |

#### <sup>1</sup> Can place a address pointer and data size when passing large amounts of data (for example, DATA0 uses address pointer, DATA1 uses data size). <sup>2</sup> Provides the processor's ID, protection context, and other details.

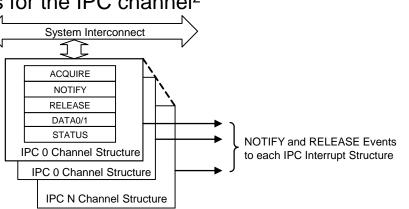

## IPC Channel Structure

- > Channel structure hardware registers are implemented as:

- IPC\_ACQUIRE: Provides lock feature by reading

- NOTIFY: Generates notification event

- RELEASE: Releases the IPC channel

- DATA0/1: 32-bit register to hold data<sup>1</sup>

- STATUS: Lock status for the IPC channel<sup>2</sup>

**Hint Bar**

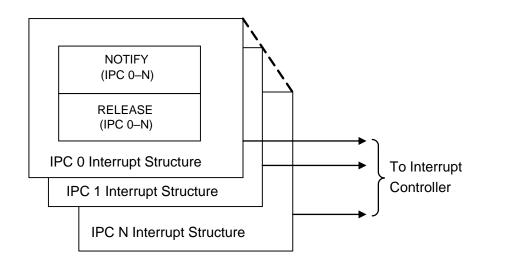

#### IPC Interrupt Structure

Each IPC interrupt has a corresponding IPC interrupt structure that is triggered by a notification or release event from any IPC channel

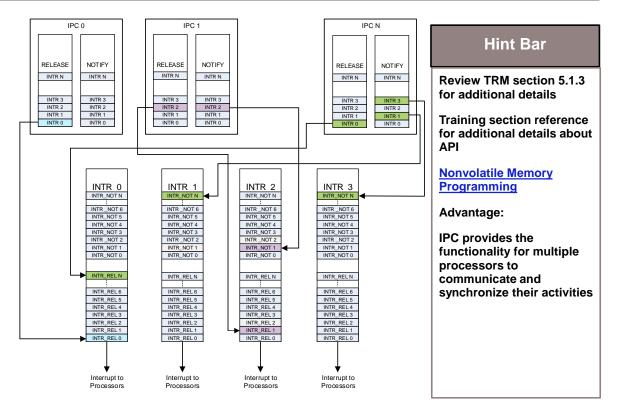

## IPC Channels and Interrupts

- Each IPC interrupt structure<sup>1</sup> configures an interrupt line, which can be triggered by a notify or release event of any IPC channel

- An IPC interrupt can be triggered from any of the IPC channels in the system

- The event generated from an IPC channel can trigger any or multiple interrupt structures

<sup>1</sup> Any processor can use all interrupt structures. However, some interrupt structures are reserved by the ROM API.

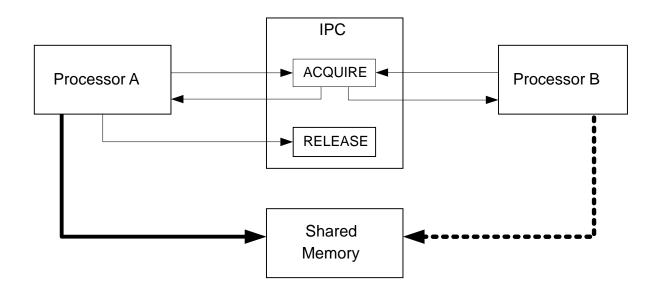

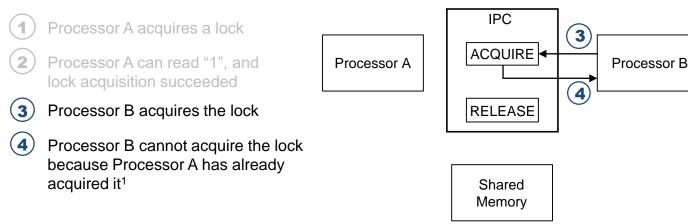

- Implementing Locks

- Example of exclusive control using lock function of IPC

#### Use Case for IPC Channel Structure

- > ACQUIRE: Locks control by reading

- > RELEASE: Unlocks control

| Hint Bar                                                            |  |  |  |

|---------------------------------------------------------------------|--|--|--|

| See the datasheet for the<br>number of IPC channels<br>implemented  |  |  |  |

| Review TRM section 5.1.1<br>for additional IPC Channel<br>details   |  |  |  |

| Review TRM section 5.1.2<br>for additional IPC Interrupt<br>details |  |  |  |

|                                                                     |  |  |  |

|                                                                     |  |  |  |

|                                                                     |  |  |  |

Implementing Locks

**Hint Bar**

memory

A and B

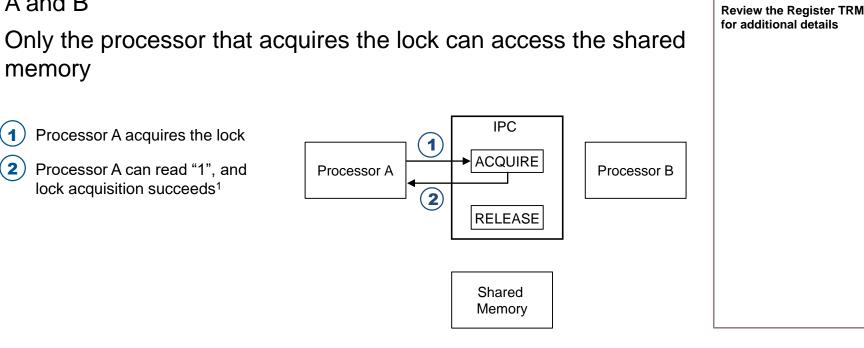

Processor A acquires the lock

Processor A can read "1", and lock acquisition succeeds<sup>1</sup>

<sup>1</sup> If read ACQUIRE.SUCCESS = 1, the read acquired the lock. If read ACQUIRE.SUCCESS = 0, the read did not acquire.

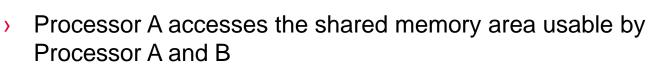

Processor A accesses shared memory area usable by Processor

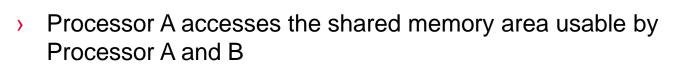

#### Implementing Locks

Only the processor that acquires the lock can access the shared memory

<sup>1</sup> If another processor has already acquired the lock, register reading is "0" (lock cannot be acquired).

**Hint Bar**

Review the Register TRM for additional details

#### Implementing Locks

Only the processor that acquires the lock can access the shared memory

5)

Processor A acquires a lock

- Processor A can read "1", and lock acquisition succeeded

- Processor B acquires lock

- Processor B cannot acquire lock because Processor A has already acquired it

Processor A accesses shared memory Processor B cannot access shared memory

- Processor A accesses shared memory by acquiring the lock

- - Processor B cannot acquire the lock

**Hint Bar**

Implementation of lock function requires the

software to set rules

#### Implementing Locks

Processor A accesses the shared memory area usable by **Hint Bar** Processor A and B Review TRM section 5.1.3 for additional details Only the processor that acquires the lock can access the shared Advantage: memory Prevents reading or IPC writing from other Processor A acquires a lock processors while writing or reading to shared ACQUIRE Processor A can read "1", and Processor A Processor B memory lock acquisition succeeded Processor B acquires lock RELEASE 6) Processor B cannot acquire lock because Processor A has already Shared acquired it Memory 5 Processor A accesses shared memory Processor B cannot access shared memory 6) Processor A releases the lock after accessing shared memory Both Processor A and Processor B can acquire the lock after release

## Use Case for Message Passing Using IPC

- Message Passing

- Example of short message passing using the DATA register of IPC for communication between processors

#### **Message Passing**

- > IPC Channel Structures

- ACQUIRE: Locks control by reading

- NOTIFY: Generates notification event

- RELEASE: Generates release event

- DATA: Data for message passing

- STATUS: Indicates Lock status of IPC

- > IPC Interrupt Structures

- NOTIFY: Generates NOTIFY interrupt

- RELEASE: Generates RELEASE interrupt

- The interrupts can trigger from any IPC structure

#### Hint Bar

Review TRM section 5.1.1 for additional IPC Channel details

Review TRM section 5.1.2 for additional IPC Interrupt details

#### **Message Passing**

<sup>1</sup> IPC features two 32-bit data registers (DATA/1).

#### **Message Passing**

#### **Message Passing**

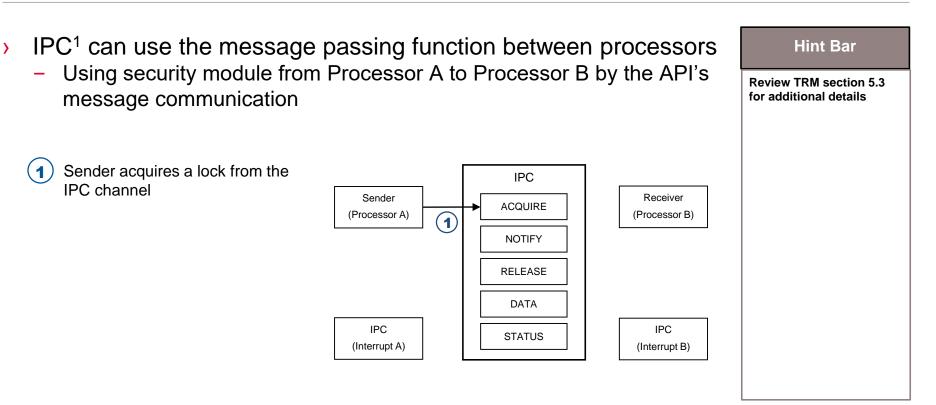

- > IPC can use the message passing function between processors

- Using security module from Processor A to Processor B by the API's message communication

# infin

#### Message Passing

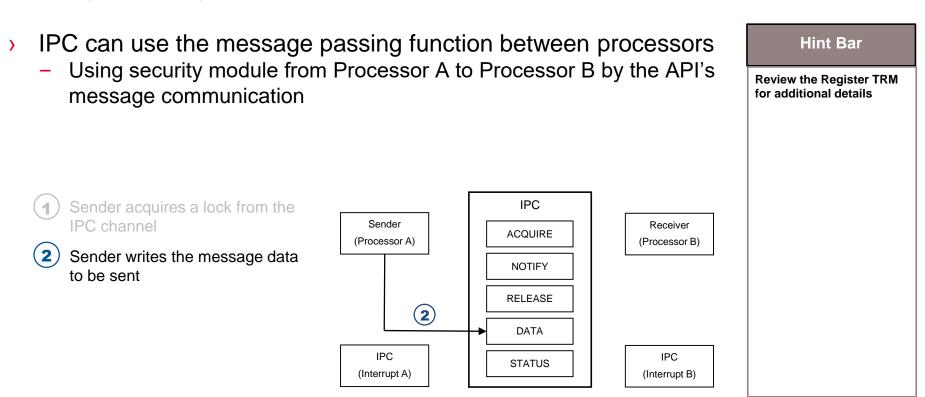

- > IPC can use the message passing function between processors

- Using security module from Processor A to Processor B by the API's message communication

#### **Message Passing**

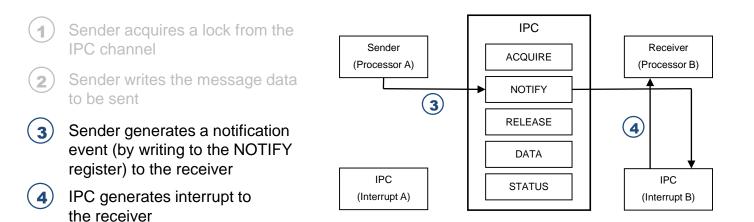

- > IPC can use the message passing function between processors

- Using security module from Processor A to Processor B by the API's message communication

#### Hint Bar

Use Case: Security Module from Main CPU to Secondary CPU by API message communication

If release event was not masked, a release event is generated for the sender

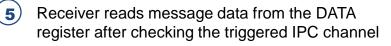

- IPC generates interrupt to the receiver

- 5

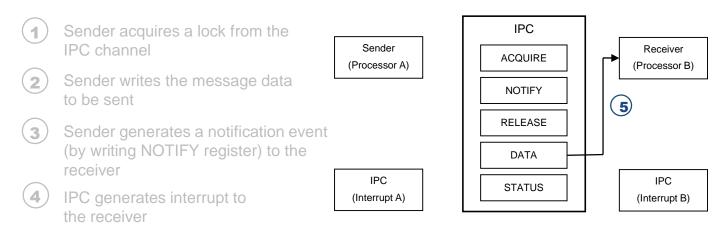

- Receiver reads message data from the DATA register after checking the triggered IPC channel

- Receiver releases the channel using the RELEASE register and also generates a release event

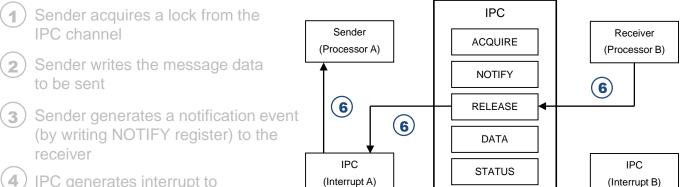

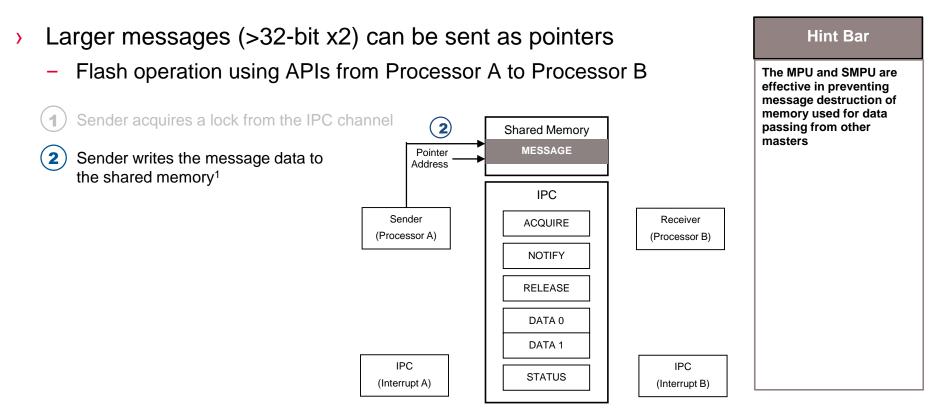

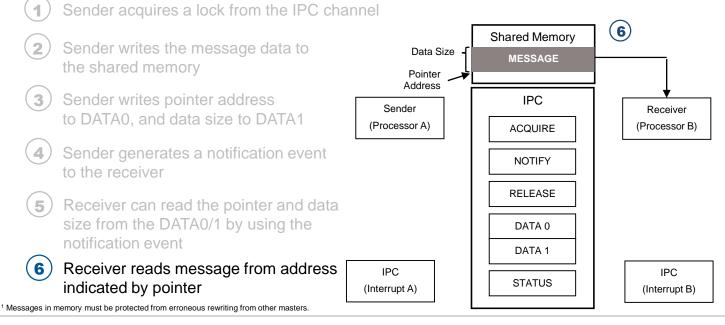

- Large Message Passing

- Example of large message passing using IPC

- Large message passing can be activated by storing message data in shared memory and passing the address pointer of the message data by using the IPC DATA register (the following slides illustrate the large message passing sequence)

- It can make the passed data variable in length by passing the address pointer and size (for example, DATA0 uses address pointer, DATA1 uses data size)

1

#### Large Message Passing

Hint Bar

Review TRM section 5.3 for additional details

- Flash operation using APIs from Processor A to Processor B

Sender acquires a lock from the IPC channel

## Use Case for Large Message Passing

<sup>1</sup> Messages in shared memory must be protected from erroneous rewriting from other masters.

1

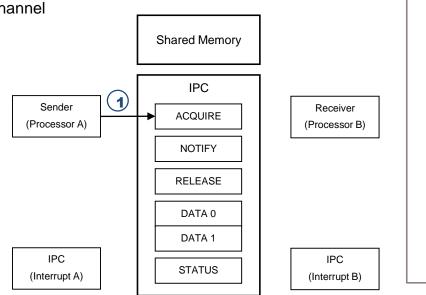

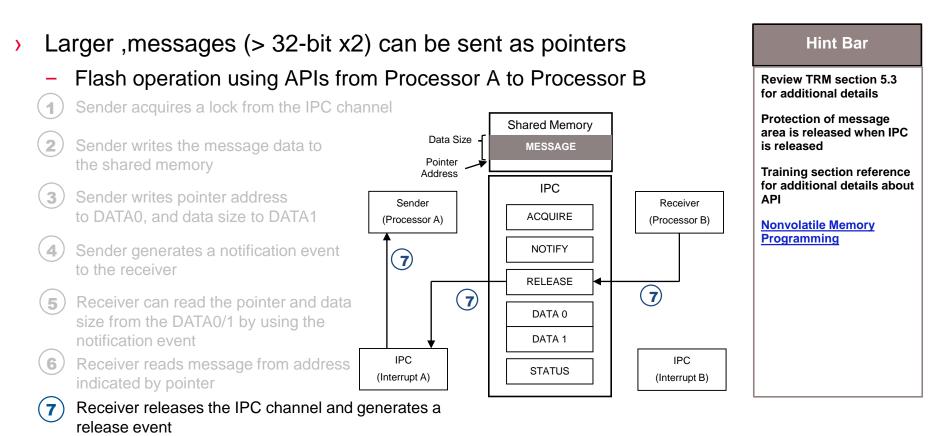

#### Large Message Passing

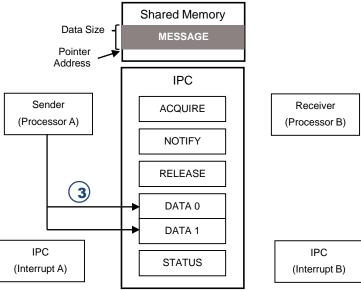

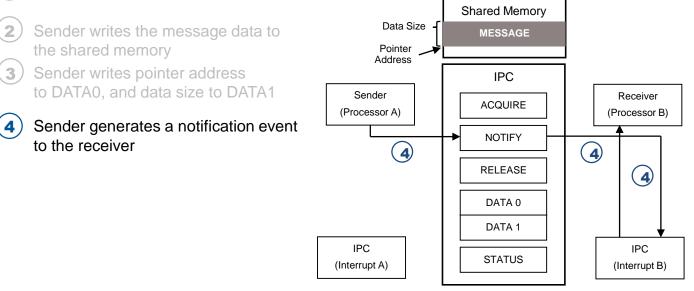

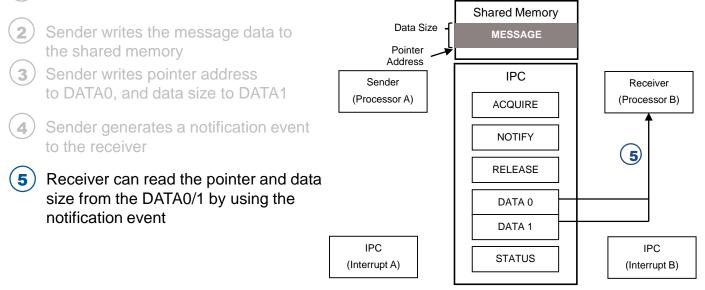

Larger messages (>32-bit x2) can be sent as pointers

- Flash operation using APIs from Processor A to Processor B

- ) Sender acquires a lock from the IPC channel

- 2) Sender writes the message data to the shared memory

- 3 Sender writes pointer address to DATA0, and data size to DATA1

#### Large Message Passing

> Larger messages (>32-bit x2) can be sent as pointers

- Flash operation using APIs from Processor A to Processor B

- ) Sender acquires a lock from the IPC channel

#### Large Message Passing

> Larger messages (>32-bit x2) can be sent as pointers

- Flash operation using APIs from Processor A to Processor B

- ) Sender acquires a lock from the IPC channel

#### Large Message Passing

- > Larger messages (>32-bit x2) can be sent as pointers

- Flash operation using APIs from Processor A to Processor B

### Large Message Passing

## Use Case for Mixing Short and Large Message Using IPC

- > Software requires to set rules according to the situation

- > Case 1: Use a dedicated IPC structure depending on short and large messages

- You can use the IPC6 structure for short messages and IPC7 structure for large messages only

- > Case 2: Use a dedicated IPC interrupt structure depending on short and large messages

- You can use the IPC6 interrupt structure for short messages and IPC7 interrupt structure for large messages only

- Different interrupt handlers are required depending on the message size

- You can use the same IPC channel structure

- > Case 3: Use a dedicated code depending on short and large messages

- Use part of the data register to identify short or large messages (for example, short: 0x05, large: 0x0a)

- The receiver should check the message size

- For short messages, passing data size is up to 64 bits including code and data

**Note:** Some IPC channel and interrupt structures are reserved for API use

# Part of your life. Part of tomorrow.

| Revision | ECN     | Submission<br>Date | Description of Change                                                                                     |

|----------|---------|--------------------|-----------------------------------------------------------------------------------------------------------|

| **       | 6084432 | 03/12/2018         | Initial release                                                                                           |

| *A       | 6390493 | 11/21/2018         | Added slides 2, 7, and 20.<br>Updated slides 3 and 4<br>Deleted IPC Channel/Interrupt Register Structures |

| *В       | 6633414 | 7/22/2019          | Updated slide 2-4.<br>Added slide 5.                                                                      |

| *C       | 7060646 | 01/06/2021         | Updated slide 2-3, 23 - 30.<br>Added slide 31                                                             |