# Customer training workshop TRAVEO<sup>™</sup> T2G CAN FD controller

> Target product list for this training material:

| Family Category                                          | Series            | Code Flash Memory Size |

|----------------------------------------------------------|-------------------|------------------------|

| TRAVEO <sup>™</sup> T2G Automotive Body Controller Entry | CYT2B6            | Up to 576 KB           |

| TRAVEO <sup>™</sup> T2G Automotive Body Controller Entry | CYT2B7            | Up to 1088 KB          |

| TRAVEO <sup>™</sup> T2G Automotive Body Controller Entry | CYT2B9            | Up to 2112 KB          |

| TRAVEO <sup>™</sup> T2G Automotive Body Controller Entry | CYT2BL            | Up to 4160 KB          |

| TRAVEO <sup>™</sup> T2G Automotive Body Controller High  | CYT3BB/<br>CYT4BB | Up to 4160 KB          |

| TRAVEO <sup>™</sup> T2G Automotive Body Controller High  | CYT4BF            | Up to 8384 KB          |

| TRAVEO <sup>™</sup> T2G Automotive Cluster               | CYT2CL            | Up to 4160 KB          |

| TRAVEO <sup>™</sup> T2G Automotive Cluster               | CYT3DL            | Up to 4160 KB          |

| TRAVEO <sup>™</sup> T2G Automotive Cluster               | CYT4DN            | Up to 6336 KB          |

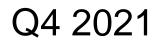

### Introduction to TRAVEO<sup>™</sup> T2G Body Controller Entry

#### CAN FD is part of the peripheral blocks ) **CPU Subsystem** CYT2BL MXS40-HT SWJ/MTB/CTI SWJ/ETM/ITM/CTI eCT Flash CRYPTO M-DMA0 4 Channel P-DMA1 44 Channel P-DMA0 92 Channel ASIL-B SRAM1 Arm Cortex SRAM0 AES. SHA. CRC 4160 KB Code-flash + Arm Cortex M4 M0+ 256 KB 256 KB TRNG, RSA, 128 KB Work-flash

#### \_ \_ \_\_\_\_

**Hint Bar**

#### Review TRM chapter 23 for additional details

ROM

32 KB

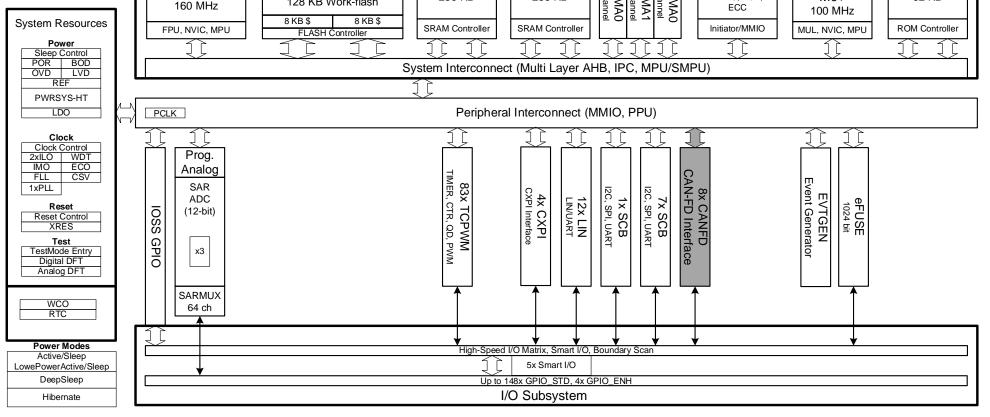

### Introduction to TRAVEO<sup>™</sup> T2G Body Controller High

#### • CAN FD is part of the peripheral blocks

#### Hint Bar

### Review TRM chapter 24 for additional details

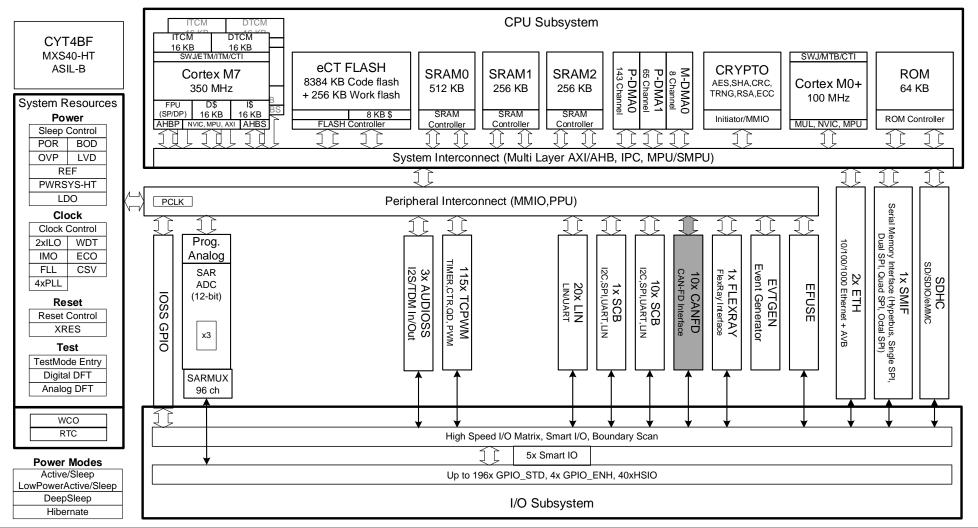

#### Introduction to TRAVEO<sup>™</sup> T2G Cluster

002-22209 \*D, 2021-10-15

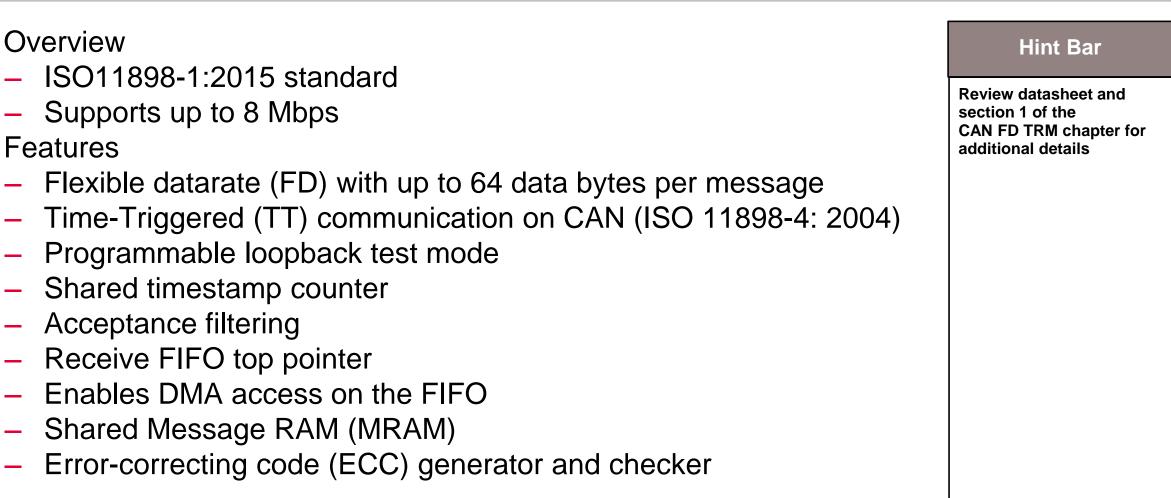

Overview

Features

#### CAN-FD controller overview

Supports up to 8 Mbps

Acceptance filtering

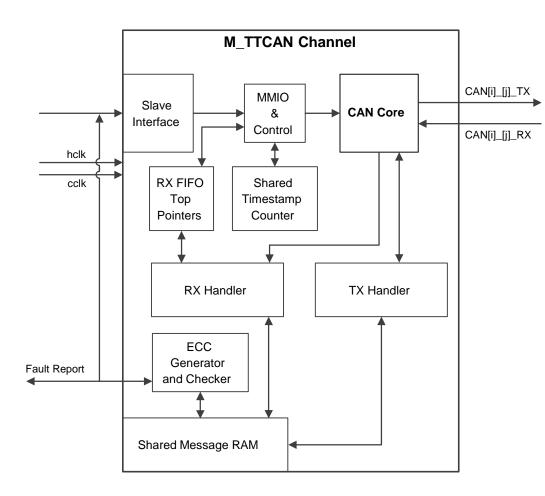

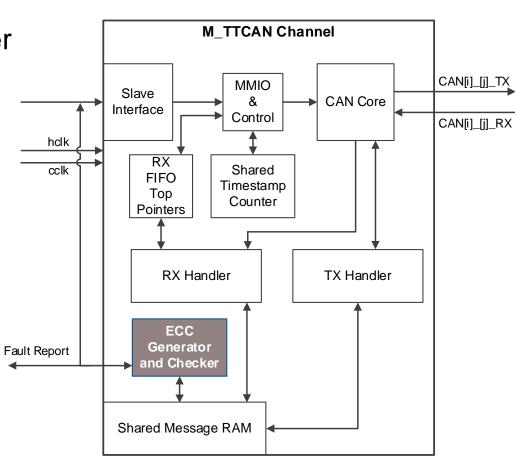

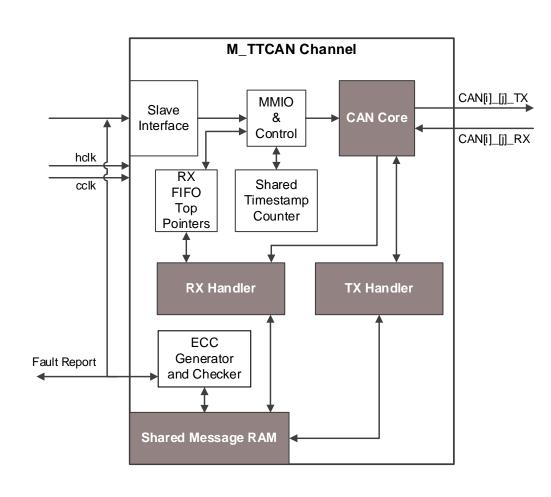

### CAN FD controller block diagram

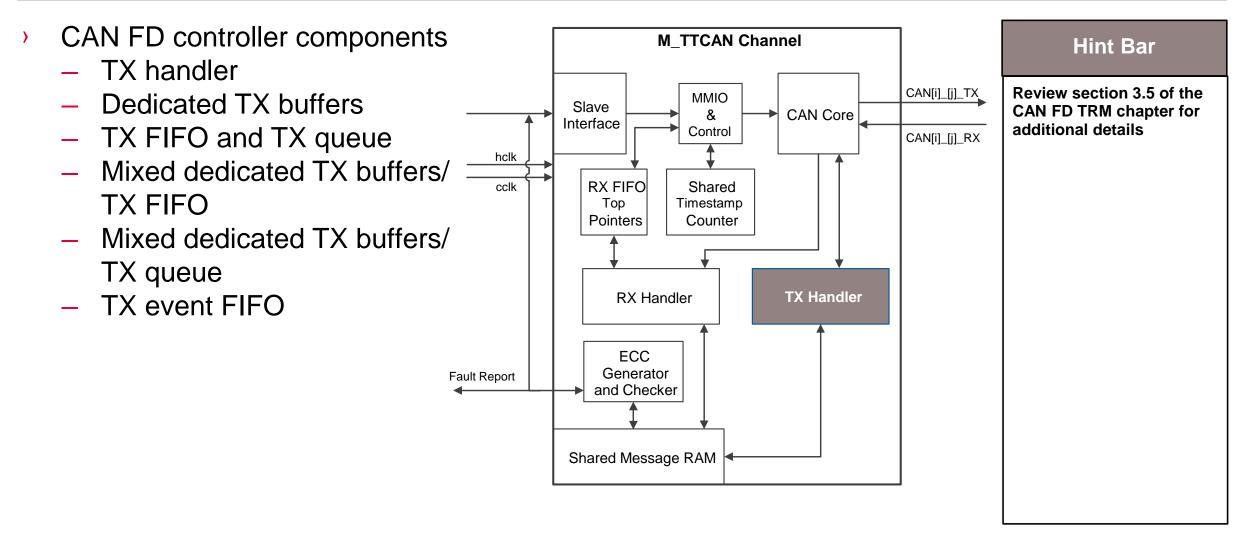

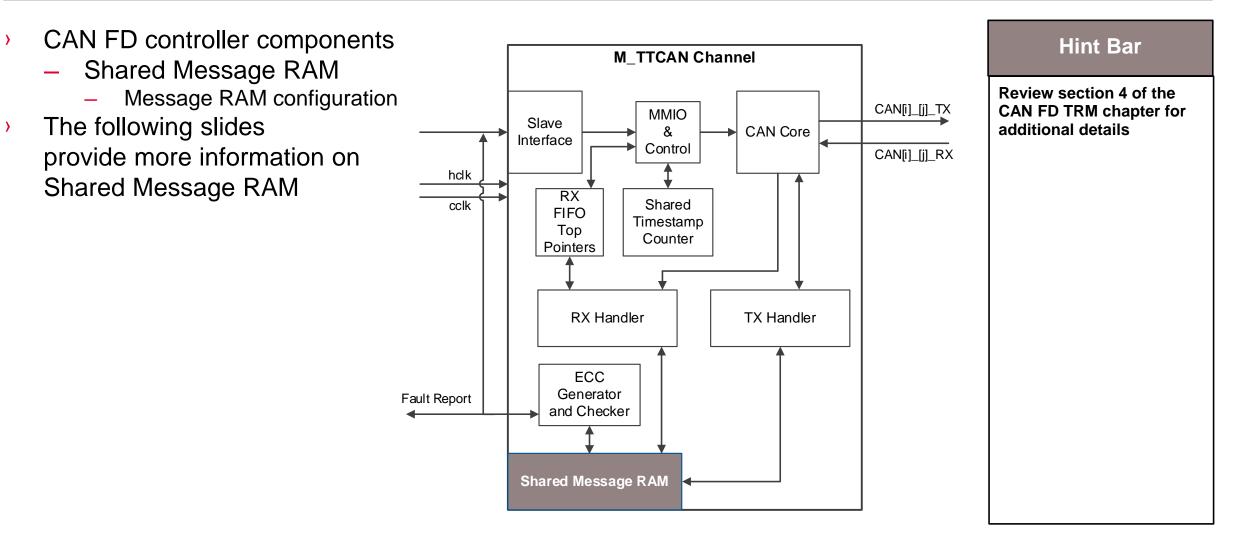

> CAN FD controller components

Hint Bar Review section 2.1 of the CAN FD TRM chapter for additional details

#### CAN core

)

)

)

)

)

Classic CAN & CAN FD operation **Hint Bar M TTCAN Channel** Supports Standard and Extended ID Review section 3.1 of the CAN[i]\_[j]\_TX **Transmitter Delay Compensation** MMIO CAN FD TRM chapter for Slave **CAN** Core & Interface additional details Supports the transmitter delay Control CAN[i]\_[j]\_RX hclk measurement and offset setting **RX FIFO** cclk Shared Power Down Top Timestamp Pointers Counter Supports sleep mode Test mode **RX Handler** TX Handler Supports loopback mode Interrupt ECC Generator Fault Report Two types of interrupts and Checker Shared Message RAM

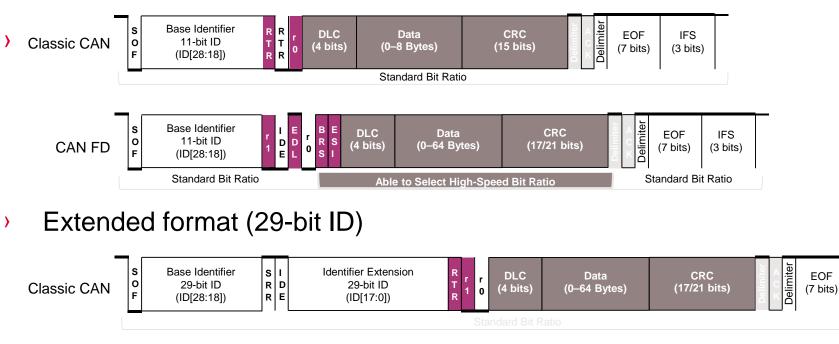

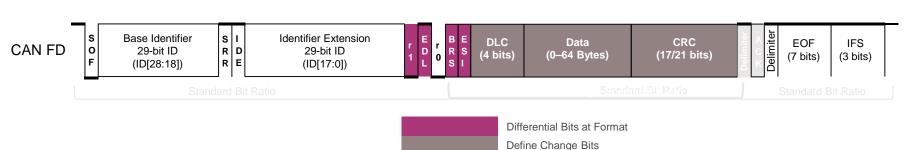

### Classic CAN & CAN FD operation

Standard format (11-bit ID)

IFS

(3 bits)

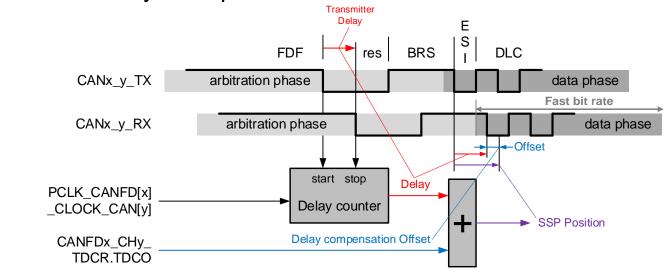

#### Transmitter delay compensation

- > Supports the transmitter delay measurement and offset setting

- > Background

- When transmitting via CANx\_y\_TX, CAN FD controller receives the transmitted data from its local CAN transceiver via CANx\_y\_RX. The received data is delayed by the transmitter delay. In case this delay is greater than TSEG1<sup>1</sup>, a bit error is detected. To enable a data phase bit time that is even shorter than the transmitter delay, the delay compensation is introduced.

- Advantage

- This enables transmission with higher bit rates during the CAN FD data phase, independent of the delay of a specific CAN transceiver

#### **Hint Bar**

Review section 3.1.4 of the CAN FD TRM chapter and Register TRM for additional details

<sup>1</sup> time segment before sample point

#### Power down (Sleep Mode)

- A clock provided to the CAN channel can be stopped by raising a clock stop request through the CTL.STOP\_REQ bit

- After receiving an acknowledge from the CAN channel, hardware automatically stops the clock

- Clearing CTL.STOP\_REQ allows exit from power down mode<sup>1</sup>

- All CAN configurations and MRAM except the timestamp counter are retained during DeepSleep mode

- > Advantages:

- Unlike older approaches, software does not have to wait for an acknowledge and can be used for other functionality

- Power down (stopping clock) reduces power consumption when the CAN bus is idle

#### Hint Bar

Review section 3.1.8 of the CAN FD TRM chapter and Register TRM for additional details

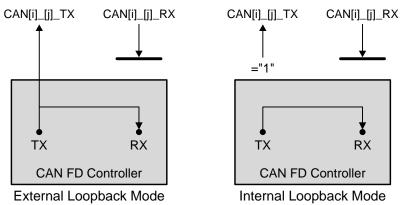

#### Test mode

- > External loopback mode

- Ignores acknowledge errors (recessive bit sampled in the acknowledge slot of a data/remote frame) in loopback mode

- Performs an internal feedback from TX output to RX input

- Transmitted messages can be monitored at the CAN[i]\_[j]\_TX pin

- Internal loopback mode

- Can be tested without affecting a running CAN system connected to the CAN[i]\_[j]\_TX and CAN[i]\_[j]\_RX pins

- > Use case

- CAN diagnosis without the influence of external ECU<sup>1</sup>

by using the internal loopback mode

#### **Hint Bar**

Review section 3.1.9 of the CAN FD TRM chapter and Register TRM for additional details

<sup>1</sup> Electrical Control Unit

Interrupt

#### 002-22209 \*D, 2021-10-15

13

#### Each interrupt source in the M\_TTCAN channel can be separately enabled or > disabled using the IE register

Each enabled interrupt from the channel can be routed either to the interrupt 0 or > interrupt 1 line using the ILS and ILE registers. By default, all interrupts are routed to the interrupt 0 line

Hint Bar

Review section 2.3 of the CAN FD TRM chapter and **Register TRM for** additional details

The description of the IE register in the Register TRM provides a list of all possible interrupt sources

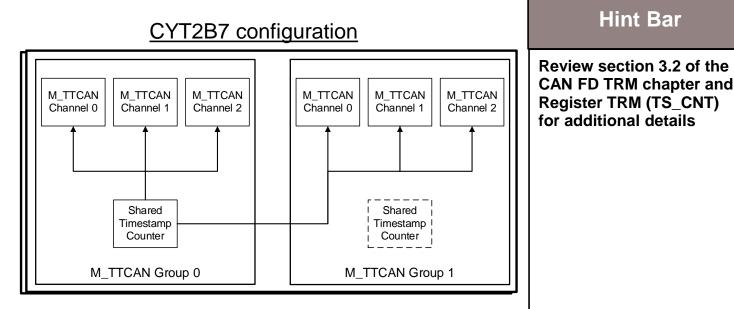

#### Shared timestamp

The shared timestamp counter supports a 16-bit timestamp value. > Hint Bar M TTCAN Channel Review section 3.2 of the **CAN FD TRM chapter for** additional details CAN[i]\_[j]\_TX MMIO Slave CAN Core & Interface Control CAN[i]\_[j]\_RX hclk RX Shared cclk FIFO Timestamp Тор Counter Pointers **RX** Handler TX Handler ECC Generator Fault Report and Checker Shared Message RAM

#### Shared timestamp counter

- The timestamp counter records a 16-bit timestamp value when messages are sent or received

- The captured timestamp value is stored in the respective buffer or FIFO element

- > Advantage:

- To make event ordering global in the device, the 16-bit timestamp counter is shared among all M\_TTCAN channels

# infineon

#### 002-22209 \*D, 2021-10-15

**RX FIFO** Shared cclk Тор Timestamp Counter **Pointers RX Handler** TX Handler ECC Generator Fault Report and Checker Shared Message RAM

M TTCAN Channel

CAN Core

MMIO

&

Control

Slave

Interface

hclk

#### CAN FD controller components

> RX Handler

**RX** handler

- Acceptance filtering

- Dedicated RX buffers

- RX FIFOs

- > RX FIFO top pointers

#### Hint Bar

Review section 3.4 of the CAN FD TRM chapter for additional details.

CAN[i]\_[j]\_TX

CAN[i]\_[j]\_RX

#### Acceptance filtering

- > Two sets of acceptance filters

- For standard identifiers

- For extended identifiers

- > Features

- Each filter element<sup>1</sup> can be configured as

- Range filter (from to)

- Filter for one or two dedicated IDs

- Classic bit mask filter

- Each filter element is configurable for acceptance or rejection filtering

- Each filter element can be enabled/disabled individually

- Filters are checked sequentially from element #0 until the first match

| ы | int | Rar |

|---|-----|-----|

|   |     | Dal |

Review section 3.4.1 of the CAN FD TRM chapter and Register TRM for additional details

<sup>1</sup> A filter element is a condition of the filtering list. There can be up to 192 filter elements

#### 18

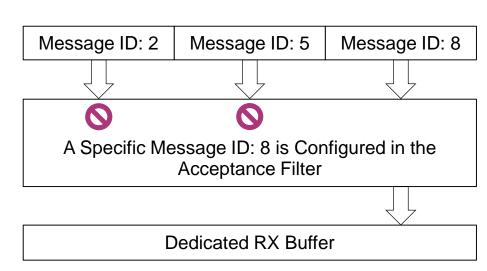

#### **Dedicated RX buffers**

- Up to 64 dedicated RX buffers

- After a received message is accepted by a filter element, the message is stored in the RX Buffer in the Message RAM referenced by the filter element

- > Use case

- Receive only the specific message ID (8) with the dedicated RX buffer and acceptance filter

- > Advantage

- Accepts frames only with specific message IDs

#### **Hint Bar**

Review section 3.4.3 of the CAN FD TRM chapter and Register TRM for additional details

Hint Bar

Review section 3.4.2 of the

CAN FD TRM chapter and

Register TRM for additional details

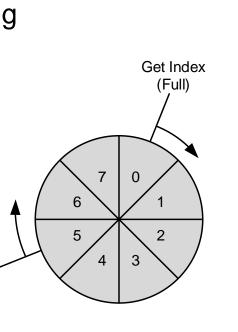

## RX FIFOs

- > RX FIFOs can be configured to hold up to 64 elements each

- Received messages that pass acceptance filtering are transferred to the RX FIFO as configured by the matching filter element

- > When the RX FIFO Put Index reaches the RX FIFO Get Index, the RX FIFO Full condition interrupt flag is set

- Watermark interrupt

- To avoid RX FIFO overflow, use the RX FIFO Watermark interrupt

- > Use case

- The RX FIFO watermark interrupt flag can be used to trigger DMA

Put Index

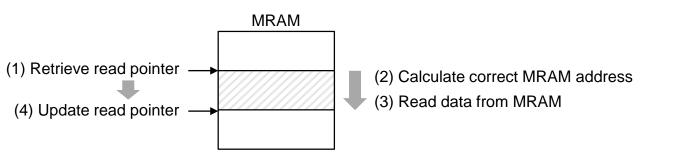

### **RX FIFO top pointer**

> Tracks the number of message data words read, and updates the pointer information after reading the last word

- Provides a single location<sup>1</sup> to read the data

- Advantages

- Reduces the software process to retrieve the read pointer, calculate correct MRAM address, and update the read pointer

- Reduces bus load and latency

- Enables DMA on FIFOs

| ulate |  |

|-------|--|

|       |  |

|       |  |

**Hint Bar**

Review section 3.4.2 of the CAN FD TRM chapter and Register TRM for additional details

<sup>1</sup> RXFTOP0\_DATA for RX FIFO0, RXFTOP1\_DATA for RX FIFO1

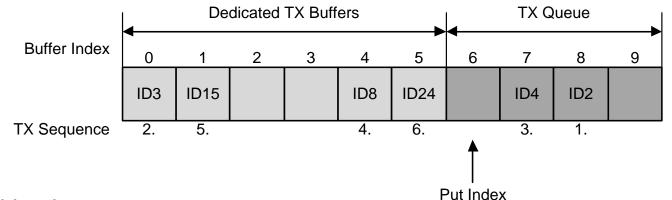

### TX handler

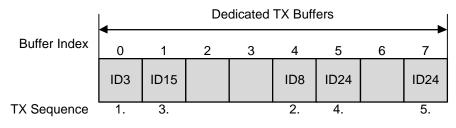

#### **Dedicated TX buffers**

- > Each 32-bit dedicated TX buffer is configured with a specific Message ID

- If multiple TX buffers are configured with the same Message ID, the TX buffer with the lowest buffer number is transmitted first

> Dedicated TX buffers allocate "Element Size" 32-bit words in the MRAM

TX Buffer/FIFO/Queue Element Size

| Data Field<br>[bytes] | Element Size<br>[RAM words] |

|-----------------------|-----------------------------|

| 8                     | 4                           |

| 12                    | 5                           |

| 16                    | 6                           |

| 20                    | 7                           |

| 24                    | 8                           |

| 32                    | 10                          |

| 48                    | 14                          |

| 64                    | 18                          |

Review section 3.5.2 of the CAN FD TRM chapter and Register TRM (TXESC.TBDS) for additional details

Hint Bar

## TX FIFO and TX Queue

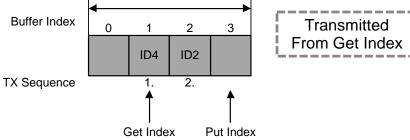

#### > TX FIFO

- Messages stored in the TX FIFO are transmitted starting with the message referenced by the Get Index<sup>1</sup>

- After each transmission, the Get Index is incremented cyclically until the TX

FIFO is empty

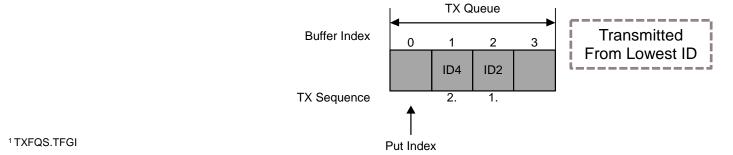

#### > TX Queue

- Messages stored in the TX queue are transmitted starting with the message with the lowest Message ID (highest priority)

- If multiple TX queues are configured with the same Message ID, the TX queue with the lowest buffer number is transmitted first

#### Hint Bar

Review sections 3.5.3 and 3.5.4 of the CAN FD TRM chapter and Register TRM for additional details

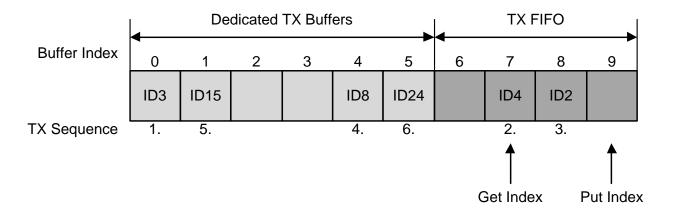

### Mixed dedicated TX buffers/TX FIFO

The MRAM TX buffer section is subdivided into a set of dedicated TX buffers and TX FIFO

Hint Bar

Review section 3.5.5 of the CAN FD TRM chapter and Register TRM for additional details

- > TX prioritization

- Scan dedicated TX buffers and the oldest pending TX FIFO buffer (referenced by Get Index)

- The TX buffer with the lowest Message ID has the highest priority and is transmitted next

### Mixed dedicated TX buffers/TX queue

The MRAM TX buffer section is subdivided into a set of dedicated TX buffers and a TX queue

Hint Bar

Review section 3.5.6 of the CAN FD TRM chapter and Register TRM for additional details

- > TX prioritization

- Scan all TX buffers with an activated transmission request

- The TX buffer with the lowest Message ID has the highest priority and is transmitted next

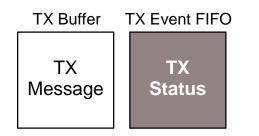

## TX Event FIFO

- > Message ID and timestamp are stored in the TX Event FIFO element

- > Can be configured to a maximum of 32 elements

- > Use case

- A TX buffer holds only the message to be transmitted, while the transmit status is stored separately in the TX Event FIFO

- > Advantages

- When operating a dynamically managed transmit queue, a TX buffer can be used for a new message immediately after successful transmission

- It is not necessary to save transmit status information from a TX buffer before overwriting that TX buffer

#### Hint Bar

Review section 3.5.8 of the CAN FD TRM chapter and Register TRM for additional details

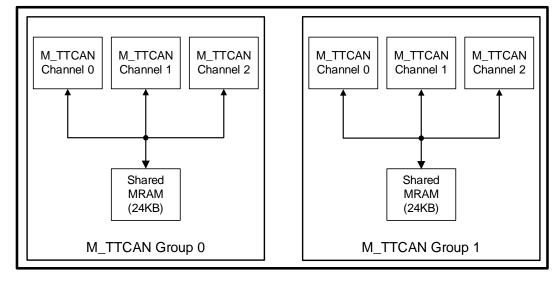

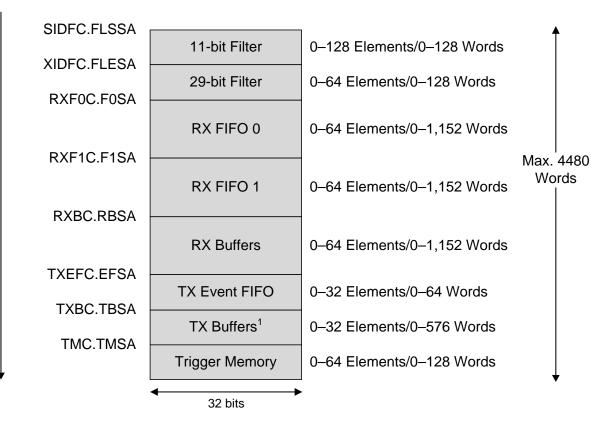

### Message RAM

#### Shared Message RAM

- Message RAM in the TRAVEO<sup>™</sup> T2G family devices is shared among multiple M\_TTCAN channels in the M\_TTCAN group

- Following is the CYT2B7 Message RAM<sup>1</sup> diagram

Hint Bar Review section 4 of the CAN FD TRM chapter and Register TRM for additional details Note: Message RAM cannot be used for system RAM

- > Advantage

- Each M\_TTCAN channel in the module can configure its required message RAM according to the needs of the application

<sup>1</sup> CYT2B9: 32KB among four channels, CYT4BF: 40KB among five channels

**Hint Bar**

Review section 4 of the CAN FD TRM chapter and

Register TRM for additional details

### Message RAM configuration

- > Filter and messages are managed separately

- > Sent and received messages are managed separately

#### Start Address

<sup>1</sup> The TX Buffer section can be configured to hold dedicated TX Buffers as well as a TX FIFO/TX Queue

### Turning Message RAM OFF

Message RAM can be turned off to save power by setting the CTL.MRAM\_OFF bit

Default value of this bit is '0' and MRAM is retained in this configuration during DeepSleep power mode

All M\_TTCAN channels must be powered down before setting the MRAM OFF bit

### ECC generator and checker

- > CAN FD components

- ECC generator and checker

- Single-error correction

- Double-error detection

- ECC-error injection

- Address error

Hint Bar

Review section 4.8 of the CAN FD TRM chapter for additional details

### ECC generator and checker (1/2)

- Single-bit error correction and double-bit error detection (SECDED)

- SEC report action:

- Report to the fault subsystem

- > DED report action:

- Report to master

- In the case of an AHB master, a bus error occurs

- In the case of an M\_TTCAN channel, the M\_TTCAN channel shuts down immediately

- Interrupt

- Report to the fault subsystem

- > Software ECC error injection support

- > Use case

- SEC report: Not needed because single-bit error is corrected automatically

- DED report: Use for failsafe operation such as stop system control

- ECC error injection: Use for initial diagnosis of ECC before application running

Review section 4.8 of the CAN FD TRM chapter and Register TRM for additional details

## ECC generator and checker (2/2)

- > Address error

- > Detects when TTCAN or MCU is trying to access out-of-range MRAM<sup>1</sup>

- > Unlike ECC errors, this can happen for both writes and reads

- Report action:

- Read from M\_TTCAN master:

- To prevent sending corrupt data, shut down the M\_TTCAN channel immediately

- Interrupt

- Read from the AHB interface:

- Bus error

- Any case (read, write, and any master):

- Report to the fault subsystem

- > Advantage

- Makes software debugging easier

| н | int | Bar |

|---|-----|-----|

|   |     | Dai |

Review section 4.8.3 of the CAN FD TRM chapter and Register TRM for additional details

<sup>&</sup>lt;sup>1</sup> CYT2B7: 24KB, CYT2B9: 32KB, CYT4BF: 40KB

#### TTCAN

- > TTCAN operation

- Reference message

- Message scheduling

- Trigger memory

- Schedule initialization

- TTCAN gap control

- Stop watch

- TTCAN error level

- TTCAN message handling

#### Hint Bar

Review section 4.8.3 of the CAN FD TRM chapter and Register TRM for additional details

#### Reference message

- A data frame characterized by a specific CAN identifier

- Received and accepted by all nodes except the Time Master (sender > of the reference message)

- Level 1 )

- Data length must be at least one

- Level 0, 2 )

- Data length must be at least four

- Extended by other data up to the sum of eight CAN data bytes )

- All bits of the identifier except the three LSBs characterize the > message as a reference message

- The last three bits specify the priorities of up to eight potential time ) masters

Review section 5.1 of the **CAN FD TRM chapter for** additional details

Hint Bar

#### Message scheduling

- TTOCF.TM controls whether M\_TTCAN operates as a potential time master or as a time slave

- If it is a potential time master, the three LSBs of the reference message's identifier, TTRMC.RID, define the master priority:

- 0: Highest priority

- 7: Lowest priority

Review section 5.2.2 of the CAN FD TRM chapter and Register TRM for additional details

#### Trigger memory

- > Part of the Message RAM

- > Stores up to 64 trigger elements

- > A trigger memory element consists of:

- Time mark (TM)

- Cycle code (CC)

- Trigger type (TYPE)

- Filter type (FTYPE)

- Message number (MNR)

- Message status count (MSC)

- Time mark event internal (TMIN)

- Time mark event external (TMEX)

- Asynchronous serial communication (ASC)

| ы | int | Bar |  |

|---|-----|-----|--|

|   | ΠΠ  | Dal |  |

Review section 5.2.3 and 4.7 of the CAN FD TRM chapter for additional details

### TTCAN schedule initialization

- Synchronization to M\_TTCAN's message schedule starts when CCCR.INIT is reset

- M\_TTCAN can operate strictly time-triggered (TTOCF.GEN = 0) or external event-synchronized time-triggered (TTOCF.GEN = 1)

- All nodes start with cycle time zero at the beginning of their trigger list with TTOST.SYS = 00 (out of synchronization); no transmission is enabled with the exception of the reference message

Review section 5.2.4 of the CAN FD TRM chapter and Register TRM for additional details

### **TTCAN** gap control

- All functions related to gap control apply only when M\_TTCAN is operated in external event-synchronized time-triggered mode (TTOCF.GEN = '1')

- TTCAN message schedule can be interrupted by inserting gaps between basic cycles of the system matrix

- During a gap, all transmissions are stopped and the CAN bus remains idle

- A gap is finished when the next reference message starts a new basic cycle

- A gap starts at the end of a basic cycle that itself was started by a reference message with bit Next\_is\_Gap = '1'

Basic Cycle Gap Basic Cycle

- > Use case

- Gaps are initialized by the current time master

#### Hint Bar

Review section 5.3 of the CAN FD TRM chapter and Register TRM for additional details

#### Stop watch

- The stop watch function enables capturing of M\_TTCAN internal time values (local time, cycle time, or global time) triggered by an external event

- To enable the stop watch function, the application program must first ) define local time, cycle time, or global time as the stop watch source via TTOCN.SWS

#### Hint Bar

Review section 5.4 of the CAN FD TRM chapter and **Register TRM for** additional details

#### TTCAN error level

- > ISO 11898-4 specifies four levels of error severity

- S0: No error

- S1: Warning

- Only notification of application; reaction is application-specific

- S2: Error

- Notification of application. All transmissions in exclusive or arbitrating time windows are disabled (no data or remote frames may be started)

- Potential time masters still transmit reference messages with the reference trigger offset TTOST.RTO set to the maximum value of 127

- S3: Severe error

- Notification of application. All CAN bus operations are stopped (transmission of dominant bits is not allowed) and CCCR.MON is set. The S3 error condition remains active until the application updates the configuration (set CCCR.CCE)

#### Hint Bar

Review section 5.7 of the CAN FD TRM chapter and Register TRM for additional details

### TTCAN message handling

- > Reference message

- For potential time masters, the identifier of the reference message is configured via TTRMC.RID

- No dedicated TX buffer is required for transmission of the reference message

- When a reference message is transmitted, the first data byte (TTCAN Level 1) corresponding to the first four data bytes (TTCAN Level 0 and Level 2) will be provided by the Frame Synchronization Entry (FSE)<sup>1</sup>

- Message reception

- Message reception is done via the two RX FIFOs, similar to event-driven CAN communication

- Message transmission

- For time-triggered message transmission, M\_TTCAN supplies 32 dedicated TX buffers

- TX FIFO or TX queue is not available when M\_TTCAN is configured for time-triggered operation (TTOCF.OM = "01" or "10")

Review section 5.8 of the CAN FD TRM chapter and Register TRM for additional details

Hint Bar

<sup>&</sup>lt;sup>1</sup> Frame Synchronization Event (FSE) occurs at the sample point of each Start-of-Frame (SoF) bit

# Part of your life. Part of tomorrow.

Copyright © Infineon Technologies AG 2021. All rights reserved.

### **Revision history**

| Revision | ECN     | Submission date | Description of change                                                                            |

|----------|---------|-----------------|--------------------------------------------------------------------------------------------------|

| **       | 6144419 | 04/25/2018      | Initial release                                                                                  |

| *A       | 6362522 | 10/24/2018      | Added pages 2, 4, 5, 29, and 33 to 41, and note descriptions in all pages.<br>Updated page 3.    |

| *В       | 6585632 | 05/31/2019      | Updated pages 2, 3, 4, 14, 21, 26, 27, 32, 41.<br>Added page 5.                                  |

| *C       | 7033664 | 11/30/2020      | Updated page 2 and 8, and added page 10.<br>Merged page 3 for TRAVEO™ T2G Body Controller Entry. |

| *D       | 7397171 | 10/15/2021      | Updated page 1 to 5, 7.                                                                          |