# Customer Training Workshop Traveo™ II Body High and Cluster 2D Clock System

# **Target Products**

# Target product list for this training material

| Family Category                            | Series     | Code Flash Memory Size |

|--------------------------------------------|------------|------------------------|

| Traveo™ II Automotive Body Controller High | CYT3BB/4BB | Up to 4160KB           |

| Traveo II Automotive Body Controller High  | CYT4BF     | Up to 8384KB           |

| Traveo II Automotive Cluster               | CYT3DL     | Up to 4160KB           |

| Traveo II Automotive Cluster               | CYT4DN     | Up to 6336KB           |

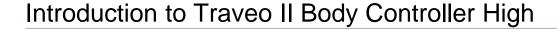

## The clock system is part of the System Resources block

#### **Hint Bar**

Review TRM chapter 18 for additional details

Training section reference

Clock System for Traveo II Body Entry

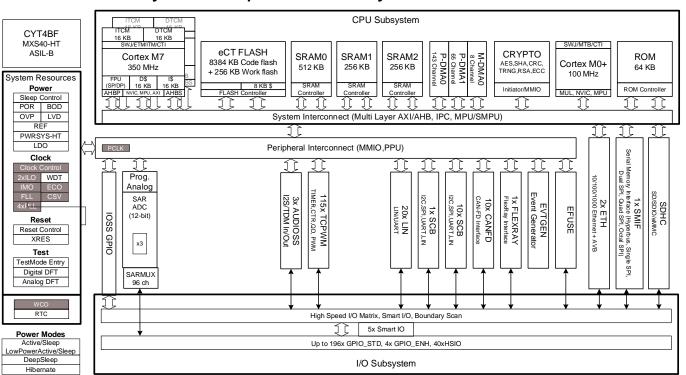

## Introduction to Traveo II Cluster

## The clock system is part of the System Resources block

#### **Hint Bar**

Review TRM chapter 18 for additional details

## **Clock System Overview**

#### Features

- Internal clock sources

- IMO: Internal main oscillator (8 MHz)

- ILO0/1: Internal low-speed oscillator (32.768 kHz)

- External clock sources

- ECO: External crystal oscillator

- WCO: Watch crystal oscillator

- EXT\_CLK: External clock generated using a signal through the I/O pin Also possible to output the internal clock

- LPECO¹: Low-power external crystal oscillator

- Clock generation

- Phase-locked loops (PLL) with and without SSCG<sup>2</sup> and fractional operation<sup>3</sup>

- Frequency-locked loop (FLL)

- Clock supervision (CSV) to detect clock abnormality

- Clock calibration counter

Review TRM chapter 18 for additional details

Hint Bar

<sup>&</sup>lt;sup>1</sup> CYT4BF dose not have LPECO

<sup>&</sup>lt;sup>2</sup> Spread Spectrum Clock Generation

<sup>&</sup>lt;sup>3</sup> Fractional operation provides an output frequency that is a fractional multiple of the input frequency

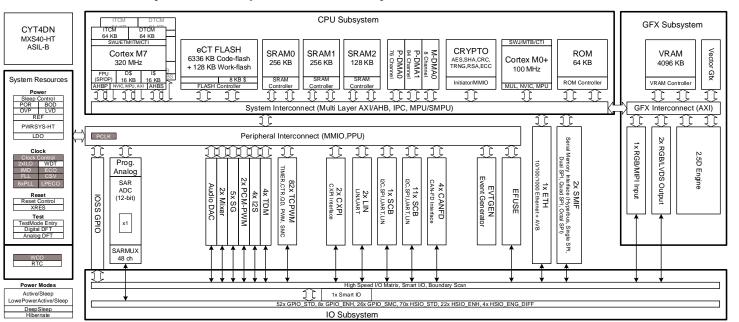

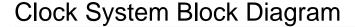

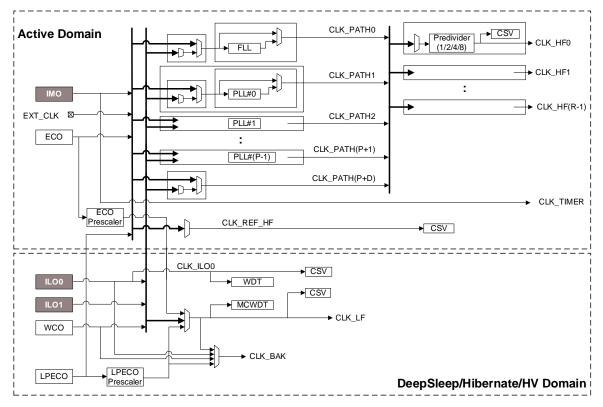

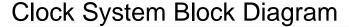

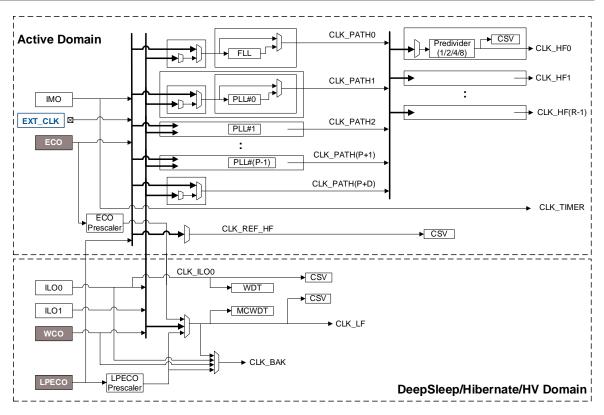

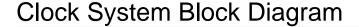

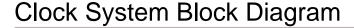

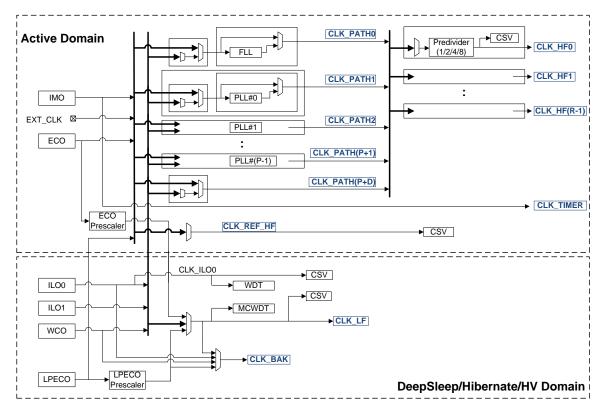

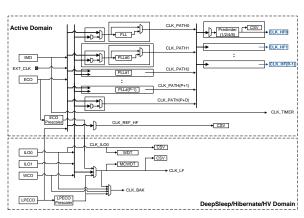

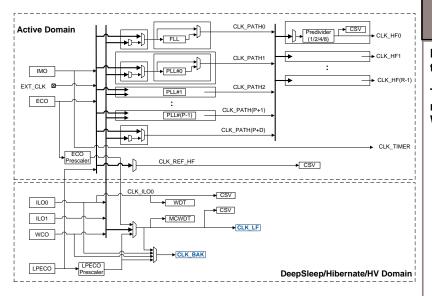

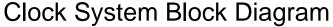

# Clock System Block Diagram

Clock system components

D: The number of direct select paths

P: The number of PLLs

R: The number of clock roots (CLK\_HF)

See the device datasheet for the number of D, P, and R

- Clock system components

- Internal clock sources

- IMO

- ILO 0/1

## Internal Clock Sources (1/2)

- IMO: Internal main oscillator

- Produces an 8-MHz fixed-frequency clock

- An accurate, high-speed internal (crystal-less) oscillator

- Available only in Active and Sleep modes

- Default clock source after POR or any other reset

- Used by PLLs to generate a wide range of high-frequency clocks

- Enabled and disabled by register<sup>1</sup>

- Default is ENABLE<sup>2</sup>

#### **Hint Bar**

Review TRM section 18.2 for additional details

<sup>&</sup>lt;sup>1</sup> IMO should not be disabled if it is the source of the clock path to CLK\_HF[0] <sup>2</sup> Refer to the Register TRM (CLK\_IMO\_CONFIG) for additional details

# Internal Clock Sources (2/2)

## ILO 0/1: Internal low-speed oscillator

- ILO0

- Produces a 32.768-kHz nominal fixed-frequency clock

- Low power and low accuracy

- Available in all power modes

- Always the source of the watchdog timer (WDT)<sup>1</sup>

- ILO1

- Used for ILO0 clock monitoring

- Parameters for ILO1 are the same as ILO0

#### **Hint Bar**

Review TRM section 18.2 for additional details

<sup>&</sup>lt;sup>1</sup> Always leave the ILO enabled because it is the source of the watchdog timer

- Clock system components

- External clock sources

- ECO

- WCO

- EXT\_CLK

- LPECO

## External Clock Sources (1/3)

- ECO: External crystal oscillator

- Contains an oscillator to drive an external up to 33.34-MHz crystal

- Used by PLLs to generate a wide range of high-frequency clocks

- ECO prescaler

- ECO trimming

- Enabled and disabled by register<sup>1</sup>

- Default is DISABLE

- WCO: External low-frequency watch crystal oscillator

- Highly accurate 32.768-kHz clock source

- Primary clock source for the real-time clock (RTC)

- Enabled and disabled by register<sup>2</sup>

- Default is DISABLE

#### **Hint Bar**

Review TRM section 18.2 for additional details

<sup>&</sup>lt;sup>1</sup> Refer to the Register TRM (CLK\_ECO\_CONFIG) for additional details

<sup>&</sup>lt;sup>2</sup> Refer to the Register TRM (CTL) for additional details

## External Clock Sources (2/3)

## ECO Trimming

- ECO supports a wide variety of crystals and ceramic resonators

- ECO can be configured by register¹

- The following trim bit fields can be configured to control the maximum peak oscillation voltage across the crystal (V<sub>P</sub>), the transconductance (gm), and the nominal frequency (f):

- ATRIM (Amplitude Trim by AGC)

- GTRIM (Gain Trim)

- WDTRIM (Watchdog Trim)

- FTRIM (Filter Trim)

- RTRIM (Feedback Resistor Trim)

Max peak value:

$$V_P = \frac{\sqrt{\frac{D_L}{2ESR}}}{\pi f(C_0 + C_L)}$$

f: Fundamental frequency of the crystal (XTAL)

D<sub>L</sub>: Maximum drive level of XTALESR: Equivalent series resistanceC<sub>0</sub>: Shunt capacitance of XTAL

C<sub>L</sub>: Parallel load capacitance of XTAL

Transconductance:  $g_m > 20 \times ESR \times (2\pi \times f)^2 \times (C_0 + C_L)^2$

$$Negative \ resistance \colon |R_{neg}| = \frac{g_{m} \times 4 \times C_{L}^{\,2}}{(2\pi \times f)^{2} \times (4 \times C_{L}^{\,2} + 4 \times CL \times C_{0})^{2}}$$

#### **Hint Bar**

Review TRM section 18.2 for additional details

## External Clock Sources (3/3)

- EXT\_CLK: External clock

- 0.25- to 100-MHz¹ clock that can be sourced from a designated I/O pin

- Can be used as the source clock for either the PLL or FLL

- Can be used as the output for the internal clock (CLK\_HF3 is available)

- When using a pin as input or output to EXT\_CLK, I/O must be set appropriately

- LPECO: Low-power external crystal oscillator

- 3.99- to 8.01-MHz clock source

- Support only cluster product

- Can operate in Active, LPACTIVE, Sleep, LPSLEEP, DeepSleep, and Hibernate

- Can generate CPU and peripheral clock source in conjunction with PLLs

- Can use a real-time-clock (RTC) source instead of WCO

- LPECO prescaler

- Enabled and disabled by register<sup>2</sup>

- Default is DISABLE

#### **Hint Bar**

Review TRM section 18.2 for additional details

<sup>&</sup>lt;sup>1</sup> Refer to datasheet for the target product

<sup>&</sup>lt;sup>2</sup> Refer to the Register TRM (BACKUP LPECO CTL) for additional details

- Clock system components

- High-speed clock generation

- PLL

- FLL

## Clock Generation

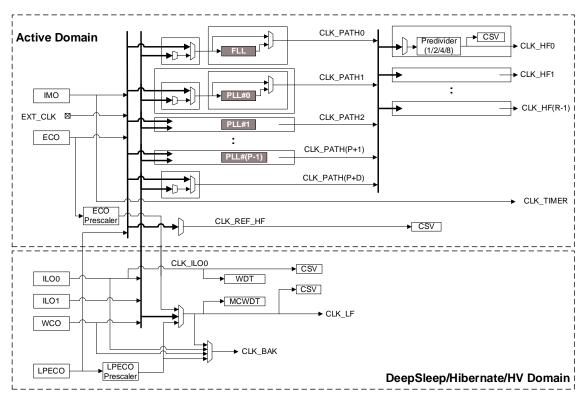

- PLL: Phase-locked loop

- Input clock can be IMO (8 MHz), ECO, or EXT CLK

- Two types of PLL: PLL and PLL400

- PLL without SSCG and fractional operation<sup>1</sup>

- Input clock range: 3.988 to 33.34 MHz (CYT4BF)<sup>2</sup>

- Output clock range: 11 to 200 MHz (CYT4BF)<sup>2</sup>

- PLL400 with SSCG and fractional operation<sup>1</sup>

- Input clock range: 3.988 to 33.34 MHz (CYT4BF)<sup>2</sup>

- Output clock range: 25 to 350 MHz (CYT4BF)<sup>2</sup>

- Supports down spread

- 24-bit fractional divider<sup>3</sup>

- SSCG and fractional operation are enabled and disabled by register<sup>4</sup>

- Default is Disable

**Hint Bar**

Review TRM section 18.3 and Register TRM for additional details

Refer to the datasheet for additional details on AC specification

Output clock range of PLL400 changes depending on spreading configuration

<sup>&</sup>lt;sup>1</sup> Refer to the device datasheet for number and location each PLL type

<sup>&</sup>lt;sup>2</sup> Refer to the device datasheet for the target product

<sup>&</sup>lt;sup>3</sup> Refer to the Register TRM (PLL400 CONFIG2 register) for additional details

<sup>&</sup>lt;sup>4</sup> Refer to the Register TRM (CLK\_PLL400M\_CONFIG2 and CLK\_PLL400M\_CONFIG3 registers) for additional details

## Clock Generation

- > FLL: Frequency-locked loop

- Input clock can be IMO (8 MHz), ECO, or EXT\_CLK

- A counter with a current-controlled oscillator (CCO)

- Starts up (locks) faster and uses lower power than the PLL

- The lock tolerance is user adjustable

- The parameters on the FLL configuration are as follows:

- Input clock range: 0.25 to 80 MHz (CYT4BF)<sup>1</sup>

- Output clock range: 24 to 100 MHz (CYT4BF)<sup>1</sup>

- FLL is set by ROM boot, and FLL can reduce startup time

#### Hint Bar

Review TRM section 18.3 and Register TRM for additional details

## > PLL connection table

| CLK DATH  | CYT4BF        | CYT4DN   |

|-----------|---------------|----------|

| CLK_PATH  | PLL Type      | PLL Type |

| CLK_PATH1 | PLL400#0      | PLL400#0 |

| CLK_PATH2 | PLL400#1      | PLL400#1 |

| CLK_PATH3 | PLL#2         | PLL400#2 |

| CLK_PATH4 | PLL#3         | PLL400#3 |

| CLK_PATH5 | Not supported | PLL400#4 |

| CLK_PATH6 | Not supported | PLL#5    |

| CLK_PATH7 | Not supported | PLL#6    |

| CLK_PATH8 | Not supported | PLL#7    |

#### **Hint Bar**

Review TRM section 18.3 and Register TRM for additional details

Refer to the datasheet for additional details

# Clock Generation PLL (1/4)

## PLL configuration parameters (CYT4BF)<sup>1</sup>

| Parameters                     | PLL w/o SSCG and Fractional Operation | PLL with SSCG and Fractional<br>Operation |

|--------------------------------|---------------------------------------|-------------------------------------------|

| Fref                           | 3.988 to 33.34 MHz                    | 3.988 to 33.34 MHz                        |

| Fout (Fvco/Output divider)     | 11 to 200 MHz                         | 25 to 350 MHz                             |

| Fpfd (Fref/Reference divider)  | 4 to 8 MHz                            | 8 to 20 MHz                               |

| Fvco (Fpfd * Feedback divider) | 170 to 400 MHz                        | 400 to 800 MHz                            |

#### **Hint Bar**

Review TRM section 18.3.1, 18.3.2, and Register TRM for additional details

Fout range changes depending on spreading configuration

Fpfd range changes depending on fractional divider configuration

<sup>&</sup>lt;sup>1</sup> Refer to the device datasheet for the target product

## Clock Generation PLL (2/4)

# Configuration example for PLL without SSCG and Fractional Operation

In this case, 200-MHz clock (Fout) is generated from the 8-MHz input clock (Fref)

|                 | Fref  | Fout               | Fpfd                               | Fvco                                |

|-----------------|-------|--------------------|------------------------------------|-------------------------------------|

| Frequency       | 8 MHz | 200 MHz = Fvco/2   | 4 MHz = Fref/2                     | 400 MHz = Fpfd x 100                |

| Divider Setting | -     | Output Divider1: 2 | Reference Divider <sup>1</sup> : 2 | Feedback Divider <sup>1</sup> : 100 |

#### **Hint Bar**

Review TRM section 18.3.1, 18.3.2, and Register TRM for additional details

<sup>&</sup>lt;sup>1</sup> Refer to the Register TRM (CLK\_PLL\_CONFIG register) for additional details of PLL without SSCG and fractional operation Refer to the Register TRM (PLL400 CONFIG register) for additional details of PLL with SSCG and fractional operation

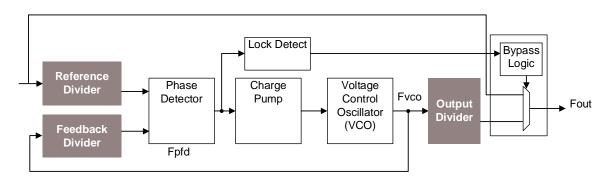

# Clock Generation PLL (3/4)

## Configuration for SSCG

Spread energy contained in the narrow band of the clock source to a wide band

- The parameters on the PLL configuration<sup>1</sup> are as follows:

- Modulation Depth: Between -3%, -2%, -1%, or 0.5%

- Modulation Rate: Between Fpfd/4096, Fpfd/2048, Fpfd/1024, or Fpfd/512

- Modulation Type: Down-spread mode only

## Advantage

Reduces the peak spectral amplitude of the fundamental and the harmonics to lower radiated emission from the clock source Review TRM section 18.3.2.1 and Register TRM for additional details

**Hint Bar**

<sup>&</sup>lt;sup>1</sup> Refer to the Register TRM (PLL400\_CONFIG3 register) for additional details

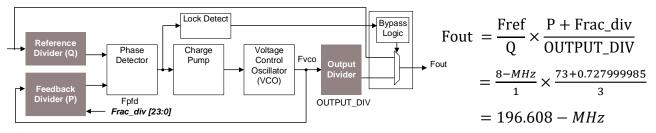

# Clock Generation PLL (4/4)

- Configuration for fractional operation

- PLL400 has a 24-bit fractional divider

- Set according to the following formula

- Accuracy is only guaranteed for the upper 21 bits

- Configuration example for fractional operation

- In this case, 196.608-MHz clock (Fout) is generated from the 8-MHz input clock (Fref)

|         | Fref  | Q                                  | Р                                  | Frac_div                         | OUTPUT_DIV                      | Fout        |

|---------|-------|------------------------------------|------------------------------------|----------------------------------|---------------------------------|-------------|

| Value   | 8 MHz | 1                                  | 73                                 | 0.727999985 = 12213813 / 2^24    | 3                               | 196.608 MHz |

| Setting | -     | Reference Divider <sup>1</sup> : 1 | Feedback Divider <sup>1</sup> : 73 | FRAC_DIV <sup>2</sup> : 12213813 | Output Divider <sup>1</sup> : 3 | -           |

## Advantage

Can generate source clock of the sampling frequency (e.g., 96 kHz) in the sound system

#### **Hint Bar**

Review TRM section 18.3.2.2 and Register TRM for additional details

<sup>&</sup>lt;sup>1</sup> Refer to the Register TRM (PLL400\_CONFIG register) for additional details

<sup>&</sup>lt;sup>2</sup> Refer to the Register TRM (PLL400\_CONFIG2 register) for additional details

- Clock system components

- Clock trees

- CLK\_PATHx

- CLK HFx

- CLK\_REF\_HF

- CLK LF

- CLK\_BAK

- CLK\_TIMER

## **Active Domain Clock Trees**

#### Clock distribution

- CLK\_PATHx

- Input sources for the CLK\_HFx roots

- CLK\_PATH0 contains the FLL output Up to 100 MHz (using FLL)

- CLK\_PATH1 to (P+1) contains the PLL output<sup>1</sup>

- Up to 200 MHz when using PLLs without SSCG and fractional operation

- Up to 350 MHz when using PLLs with SSCG and fractional operation

- CLK\_PATH (P+D) is a connection to root clocks

Up to 33.34 MHz (using ECO)

- CLK\_REF\_HF

- Selects IMO, ECO, EXT\_CLK

- Typically selects the IMO (8 MHz)

- Used as reference clock for CSV\_CLK\_HF0 to R-1 (CLK\_HF 0 to R-1 clock supervision)

#### - TIMER CLK

- CLK\_IMO is input source for CLK\_TIMER

- Used as source clock of SysTick timer in CPU

<sup>&</sup>lt;sup>1</sup> Refer to the device datasheet for the target product

# **CLK\_HF Clock Trees**

## CLK\_HFx can select CLK\_PATHx as source clock by register<sup>1</sup>

| 21112 11 | Usage Function                                                                      |                                                                     |  |  |

|----------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|

| CLK Path | CYT4BF                                                                              | CYT4DN                                                              |  |  |

| CLK_HF0  | Root clock for CPUSS, PERI (CLK_MEM, CLK_SLOW, CLK_PERI)                            | Root clock for CPUSS, PERI (CLK_MEM, CLK_SLOW, CLK_PERI)            |  |  |

| CLK_HF1  | CM7 CPU Core#0, CM7 CPU Core#1                                                      | CM7 CPU Core#0, CM7 CPU Core#1                                      |  |  |

| CLK_HF2  | Peripheral clock root other than CLK_PERI                                           | Peripheral clock root other than CLK_PERI                           |  |  |

| CLK_HF3  | Event generator, clock output on EXT_CLK pins (when used as output)                 | Event generator, clock output on EXT_CLK pins (when used as output) |  |  |

| CLK_HF4  | Ethernet Channel#0 and Channel#1 internal clock                                     | Ethernet Channel#0 internal clock                                   |  |  |

| CLK_HF5  | I2S channel#0, I2S channel#1, I2S channel#<br>Channel#0 TSU, Ethernet Channel#1 TSU | Sound Subsystem #0 root clock, ETH0 TSU clock (CLK_IF_SRSS0)        |  |  |

| CLK_HF6  | Root clock for SDHC, SMIF interface clock                                           | Sound Subsystem #1 root clock (CLK_IF_SRSS1)                        |  |  |

| CLK_HF7  | Not connect                                                                         | Sound Subsystem #2 root clock (CLK_IF_SRSS2)                        |  |  |

| CLK_HF8  | Not supported                                                                       | SMIF#0 root clock                                                   |  |  |

| CLK_HF9  | Not supported                                                                       | SMIF#1 root clock                                                   |  |  |

| CLK_HF10 | Not supported                                                                       | Video Subsystem root clock                                          |  |  |

| CLK_HF11 | Not supported                                                                       | Display#0 root clock                                                |  |  |

| CLK_HF12 | Not supported                                                                       | Display#1 root clock                                                |  |  |

| CLK_HF13 | Not supported                                                                       | Not connect                                                         |  |  |

<sup>&</sup>lt;sup>1</sup> Refer to the Register TRM (CLK\_ROOT\_SELECT) for additional details

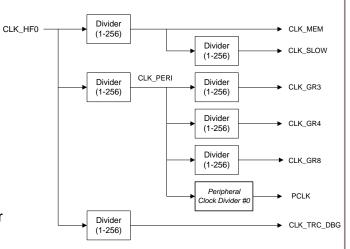

## CLK\_HF Distribution (1/2)

#### CLK HF0¹ distribution

- Distributed to CLK\_MEM, CLK\_SLOW, CLK\_PERI, and CLK\_TRC\_DBG

- CLK MEM

- Source clock for CPUSS fast infrastructure

- Up to 200 MHz<sup>2</sup>

- CLK SLOW

- Source clock for CPUSS slow infrastructure such as CM0+, Crypto, DMAs, test controller, and some peripherals<sup>3</sup>

- Up to 100 MHz

- CLK\_PERI

- Source clock for some peripherals via divider

- Up to 100 MHz

- PCLK and CLK\_GR

- Source clock for peripheral functions via divider

- CLK TRC DBG

- Source clock for trace components in debug infrastructure

- Runs only when debugger is connected

#### **Hint Bar**

Training section references:

**CPU Subsystem**

<sup>&</sup>lt;sup>1</sup> CLK\_HF0 can be enabled and disabled by register. CLK\_HF0 is always enabled as the clock source of CPU

<sup>&</sup>lt;sup>2</sup> Refer to the device datasheet for the target product

<sup>3</sup> eFuse and SRSS registers

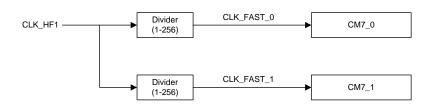

# CLK\_HF Distribution (2/2)

- CLK HF1 distribution

- Root clock for the CM7 CPUs

- Distributed to CLK\_FAST\_0 and CLK\_FAST\_1

- Divider setting is possible independently for each M7 CPU

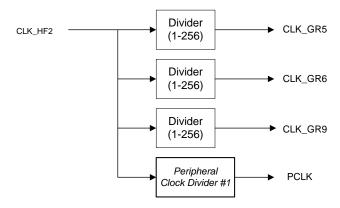

- CLK\_HF2 distribution

- Input clock for peripheral clock dividers

- Root clock such as CAN FD, LIN, SCB, SAR ADC

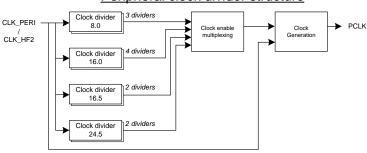

## Peripheral Clock Distribution

#### PERI Clock Divider

- Output of dividers can be routed to any peripheral

- Two dividers

- Peripheral clock divider#0

- Input clock: CLK\_PERI

- Used for IOSS, TCPWM, and CPUSS

- Peripheral clock divider#1

- Input clock: CLK\_HF2

- Used for CAN FD, LIN, SCB, and SAR ADC

- Four types of dividers<sup>1</sup>

- 8-bit divider<sup>2</sup>

- 16-bit divider<sup>2</sup>

- 16.5-bit divider<sup>2</sup>

- 24.5-bit divider<sup>2</sup>

- Supports fractional clock dividers

- Phase aligning

- Can be phase-aligned with any of the other (enabled) clock dividers

#### Peripheral clock divider structure

#### **Hint Bar**

Review TRM section 18.6 for additional details on clock numbers, which are assigned for each peripheral

Clock dividers can be configured through the following registers:

DIV\_8\_CTL

DIV 16 CTL

**DIV 16 5 CTL**

**DIV 24 5 CTL**

Clock Enable multiplexers can be configured through CLOCK\_CTL registers, which are assigned for each peripheral

<sup>&</sup>lt;sup>1</sup> Not all dividers are supported

<sup>&</sup>lt;sup>2</sup> The supported number of each divider differs between Peripheral clock divider#0 and Peripheral clock divider#

## DeepSleep/Hibernate/HV Domain Clock Trees

#### Clock distribution

- CLK\_LF

- Selects ILO0, ILO1, WCO, LPECO

- Input source for MCWDT

- Used as reference clock for CSV\_ILO (CLK\_ILO0 clock supervision)

- CLK BAK

- Selects CLK\_LF, ILO0, ILO1, WCO, LPECO

- Input source for RTC¹ clock

#### **Hint Bar**

Multi-counter watchdog timer (MCWDT)

Training section references: Watchdog Timer

<sup>&</sup>lt;sup>1</sup> Typically, WCO is connected to RTC. CLK\_LF can also connect to RTC

- Clock system components

- Clock supervision (CSV) allows one clock to be monitored with another clock (reference clock)

- Monitored clock sources

- CLK\_HFx

- CLK\_REF\_HF

- CLK\_ILO0

- CLK\_LF

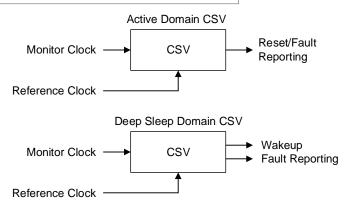

- CSV power domain

- Active domain CSV

- DeepSleep domain CSV

# Clock Supervision (1/2)

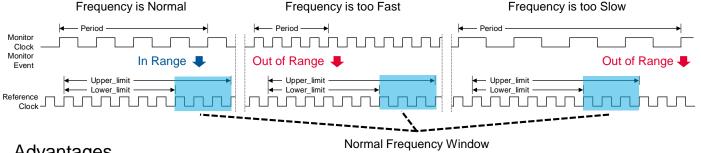

- > Checks if the frequency of the monitored clock is within the allowed frequency window

- Uses a reference clock to supervise the behavior of the monitor clock

| <b>CSV Components</b> | Monitor Clock | Reference Clock | Note                                                                                                |

|-----------------------|---------------|-----------------|-----------------------------------------------------------------------------------------------------|

| CSV_HFx               | CLK_HFx       | CLK_REF_HF      | CLK_REF_HF is selected the IMO or EXT_CLK or ECO CLK_REF_HF is typically selected the IMO (default) |

| CSV_REF               | CLK_REF_HF    | CLK_ILO0        | _                                                                                                   |

| CSV_ILO               | CLK_ILO0      | CLK_LF          | CLK_LF is selected WCO or ILO1 or ECO Pre-scaler                                                    |

| CSV_LF                | CLK_LF        | CLK_ILO0        | _                                                                                                   |

- Active domain CSV: CSV\_HF0/1 and CSV\_REF

- Automatically stops during DeepSleep and restarts by wakeup

- "Wait" function to monitor startup time¹

- Possible to generate a reset or a fault report

- DeepSleep domain CSV: CSV\_ILO, CSV\_LF

- Operates during Active and DeepSleep

- Generates wakeup and fault reports

- All CSVs are initially off

<sup>&</sup>lt;sup>1</sup> Need to prevent a false error detection at startup

# Clock Supervision (2/2)

#### CSV operation

- The monitored clock generates a Monitor event (Period) and the reference clock generates a lower and upper limit

- The Monitor event is compared against a lower limit/upper limit

- An error is reported if the Monitor event ≤ lower limit or the Monitor event > upper limit

## Advantages

- Detects clock stop, too fast, and too slow by frequency window

- Monitors clock in Active, Sleep, and DeepSleep power modes with Active domain CSV and DeepSleep domain CSV

- Can achieve ASIL-B

#### **Hint Bar**

The monitor clock and the reference clock are asynchronous (typical). Therefore, the frequency window needs to account for the maximum clock tolerance

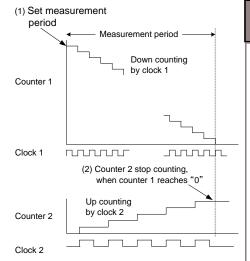

## Clock Calibration Counter

#### Clock Calibration Counter Operation

- Two counters: Counter1 and Counter2

- Counter1 is clocked by clock1 (reference clock)

- Counter2 is clocked by clock2 (measurement clock)

- Counter1 sets the measurement period by the count number of clock1 (1)

- Counter2 indicates the count number of clock2 during the measurement period (2)

- Clock2 frequency can be calculated using the following formula with two counter values  $\operatorname{clock2frequency} = \frac{\operatorname{Counter2value}}{\operatorname{Counter1value}} \times \operatorname{clock1frequency}$

- All clock sources are available for these two clocks (clock1 and clock2)

#### Use Case

Measure a low-accuracy clock such as the ILO using a high-accuracy clock such as the ECO

#### **Hint Bar**

Review TRM section 18.7 for additional details

Count Clock1 and 2 can be selected through the CLK\_OUTPUT\_FAST register

# Comparison Between CYT2BL, CYT4BF, and CYT4DN (1/4)

|             | Features             | CYT2BL          | CYT4BF                             | CYT4DN          |

|-------------|----------------------|-----------------|------------------------------------|-----------------|

| IMO         |                      | Supported       |                                    |                 |

| ECO         |                      | Supported       |                                    |                 |

| ILO 0       |                      |                 | Supported                          |                 |

| ILO 1       |                      |                 | Supported                          |                 |

| WCO         |                      |                 | Supported                          |                 |

| LPECO       |                      | Not impleme     | ented                              | Supported       |

| FLL         | Number of FLL        |                 |                                    |                 |

|             | Input Range          | 0.25 to 80 MHz  |                                    | 0.25 to 100 MHz |

|             | Output Range         | 24 to 100 MHz   |                                    | '               |

| PLL         | Number of PLL        | 1               | 2                                  | 3               |

|             | Input Range          |                 | 3.988 to 33.34 MHz                 |                 |

|             | Output Range         | 11 to 160 MHz   | 11 to 2                            | 00 MHz          |

| PLL400      | Number of PLL        | Not implemented | 2                                  | 5               |

| Input Range |                      | Not implemented | Not implemented 3.988 to 33.34 MHz |                 |

| Output F    | Output Range         | Not implemented | 25 to 350 MHz (*)                  | 25 to 400 MHz   |

| SSCG        |                      | Not implemented | Y                                  | es              |

|             | Fractional Operation | Not implemented | Yes                                |                 |

(\*) Spreading off

# Comparison Between CYT2BL, CYT4BF, and CYT4DN (2/4)

| Fea          | tures      | CYT2BL                                                       | CYT4BF          | CYT4DN                               |

|--------------|------------|--------------------------------------------------------------|-----------------|--------------------------------------|

|              | CLK_PATH 0 | FLL                                                          |                 |                                      |

|              | CLK_PATH 1 | PLL                                                          | PI              | _L400                                |

|              | CLK_PATH 2 | ECO,IMO,EXT_CLK,WCO, ILO0/1                                  | PI              | _L400                                |

|              | CLK_PATH 3 | ECO,IMO,EXT_CLK,WCO, ILO0/1                                  | PLL             | PLL400                               |

|              | CLK_PATH 4 | Not implemented                                              | PLL             | PLL400                               |

|              | CLK_PATH 5 | Not implemented ECO,IMO,EXT_CLK,WCO, ILO0/1  Not implemented |                 | PLL400                               |

| CLK Trees    | CLK_PATH 6 |                                                              |                 | PLL                                  |

| Source Clock | CLK_PATH 7 | Not impler                                                   | Not implemented |                                      |

|              | CLK_PATH 8 | Not impler                                                   | mented          | PLL                                  |

|              | CLK_PATH 9 | Not impler                                                   | mented          | ECO,IMO,EXT_CLK,WCO,<br>ILOO/1,LPECO |

|              | CLK_REF_HF | ECO,IMO,EXT_CLK                                              |                 | ECO,IMO,EXT_CLK, LPECO               |

|              | CLK_TIMER  | CLK_HF0, IMO                                                 |                 | IMO                                  |

|              | CLK_LF     | ILO0/1, WCO, ECO                                             |                 | ILO0/1, WCO, ECO, LPECO              |

|              | CLK_BAK    | CLK_LF, ILC                                                  | 00, WCO         | CLK_LF, ILO0, WCO, LPECO             |

# Comparison Between CYT2BL, CYT4BF, and CYT4DN (3/4)

| Featu               | res                     | CYT2BL                                     | CYT4BF                                    | CYT4DN                                  |

|---------------------|-------------------------|--------------------------------------------|-------------------------------------------|-----------------------------------------|

|                     | CLK_HF0                 | CPUSS clocks, PERI, and AHB infrastructure | CPUSS (Memories, CLK_SLOW, Peripherals)   | CPUSS (Memories, CLK_SLOW, Peripherals) |

|                     | CLK_HF1                 | Event Generator                            | CPUSS (Cortex-M7 CPU 0, 1)                | CPUSS (Cortex-M7 CPU 0, 1)              |

|                     | CLK_HF2                 | Not connect                                | CAN FD, FlexRay, LIN, TCPWM, SCB, SAR ADC | CAN FD, CXPI, LIN, SCB,<br>SAR ADC      |

|                     | CLK_HF3                 | Not implemented                            | Event Generator                           | Event Generator                         |

|                     | CLK_HF4                 | Not implemented                            | Ethernet                                  | Ethernet                                |

| 0116                | CLK_HF5 CLK_HF6 CLK_HF7 | Not implemented                            | Audio subsystem                           | Sound Subsystem #0                      |

| CLK<br>Distribution |                         | Not implemented                            | SDHC Interface, SMIF                      | Sound Subsystem #1                      |

|                     |                         | Not implemented                            | Not connect                               | Sound Subsystem #2                      |

|                     | CLK_HF8                 | Not implemented                            | Not implemented                           | SMIF #0                                 |

|                     | CLK_HF9                 | Not implemented                            | Not implemented                           | SMIF #1                                 |

|                     | CLK_HF10                | Not implemented                            | Not implemented                           | Video Subsystem                         |

|                     | CLK_HF11                | Not implemented                            | Not implemented                           | Video Display #0                        |

|                     | CLK_HF12                | Not implemented                            | Not implemented                           | Video Display #1                        |

|                     | CLK_HF13                | Not implemented                            | Not implemented                           | Not connect                             |

# Comparison Between CYT2BL, CYT4BF, and CYT4DN (4/4)

| Features            |                          | CYT2BL CYT4BF      |  | CYT4DN                                  |

|---------------------|--------------------------|--------------------|--|-----------------------------------------|

| Clock Divider       | Number of Dividers       | 1 2                |  | 2                                       |

|                     | Fractional Clock Divider | 7/L 5-DIT OIVIOARS |  | 16.5-bit dividers,<br>24.5-bit dividers |

|                     | Phase Aligning           | Supported          |  |                                         |

| Clock Supervision   |                          | Supported          |  |                                         |

| Calibration Counter |                          | Supported          |  |                                         |

Part of your life. Part of tomorrow.

| Revision | ECN     | Submission<br>Date | Description of Change                                                                                                                         |

|----------|---------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 6400993 | 12/7/2018          | Initial release                                                                                                                               |

| *A       | 6633414 | 7/22/2019          | Added slide 4,12<br>Updated Figure slide 6, 7, 10, 13, 19, 20, 22, 23, 25, 26<br>Updated slide 2, 5, 13, 15 - 17, 21, 22, 24, 25, 28, 32 – 34 |

| *B       | 7060646 | 01/06/2021         | Updated slide 2-5, 9, 11, 13, 15-17, 21-23, 25, 30, 32-35                                                                                     |