## Customer training workshop TRAVEO™ T2G Body High and Cluster 2D CPU subsystem (CPUSS)

Q1, 2024

#### **Target products**

> Target product list for this training material:

| Family category                                         | Series     | Code flash memory size |

|---------------------------------------------------------|------------|------------------------|

| TRAVEO <sup>™</sup> T2G Automotive Body Controller High | CYT3BB/4BB | Up to 4160 KB          |

| TRAVEO™ T2G Automotive Body Controller High             | CYT4BF     | Up to 8384 KB          |

| TRAVEO™ T2G Automotive Body Controller High             | CYT6BJ     | Up to 16768 KB         |

| TRAVEO™ T2G Automotive Cluster                          | CYT3DL     | Up to 4160 KB          |

| TRAVEO™ T2G Automotive Cluster                          | CYT4DN     | Up to 6336 KB          |

Review TRM section 4.1 for additional details

specific to the CPUSS

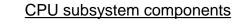

#### **CPU subsystem overview**

The CPU subsystem (CPUSS) is based on dual 32-bit Arm<sup>®</sup> Cortex<sup>®</sup> CPUs.

<sup>1</sup> CYT6 series have four Cortex-M7 CPUs, CYT4 series have two Cortex-M7 CPUs, and CYT3 series have single Cortex-M7 CPU

## **Cortex®-M7 features summary**

- > Main CPU

- Up to four Cortex<sup>®</sup>-M7 CPUs<sup>1</sup>

- Execution of application software

- Up to 350-MHz operation (CYT4BF)<sup>2</sup>

- Up to 320-MHz operation (CYT4DN,CYT6BJ<sup>2</sup>

- Tightly-coupled memories (ITCM and DTCM) and instruction and data caches<sup>3</sup>

- > System tick (SysTick) timer

- > Floating-point unit (FPU)

- Single and double precision

- Compliant with the ANSI/IEEE Std 754-2008

IEEE Standard for Binary Floating-Point

Arithmetic

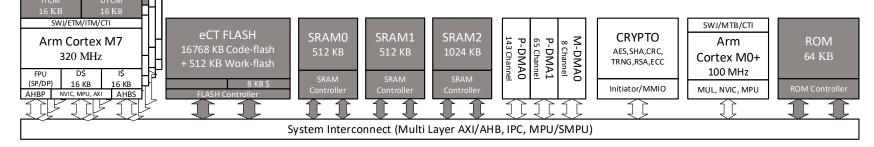

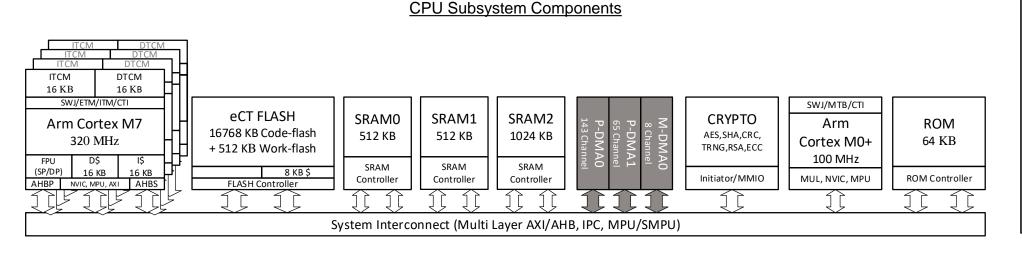

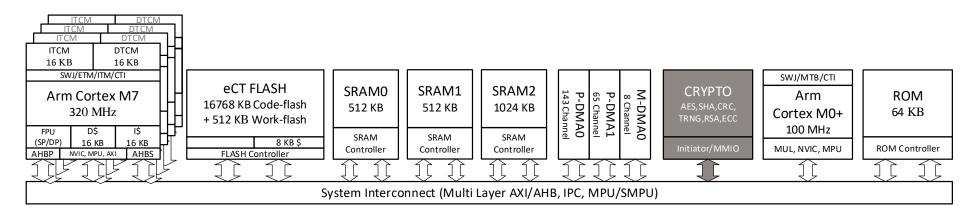

| ITCM DTCM<br>ITCM DTCM<br>ITCM DTCM<br>ITCM DTCM<br>ITCM DTCM<br>16 KB 16 KB | <u>C</u>                                                | <u>PU Subs</u>     | ystem Co           | omponer            | <u>nts</u> – C                                                       | ross-trigg                              | jering com                                  | iponent (      |

|------------------------------------------------------------------------------|---------------------------------------------------------|--------------------|--------------------|--------------------|----------------------------------------------------------------------|-----------------------------------------|---------------------------------------------|----------------|

| SWJ/ETM/ITM/CTI<br>Arm Cortex M7<br>320 MHz<br>FPU DS IS                     | eCT FLASH<br>16768 KB Code-flash<br>+ 512 KB Work-flash | SRAM0<br>512 КВ    | SRAM1<br>512 KB    | SRAM2<br>1024 KB   | M-DMA0<br>8 Channel<br>P-DMA1<br>65 Channel<br>P-DMA0<br>143 Channel | CRYPTO<br>AES, SHA,CRC,<br>TRNG,RSA,ECC | SWJ/MTB/CTI<br>Arm<br>Cortex M0+<br>100 MHz | ROM<br>64 KB   |

| (SP/OP) 16 KB 16 KB<br>AHBP NVIC MPU, AXI AHBS                               | 8 KB \$<br>FLASH Controller                             | SRAM<br>Controller | SRAM<br>Controller | SRAM<br>Controller |                                                                      | Initiator/MMIO                          | MUL, NVIC, MPU                              | ROM Controller |

| System Interconnect (Multi Layer AXI/AHB, IPC, MPU/SMPU)                     |                                                         |                    |                    |                    |                                                                      |                                         |                                             |                |

<sup>1</sup> CYT6 series have four Cortex-M7 CPUs, CYT4 series have two Cortex<sup>®</sup>-M7 CPUs, and CYT3 series have single Cortex<sup>®</sup>-M7 CPU

<sup>2</sup> See the device datasheet for operation frequency of target product.

$^{\scriptscriptstyle 3}$  See the device data sheet for supported capacity of ITCM, DTCM and caches.

- Sixteen protection regions

- Privileged/unprivileged, read/write attributes

Memory protection unit (MPU)

- Nested vector interrupt controller (NVIC)

- Eight external system interrupts, eight internal software interrupts, eight interrupt levels, and one non-maskable interrupt

- Wakeup interrupt controller (WIC) support

- Vector table relocation (VTOR)

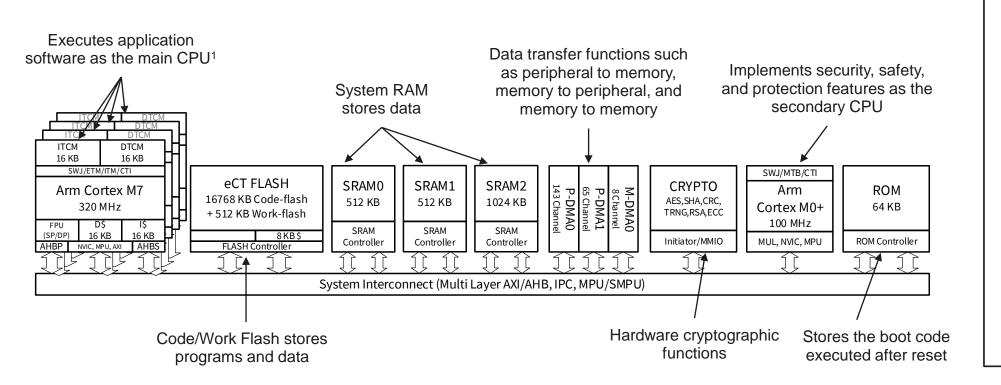

- Debug components

- Supported SWD and JTAG interface (SWJ)

- Tracing components (ETM/ITM over ETB/TPIU)

- Cross-triggering component (CTI)

| Arm <sup>®</sup> provides additional<br>reference material on their<br>webpage at:<br><u>infocenter.arm.com</u> |

|-----------------------------------------------------------------------------------------------------------------|

| Training section references:                                                                                    |

| - Interrupts                                                                                                    |

| - Program and debug interface                                                                                   |

| - Protection units                                                                                              |

| - SRAM interface                                                                                                |

| Combined SWD/JTAG<br>interface (SWJ)                                                                            |

| Embedded trace macrocell (ETM)                                                                                  |

| Instrumentation trace<br>macrocell (ITM)                                                                        |

| Cross-triggering interface (CTI)                                                                                |

| Embedded trace buffer<br>(ETB)                                                                                  |

| Trace port interface Unit<br>(TPIU)                                                                             |

Hint Bar

Arm<sup>®</sup> provides additional

webpage at:

references:

- Interrupts

interface

(ETM)

(CTI)

infocenter.arm.com

- Program and debug

Combined SWD/JTAG

Micro trace buffer (MTB)

**Embedded trace macrocell**

**Cross-triggering interface**

- Protection units

**Training section**

reference material on their

## **Cortex<sup>®</sup>-M0+ features summary**

- Secondary CPU >

- Execution of boot process

- Secure master in secure system to establish a root-of-trust

- Up to 100-MHz operation<sup>1</sup>

- SysTick timer >

- Memory protection unit (MPU)

- Eight protection regions

- Privileged/unprivileged access attributes

- Nested vector interrupt controller (NVIC)

- Eight external system interrupts, eight internal software interrupts, four interrupt levels, and one nonmaskable interrupt

- Wakeup interrupt controller (WIC) support

- Vector table relocation (VTOR)

- Debug components

- Supported SWD and JTAG interface (SWJ)

- Tracing component (ETM over MTB)

- Cross-triggering component (CTI)

<sup>1</sup> For CM4 to operate at 160 MHz, CM0+ is required to operate at a frequency of 80 MHz. See the device datasheet for operation frequency of target product.

### **CPUSS dedicated master identifier**

- Each bus master has a dedicated master identifier, which is used for:

- Bus arbitration

- IPC lock acquire functionality

- Violation access information by MPU, SMPU, and PPU

| Master<br>Identifier <sup>1</sup> | Bus Master (CYT6BJ)      | Bus Master (CYT4DN)      | Hint Bar                                |

|-----------------------------------|--------------------------|--------------------------|-----------------------------------------|

| 0                                 | Cortex <sup>®</sup> -M0+ | Cortex <sup>®</sup> -M0+ | Inter processor                         |

| 1                                 | Crypto                   | Crypto                   | communication (IPC)                     |

| 2                                 | P-DMA 0                  | P-DMA 0                  | Memory protection unit                  |

| 3                                 | P-DMA 1                  | P-DMA 1                  | (MPU)                                   |

| 4                                 | M-DMA                    | M-DMA                    | Shared memory protection<br>unit (SMPU) |

| 5                                 | SDHC                     | -                        |                                         |

| 7                                 | Cortex-M7_2              | -                        | Peripheral protection unit (PPU)        |

| 8                                 | Cortex-M7_3              | -                        |                                         |

| 9                                 | Ethernet 0               | Ethernet 0               |                                         |

| 10                                | Ethernet 1               | JPEG Decorder            |                                         |

| 11                                | -                        | AXI DMA                  |                                         |

| 12                                | -                        | Video Subsystem          |                                         |

| 13                                | Cortex-M7_1              | Cortex-M7_1              |                                         |

| 14                                | Cortex-M7_0              | Cortex-M7_0              |                                         |

| 15                                | DAP Tap Controller       | DAP Tap Controller       |                                         |

<sup>1</sup> See the device datasheet for master identifier number and regarding peripherals of target product.

Sys Interface in CM7 can

only access peripherals

only access memory

Code Interface in CM7 can

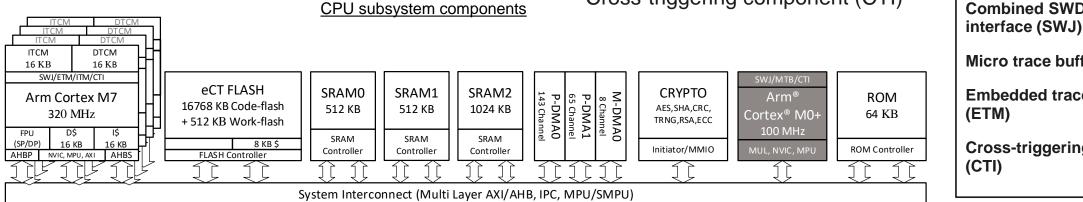

#### **CPUSS** bus infrastructure

- > AHB-Lite and AXI bus infrastructure

- > Bus clock domains

- Fast/slow clock domains

- Each memory interface has both domains

- Bus competition

CPUSS has multiple bus masters

Design a system that considers

- bus competition by simultaneous access

## **CPU** features

#### > Cortex<sup>®</sup>-M7

- 5 CoreMark/MHz and 2.14 DMIPS/MHz

- ISA Support (Thumb/Thumb-2)

- 6-stage superscalar + branch prediction pipeline

- Interconnect

- AXI master

- AHB peripheral port (AHBP/AHBS)

- Tightly-coupled memory (ITCM/DTCM)

- Instruction and data cache

- DSP extensions

- Single-cycle 16/32-bit MAC, single-cycle dual 16-bit MAC

- 8/16-bit SIMD arithmetic

- Floating Point Unit (FPU)

- Memory Protection Unit (MPU)

- Nested vector interrupt controller (NVIC)

- Vector table relocation (VTOR)

- Wake-up Interrupt Controller(WIC)

- SysTick Timer

#### Cortex<sup>®</sup>-M0+

- 1.99 CoreMark/MHz and 0.9 DMIPS/MHz

- ISA Support (Thumb/Thumb-2)

- 2-stage Pipeline

- Interconnect

- AHB Lite

- Memory Protection Unit (MPU)

- Nested vector interrupt controller (NVIC)

- Vector table relocation (VTOR)

- Wake-up Interrupt Controller(WIC)

- SysTick Timer

#### Hint Bar

Arm provides additional reference material on their webpage at: infocenter.arm.com

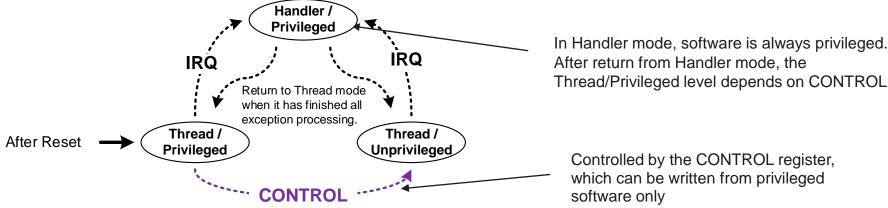

#### **CPU** mode transition

- Both CPUs support two operating modes and two privilege levels: >

- Operating mode

- Thread mode executes application software

- Handler mode handles exceptions

- Privilege levels

- Unprivileged: Software has limited access to MSR/MRS instructions (uses CPS instructions), system timer, NVIC, system control block, and memory/peripherals

- Privileged: Software can use all instructions and has access to all resources

Transition from Thread/Privileged to Thread/Unprivileged by CONTROL register<sup>1</sup> Transition from Thread/Unprivileged to Thread/Privileged via SVC<sup>2</sup>

After return from Handler mode, the Thread/Privileged level depends on CONTROL

Controlled by the CONTROL register, which can be written from privileged

#### Hint Bar

**Review TRM section 4.5** for additional details specific to CPU modes

Arm provides additional reference material on their webpage at: infocenter.arm.com

Move to system coprocessor register from the Arm register (MSR)

Move the contents of program status register to a general-purpose register (MRS)

Change processor state (CPS)

<sup>1</sup> The CONTROL register is a CPU-specific register. It defines privileged/unprivileged, stack pointer, and FPU extension. <sup>2</sup> Supervisor calls are used to request privileged operations

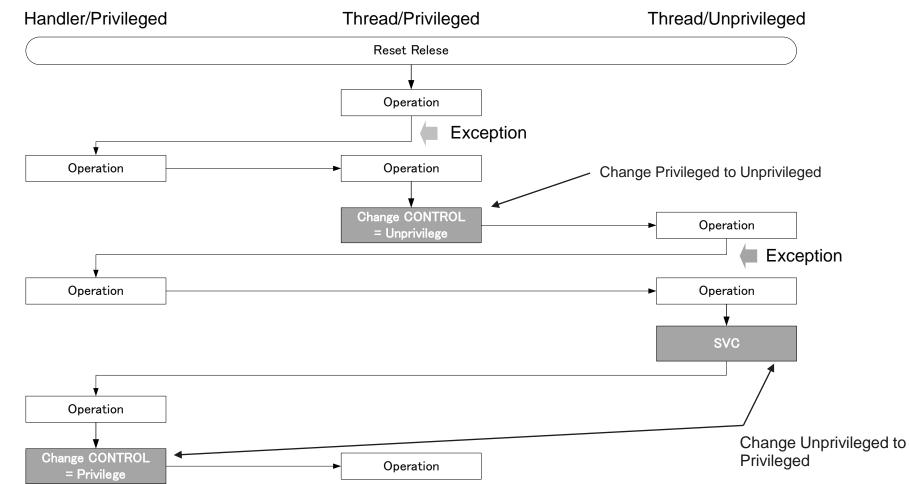

#### **Operation modes transition**

> Use Case: Changing Privileged/Unprivileged mode

Arm provides additional reference material on their webpage at: <u>infocenter.arm.com</u>

**Hint Bar**

#### **Memory Protection**

- Each CPU has a memory protection > unit (MPU)<sup>1</sup> that:

- Realizes software separation \_ freedom of interface

- Includes address range, \_ read/write, and privileged/unprivileged attributes

- Features sixteen protection regions

- Use case >

- Software partitioning of ASIL and QM in Functional Safety

Example of MPU Operation

Arm provides additional reference material on their webpage at: infocenter.arm.com

**Hint Bar**

<sup>1</sup> MPU registers are written by privileged software and are only one part of the protection concept. For details, refer to the Protection Units training section.

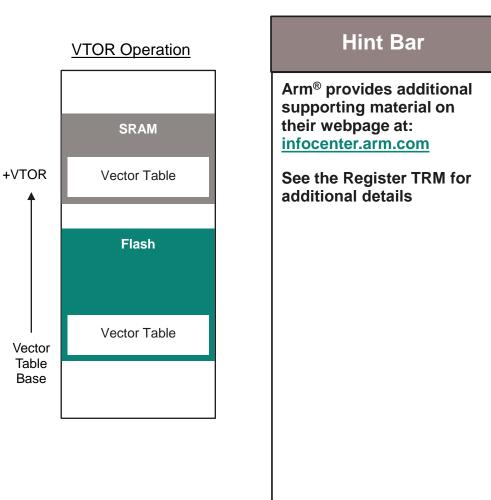

#### **Vector table relocation**

- > Vector Table Offset Register (VTOR)<sup>1</sup>

- Defines the location of the vector table of each core.

There is a VTOR for each CM7 and another one for CM0.

- Can be used to relocate the vector table from Flash to SRAM, allowing the interrupt handlers to change dynamically

- VTOR is written from privileged software only

- Use the following registers to set VTOR for both cores:

- CM0\_VECTOR\_TABLE\_BASE: By default, set to beginning of Flash by Boot ROM

- CM7\_x\_VECTOR\_TABLE\_BASE: Set by CM0+ application before releasing the CPU core CM7\_x from reset <sup>2</sup>

- After boot, each core copies the vector table to SRAM and updates VTOR with the address of the new location

- > Use cases

- Execute the program with RAM only, for Flash programming or performance improvement

- Use different vectors depending on software level or system mode, such as normal and reprogramming

#### **System Tick generation**

- > Each CPU supports a SysTick timer to measure time duration, which provides:

- A 24-bit down counter

- A selectable internal CPU clock or external clock

- Active and Sleep mode operation

- SysTick interrupt generation

- > SysTick registers can be written from Privileged software only

- > Use Cases

- RTOS tick timer

- Alarm timer to alert when an action is not completed within a particular duration

- Software completion time measurement

Arm<sup>®</sup> provides additional supporting material on their webpage at: <u>infocenter.arm.com</u>

**Training section**

- SRAM interface

references:

- Flash

- Boot

#### **CPU** subsystem memory feature summary

- > TCM

- ITCM and DTCM (instruction/data tightly coupled memory) for CM7

- Size 16KB: ITCM/16KB: DTCM (CYT4BF, CYT6BJ)<sup>1</sup>

64KB: ITCM/64KB: DTCM(CYT4DN)<sup>1</sup>

- Error-correction code (ECC) function (SEC/DED)

- > SRAM

- Data storage and code execution

- Size: up to 1024KB(CYT4BF)<sup>1</sup> up to 2048KB(CYT6BJ)<sup>1</sup> up to 640KB(CYT4DN)<sup>1</sup>

- Each CPU sharing

- ECC function

- > Flash

- Code and Work Flash

- Size: up to 8MB: Code/ 256KB: Work (CYT4BF)<sup>1</sup>

- up to 8MB x 2: Code/ 256KB x 2: Work (CYT6BJ) <sup>1</sup>

- up to 6MB: Code/ 128KB: Work (CYT4DN) <sup>1</sup>

- ECC function

- Instruction cache for each CPU

- APIs for Flash programming

- > ROM

- Boot code for CM0+

- API<sup>2</sup> function implementation

<sup>1</sup> See the device datasheet for memory size of target product.

<sup>2</sup> No user access to read or modify SROM code

#### **P-DMA/M-DMA** feature summary

- > Peripheral DMA (P-DMA)

- Single transfer engine shared for all channels

- Focuses on low-latency transfer

- Transfer modes:

- Single, 1D, 2D, and CRC

- Memory DMA (M-DMA)

- Dedicated transfer engine for each channel

- Focuses on high-memory bandwidth

- Transfer modes:

- Single, 1D, 2D, Memory Copy, and Scatter

| Hint Bar                     |

|------------------------------|

| Training section references: |

| - Direct Memory Access       |

|                              |

|                              |

|                              |

|                              |

|                              |

|                              |

|                              |

**Training section**

- Device Security

references:

## Cryptographic (Crypto) feature summary

- > Hardware Crypto functions<sup>1</sup>

- Symmetric key encryption and decryption

- Hashing

- Message authentication

- Random number generation

- Cyclic redundancy checking

- Asymmetric key cryptography

#### CPU Subsystem Components

<sup>1</sup> Access limited to the secure master (CM0+)

## Appendix

## **Comparison between families**

| Features                    |                     | Body Controller Entry<br>(CYT2BL)          | Body Controller High<br>(CYT6BJ) | Body Controller High<br>(CYT4BF) | Cluster<br>(CYT4DN) |  |  |  |

|-----------------------------|---------------------|--------------------------------------------|----------------------------------|----------------------------------|---------------------|--|--|--|

|                             | CPU                 |                                            |                                  | Two Corte                        | tex-M7 CPUs         |  |  |  |

|                             | Operating Frequency | Up to 160 MHz                              | Up to 320 MHz                    | Up to 350 MHz                    | Up to 320 MHz       |  |  |  |

|                             | FPU                 | Single-precision Single/double-precision   |                                  |                                  |                     |  |  |  |

| Main CPU                    | Cache               | N/A 16KB instruction, 16KB data            |                                  |                                  |                     |  |  |  |

|                             | MPU                 | Cortex-M4: 8 regions Cortex-M7: 16 regions |                                  |                                  |                     |  |  |  |

|                             | Interrupt Structure | NVIC+WIC                                   |                                  |                                  |                     |  |  |  |

|                             | System Tick Timer   | Supported                                  |                                  |                                  |                     |  |  |  |

|                             | CPU                 |                                            | Cortex-M0+ CPU                   |                                  |                     |  |  |  |

|                             | Operating Frequency | Same (Up to 100 MHz)                       |                                  |                                  |                     |  |  |  |

| Secondary CPU               | MPU                 | Cortex-M0+: 8 regions                      |                                  |                                  |                     |  |  |  |

|                             | Interrupt Structure | NVIC+WIC                                   |                                  |                                  |                     |  |  |  |

|                             | System Tick Timer   | Supported                                  |                                  |                                  |                     |  |  |  |

|                             | Bus Interface       | AHB-Lite AXI, AHB-Lite                     |                                  |                                  |                     |  |  |  |

| Flash                       | ECC (SEC/DED)       | Supported                                  |                                  |                                  |                     |  |  |  |

| FIDSI                       | Bank Modes          | Supported                                  |                                  |                                  |                     |  |  |  |

|                             | Size (Code/Work)    | 4MB / 128KB                                | 16MB / 512KB                     | 8MB / 256KB                      | 6MB / 128KB         |  |  |  |

|                             | Bus Interface       | AHB-Lite AXI, AHB-Lite                     |                                  |                                  |                     |  |  |  |

| SRAM                        | ECC (SEC/DED)       | Support                                    |                                  |                                  |                     |  |  |  |

| SKAW                        | TCM Size            | N/A                                        | 16KB ITCM, 16KB DTCM             |                                  | 64KB ITCM,64KB DTCM |  |  |  |

|                             | SRAM Size           | 512KB                                      | 2048KB                           | 1024KB                           | 640KB               |  |  |  |

| Boot                        |                     | Supported                                  |                                  |                                  |                     |  |  |  |

| Device Security with Crypto |                     | Supported                                  |                                  |                                  |                     |  |  |  |

| Direct Memory Access        | P-DMA               | Supported                                  |                                  |                                  |                     |  |  |  |

|                             | M-DMA               | Supported                                  |                                  |                                  |                     |  |  |  |

<sup>1</sup> This functionality is for debug purposes

#### **Revision History**

| Revision | ECN     | Submission<br>Date | Description of Change                                  |

|----------|---------|--------------------|--------------------------------------------------------|

| **       | 6381034 | 11/12/2018         | Initial release                                        |

| *A       | 6633371 | 7/22/2019          | Updated page 2, 3 to 6, 14 to 16, 18.<br>Added page 8. |

| *B       | 7060645 | 01/06/2021         | Updated Slide 2, 4, 6, 14                              |

| *C       | 8013047 | 03/15/2024         | Updated Slide 2, 3 to 7, 14 to 16, 18.                 |

# Part of your life. Part of tomorrow.