Customer training workshop

### TRAVEO<sup>™</sup> T2G Body Entry Clock System

#### Target products

> Target product list for this training material:

| Family category                                          | Series | Code flash memory size |

|----------------------------------------------------------|--------|------------------------|

| TRAVEO <sup>™</sup> T2G Automotive Body Controller Entry | CYT2B6 | Up to 576 KB           |

| TRAVEO <sup>™</sup> T2G Automotive Body Controller Entry | CYT2B7 | Up to 1088 KB          |

| TRAVEO <sup>™</sup> T2G Automotive Body Controller Entry | CYT2B9 | Up to 2112 KB          |

| TRAVEO™ T2G Automotive Body Controller Entry             | CYT2BL | Up to 4160 KB          |

**Hint Bar**

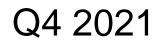

#### Introduction to CYT2BL

#### The clock system is part of the System Resources block

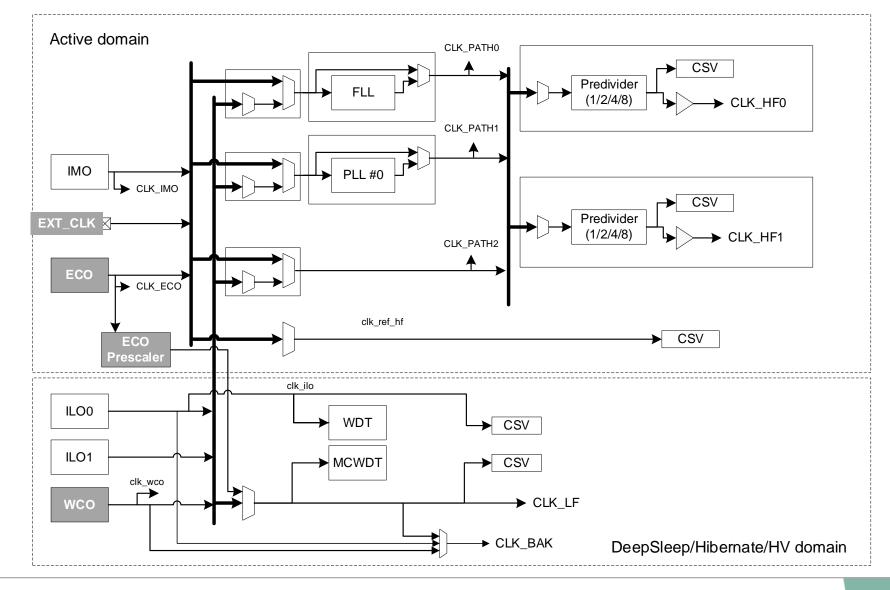

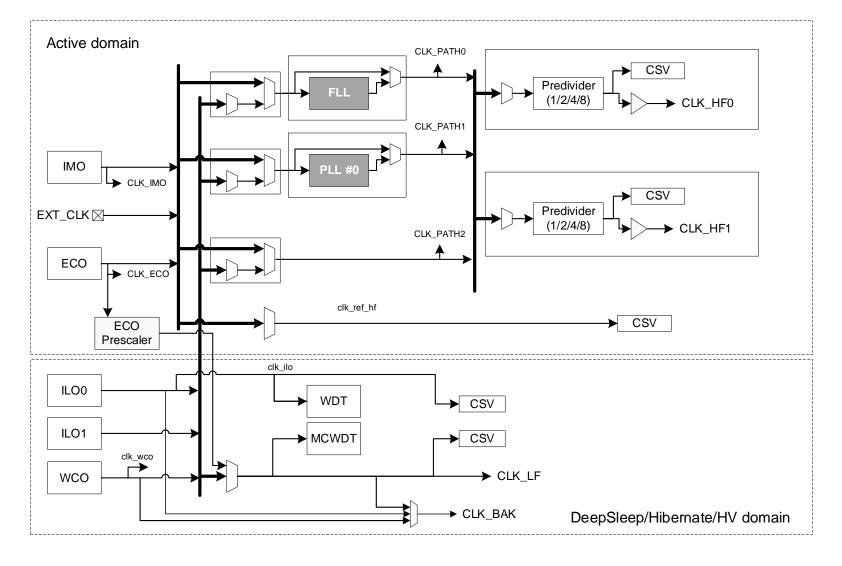

#### Clock system overview

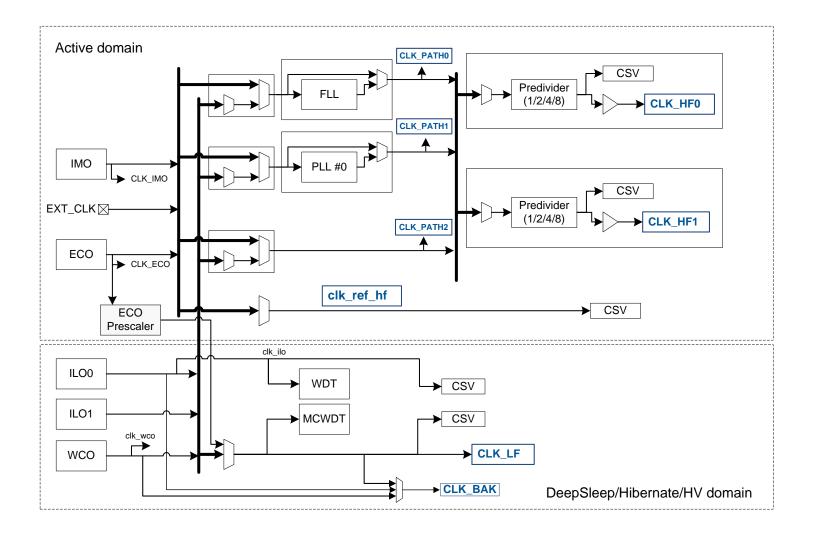

The clock system supplies clocks for MCU operation Hint Bar Features > **Review Chapter 18 in the** Internal clock sources TRM for additional details – 8-MHz IMO 32.768-kHz ILO0/1 External clock sources External crystal oscillator (ECO) Watch crystal oscillator (WCO) External clock (EXT\_CLK) generated using a signal through I/O pin It is also possible to output the internal clock **Clock** generation Phase lock loop (PLL) Frequency lock loop (FLL) Clock supervision (CSV) for detecting clock abnormality Clock calibration counter

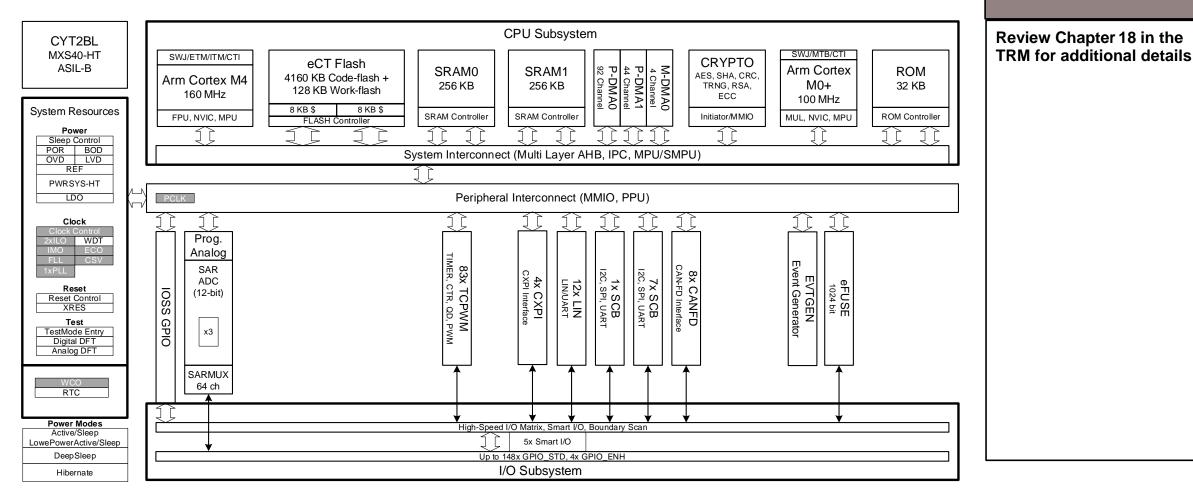

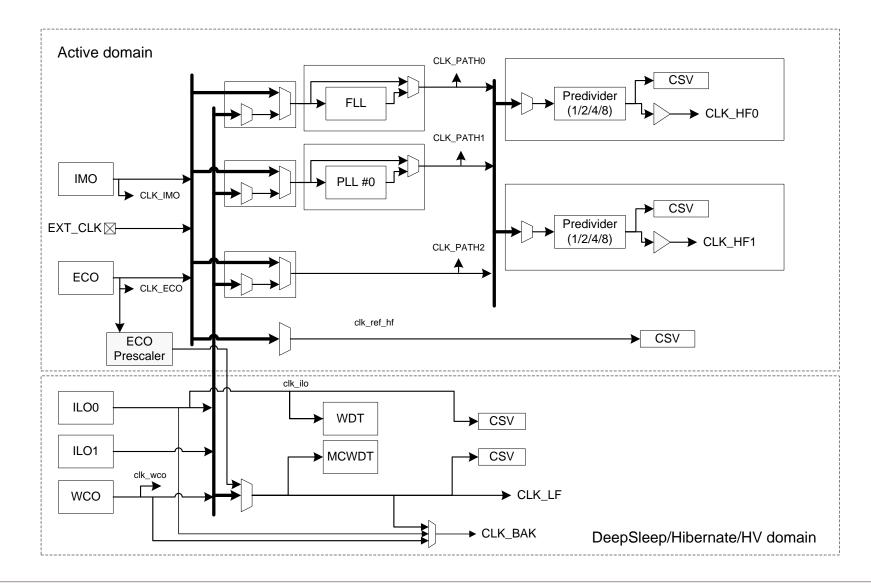

#### Clock system block diagram

#### Internal clock sources

- Internal main oscillator (IMO)

- Internal low-speed oscillator 0/1 (ILO0/1)

#### IMO: Internal main oscillator

- > Produces an 8-MHz fixed frequency

- > An accurate, high-speed internal (crystal-less) oscillator

- > Available in only Active and Sleep modes

- > Default clock source after POR or any other reset

- > Used by PLL0 to generate a wide range of high-frequency clocks

- > Enabled and disabled by register<sup>1</sup>

- Default is ENABLE<sup>2</sup>

| <b>Hint Bar</b> |  |

|-----------------|--|

|-----------------|--|

Review Section 18.2 in the TRM for additional details

Refer to the datasheet for additional details on AC specifications

<sup>1</sup> IMO should not be disabled if it is the source of the clock path to CLK\_HF[0] <sup>2</sup> Refer to the Register TRM (CLK\_IMO\_CONFIG) for additional details

#### ILO 0/1: Internal low-speed oscillators

#### > ILOO

- Produces a 32.768-kHz nominal fixed frequency

- Low power and low accuracy

- Available in all power modes

- Always the source of the Watchdog timer<sup>1</sup>

- > ILO1

- Used for ILO0 clock monitoring

- Parameters for ILO1 are the same as ILO0

Refer to the datasheet for additional details on AC specification

<sup>1</sup> Always leave the ILO enabled, as it is the source of the Watchdog timer

#### External clock sources

- > ECO

- > WCO

- > EXT\_CLK

- > ECO

- Contains an oscillator to drive an external 3.988 MHz to 33.34 MHz crystal

- Used by PLL0 to generate a wide range of high-frequency clocks

- ECO pre-scaler

- ECO trimming

- Enabled and disabled by register<sup>1</sup>

- Default is DISABLE

- > WCO

- Highly accurate 32.768-kHz clock source

- Primary clock source for the real-time clock (RTC)

- Enabled and disabled by register<sup>2</sup>

- Default is DISABLE

- > EXT\_CLK

- 0.25 MHz to 80 MHz clock that can be sourced from a designated I/O pin

- Can be used as the source clock for either the PLL or FLL

- Can be used to output the internal clock (CLK\_HF1 is available)

- When using a pin as an input to EXT\_CLK,

I/O must be set appropriately<sup>3</sup>

Refer to the Register TRM (CLK\_ECO\_CONFIG) for additional details

Refer to the Register TRM (CTL) for additional details

Refer to the TRM section 18.2.3 and the datasheet for additional details

Review Section 18.2 in the TRM for additional details

Refer to the datasheet for additional details on AC specification

### ECO trimming

- ECO supports a wide variety of crystals and ceramic resonators >

- ECO can be configured by register<sup>1</sup> >

- The following trim bit fields can be configured to control the maximum peak oscillation voltage across the crystal (VP), the transconductance (gm), and the nominal frequency (f):

- ATRIM (Amplitude Trim by AGC)

- GTRIM (Gain Trim)

- WDTRIM (Watchdog Trim)

- FTRIM (Filter Trim)

- RTRIM (Feedback Resistor Trim)

Max peak value:  $V_P = \frac{\sqrt{\frac{\nu_L}{2ESR}}}{\pi f(C_1 + C_2)}$

- f: Fundamental frequency of the crystal (XTAL)

- D<sub>i</sub>: Maximum drive level of XTAL

- ESR: Equivalent series resistance

- Shunt capacitance of XTAL

- C<sub>1</sub>: Parallel load capacitance of XTAL

Transconductance:  $g_m > 20 \times ESR \times (2\pi \times f)^2 \times (C_0 + C_L)^2$

Negative resistance:  $|R_{neg}| = \frac{g_m \times 4 \times C_L^2}{(2\pi \times f)^2 \times (4 \times C_L^2 + 4 \times C_L \times C_L)^2}$

Hint Bar

**Review TRM section 18.2** for additional details

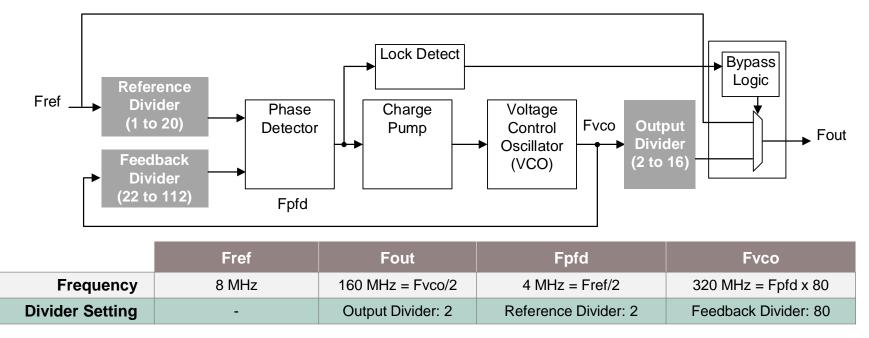

#### High-speed clock generation

- > Phase lock loop (PLL)

- > Frequency lock loop (FLL)

#### Clock generation: PLL and FLL

| > PLL |

|-------|

|-------|

- Input clock can be IMO (8 MHz), ECO, or EXTCLK

- PLL configuration parameters:

- Input clock range: 3.988 to 33.34 MHz

- Output clock range: 11 to 160 MHz (CYT2BL)<sup>1</sup>

- > FLL

- Input clock can be IMO (8 MHz), ECO, or EXTCLK

- A counter with a current-controlled oscillator (CCO)

- Starts up (locks) faster and uses lower power than the PLL

- The lock tolerance is user adjustable

- Parameters on the FLL configuration:

- Input clock range: 0.25 MHz to 80 MHz

- Output clock range: 24 MHz to 100 MHz (CYT2BL)<sup>1</sup>

| Н | int | Bar |

|---|-----|-----|

|   |     |     |

Review Section 18.3 in the TRM and Register TRM for additional details

Refer to the datasheet for additional details on AC specification

#### PLL configuration example

- > Parameters on PLL configuration:

- > Fref:

- > Fout (Fvco/Output divider):

- > Fpfd (Fref/Reference divider):

- > Fvco (Fpfd \* Feedback divider):

3.988 MHz to 33.34 MHz 11 MHz to 160 MHz (CYT2BL)<sup>1</sup>

4 MHz to 8 MHz

170 MHz to 400 MHz

**Hint Bar**

Review section 18.3.1 in the TRM and Register TRM for additional details

<sup>1</sup> Refer to the data sheet for target product.

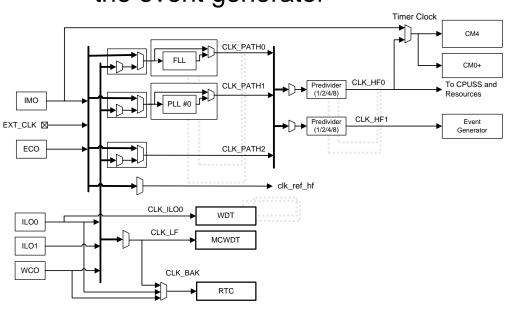

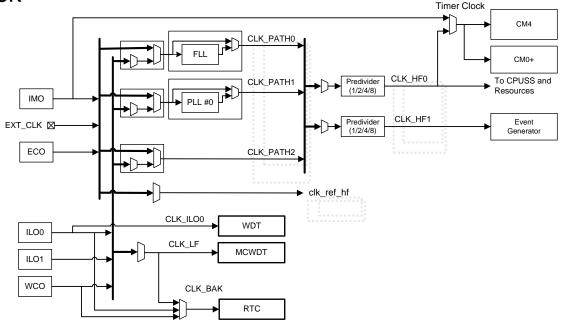

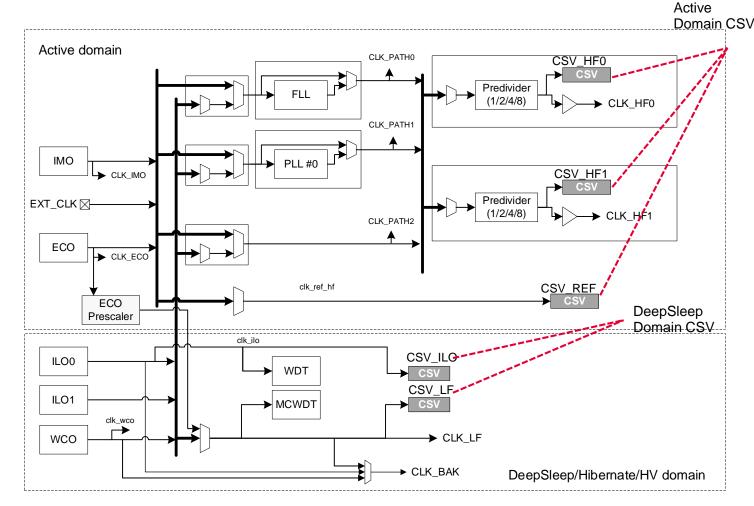

#### Clock trees

- > CLK\_PATH0/1/2

- > CLK\_HF0/1

- > clk\_ref\_hf

- > CLK\_LF

- > CLK\_BAK

- > CLK\_HF0 distribution

#### **Clock distribution**

- CLK\_PATHx

- Input sources for the CLK\_HF roots

- CLK\_PATH0 contains the FLL output Up to 100 MHz (using FLL)<sup>1</sup>

- CLK\_PATH1 contains the PLL output

Up to 160 MHz (using PLL)<sup>1</sup>

- CLK\_PATH2 is a connection to root clocks

Up to 22.24 MHz (using ECO)

- Up to 33.34 MHz (using ECO)

- CLK\_REF\_HF

- Selects IMO, ECO, EXTCLK

- Typically selects the IMO (8 MHz)

- Used as a reference clock for CLK\_HF0/1 clock supervision

<sup>1</sup> Refer to the data sheet for target product.

- CLK\_HF0/1

- Selects CLK\_PATH0, 1, 2

- CLK\_HF0 is the input source for the CPUSS and resources such as Timer, SCB, and SAR ADC

- CLK\_HF1 is the input source for the event generator

<sup>1</sup> Typically WCO is connected to RTC. CLK\_LF also can connect to RTC.

#### Clock distribution

- CLK\_LF >

- ILO0, ILO1, or WCO (32.768 kHz) can be the input clock for CLK\_LF

- Input sources for the MCWDT clock

- Uses reference clock for CLK\_ILO0 Clock Supervision

- CLK\_BAK >

- ILO0, ILO1, or WCO (32.768 kHz) can be the input clock for CLK\_BAK

- Input sources for RTC<sup>1</sup> clock

**Hint Bar**

Training section reference:

- CPU Subsystem

17

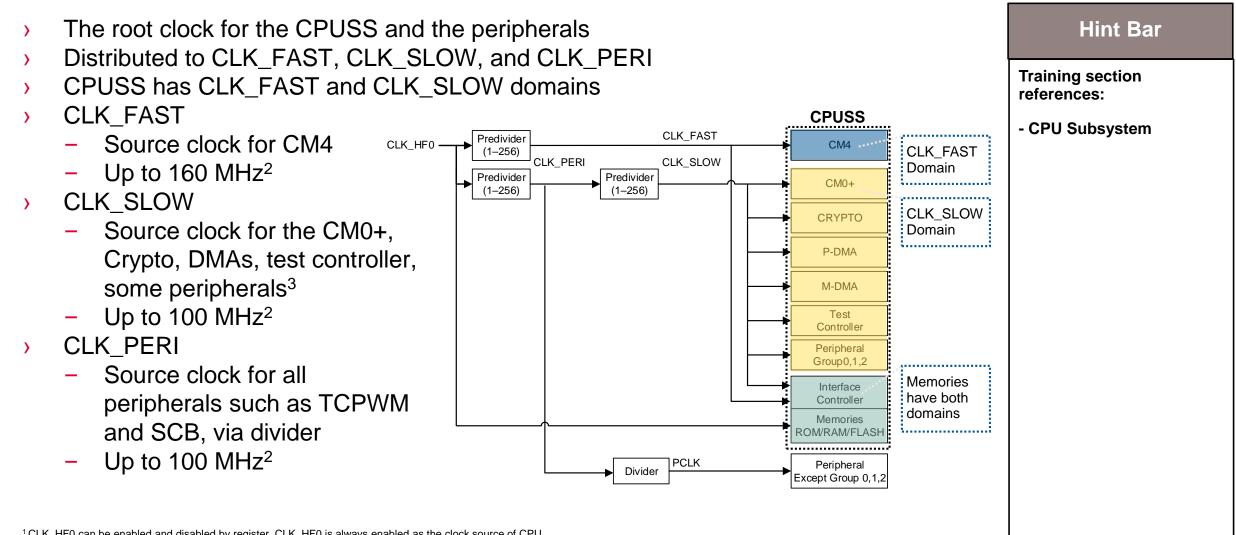

#### CLK\_HF0<sup>1</sup> distribution

<sup>&</sup>lt;sup>1</sup>CLK\_HF0 can be enabled and disabled by register. CLK\_HF0 is always enabled as the clock source of CPU.

<sup>&</sup>lt;sup>2</sup> Refer to the data sheet for target product.

<sup>&</sup>lt;sup>3</sup> CPUSS and PPU registers

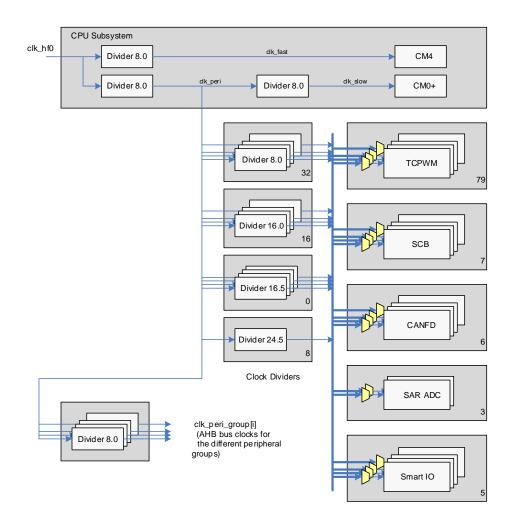

#### Peri clock distribution

- PERI clock divider >

- Four types of dividers<sup>1</sup>

- 8-bit divider

- 16-bit divider

- 16.5-bit divider \_

- 24.5-bit divider \_

- Fractional clock dividers supported \_

- Output of dividers can be routed to any peripheral

- Phase aligning \_

- Can be phase-aligned with any of the other (enabled) clock dividers.

| Hint Bar                                                                |

|-------------------------------------------------------------------------|

| Clock dividers can be<br>configured through the<br>following registers: |

| DIV_8_CTL                                                               |

| DIV_16_CTL                                                              |

| DIV_16_5_CTL                                                            |

| DIV_24_5_CTL                                                            |

| Clock Enable multiplexers                                               |

CI can be configured through **CLOCK\_CTL** registers, which are assigned for each peripheral

**Review Section 18.7 in the** TRM for additional details on clock numbers, which are assigned for each peripheral

<sup>1</sup>Not all dividers are supported

#### Clock supervision (CSV)

- Clock supervision (CSV) allows one clock to be monitored with another clock (reference clock)

- > Monitored clock sources:

- CLK\_HF0

- CLK\_HF1

- CLK\_REF\_HF

- ILO0

- CLK\_LF

- > CSV power domains:

- Active domain CSV

- DeepSleep domain CSV

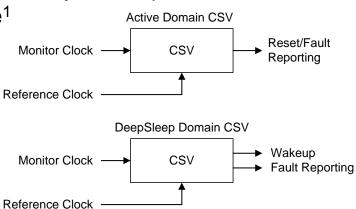

#### Clock supervision features

- > Checks that the frequency of the monitored clock is within the allowed frequency window

- Uses a reference clock to supervise the behavior of the monitor clock

| CSV Components | Monitor Clock | Reference Clock | Note                                               |

|----------------|---------------|-----------------|----------------------------------------------------|

| CSV_HF0/1      | CLK_HF0/1     | clk_ref_hf      | clk_ref_hf is typically selected the IMO (default) |

| CSV_REF        | clk_ref_hf    | ILO0            | -                                                  |

| CSV_ILO        | ILO0          | CLK_LF          | CLK_LF is selected WCO<br>or ILO1                  |

| CSV_LF         | CLK_LF        | ILO0            | -                                                  |

- Active domain CSV: CSV\_HF0/1, CSV\_REF

- Automatically stops during DeepSleep, and restarts by wakeup

- Wait function of monitoring start for startup time<sup>1</sup>

- Possible to generate a Reset or a Fault report

- DeepSleep domain CSV: CSV\_ILO, CSV\_LF

- Operates during Active and DeepSleep

- Generates Wakeup and Fault reports

- All CSVs are initially OFF

#### **Hint Bar**

See the Register TRM for additional details

<sup>1</sup>Need to prevent a false error detection at startup

## infineon

#### **CSV** operation

- The monitored clock generates a monitor event (Period), and the reference clock Hint Bar generates a lower and upper limit The monitor event is compared against a lower limit/upper limit The monitor clock and the reference clock are An error is reported if the monitor event  $\leq$  lower limit, or if the monitor event > upper limit asynchronous (typical). Therefore, the frequency Frequency is Normal Frequency is too Fast Frequency is too Slow window needs to account for maximum clock Period ——> — Period Period tolerance. Monitor Clock Monitor In Range 📕 Out of Range 📕 Out of Range Event Upper limit Upper limit Lower limit Lower limit Lower limit Reference Clock Normal Frequency Window

- > Advantages

- Detects whether the clock stops, runs too fast or runs too slow, and if the period is not within the frequency window

- Monitors clock in each power mode such as Active, Sleep, and DeepSleep with Active domain CSV and DeepSleep domain CSV

- Can achieve ASIL-B

#### Clock calibration counter

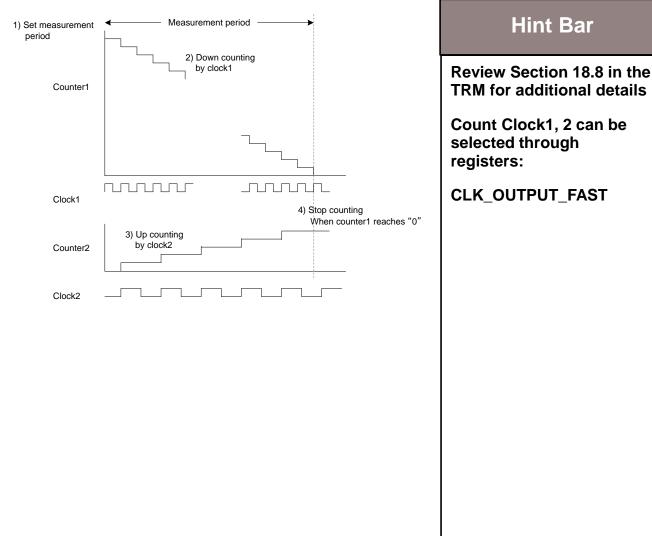

- > Clock calibration counter operation

- Two counters: Counter1 and Counter2

- Counter1 is clocked by clock1: reference clock

- Counter2 is clocked by clock2: measurement clock.

- Counter1 sets the measurement period by the count number of clock1

- Counter2 indicates the count number of clock2 during the measurement period

- Clock2 frequency can be calculated from the following formula using two count numbers:

$clock2 frequency = \frac{Counter2 value}{Counter1 value} \times clock1 frequency$

All clock sources are available as a source for these two clocks.

> Use case

Measure a lower-accuracy clock, such as the ILO, using a higher-accuracy clock such as the ECO

#### Comparison Between CYT2BL, CYT4BF, and CYT4DN (1/4)

|        | Features             | CYT2BL                             | CYT4BF                       | CYT4DN        | Note              |

|--------|----------------------|------------------------------------|------------------------------|---------------|-------------------|

| IMO    |                      | Supported                          |                              |               |                   |

| ECO    |                      |                                    | Supported                    |               |                   |

| ILO 0  |                      |                                    | Supported                    |               |                   |

| ILO 1  |                      |                                    | Supported                    |               |                   |

| WCO    |                      |                                    | Supported                    |               |                   |

| LPECO  |                      | Not impl                           | emented                      | Supported     |                   |

| FLL    | Number of FLL        |                                    | 1                            |               |                   |

|        | Input Range          | 0.25 to                            | 0.25 to 80 MHz 0.25 to 100 M |               |                   |

|        | Output Range         |                                    | 24 to 100 MHz                |               |                   |

| PLL    | Number of PLL        | 1 2                                |                              | 3             |                   |

|        | Input Range          |                                    | 3.988 to 33.34 MHz           |               |                   |

|        | Output Range         | 11 to 160 MHz                      | 11 to 2                      | 00 MHz        |                   |

| PLL400 | Number of PLL        | Not implemented                    | 2                            | 5             |                   |

|        | Input Range          | Not implemented 3.988 to 33.34 MHz |                              | 3.34 MHz      |                   |

|        | Output Range         | Not implemented 25 to 350 MHz (*)  |                              | 25 to 400 MHz | (*) Spreading off |

|        | SSCG                 | Not implemented Yes                |                              |               |                   |

|        | Fractional Operation | Not implemented                    | Yes                          |               |                   |

#### Comparison Between CYT2BL, CYT4BF, and CYT4DN (2/4)

| Fe           | eatures    | CYT2BL CYT4BF                  |                                | CYT4DN                               | Note |

|--------------|------------|--------------------------------|--------------------------------|--------------------------------------|------|

| CLK Trees    | CLK_PATH 0 |                                | FLL                            |                                      |      |

| Source Clock | CLK_PATH 1 | PLL                            | PLL                            | PLL400                               |      |

|              | CLK_PATH 2 | ECO,IMO,EXT_CLK,WCO,<br>ILO0/1 | PLL                            | 400                                  |      |

|              | CLK_PATH 3 | ECO,IMO,EXT_CLK,WCO,<br>ILO0/1 | PLL                            | PLL400                               |      |

|              | CLK_PATH 4 | Not implemented                | PLL                            | PLL400                               |      |

|              | CLK_PATH 5 | Not implemented                | ECO,IMO,EXT_CLK,WCO,<br>ILO0/1 | PLL400                               |      |

|              | CLK_PATH 6 | Not impl                       | Not implemented                |                                      |      |

|              | CLK_PATH 7 | Not impl                       | emented                        | PLL                                  |      |

|              | CLK_PATH 8 | Not implemented                |                                | PLL                                  |      |

|              | CLK_PATH 9 | Not implemented                |                                | ECO,IMO,EXT_CLK,WCO,<br>ILO0/1,LPECO |      |

|              | CLK_REF_HF | ECO,IMO,EXT_CLK                |                                | ECO,IMO,EXT_CLK<br>,LPECO            |      |

|              | CLK_TIMER  | CLK_HF0, IMO                   |                                | 0                                    |      |

|              | CLK_LF     | ILO0/1, WCO, ECO               |                                | ILO0/1, WCO, ECO<br>,LPECO           |      |

|              | CLK_BAK    | CLK_LF, ILO0, WCO              |                                | CLK_LF, ILO0, WCO<br>,LPECO          |      |

#### Comparison between CYT2BL, CYT4BF, and CYT4DN (3/4)

| Featu            | ires     | CYT2BL                                     | CYT4BF                                     | CYT4DN                                     | Note |

|------------------|----------|--------------------------------------------|--------------------------------------------|--------------------------------------------|------|

| CLK Distribution | CLK_HF0  | CPUSS clocks, PERI, and AHB infrastructure | CPUSS (Memories,<br>CLK_SLOW, Peripherals) | CPUSS (Memories,<br>CLK_SLOW, Peripherals) |      |

|                  | CLK_HF1  | Event Generator                            | CPUSS (Cortex-M7 CPU 0, 1)                 | CPUSS (Cortex-M7 CPU 0, 1)                 |      |

|                  | CLK_HF2  | Not connect                                | CAN FD, FlexRay, LIN,<br>TCPWM, SCB, SAR   | CAN FD, CXPI, LIN, SCB,<br>SAR             |      |

|                  | CLK_HF3  | Not implemented                            | Event Generator                            | Event Generator                            |      |

|                  | CLK_HF4  | Not implemented                            | Ethernet                                   | Ethernet                                   |      |

|                  | CLK_HF5  | Not implemented                            | Audio subsystem                            | Sound Subsystem #0                         |      |

|                  | CLK_HF6  | Not implemented                            | SDHC Interface, SMIF                       | Sound Subsystem #1                         |      |

|                  | CLK_HF7  | Not implemented                            | Not connect                                | Sound Subsystem #2                         |      |

|                  | CLK_HF8  | Not implemented                            | Not implemented                            | SMIF #0                                    |      |

|                  | CLK_HF9  | Not implemented                            | Not implemented                            | SMIF #1                                    |      |

|                  | CLK_HF10 | Not implemented                            | Not implemented                            | Video Subsystem                            |      |

|                  | CLK_HF11 | Not implemented                            | Not implemented                            | Video Display #0                           |      |

|                  | CLK_HF12 | Not implemented                            | Not implemented                            | Video Display #1                           |      |

|                  | CLK_HF13 | Not implemented                            | Not implemented                            | Not connect                                |      |

#### Comparison between CYT2BL, CYT4BF, and CYT4DN (4/4)

|                     | Features                 | CYT2BL CYT4BF                                            |  | CYT4DN | Note |

|---------------------|--------------------------|----------------------------------------------------------|--|--------|------|

| Clock Divider       | Number of Dividers       | 1 2                                                      |  | 2      |      |

|                     | Fractional Clock Divider | 24.5-bit dividers16.5-bit dividers,<br>24.5-bit dividers |  |        |      |

|                     | Phase Aligning           | Supported                                                |  |        |      |

| Clock Supervision   |                          | Supported                                                |  |        |      |

| Calibration Counter |                          | Supported                                                |  |        |      |

# Part of your life. Part of tomorrow.

#### **Revision History**

| Revision | ECN     | Submission<br>Date | Description of Change                                                                                                                                       |

|----------|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 6157641 | 04/29/2018         | Initial release                                                                                                                                             |

| *A       | 6364397 | 10/25/2018         | Added slide 2 and the note descriptions of all pages.<br>Updated slides 3-6, 9, 11, 14, 19.<br>Added Clock Calibration Counter slide<br>Updated the figures |

| *В       | 7060645 | 01/06/2021         | Updated slide 2 - 4, 8, 10, 13, 16, 17, 18, 25-28<br>Deleted slide 4<br>Added slide 11                                                                      |

| *C       | 7450141 | 11/16/2021         | Updated slide 1, 2, 14                                                                                                                                      |