# Customer training workshop TRAVEO™ T2G audio digital-analog converter

# Target products

# Target product list for this training material

| Family Category                | Series | Code Flash Memory Size |

|--------------------------------|--------|------------------------|

| TRAVEO™ T2G Automotive Cluster | CYT3DL | Up to 4160KB           |

| TRAVEO™ T2G Automotive Cluster | CYT4DN | Up to 6336KB           |

| TRAVEO™ T2G Automotive Cluster | CYT4EN | Up to 6336 KB          |

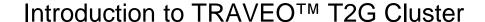

The Audio DAC is part of peripheral blocks

### **Hint Bar**

Review TRM chapter 34 for additional details

### Audio DAC overview

- Audio digital-to-analog converter (DAC) converts the PCM data to analog and drives to both left and right pins respectively

- Features

- Programmable sampling rate (from 8 kHz to up to 48 kHz) and frequency control

- 64 entry TX FIFOs with interrupt and trigger support

- Two 16-bit PCM data each for left and right to form a stereo

- Cascaded Integrated-Comb (CIC) filter, Finite Impulse Response (FIR) filter, Interpolation filter, and delta-sigma modulator (DSM)

### **Hint Bar**

Review TRM section 34.6 for additional details

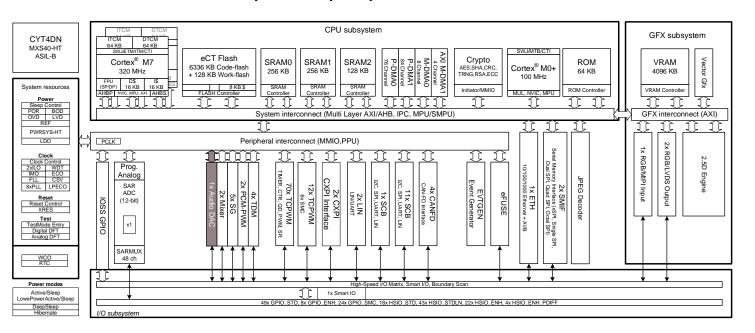

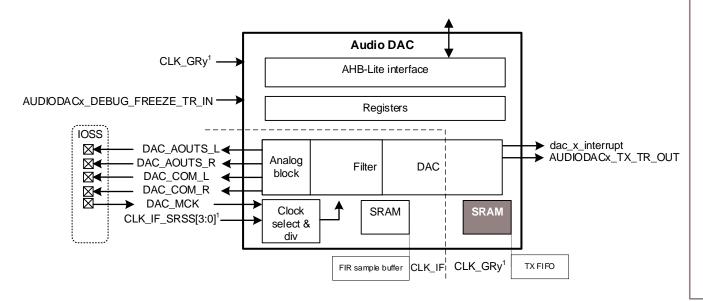

# Audio DAC block diagram

# Audio DAC components

- Clock

- TX FIFO

### **Hint Bar**

Review TRM section 34.6.2 for additional details

<sup>&</sup>lt;sup>1</sup> See the device datasheet for assigned clocks to CLK\_IF\_SRSS[3:0] and CLK\_GRy

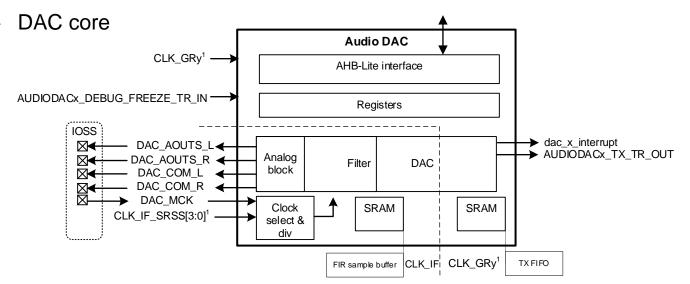

# Audio DAC components - Clock

### Clock

- Clock selection and divider

- Oversampling rate

### **Hint Bar**

Review TRM section 34.6.3 for additional details

<sup>&</sup>lt;sup>1</sup> See the device datasheet for assigned clocks to CLK\_IF\_SRSS[3:0] and CLK\_GRy

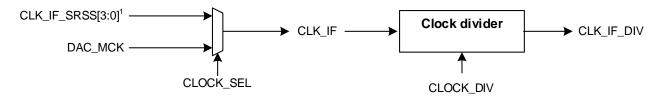

### Clock selection and divider

PWM interface clock can be derived from one of these clock signals

| Signal                        | Description            |

|-------------------------------|------------------------|

| CLK_IF_SRSS[3:0] <sup>1</sup> | One of the SRSS clocks |

| DAC_MCK                       | External master clock  |

The divided clock will be used as the DAC core system clock

### **Hint Bar**

Review TRM section 34.6.3 for additional details

Review the Clock System Training section for additional details about high-frequency clocks

DAC core system clock frequency is the function of CLK\_IF/(CLOCK\_DIV+1)

<sup>&</sup>lt;sup>1</sup> See the device datasheet for assigned clocks to CLK IF SRSS[3:0]

# Oversampling rate

- System clock frequency can be used to perform oversampling on the DAC components to achieve the required sampling rate (Fs)

- Recommended Fs with system clock frequency configuration

| FS_SEL | OSR | System Clock<br>Frequency | Fs (kHz)           |

|--------|-----|---------------------------|--------------------|

| 01     | 128 | 256 x Fs                  | 32, 44.1, 48       |

| 10     | 256 | 256 x Fs                  | 16, 22.05, 24      |

| 11     | 512 | 512 x Fs                  | 8, 11.05, 12, 12.8 |

### **Hint Bar**

Review TRM section 34.6.3 for additional details

Fs and system clock can only be configured when there is no in-flight PCM data, and DAC\_BUSY = 0 before the start of DAC use

FS\_SEL: Sample frequency select

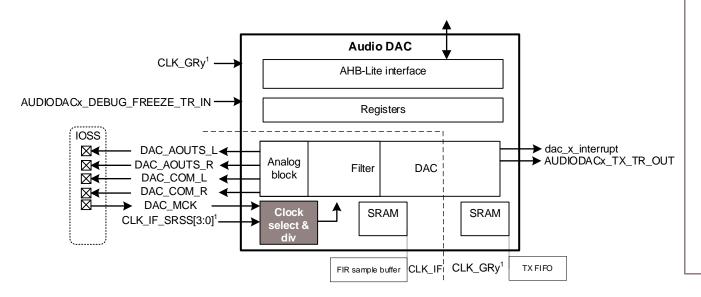

# Audio DAC components – TX FIFO

- Audio DAC components

- TX FIFO

### **Hint Bar**

Review TRM section 34.6.6 for additional details

<sup>&</sup>lt;sup>1</sup> See the device datasheet for assigned clocks to CLK\_IF\_SRSS[3:0] and CLK\_GRy

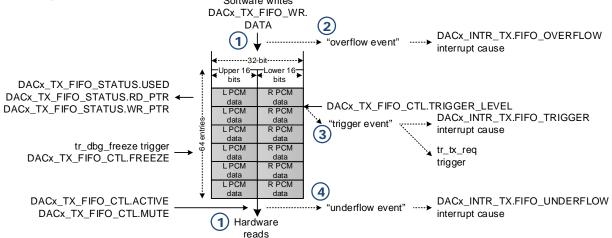

# TX FIFO operation

- TX FIFO operation follows these steps:

- SW writes to TX FIFO and HW reads from TX FIFO to transfer PCM data to DAC core

- When SW writes to a full TX FIFO, HW sets INTR\_TX.FIFO\_OVERFLOW interrupt

- When TX\_FIFO\_STATUS.USED < TX\_FIFO\_CTL.TRIGGER\_LEVEL, HW sets tx\_tx\_req trigger and INTR\_TX.FIFO\_TRIGGER interrupt

- When HW reads from an empty FIFO, HW sets INTR\_TX.FIFO\_UNDERFLOW interrupt

Software writes

### Hint Bar

Review TRM section 34.6.6 for additional details

Review the Registers TRM for additional details

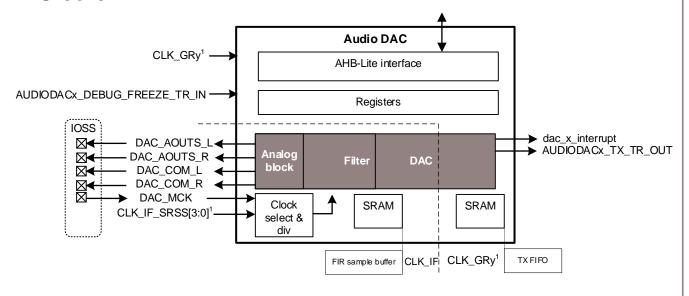

# Audio DAC components – DAC core

# Audio DAC components

DAC core

### **Hint Bar**

Review TRM section 34.6.5 for additional details

<sup>&</sup>lt;sup>1</sup> See the device datasheet for assigned clocks to CLK\_IF\_SRSS[3:0] and CLK\_GRy

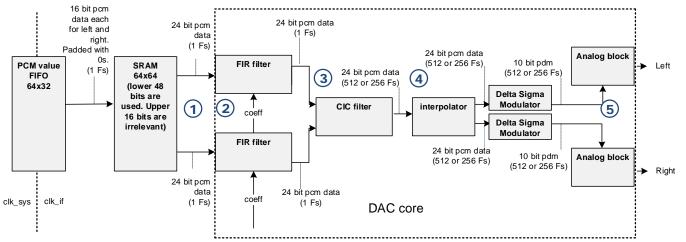

# DAC core process

### DAC processing path

- Audio DAC receives the processed two-channel data from TX FIFO

- The data goes through the FIR filter with a series of delays, multiplier, and adder

- The data is fed through the CIC filter with comb-type filters and integral filters

- The interpolator converts PCM data to PDM bitstream and feeds it to DSM for noise shaping

- 5 Output of the DSM drives the multi-level DAC after synchronization and level shifting

### Hint Bar

Review TRM section 34.6.5 for additional details

The processing of the FIR filter, CIC filter, interpolator, and DSM cannot be configured by the user

Review the Appendix section for additional details about FIR filter, CIC filter, and Delta-Sigma Modulator (DSM)

Noise shaping increases the apparent S/N ratio of the resultant signal by lowering the noise present in the audible range and increasing the noise above the audible range

# Appendix

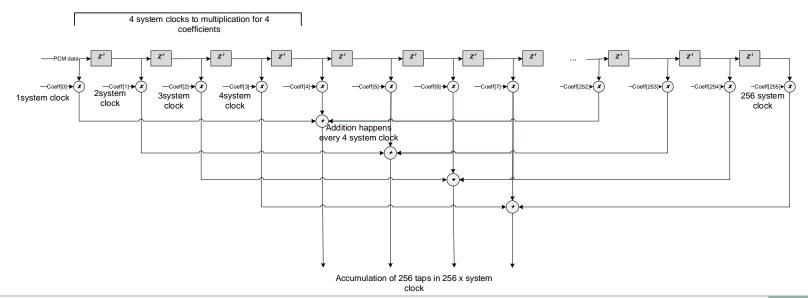

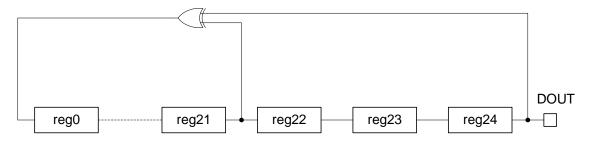

### FIR Filter

- FIR filter in DAC core

- Coefficient multiplication of 256 TAPs is carried with one multiplier

- Four multiplications are performed for one sample value with system clock/4 frequency (64 Fs)

- Result of the multiplication is accumulated in every system clock/4 frequency (64 Fs), which equals to 64 TAP multiplications of 4 (4 x 64) = 256 TAPs being executed

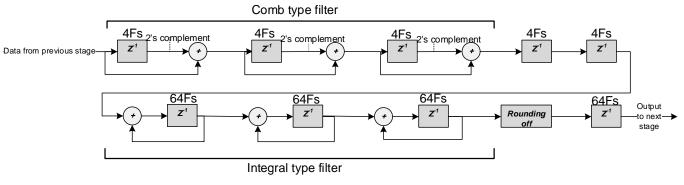

### CIC Filter

- CIC filter in DAC core

- First three stages: Comb-type filter

- Operates at system clock/64 (4 Fs)

- Last three stages: Integral-type filter

- Operates at system clock/4 (64 Fs)

- CIC-Interpolation is sequentially connected and outputs in 256 Fs rate

- Advantage

- Has anti-aliasing and oversampling role

### **Hint Bar**

Review TRM section 34.6.5 for additional details

Cascaded Integrated-Comb (CIC)

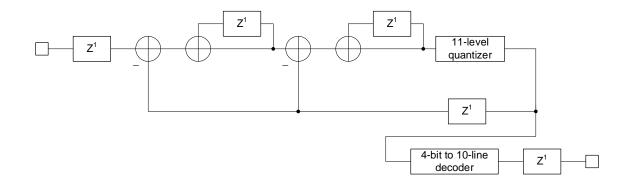

# Delta-sigma modulator (1/2)

- CIDF delta-sigma modulation circuit

- Set the quantizer to 11-level

- Quantization noise in passband is reduced by more than 1-bit delta-sigma configuration

- Decode 11-level (4-bit) to 10-line (weight is equal to 1)

- Drive analog DAC block with PDM waveform

### **Hint Bar**

Review TRM section 34.6.5 for additional details

Pulse density modulation (PDM)

# Delta-Sigma Modulator (2/2)

# Dynamic Element Matching

- Averages the output voltage by sequentially changing the elements at the "High" level

- To reduce the influence of the relative error that can increase noise and distortion

### Dithering

- Suppresses idle tone generation

- Is added before DSM to improve S/N ratio

### **Hint Bar**

Review TRM section 34.6.5 for additional details

Signal-to-noise ratio (S/N ratio)

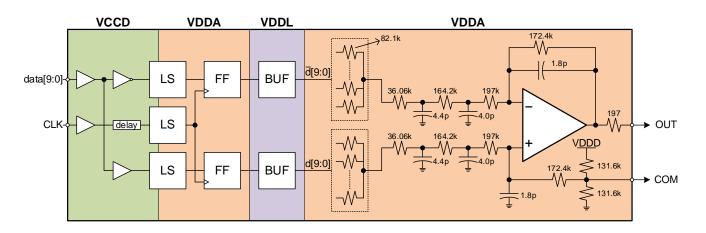

# Analog block

- Output of the DSM passes through LSs, FFs, and BUFs, and finally drives the DAC input resistors

- DAC resistors are summed at the input of opamp

- An active third-order LPF with cut-off frequency of 90 kHz is used

- To filter high-frequency quantization noise

- To provide low-impedance drive

### Hint Bar

Review TRM section 34.6.5 for additional details

Level-shifter (LS)

Flip-flop (FF)

Logic buffer (BUF)

Low-pass filter (LPF)

Part of your life. Part of tomorrow.

| Revision | ECN     | Submission Date | Description of Change                         |

|----------|---------|-----------------|-----------------------------------------------|

| **       | 6638977 | 2019/07/29      | Initial release                               |

| *A       | 6805412 | 2020/02/12      | Added note descriptions in each slide         |

| *B       | 7052598 | 2020/12/21      | Updated 2, 5, 6, 7, 9, 11                     |

| *C       | 7799385 | 2022/08/17      | Updated 1 to 6, 9, 11. Removes the Test mode. |