## **Programming Guide and User Manual**

## **About this document**

- This document describes how to program the TLI4971 with the Infineon proprietary one wire interface (SICI).

- Timing of the serial inspection interface.

- Command structure and commands for write/read and EEPROM access.

- A description of the user changeable EEPROM section.

- Details on the diagnosis mode.

For productive in circuit programming Infineon recommends to use a verified programmer which has been a coproduction development between Infineon and CGS. For further documentation please refer to <a href="Sensor-Programmer-CGS">Sensor-Programmer-CGS</a> - Computer Gesteuerte Systeme GmbH (cgs-gruppe.de)

Further Infineon provides a programming board for laboratory usage.

### **Scope and purpose**

TLI4971 Coreless Current Sensor Feature set, EEPROM and interface description.

### **Intended audience**

- Users who use the high variety of the TLI4971 current sensor by programming the functionality like full scale or over current detection, operating modes etc. to their need.

- Current Sensor Module Developers.

# **Programming Guide and User Manual**

## **Current Sensor TLI4971**

## **Table of contents**

| Curr       | rent Sensor TLI4971                                  |    |

|------------|------------------------------------------------------|----|

| Abou       | ut this document                                     |    |

| Table      | le of contents                                       | 2  |

| 1          | Application and Programming circuit                  | 3  |

| 1.1        | Circuit / Precondition                               | 3  |

| 1.2        | In-circuit programming                               | 4  |

| 2          | Serial Inspection and Configuration Interface (SICI) | 6  |

| 2.1        | Hardware Implementation                              | 6  |

| 2.2        | Entering Communication Mode                          |    |

| 2.3        | Communication timing                                 |    |

| 2.3.1      | 0 , 0                                                |    |

| 2.4        | Interface Timing Definition                          |    |

| 2.5        | Definition of Voltage Levels                         |    |

| 3          | Interface description                                |    |

| 3.1<br>3.2 | Command Structure                                    |    |

| 3.2<br>3.3 | Read / Write CommandInterface Commands               |    |

| 3.4        | Write and programming sequence                       |    |

| 3.5        | Temporary register                                   |    |

| 3.6        | Read Example (temperature register read out)         |    |

| 4          | EEPROM                                               |    |

| 4.1        | EEPROM Content                                       |    |

| 4.2        | Programming Example                                  |    |

| 4.3        | Margin Test                                          | 19 |

| 4.4        | Cyclic Redundancy Check                              | 21 |

| 4.5        | Code example CRC calculation                         | 23 |

| 5          | Operation Mode                                       | 24 |

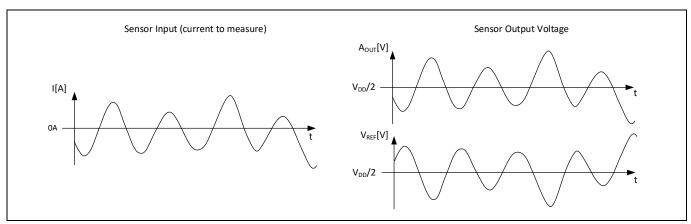

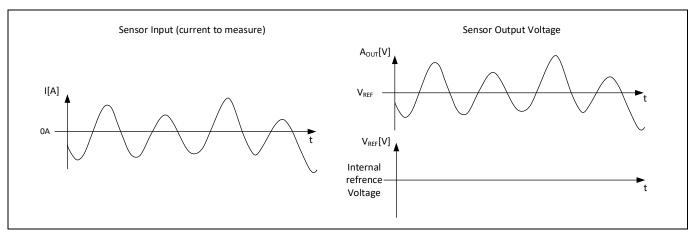

| 5.1        | Single-Ended Mode                                    |    |

| 5.2        | Fully-differential Mode                              |    |

| 5.3        | Semi-differential Mode                               |    |

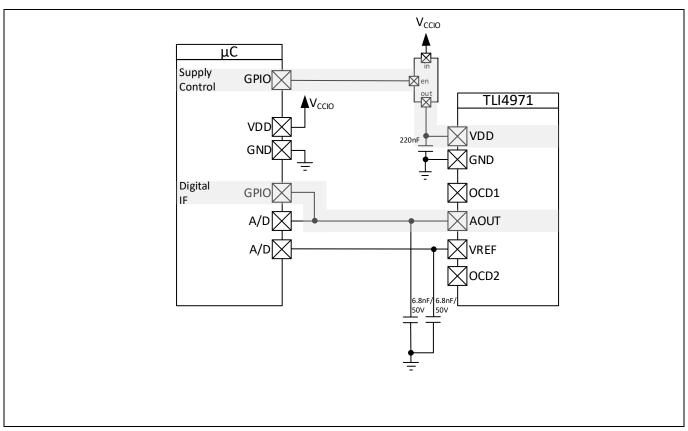

| 6          | How to connect the sensor in a 5V domain             |    |

| 6.1        | Single-Ended Mode                                    |    |

| 6.2        | Semi and or Fully-differential Mode                  |    |

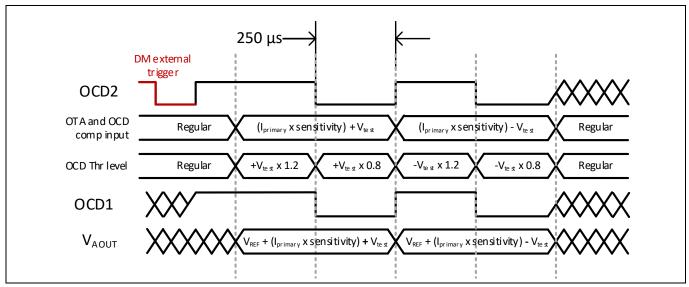

| 7          | Diagnosis Mode                                       | 27 |

| Q          | Glossary                                             | 29 |

# 1 Application and Programming circuit

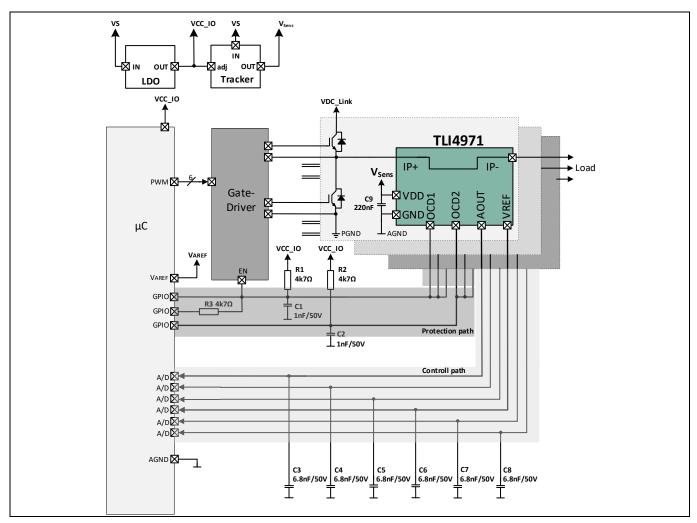

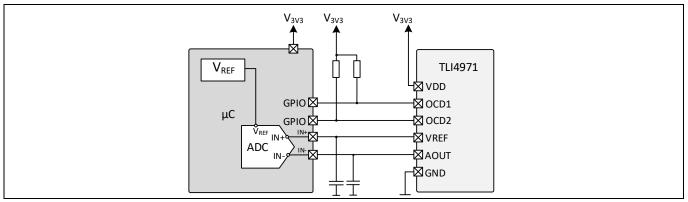

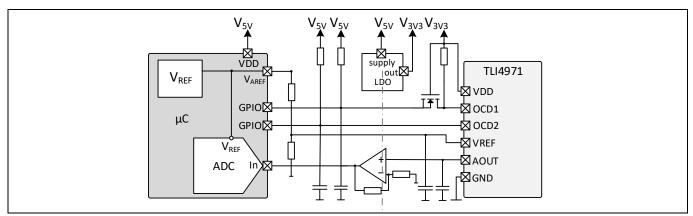

The sensor has implemented a serial interface to set the EEPROM content. This chapter describes the hardware environment to program the device. Further, it shows the recommended circuit for a three-phase GPD application.

Figure 1 TLI4971 3-phase GPD application circuit for semi and or fully-differential mode

The protection functionality is covered by two open drain outputs (OCD1 and OCD2) to indicate an overload and to protect the system in case of an over current event. The OCD1 output shut down the HV gate-driver. The OCD2 connect to an interrupt input of the microcontroller.

## 1.1 Circuit / Precondition

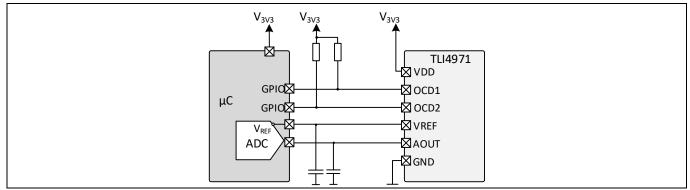

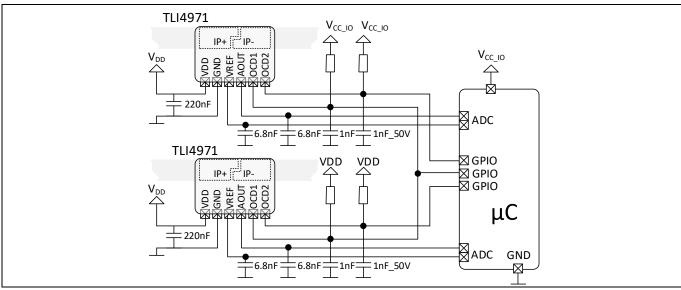

Each device can be set separately via the SICI-one wire interface.

In order to communicate with the sensor via the SICI one wire interface the  $A_{OUT}$  lines of each sensor need to connect to a microcontroller.

As a first step of the programming procedure, the parameter set has to download into the volatile memory area of the sensor via the SICI interface.

In a second step, the parameter needs to get stored into the EEPROM by sending the programming command and applying the programming voltage on OCD2 pin.

OCD2 and V<sub>DD</sub> need to be controlled by the programmer.

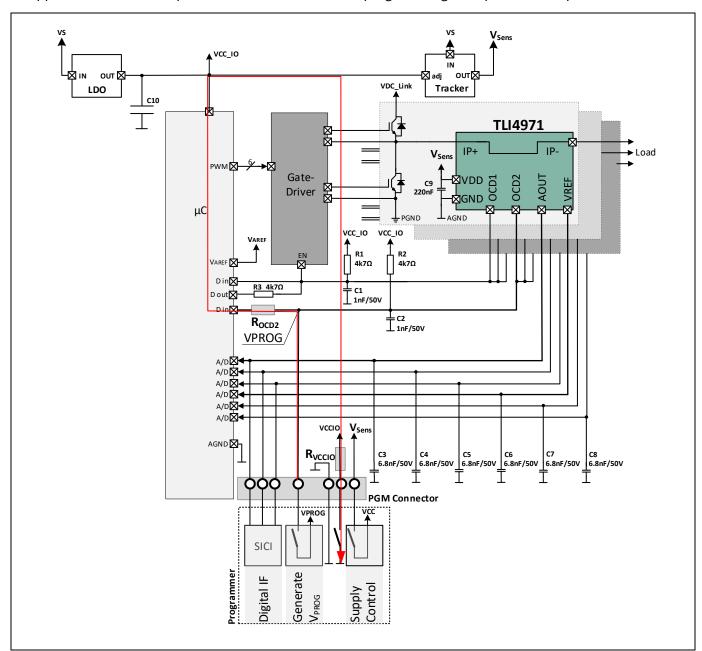

#### 1.2 **In-circuit programming**

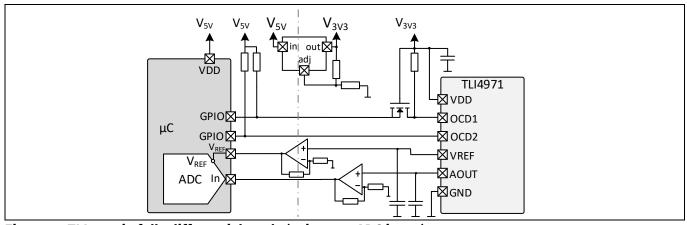

To program the EEPROM the digital interface sends a particular programming sequence and applies the programming voltage at pin OCD2. In a multiple sensor system the OCD2 can be connected together as each sensor will receive their individual data set via the separated A<sub>OUT</sub> pin connection. The programming voltage can be applied to all sensors in parallel. Please find a detailed programming example in the chapter 3.

Figure 2 External Programmer connected to GPD application circuit (TLI4971 in-circuit-programming)

The recommended serial resistors R<sub>OCD2</sub> and R<sub>VCCIO</sub> are used to avoid a current feedback into the supply and to avoid possible high floating of the µC supply. The resistors R<sub>OCD2</sub> and R<sub>VCCIO</sub> have to be determined as described in following formula.

$$\frac{V_{CCIO}}{R_{VCCIO}} > \frac{V_{PROG} - V_{CCIO}}{R_{OCD2}} \mid R_{OCD2} = 10 \text{k}\Omega \, \text{R}_{VCCIO} = 330\Omega$$

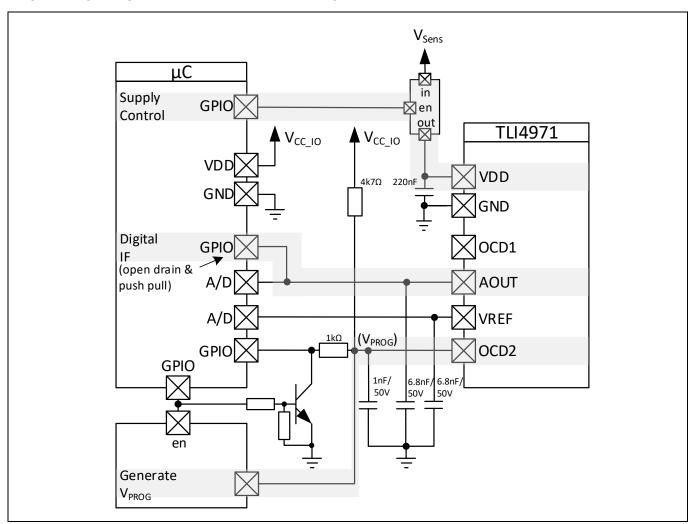

Alternatively, the OCD2 channel can be connected with a pull down resistor to GND while applying the programming voltage on the OCD2 pin as shown in Figure 4.

Figure 3: TLI4971 In-circuit programming without external programmer

#### **Serial Inspection and Configuration Interface (SICI)** 2

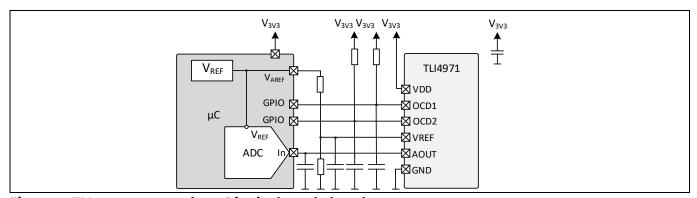

The sensor features a digital 16bit bidirectional one wire interface (SICI). Connect the A<sub>OUT</sub> pin to a GPIO port in order to establish a communication between the sensor and the controller.

#### 2.1 **Hardware Implementation**

Figure 4 SICI application circuit

To activate the interface the AOUT shall be forced to GND during and after the sensor startup.

The communication is based on transmitting a bit stream to the sensor driven by an external controller. For this interface, the A<sub>OUT</sub> pin is used as an I/O pin to read from the device and to write the registers of the device by driving the pin with a defined timing.

The interface timing specification is shown in Table 1 and described in Figure 6 and Figure 7.

#### 2.2 **Entering Communication Mode**

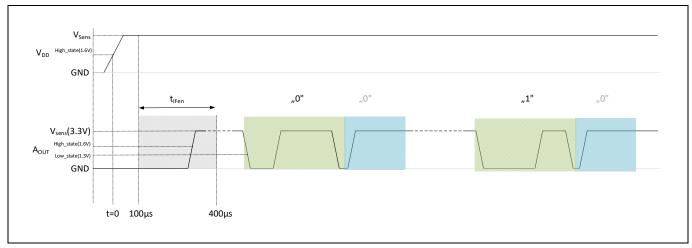

After or while suppling the sensor, the A<sub>OUT</sub> pin shall be forced to GND to enter the interface mode of the device. Figure 5 shows the "interface enable time" t<sub>IFen</sub> which is the valid time window to enable the SICI interface. This low state has only to be present once after start up to allow the device to receive the 16 bit enter-interfacecommand. The activation will also work if the A<sub>OUT</sub> stays at ground from the beginning. While sending the enterinterface-command, the device answers to each sent bit with logic "0" as shown in Figure 5.

After sending the enter-interface-command, the A<sub>OUT</sub> pin will remain at V<sub>Sens</sub> (open drain). If the interface activation is not successful the A<sub>OUT</sub> pin will reflect the quiescent voltage.

To enable the access to the sensor memory the internal intelligent state machine (ISM) needs to be disabled with a dedicated command like described in chapter 3.

Figure 5 Enabling SICI interface after device start up

## 2.3 Communication timing

As communication runs in both direction the GPIO of the external controller shall support tri state. After releasing the  $A_{\text{OUT}}$  back to  $V_{\text{Sens}}$ , the 16-bit enter-interface-command with LSB first has to be send from the controller. Figure 5 shows the LSB and MSB of the enter-interface-command.

In the Figure 5, the green highlighted squares indicate the received bit while the blue highlighted squares indicate the bits sent by the sensor.

## 2.3.1 Single low/high PWM transmission

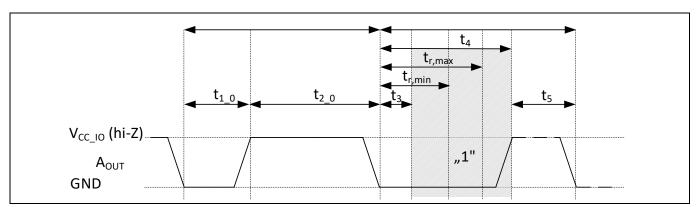

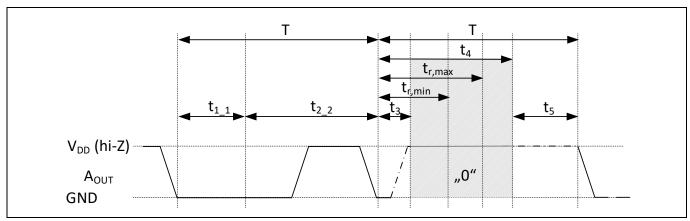

The initial pulse length t<sub>1</sub> & t<sub>2</sub> in Figure 6 and Figure 7 determines the write sequence.

Figure 6 SICI duty cycle; sending logic '0' to the device; receiving logic '1' from the device

The read-out time  $t_4$  is marked with a grey square. The timing of the read sequence  $t_4$  is depending on the low time  $t_1$  and high time  $t_2$  as described in Table 1.

Figure 7 SICI duty cycle; sending logic '1' to the device; receiving logic '0' from the device

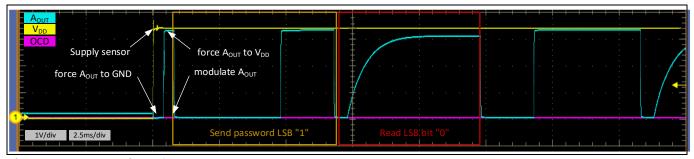

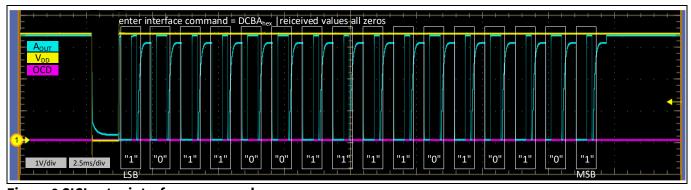

Figure 8 SICI enter interface sequence

Figure 8 describes the interface activation by modulating the AOUT after startup. The modulation of the first two bits can be seen in the picture.

Figure 9 SICI enter interface command

Figure 9 shows the oscilloscope picture of the enter interface command to activate the sensor interface after performing the startup sequence.

#### **Interface Timing Definition** 2.4

Table 1 Interface timing

| Parameter             | Symbol                  | Min.                                       | Тур.                           | Max. | Unit                | Notes                                                                                                                                                                                                        |

|-----------------------|-------------------------|--------------------------------------------|--------------------------------|------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface enable time | t <sub>IFen</sub>       | 100                                        | 150                            | 400  | μs                  | Drive A <sub>OUT</sub> to GND                                                                                                                                                                                |

| Period time of 1 bit  | Т                       | 40                                         | t <sub>1</sub> +t <sub>2</sub> | 7500 | μs                  | One communication frame consist of 16 x 2 bits (16bits write / 16bits read)                                                                                                                                  |

| Low time sending 0    | <i>t</i> <sub>1_0</sub> | 28                                         | 33                             | 38   | % of T              | Drive A <sub>OUT</sub> to GND                                                                                                                                                                                |

| Low time sending 1    | <i>t</i> <sub>1_1</sub> | 62                                         | 67                             | 72   | % of T              | Drive A <sub>OUT</sub> to GND                                                                                                                                                                                |

| High time sending 0   | t <sub>2_0</sub>        |                                            | T-t <sub>1_0</sub>             |      | μs                  | The device drives A <sub>OUT</sub> to V <sub>DD</sub> by default.                                                                                                                                            |

| High time sending 1   | t <sub>2_1</sub>        |                                            | T-t <sub>1_0</sub>             |      | μs                  | The device drives A <sub>OUT</sub> to V <sub>DD</sub> by default.                                                                                                                                            |

| Low time before read  | t <sub>3</sub>          | 10                                         | -                              | 30   | % of t <sub>4</sub> | Drive $A_{OUT}$ to GND<br>$t_4 = 2 * ABS(t_{1\_X} - t_{2\_X})$<br>$t_3$ can be set as applicable. Increase of<br>$t_3$ will reduce sensor response time $t_4$ .<br>Therefore $t_r$ has to be set accordingly |

| Reading time          | <i>t</i> r              | 50                                         | -                              | 80   | % of t <sub>4</sub> | The device drives A <sub>OUT</sub> to V <sub>DD</sub> by default. Set the external controller in tri state.                                                                                                  |

| Response time         | <i>t</i> <sub>4</sub>   | 2 abs(t <sub>1_x</sub> -t <sub>2_x</sub> ) | -                              | -    | μs                  | t <sub>3</sub> can be set as applicable. Increase of t <sub>3</sub> will reduce the response time t <sub>4</sub> .                                                                                           |

| Time between 2 bits   | <b>t</b> 5              | 1                                          | T-t <sub>4</sub>               | 5400 | μs                  |                                                                                                                                                                                                              |

| Max high time         | <b>t</b> high           | 1                                          | -                              | 5400 | μs                  | Only valid for a single bit high time. There is no restriction in timing between two commands                                                                                                                |

| Min low time          | tlow                    | 1                                          | -                              | 5400 | μs                  |                                                                                                                                                                                                              |

- There is no timing restriction between two commands as long as the A<sub>OUT</sub> pin is not driven to GND.

- The typical threshold level to detect a logic "0" during a high to low transition is 1.3V.

- The typical threshold level to detect a logic "1" during a low to high transition is 1.6V.

#### **Definition of Voltage Levels** 2.5

Table 2 SICI High and low level definition

| Parameter                                   | Symbol     | Min. | Тур. | Мах. | Unit | comment    |

|---------------------------------------------|------------|------|------|------|------|------------|

| Voltage level for SICI – High <sup>1)</sup> | VslCl_High | 1.6  | 3.3  | 3.5  | V    | high state |

| Voltage level for SICI – Low <sup>2)</sup>  | Vsici_Low  | -0.3 | 0    | 1.3  | V    | low state  |

# 3 Interface description

### 3.1 Command Structure

A typical SICI communication consists in multiple input commands sent to the device via  $A_{OUT}$  voltage modulation, to which the sensor responds modulating the same  $A_{OUT}$  pin.

An input command is composed of 16 bits LSB first. One bit consists of a transmission sequence initiated by the master and a receiving sequence driven by the device. The reply data stream sent by the device starts with the LSB.

A typical communication consists of a command including the access information and address sent by the master to the device. The device replies with data from the former received command. The upper nibble of the command include the access information.

#### **Table 3 SICI Command structure**

| 15  | 14 | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3 | 2 | 1 | LSB |

|-----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|---|---|-----|

| w/r | 0  | Ac1 | Ac0 | Ad7 | Ad6 | Ad5 | Ad4 | Ad3 | Ad2 | Ad1 | Ad0 | 0 | 0 | 0 | 0   |

**Table 4 Access bit description**

| w/r | Ac1 | Ac0 | description                                       |

|-----|-----|-----|---------------------------------------------------|

| 1   | 0   | Χ   | Set ones and zeros like the sent 16 bit data word |

| 1   | 1   | 0   | Set only the sent zeros. The ones will not be set |

| 1   | 1   | 1   | Set only the sent ones. The zeros will not be set |

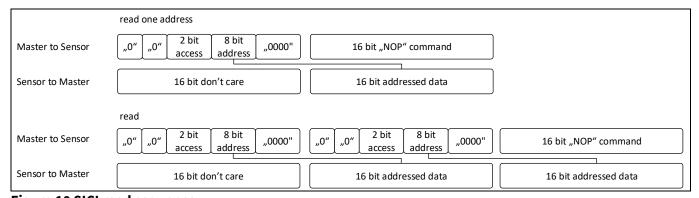

## 3.2 Read / Write Command

There is always a delay of one command between the request command and the addressed data. When a new read command is sent to the sensor, the device replies with the data requested with the former command. The NOP command terminates a read sequence without initializing a new read or write sequence.

Figure 10 SICI read sequence

Figure 11 SICI write sequence

# **Programming Guide and User Manual**

#### **Interface Commands** 3.3

## **Table 5 Available Commands**

| address <sub>hex</sub>                 | command <sub>hex</sub>                                                        | description                                                                                                                                                                                                   |

|----------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | ABCD <sub>hex</sub>                                                           | Activate communication as described in chapter Entering Communication Mode                                                                                                                                    |

| 25 <sub>hex</sub>                      | 8000 <sub>hex</sub>                                                           | reserve if-access to the EEPROM data bus to avoid that ISM is blocking the data bus                                                                                                                           |

| 01 <sub>hex</sub>                      | 0000 <sub>hex</sub>                                                           | Prevent unintended activation of the OCD2 output                                                                                                                                                              |

| 40 <sub>hex</sub> to 42 <sub>hex</sub> | 8400 <sub>hex</sub>                                                           | Initialize Write command to address 40 <sub>hex</sub>                                                                                                                                                         |

|                                        | XYXY                                                                          | send data XYXY to previous addressed line<br>where XYXY stand for 16bit data<br>placeholder                                                                                                                   |

| 40 <sub>hex</sub> to 51 <sub>hex</sub> | 0400 <sub>hex</sub>                                                           | Initialize read command at address 40 <sub>hex</sub>                                                                                                                                                          |

| 41 <sub>hex</sub>                      | 0410 <sub>hex</sub>                                                           | Initialize read command at address 41 <sub>hex</sub> read data from previous address 40 <sub>hex</sub>                                                                                                        |

| 51 <sub>hex</sub>                      | 0510 <sub>hex</sub>                                                           | Initialize read command at address 51 <sub>hex</sub> read data from previous address                                                                                                                          |

|                                        | FFFF <sub>hex</sub>                                                           | No operation command, to read former addressed values.                                                                                                                                                        |

| 3E <sub>hex</sub>                      | 0044 <sub>hex</sub>                                                           | Compare cell voltages of programmed ones                                                                                                                                                                      |

| 3E <sub>hex</sub>                      | 0045 <sub>hex</sub>                                                           | Compare cell voltages of programmed zeros                                                                                                                                                                     |

| 3E <sub>hex</sub>                      | 0248 <sub>hex</sub>                                                           | Set EEPROM bits to zero                                                                                                                                                                                       |

| 3E <sub>hex</sub>                      | 024B <sub>hex</sub>                                                           | Set EEPROM bits to one                                                                                                                                                                                        |

| 3E <sub>hex</sub>                      | 024C <sub>hex</sub>                                                           | Refresh the all EEPROM lines                                                                                                                                                                                  |

| 3E <sub>hex</sub>                      | 024E <sub>hex</sub>                                                           | Program all set zeros into EEPROM                                                                                                                                                                             |

| 3E <sub>hex</sub>                      | 024F <sub>hex</sub>                                                           | Program all set ones into EEPROM                                                                                                                                                                              |

|                                        | 25hex  01hex  40hex to 42hex  41hex  51hex  3Ehex  3Ehex  3Ehex  3Ehex  3Ehex | ABCDhex  25hex 8000hex  01hex 0000hex  40hex to 42hex 8400hex  XYXY  40hex to 51hex 0400hex  41hex 0410hex  51hex 0510hex  FFFFhex  3Ehex 0044hex  3Ehex 0248hex  3Ehex 0248hex  3Ehex 024Chex  3Ehex 024Ehex |

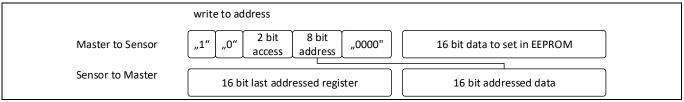

#### 3.4 Write and programming sequence

**Figure 12 Programming Sequence**

Figure 12 shows the command sequence for a write command and describes the sequence to program the EEPROM. After writing the values into the EEPROM, the programming voltage has to be applied for 30ms followed by a refresh command as shown.

#### **Temporary register** 3.5

For test purpose, it is possible to change the sensor settings in the temporary registers. This allows to test user settings without programming the EEPROM.

The addresses for the temporary registers are different from the EEPROM addresses. See Table 6 for details.

In order to access temporary registers send 0x8000 to address 25<sub>hex</sub>. Set to 0x0000 to leave the interface mode and to change into normal operating mode until the next power down. The sensor uses the content of the temporary registers instead of the correlating EEPROM values until the next power down.

**Table 6 Temporary register description**

| Temporary register address | EEPROM register address | Note                                                                                                                           |  |  |  |  |  |

|----------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 25 <sub>hex</sub>          | -                       | Write 0x8000 to this address to get access to the register (otherwise the registers gets occupied / overwritten by the sensor) |  |  |  |  |  |

| 01 <sub>hex</sub>          | -                       | Write 0x0000 to temporary disables failure indications like CRC check.                                                         |  |  |  |  |  |

| 11 <sub>hex</sub>          | 40 <sub>hex</sub>       | Bit description and bit position same for both addresses                                                                       |  |  |  |  |  |

| 12 <sub>hex</sub>          | 41 <sub>hex</sub>       | Bit description and bit position same for both addresses                                                                       |  |  |  |  |  |

| 13 <sub>hex</sub>          | 42 <sub>hex</sub>       | Bit description and bit position same for both addresses                                                                       |  |  |  |  |  |

## 3.6 Read Example (temperature register read out)

The temperature value can be read out via the SICI interface. The following example describes the required command sequence to enter the interface and to read out the 16 bit temperature value. The temperature sensitivity is set to a sensitivity of 16 LSB $_{16}$ /°C. The ADC value for 25°C corresponds to 1408 LSB $_{16}$ . The following formula describes how to calculate the temperature dependent on the 16bit value.

$$Temperature = \frac{ADC_{value} - 2048}{16} + 65$$

Table 7 Command sequence example to read out the internal 16 bit temperature value

| rabte i commana sequence examp             | te to read out the internat 20 bit ter | iiperatare vatae                                        |

|--------------------------------------------|----------------------------------------|---------------------------------------------------------|

| Command / sequence                         | minimum frame time                     | Description                                             |

| ABCD <sub>hex</sub>                        | 0.64ms                                 | Enter interface command (sending 16bit reading 16bit)   |

| Write command to address 25 <sub>hex</sub> | 0.64ms                                 | Power down ISM<br>(write to address 25 <sub>hex</sub> ) |

| 8000 <sub>hex</sub>                        | 0.64ms                                 | Power down ISM<br>(write data)                          |

| Read command at address 18 <sub>hex</sub>  | 0.64ms                                 | Sending the address to read the temperature value       |

| FFFF <sub>hex</sub>                        | 0.64ms                                 | Reading the data.                                       |

Power on and off the device to activate normal operating mode. (1.5ms typical after power on) Alternatively set the device in normal operating mode by sending the following commands:

| Write command to address 25 <sub>hex</sub> | 0.64ms | Power on ISM<br>(write command to address) |

|--------------------------------------------|--------|--------------------------------------------|

| 0000 <sub>hex</sub>                        | 0.64ms | Power on ISM<br>(send data)                |

Wait until the  $A_{OUT}$  settles into calibrated mode. In calibrated mode, the  $A_{OUT}$  reflects the voltage level of the  $V_{REF}$  pin. Assumed no current flows through the primary current rail of the device.

#### 4 **EEPROM**

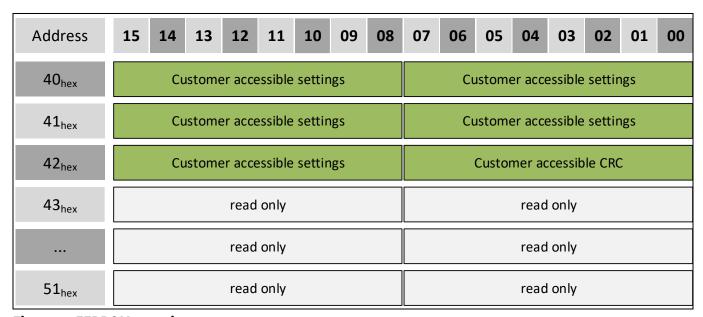

The sensor's non volatile memory (EEPROM) is organized in 16-bit (word) registers which can be addressed individually.

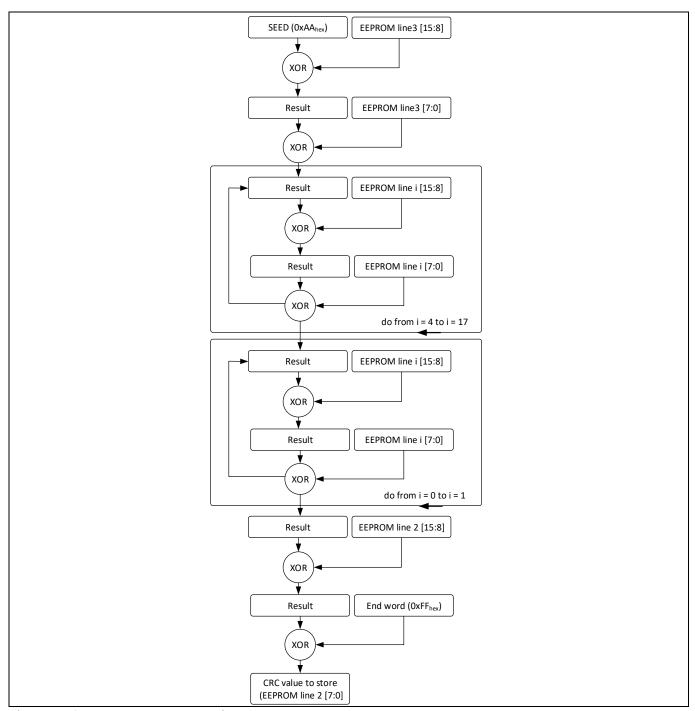

When content in the user area is re programmed, a CRC check register has to be updated. Since the EEPROM CRC is calculated covering the entire EEPROM storage space, the user is required to readout the entire EEPROM content, calculate the new CRC values and store it into the respective registers. An incorrect CRC value will be detected by the sensor and cause a transition to its safe state. In case of a CRC error the OCD open drain output will be set to GND.

All 18 lines of the EEPROM are readable because the CRC calculation has to be done with the complete data content of the EEPROM. The device is doing a cyclic redundancy check (CRC) of the EEPROM content while accessing the EEPROM and indicates an error on the OCD pin in case of a wrong programmed CRC.

Figure 13 EEPROM overview

# **Programming Guide and User Manual**

#### **EEPROM Content** 4.1

## Table 8 EEPROM (address 40<sub>hex</sub> - 42<sub>hex</sub>)

| address                  | 15                   | 14                 | 13                    | 12                     | 11    | 10 | 9                                           | 8 | 7   | 6                                              | 5 | 4                   | 3 | 2 | 1 | 0                   |  |  |

|--------------------------|----------------------|--------------------|-----------------------|------------------------|-------|----|---------------------------------------------|---|-----|------------------------------------------------|---|---------------------|---|---|---|---------------------|--|--|

| 40 <sub>hex</sub>        | OCD2 <sub>en</sub>   | OCD1 <sub>en</sub> |                       | OCD2 <sub>deglit</sub> | ch    |    | OCD1 <sub>deglitch</sub> OP <sub>mode</sub> |   |     |                                                |   | MEAS <sub>rng</sub> |   |   |   | MEAS <sub>rng</sub> |  |  |

| <b>41</b> <sub>hex</sub> |                      |                    | OCD2 <sub>thr</sub>   | sh                     |       |    |                                             |   | OCD | OCD1 <sub>thrsh</sub> OCD <sub>comp_hyst</sub> |   |                     |   |   |   |                     |  |  |

| 42 <sub>hex</sub>        | RATIO <sub>Off</sub> | $RATIO_{Gain}$     | OCD2f <sub>only</sub> | QV1V5 <sub>sd</sub>    | Empty | ٧  | REF <sub>ext</sub>                          |   | CRC |                                                |   |                     |   |   |   |                     |  |  |

Table 9 Functional description Address 40<sub>hex</sub>

| Bit field<br>name        | Bit   | Туре |            |                   | Bit field description                     | Default<br>value                 |                                             |      |        |                  |                                   |

|--------------------------|-------|------|------------|-------------------|-------------------------------------------|----------------------------------|---------------------------------------------|------|--------|------------------|-----------------------------------|

|                          |       |      | The measu  | rement rar        | nge bits define the sensitivity in mV/A   |                                  |                                             |      |        |                  |                                   |

|                          |       |      | Symbol     | Setting           | Description / Full Scale setting          |                                  |                                             |      |        |                  |                                   |

|                          |       |      | S1         | 05 <sub>hex</sub> | ±120A Full Scale (FS) / 10mV/A            |                                  |                                             |      |        |                  |                                   |

|                          | 4:0   |      | S2         | 06 <sub>hex</sub> | ±100A / 12 mV/A                           |                                  |                                             |      |        |                  |                                   |

| $MEAS_{rng}$             |       | rw   | S3         | 08 <sub>hex</sub> | ±75A / 16 mV/A                            | xxx0x                            |                                             |      |        |                  |                                   |

|                          |       |      |            | S4                | 0C <sub>hex</sub>                         | ±50A / 24 mV/A                   |                                             |      |        |                  |                                   |

|                          |       |      | <b>S</b> 5 | 10 <sub>hex</sub> | ±37.5A / 32 mV/A                          |                                  |                                             |      |        |                  |                                   |

|                          |       |      | S6         | 18 <sub>hex</sub> | ±25A / 48 mV/A                            |                                  |                                             |      |        |                  |                                   |

|                          |       |      | Symbol     | Setting           | Description                               |                                  |                                             |      |        |                  |                                   |

|                          |       |      |            |                   | Semi-differential bidirectional VoQbid_1: |                                  |                                             |      |        |                  |                                   |

|                          |       |      | SD bid     | 0 <sub>hex</sub>  | $V_{REF} = V_{DD} / 2$                    |                                  |                                             |      |        |                  |                                   |

|                          |       |      |            |                   | $V_{OQbid_2}: V_{REF} = 1.5 (QV1V5 = 1)$  |                                  |                                             |      |        |                  |                                   |

|                          |       |      |            | 1                 | Fully-differential                        |                                  |                                             |      |        |                  |                                   |

| $OP_{mode}$              | 6:5   | rw   | rw         | rw                | FD                                        | $1_{hex}$                        | $(V_{OQ} = V_{DD}/2)$ (doubled sensitivity) | 00   |        |                  |                                   |

|                          |       |      | İ          | CD                | 2                                         | Semi-differential unidirectional |                                             |      |        |                  |                                   |

|                          |       |      |            |                   |                                           |                                  |                                             |      | SD uni | $2_{\text{hex}}$ | $V_{OQuni}: V_{REF} = V_{DD}/5.5$ |

|                          |       |      |            | ſ                 | Single-ended                              |                                  |                                             |      |        |                  |                                   |

|                          |       |      | SE         | $3_{hex}$         | $V_{OQ} = V_{REF} = V_{REF\_ext}$         |                                  |                                             |      |        |                  |                                   |

|                          |       |      | The device | standard s        | setting is the semi-differential mode     |                                  |                                             |      |        |                  |                                   |

|                          |       |      | Symbol     | Setting           | Deglitch time in ns                       |                                  |                                             |      |        |                  |                                   |

|                          | 9:7   |      |            | d0                | 0 <sub>hex</sub>                          | 0 (standard setting)             |                                             |      |        |                  |                                   |

|                          |       |      | rw         | d1                | $1_{hex}$                                 | 500                              |                                             |      |        |                  |                                   |

|                          |       |      |            | rw                | d2                                        | 2 <sub>hex</sub>                 | 1000                                        |      |        |                  |                                   |

| $OCD1_{deglitch}$        |       | rw   |            |                   | rw                                        | d3                               | 3 <sub>hex</sub>                            | 1500 | 000    |                  |                                   |

|                          |       |      | d4         | 4 <sub>hex</sub>  | 2000                                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d5         | 5 <sub>hex</sub>  | 2500                                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d6         | 6 <sub>hex</sub>  | 3000                                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d7         | 7 <sub>hex</sub>  | 3500                                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | Symbol     | Setting           | Deglitch time in ns                       |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d0         | 0                 | 0 (standard setting)                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d1         | 1                 | 500                                       |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d2         | 2                 | 1000                                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d3         | 3                 | 1500                                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d4         | 4                 | 2000                                      |                                  |                                             |      |        |                  |                                   |

| 0000                     | 12.10 |      | d5         | 5                 | 2500                                      | 0000                             |                                             |      |        |                  |                                   |

| OCD2 <sub>deglitch</sub> | 13:10 | rw   | d6         | 6                 | 3000                                      | 0000                             |                                             |      |        |                  |                                   |

|                          |       |      | d7         | 7                 | 3500                                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d8         | 8                 | 4000                                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d9         | 9                 | 4500                                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d10        | 10                | 5000                                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d11        | 11                | 5500                                      |                                  |                                             |      |        |                  |                                   |

|                          |       |      | d12        | 12                | 6000                                      |                                  |                                             |      |        |                  |                                   |

# **Programming Guide and User Manual**

|                    |    |    | d13         | 13                        | 6500                                                                                                                                                            |   |

|--------------------|----|----|-------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                    |    |    | d14         | 14                        | 7000                                                                                                                                                            |   |

|                    |    |    | d15         | 15                        | 7500                                                                                                                                                            |   |

| OCD1 <sub>en</sub> | 14 | rw | functionali | ty of chan<br>internal fa | etection enable bit 1 activates the over-current and 1. If this bit set to zero the OCD pin 1 will not ailure or an over-current event. The standard setting is | 1 |

| OCD2 <sub>en</sub> | 15 | rw | functionali | ty of chan<br>internal fa | etection enable bit 2 activates the over-current and 2. If this bit set to zero the OCD pin 2 will not ailure or an over-current event. The standard setting is | 1 |

| Bit field<br>name        | Bit   | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      | Ві                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | t field o                                                                                                                                                                                           | lescript                                                                                                                                                                         | ion                                                                                                                                 |                                                                                                                                                       |                                                                                                                   | Default<br>value |

|--------------------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------|

| OCD <sub>comp_hyst</sub> | 3:0   | rw   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | for 25A x for 25A x for 50A threshol a = 120 A aresh = OC            | - and 75A - and 120 ds for 12 * 1.25 = 1 D1 <sub>thresh</sub> * A * (1 - ( ds for 75 A * (1 - ( ds for 75 A * (1 - ( ds for 50 A * (1 - ( ds for 25 A * (1 - ( | A-full-sca<br>0A-full-sca<br>0A-full-sca<br>0A-full-sca<br>150 A<br>(1 - ( OC<br>(6hex / 13<br>08 A<br>(1 - ( OC<br>6hex / 18<br>A-full-sca<br>1 A<br>1 A<br>1 A<br>1 A<br>1 A<br>1 A<br>1 A<br>1 A | ale-variar cale-variar cale-varia | nt ant: ant: ant: asetting / OG A asetting / OG A nt: A A nt: A A A A A A A A A A A A A A A A A A A                                 | $CD1_{thrsh\_se}$                                                                                                                                     |                                                                                                                   | 0x1x             |

| $OCD1_{thrsh}$           | 9:4   | rw   | Threshold lo Symbol level   ITHR1.1   ITHR1.2   ITHR1.3   ITHR1.5   ITHR1.6   ITHR1.8   THR1.8   THR1. | x FS<br>1.25<br>1.39<br>1.54<br>1.68<br>1.82<br>1.96<br>2.11<br>2.25 | S1 13hex*) 16hex 19hex 1Chex 1Ehex 21hex 24hex 27hex                                                                                                                                                                                                                                                                                                                                                                                                                                                           | S2  0F <sub>hex</sub> 11 <sub>hex</sub> 14 <sub>hex</sub> 16 <sub>hex</sub> 18 <sub>hex</sub> 1B <sub>hex</sub> 1D <sub>hex</sub> 1F <sub>hex</sub> e 2118 a                                        | Setting S3 OAhex*) OBhex ODhex OFhex 11hex 12hex 14hex 16hex nd later                                                                                                            | S4 14 <sub>hex</sub> *) 17 <sub>hex</sub> 1A <sub>hex</sub> 1D <sub>hex</sub> 20 <sub>hex</sub> 23 <sub>hex</sub> 26 <sub>hex</sub> | S5<br>0D <sub>hex</sub><br>0F <sub>hex</sub><br>12 <sub>hex</sub><br>14 <sub>hex</sub><br>16 <sub>hex</sub><br>18 <sub>hex</sub><br>1B <sub>hex</sub> | S6 07 <sub>hex</sub> *) 09 <sub>hex</sub> 0A <sub>hex</sub> 0C <sub>hex</sub> 0D <sub>hex</sub> 10 <sub>hex</sub> | xxxxx            |

| OCD2 <sub>thrsh</sub>    | 15:10 | rw   | Threshold le                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | u                                                                                                                                                                                                   |                                                                                                                                                                                  |                                                                                                                                     |                                                                                                                                                       |                                                                                                                   | XXXXXX           |

### **Programming Guide and User Manual**

| Symbol              |           |                             |                   | Setting              |                             |                   |                      |

|---------------------|-----------|-----------------------------|-------------------|----------------------|-----------------------------|-------------------|----------------------|

| level               | x FS      | S1                          | S2                | <b>S</b> 3           | S4                          | <b>S</b> 5        | S6                   |

| I <sub>THR2.1</sub> | 0.50      | 0E <sub>hex</sub>           | 0B <sub>hex</sub> | 07 <sub>hex</sub>    | 0E <sub>hex</sub>           | 09 <sub>hex</sub> | 04 <sub>hex</sub>    |

| I <sub>THR2.2</sub> | 0.61      | 13 <sub>hex</sub>           | 0F <sub>hex</sub> | 0A <sub>hex</sub>    | 13 <sub>hex</sub>           | 0D <sub>hex</sub> | 06 <sub>hex</sub>    |

| I <sub>THR2.3</sub> | 0.71      | 17 <sub>hex</sub>           | 12 <sub>hex</sub> | $0C_{hex}$           | 17 <sub>hex</sub>           | $10_{\text{hex}}$ | 08 <sub>hex</sub>    |

| I <sub>THR2.4</sub> | 0.82      | <b>1B</b> <sub>hex</sub> *) | 16 <sub>hex</sub> | OF <sub>hex</sub> *) | <b>1C</b> <sub>hex</sub> *) | 13 <sub>hex</sub> | OB <sub>hex</sub> *) |

| I <sub>THR2.5</sub> | 0.93      | 1F <sub>hex</sub>           | 1A <sub>hex</sub> | 12 <sub>hex</sub>    | 21 <sub>hex</sub>           | 17 <sub>hex</sub> | $0D_{hex}$           |

| I <sub>THR2.6</sub> | 1.04      | 24 <sub>hex</sub>           | 1D <sub>hex</sub> | 15 <sub>hex</sub>    | 25 <sub>hex</sub>           | 1A <sub>hex</sub> | $0F_{hex}$           |

| I <sub>THR2.7</sub> | 1.14      | 28 <sub>hex</sub>           | 21 <sub>hex</sub> | 17 <sub>hex</sub>    | 2A <sub>hex</sub>           | 1D <sub>hex</sub> | $11_{hex}$           |

| I <sub>THR2.8</sub> | 1.25      | $2D_{hex}$                  | 24 <sub>hex</sub> | 1A <sub>hex</sub>    | 2E <sub>hex</sub>           | 21 <sub>hex</sub> | 14 <sub>hex</sub>    |

| *) Standar          | d setting | datecod                     | le 2118 a         | nd later             |                             |                   |                      |

Table 11 Functional description Address 42<sub>hov</sub>

| Bit field<br>name     | Bit  | Туре |                         |                  | Bit field description                                                                                                                                                                  | Default<br>value |

|-----------------------|------|------|-------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| CRC                   | 7:0  | rw   | end of the              | EEPROM (a        | te by byte, starting from address $42_{hex}$ . After reaching the address $51_{hex}$ ), the address $40_{hex}$ to $41_{hex}$ are append. The sed on the polynomial $x^8+x^4+x^3+x^2+1$ | -                |

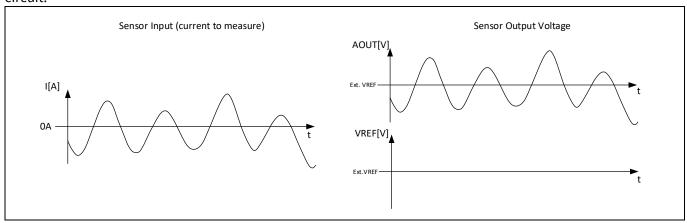

|                       |      |      | Symbol                  | Setting          | Description V <sub>REF_nom</sub> = 1.65 V (±10% if ratiometricity is enabled)                                                                                                          |                  |

|                       |      |      | 1V65                    | O <sub>hex</sub> | standard setting                                                                                                                                                                       |                  |

| $VREF_{ext}$          | 10:8 | rw   | _1V2                    | 1 <sub>hex</sub> | $V_{REF\_nom} = 1.2 \text{ V } (\pm 10\% \text{ if ratiometricity is enabled})$                                                                                                        | 000              |

|                       |      |      | 1V5                     | 2 <sub>hex</sub> | $V_{REF\_nom} = 1.5 \text{ V } (\pm 10\% \text{ if ratiometricity is enabled})$                                                                                                        |                  |

|                       |      |      | 1V8                     | 3 hex            | V <sub>REF_nom</sub> = 1.8 V (±10% if ratiometricity is enabled)                                                                                                                       |                  |

|                       |      |      | Standard is             | s set to 1.6     | 5V                                                                                                                                                                                     |                  |

| Not used              | 11   | rw   | Not used                |                  |                                                                                                                                                                                        | 0                |

| QV1V5 <sub>sd</sub>   | 12   | rw   | The bit<br>Default is 0 |                  | he quiescent voltage to 1.5V in semi-differential.                                                                                                                                     | 0                |

|                       |      |      | If the bit is           | set to one       | only failure indication is activated at the OCD2 channel.                                                                                                                              |                  |

| OCD2f <sub>only</sub> | 13   | rw   | Over curre              | nt detectio      | n is not activated if the bit is set to one.                                                                                                                                           | 0                |

|                       |      |      | Default is 0            | ) (= fault sig   | gnal on both OCDs)                                                                                                                                                                     |                  |

| DATIO                 | 1.4  |      | If the bit is           | set, the ser     | nsitivity is ratio metric to VDD respective to VREF in single-                                                                                                                         | 0                |

| $RATIO_{Gain}$        | 14   | rw   | ended mod               | de. Default      | is 0 (=disabled)                                                                                                                                                                       | 0                |

| RATIO <sub>off</sub>  | 15   | rw   |                         |                  | t behavior of the quiescent voltage is activated if the bit is                                                                                                                         | 0                |

| IVATIO0#              | 13   | I VV | set to one.             | Default is (     | O (=disabled)                                                                                                                                                                          |                  |

#### 4.2 **Programming Example**

Table 12 will guide the user through a complete programming sequence.

After activating the interface the integrated intelligent state machine (ISM) has to be powered down. To avoid unintended high current consumption during applying the programming voltage at the OCD2 pin, the error indication has to be disabled by writing the disable failure indication command to the device.

Programming requires two single commands followed by the programming pulse. One sequence is required to program the ones and one sequence to program the zeros into the EEPROM. All digital values are stored in the EEPROM. Figure 12 gives timing and an exemplary description of the programming sequence.

# **Programming Guide and User Manual**

Table 12 EEPROM programming example

| Command name               | address <sub>hex</sub> | command <sub>hex</sub>      | description                                        |  |  |

|----------------------------|------------------------|-----------------------------|----------------------------------------------------|--|--|

| Enter Interface            |                        | DCBA <sub>hex</sub>         | Enter interface                                    |  |  |

| Davis davis ICM            |                        | 8250 <sub>hex</sub>         | Write command: get access to the register          |  |  |

| Power down ISM             | 25 <sub>hex</sub>      | 8000 <sub>hex</sub>         | Set data                                           |  |  |

| Disable failure indication |                        | 8010 <sub>hex</sub>         | Write command                                      |  |  |

| Disable failure indication | 01 <sub>hex</sub>      | 0000 <sub>hex</sub>         | Set data                                           |  |  |

| Read all register          |                        |                             | Read data before modifying values                  |  |  |

| Read command (All EEPROM   | 40 <sub>hex</sub>      | 0400 <sub>hex</sub>         | Read command at EEPROM line 0                      |  |  |

| register)                  | n                      | 00n0                        | Read command for address "n"                       |  |  |

|                            | 51 <sub>hex</sub>      | 0510 <sub>hex</sub>         | Address last line in EEPROM                        |  |  |

| NOP                        |                        | FFFF <sub>hex</sub>         | Read values from previous address                  |  |  |

| Write command              |                        | 8400 <sub>hex</sub>         | Write to EEPROM line 0: Access: set ones and zeros |  |  |

| Write data                 | 40 <sub>hex</sub>      | nnnn <sub>hex</sub>         | Write content to be programmed                     |  |  |

| EEPROM program zeros       | 25                     | 83E0 <sub>hex</sub>         | Write to EEPROM command line                       |  |  |

|                            | 3E <sub>hex</sub>      | 024 <b>E</b> <sub>hex</sub> | Set EEPROM command program zeros                   |  |  |

|                            |                        |                             | Apply programming voltage                          |  |  |

| EEPROM refresh             | 25                     | 83E0 <sub>hex</sub>         | Write to EEPROM command line                       |  |  |

|                            | 3E <sub>hex</sub>      | 024 <b>C</b> <sub>hex</sub> | Set EEPROM command refresh                         |  |  |

|                            |                        |                             | Wait 100 μs                                        |  |  |

| Write command              |                        | 8400 <sub>hex</sub>         | Write to EEPROM line 0: Access: set ones and zeros |  |  |

| Write data                 | 40 <sub>hex</sub>      | nnnn <sub>hex</sub>         | Write content to be programmed                     |  |  |

| EEPROM program ones        | 25                     | 83E0 <sub>hex</sub>         | Write to EEPROM command line                       |  |  |

|                            | 3E <sub>hex</sub>      | 024 <b>F</b> <sub>hex</sub> | Set EEPROM command program ones                    |  |  |

|                            |                        |                             | Apply programming voltage                          |  |  |

| EEDDOM volume              | 3E <sub>hex</sub>      | 83E0 <sub>hex</sub>         | Write to EEPROM command line                       |  |  |

| EEPROM refresh             |                        | 024C <sub>hex</sub>         | Set EEPROM command refresh                         |  |  |

|                            |                        |                             | Wait 100 μs                                        |  |  |

### **Programming Guide and User Manual**

Table 13 EEPROM voltage and timing parameter

| Parameter                                                        | Symbol               | Min  | Тур  | Max  | Unit | Note                                                                                                                                                                                                                          |

|------------------------------------------------------------------|----------------------|------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programming Voltage                                              | V <sub>PROG</sub>    | 20.5 | 20.6 | 21.0 | V    | EEPROM designed to write under specified condition on the first shot. In case of lower voltage (i.e. 15V) Infineon recommends a margin test to proof quality of EEPROM content and repeat the programming-sequence if needed. |

| EEPROM threshold margin level at start of lifetime <sup>1)</sup> | $V_{TH\_0h}$         | 3.55 | 3.8  | 4.15 | V    | "1" programmed cells                                                                                                                                                                                                          |

|                                                                  |                      |      |      | 0.25 | V    | "0" programmed cells                                                                                                                                                                                                          |

| EEPROM threshold margin level after lifetime                     | $V_{TH\_LT}$         | 1.9  |      |      | V    | "1" programmed cells                                                                                                                                                                                                          |

|                                                                  |                      |      |      | 1.1  | V    | "0" programmed cells                                                                                                                                                                                                          |

| Margin voltage sweep range, test of "1" bits                     | $V_{ m margin}$      | 1.3  |      | 4.3  | V    | 25mV step size recommended                                                                                                                                                                                                    |

| Margin voltage sweep range, test of "0" bits                     |                      | 0    |      | 1.7  | V    |                                                                                                                                                                                                                               |

| EEPROM Programming time                                          | $t_{\sf EEPvprog}$   |      | 30   |      | ms   | Time to apply programming voltage V <sub>PROG</sub> on OCD2 pin                                                                                                                                                               |

| EEPROM wait time                                                 | t <sub>EEPwait</sub> |      | 100  |      | μs   | Wait time after EEPROM refresh command                                                                                                                                                                                        |

| Programming Current consumption                                  | $I_{PROG}$           |      | 6    | 10   | mA   | Current consumption of OCD2 while applying the programming voltage                                                                                                                                                            |

Limits for EEPROM programming and margin level test at the same temperature. Alternatively the temperature characteristic of the margin level test needs to be considered: VTH(T)=VTH(WRITE\_ERASE)+0.0016V/K\*(TPROG-T). Please note that only a typical temperature coefficient is used.

#### 4.3 **Margin Test**

The margin test command is used in order to check the threshold voltages of the programmed EEPROM cells. For reliable sensor EEPROM operation the threshold level of the cells have to be kept within the specification (Table 13). After sending the margin test command an external margin voltage can be switched to the control gates while refreshing the EEPROM-registers by an external trigger, so that the switching threshold of the EEPROM cells can be identified (Table 13). EEPROM cells programmed to '0' or to '1' need to be tested separately. For the '1' programmed cells a threshold voltage smaller than the applied margin voltage a '0' will be stored to the EEPROM registers, for those with a higher threshold a '1'. Vice versa the procedure when testing '0' programmed cells, for a margin voltage smaller than the threshold a '1' and for those higher than the

## **Programming Guide and User Manual**

threshold a '0' is stored in the EEPROM registers. By sweeping the external margin voltage the effective threshold voltages of each EEPROM cell can be identified. The threshold voltages of cells programmed to '1' can be found in this way. The smallest possible margin voltage is 0V, it is therefore not possible to determine the threshold voltages below 0V for the cells programmed to '0'.

Table 14 EEPROM margin test

| Command name                 | address <sub>hex</sub> | command <sub>hex</sub>      | description                                                            |