#### **High-speed CAN FD transceiver**

#### **Features**

- Fully compliant to ISO 11898-2:2024 and SAE J2284-4/-5

- Loop delay symmetry for controller area network (CAN) FD data frames up to 5 Mbit/s

- Very low electromagnetic emission (EME) allows the use without additional common mode choke

- Bus wake-up pattern (WUP) function with optimized filter time for worldwide original equipment manufacturer (OEM) usage

- · Standby mode with minimized guiescent current

- Excellent electrostatic discharge (ESD) robustness

- · TxD timeout function

- · Very low CAN bus leakage current in power-down state

- Overtemperature protection

- Protected against automotive transients according to ISO 7637 and SAE J2962-2

- · Green Product (RoHS compliant)

#### **Potential applications**

- · Engine control units

- · Gateway modules

- · Body control modules (BCM)

#### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

#### **Description**

The TLE9351BSJ is a high speed *CAN* transceiver, used in HS CAN systems for automotive applications as well as for industrial applications. It is designed to fulfill the requirements of ISO 11898-2:2024 physical layer specification as well as SAE J1939 and SAE J2284.

The TLE9351BSJ is available in a *Restriction of Hazardous Substances in Electrical and Electronic Equipment (RoHS)* compliant, halogen free PG-DSO-8 package.

As an interface between the physical bus layer and the HS CAN protocol controller, the TLE9351BSJ is designed to protect the microcontroller against interferences generated inside the network. A very high *ESD* robustness and the optimized RF immunity allows the use in automotive applications without additional protection devices, such as suppressor diodes or common mode chokes.

Based on the high symmetry of the CANH and CANL output signals, the TLE9351BSJ provides a very low level of *EME* within a wide frequency range. The TLE9351BSJ fulfills even stringent *electromagnetic compatibility (EMC)* test limits without an additional external circuit, such as a common mode choke.

The optimized transmitter symmetry combined with the optimized delay symmetry of the receiver enables the TLE9351BSJ to support CAN FD data frames. The device supports data transmission rates up to 5 Mbit/s, depending on the size of the network and the inherent parasitic effects.

Dedicated low-power modes, such as standby mode, provide very low quiescent current during power-up of the device. In standby mode the typical quiescent current on  $V_{CC}$  is less than 10  $\mu$ A while the device can still wake up by a bus signal on the HS CAN bus.

Fail-safe features, such as overtemperature protection, output current limitation or the TxD timeout feature are designed to protect the TLE9351BSJ and the external circuitry from irreparable damage.

| Туре       | Package  | Marking |

|------------|----------|---------|

| TLE9351BSJ | PG-DSO-8 | 9351B   |

### **Datasheet**

# **Table of contents**

|       | Features                                                  | 1  |

|-------|-----------------------------------------------------------|----|

|       | Potential applications                                    | 1  |

|       | Product validation                                        | 1  |

|       | Description                                               | 1  |

|       | Table of contents                                         | 2  |

| 1     | Block diagram                                             | 4  |

| 2     | Pin configuration                                         | 5  |

| 2.1   | Pin assignment                                            |    |

| 2.2   | Pin definitions and functions                             |    |

| 3     | General product characteristics                           | 6  |

| 3.1   | Absolute maximum ratings                                  |    |

| 3.2   | Functional range                                          |    |

| 3.3   | Thermal resistance                                        |    |

| 4     | High speed CAN functional description                     | 8  |

| 4.1   | High speed CAN physical layer                             | 8  |

| 5     | Modes of operation                                        | 10 |

| 5.1   | Normal-operating mode                                     | 10 |

| 5.2   | Standby mode                                              | 10 |

| 5.3   | Power-down state                                          | 11 |

| 5.4   | Wake-up pattern (WUP) detection                           | 11 |

| 6     | Fail safe functions                                       | 13 |

| 6.1   | Short circuit protection                                  | 13 |

| 6.2   | Unconnected logic pins                                    | 13 |

| 6.3   | V <sub>CC</sub> undervoltage                              | 13 |

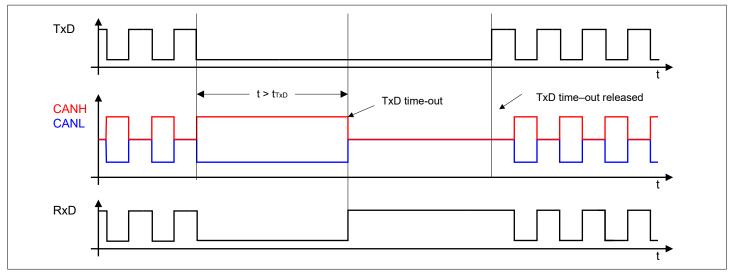

| 6.4   | TxD timeout feature                                       | 13 |

| 6.5   | Delay time for mode change                                |    |

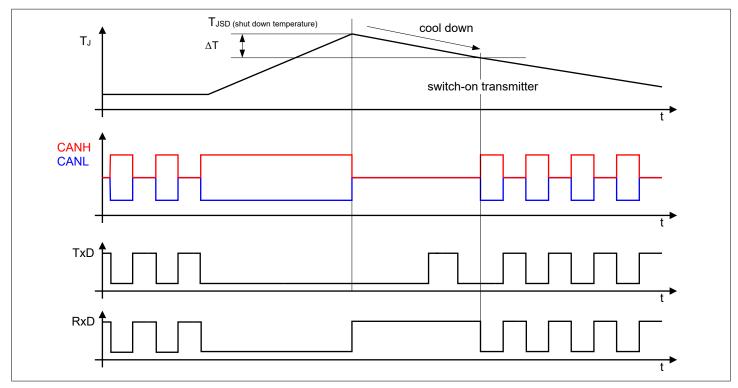

| 6.6   | Overtemperature protection                                | 14 |

| 7     | Electrical characteristics                                |    |

| 7.1   | Power supply interface                                    |    |

| 7.1.1 | Electrical characteristics current consumption            |    |

| 7.1.2 | Electrical characteristics undervoltage detection         | 17 |

| 7.2   | Electrical characteristics CAN controller interface       | 18 |

| 7.3   | Electrical characteristics receiver                       |    |

| 7.4   | Electrical characteristics transmitter                    |    |

| 7.5   | Electrical characteristics dynamic transceiver parameters |    |

| 7.6   | Diagrams                                                  | 24 |

# **Datasheet**

### Table of contents

| 8   | Application information                   | 26 |

|-----|-------------------------------------------|----|

| 8.1 | ESD robustness according to IEC 61000-4-2 |    |

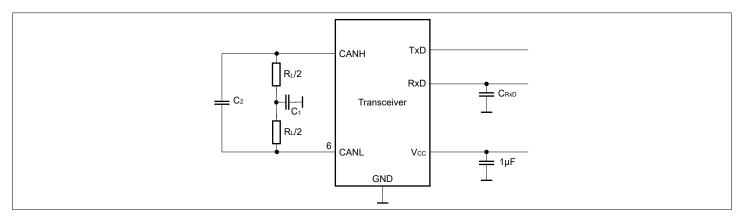

| 8.2 | Application example                       | 27 |

| 8.3 | Further application information           | 27 |

| 9   | Package information                       | 28 |

|     | Glossary                                  | 29 |

|     | Revision history                          | 31 |

|     | Disclaimer                                | 32 |

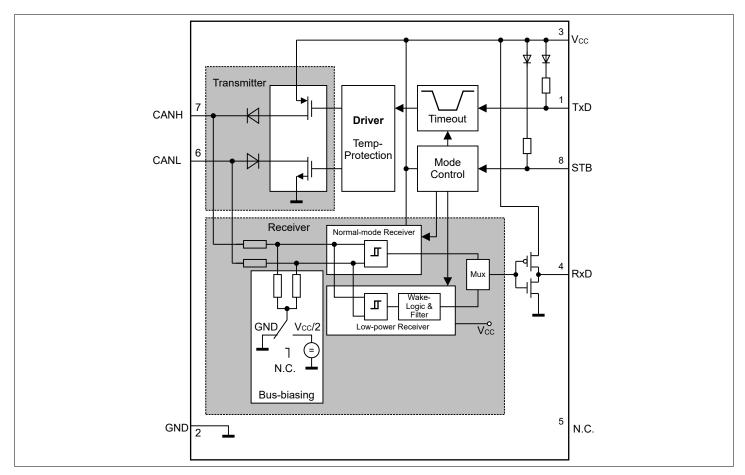

1 Block diagram

# 1 Block diagram

Figure 1 Block diagram

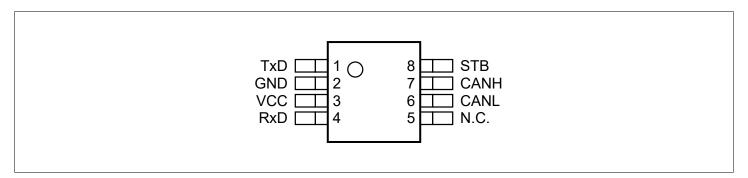

2 Pin configuration

# 2 Pin configuration

# 2.1 Pin assignment

Figure 2 Pin configuration

# 2.2 Pin definitions and functions

### Table 1Pin definitions and functions

| Pin No. | Symbol | Function                                                              |

|---------|--------|-----------------------------------------------------------------------|

| 1       | TxD    | Transmit data input;                                                  |

|         |        | Internal pull-up to $V_{CC}$ , "low" for dominant state.              |

| 2       | GND    | Ground                                                                |

| 3       | VCC    | Transmitter supply voltage;                                           |

|         |        | A decoupling capacitor of 1 μF to <i>ground (GND)</i> is recommended. |

| 4       | RxD    | Receive data output;                                                  |

|         |        | "Low" in dominant state.                                              |

| 5       | N.C.   | Not Connected;                                                        |

|         |        | This pin is without function, not connected internally.               |

| 6       | CANL   | CAN bus low level input/output (I/O);                                 |

|         |        | Bus level on the CANL input/output.                                   |

| 7       | CANH   | CAN bus high level I/O;                                               |

|         |        | Bus level on the CANH input/output.                                   |

| 8       | STB    | Standby input;                                                        |

|         |        | Internal pull-up to $V_{CC}$ , "low" for normal-operating mode.       |

3 General product characteristics

#### **General product characteristics** 3

#### **Absolute maximum ratings** 3.1

#### Absolute maximum ratings voltages, currents and temperatures 1) Table 2

All voltages with respect to ground; positive current flowing into pin; (unless otherwise specified)

| Parameter                                     | Symbol                   |      | Value | s                    | Unit | Note or Test<br>Condition | Number   |

|-----------------------------------------------|--------------------------|------|-------|----------------------|------|---------------------------|----------|

|                                               |                          | Min. | Тур.  | Max.                 |      |                           |          |

| Voltages                                      |                          |      |       |                      |      |                           |          |

| Transmitter supply voltage                    | V <sub>CC</sub>          | -0.3 | _     | 6.0                  | V    | _                         | P_7.1.1  |

| CANH and CANL DC voltage<br>versus <i>GND</i> | V <sub>CANH</sub>        | -40  | _     | 40                   | V    | -                         | P_7.1.3  |

| Differential voltage between CANH and CANL    | V <sub>CAN_Diff</sub>    | -40  | _     | 40                   | V    | -                         | P_7.1.4  |

| Voltage at the digital input pins: STB, TxD   | V <sub>MAX_IO</sub>      | -0.3 | _     | 6.0                  | V    | -                         | P_7.1.5  |

| Voltage at the digital output pin:            | $V_{\mathrm{MAX\_RxD}}$  | -0.3 | -     | V <sub>CC</sub> +0.3 | V    | -                         | P_7.1.9  |

| Currents                                      |                          |      |       |                      | 1    | 1                         | ,        |

| RxD output current                            | I <sub>RxD</sub>         | -5   | _     | 5                    | mA   | _                         | P_7.1.6  |

| Temperatures                                  |                          |      |       |                      |      |                           | ·        |

| Junction temperature                          | $T_{j}$                  | -40  | _     | 150                  | °C   | _                         | P_7.1.7  |

| Storage temperature                           | $T_{S}$                  | -55  | -     | 150                  | °C   | _                         | P_7.1.8  |

| ESD robustness                                |                          |      |       |                      |      |                           |          |

| ESD robustness at CANH, CANL<br>versus GND    | V <sub>ESD_HBM_CAN</sub> | -10  | _     | 10                   | kV   | <sup>2)</sup> HBM;        | P_7.1.10 |

| ESD robustnessat all other pins               | V <sub>ESD_HBM_ALL</sub> | -2   | -     | 2                    | kV   | <sup>2)</sup> HBM;        | P_7.1.11 |

| ESD robustness at corner pins                 | V <sub>ESD_CDM_CP</sub>  | -750 | _     | 750                  | V    | <sup>3)</sup> CDM         | P_7.1.14 |

| ESD immunity at any other pins                | V <sub>ESD_CDM</sub>     | -500 | _     | 500                  | ٧    | <sup>3)</sup> CDM         | P_7.1.12 |

Not subject to production test, specified by design. 1)

Latchup robustness: class II according to AEC - Q100-04. Note:

Human body model (human body model (HBM)) robustness according to AE - Q100-002.

<sup>2)</sup> 3) Charged device model (charged device model (CDM)) robustness according to AEC - Q100-011 Rev-D; voltage level refers to test condition (TC) mentioned in the standard.

#### **Datasheet**

3 General product characteristics

# 3.2 Functional range

Table 3 Functional range

| Parameter                  | Symbol          |      | Values |      | Unit | Note or Test<br>Condition | Number   |

|----------------------------|-----------------|------|--------|------|------|---------------------------|----------|

|                            |                 | Min. | Тур.   | Max. |      |                           |          |

| Supply voltages            |                 |      |        | •    | •    |                           | <u>.</u> |

| Transmitter supply voltage | V <sub>CC</sub> | 4.5  | _      | 5.5  | V    | _                         | P_7.2.1  |

| Thermal parameters         |                 |      |        |      |      |                           |          |

| Junction temperature       | T <sub>j</sub>  | -40  | _      | 150  | °C   | 1)                        | P_7.2.3  |

<sup>1)</sup> Not subject to production test, specified by design.

Note:

Within the functional range the integrated circuit (IC) operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

## 3.3 Thermal resistance

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, please visit www.jedec.org.

Table 4 Thermal resistance 1)

| Parameter                            | Symbol                 |      | Values |      | Unit | Note or Test<br>Condition             | Number  |

|--------------------------------------|------------------------|------|--------|------|------|---------------------------------------|---------|

|                                      |                        | Min. | Тур.   | Max. |      |                                       |         |

| Thermal resistance                   | ,                      |      |        |      | •    |                                       |         |

| Junction to ambient PG-DSO-8         | R <sub>thJA_DSO8</sub> | _    | 120    | _    | K/W  | 2)                                    | P_7.3.2 |

| Thermal shutdown (junction tempera   | iture)                 |      | 1      |      | 1    |                                       |         |

| Thermal shutdown temperature, rising | $T_{JSD}$              | 170  | 180    | 190  | °C   | Temperature falling:<br>minimum 150°C | P_7.3.3 |

| Thermal shutdown hysteresis          | ΔΤ                     | 5    | 10     | 20   | K    | _                                     | P_7.3.4 |

<sup>1)</sup> Not subject to production test, specified by design

<sup>2)</sup> Specified  $R_{thJA}$  value is according to JEDEC JESD51-2,-7 at natural convection on FR4 2s2p board. The product was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with two inner copper layers (2 × 70µm Cu, 2 × 35µm Cu).

4 High speed CAN functional description

## 4 High speed CAN functional description

HS *CAN* is a serial bus system that connects microcontrollers, sensors and actuators for real-time control applications. ISO 11898 describes the use of the CAN within road vehicles. According to the 7-layer OSI reference model the physical layer of a HS CAN bus system specifies the data transmission from one CAN node to all other CAN nodes available within the network. The physical layer specification of a CAN bus system includes all electrical specifications of a CAN. The CAN transceiver is part of the physical layer specification. The TLE9351BSJ is a high speed CAN transceiver with a dedicated bus wake-up function according to ISO 11898-2:2016.

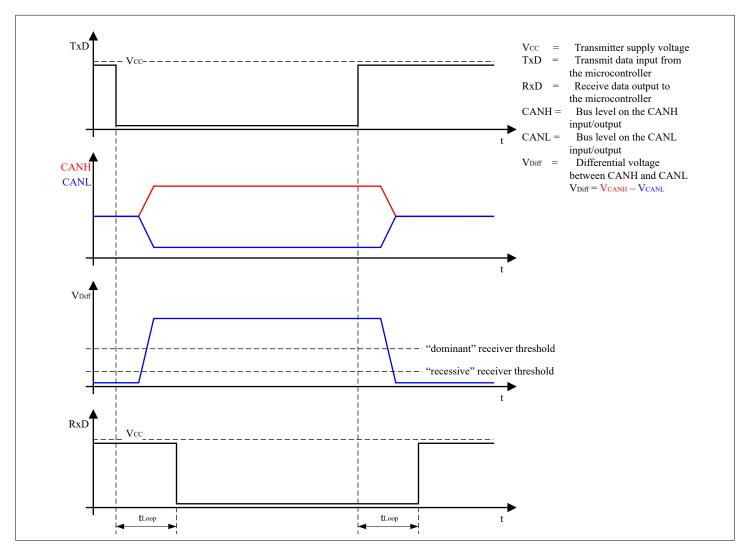

## 4.1 High speed CAN physical layer

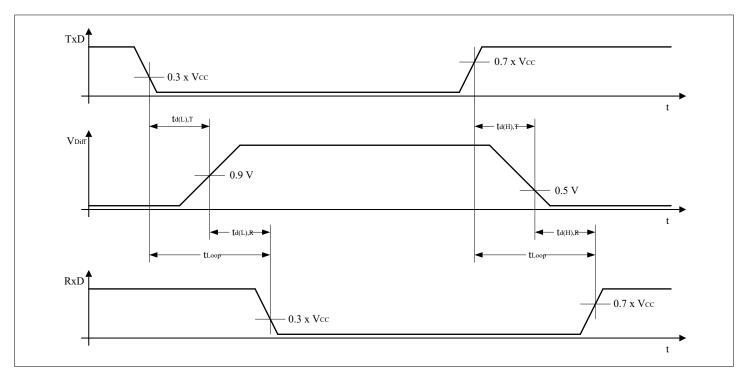

Figure 3 High speed CAN bus signals and logic signals

#### **Datasheet**

4 High speed CAN functional description

The TLE9351BSJ operates as an interface between the *CAN* controller and the physical bus medium. A HS CAN is a two wire differential network which allows data transmission rates up to 5 Mbit/s. The characteristics for a HS CAN are the two signal states on the CAN bus: dominant and recessive (see High speed CAN physical layer).

The CANH and CANL pins are the interface to the CAN bus and both pins operate as an input and output simultaneously. The RxD and TxD pins are the interface to the microcontroller. The pin TxD is the serial data input from the CAN controller, the RxD pin is the serial data output to the CAN controller. As shown in Figure 1, the TLE9351BSJ includes a receiver and a transmitter unit, allowing the transceiver to send data to the bus medium and monitor the data from the bus medium at the same time. The TLE9351BSJ converts the serial data stream which is available on the transmit data input TxD, into a differential output signal on the CAN bus, provided by the CANH and CANL pins. The receiver stage of the TLE9351BSJ monitors the data on the CAN bus and converts them to a serial, single-ended signal on the RxD output pin. A "low" signal on the TxD pin creates a dominant signal on the CAN bus, followed by a logical "low" signal on the RxD pin (see High speed CAN physical layer). The feature of broadcasting data to the CAN bus and listening to the data traffic on the CAN bus simultaneously is essential to support the bit-to-bit arbitration within CAN.

ISO 11898-2:2016 specifies the voltage levels for HS CAN transceivers. Whether a data bit is dominant or recessive depends on the voltage difference between the CANH and CANL pins ( $V_{\text{Diff}} = V_{\text{CANH}} - V_{\text{CANL}}$ ).

To transmit a dominant signal to the CAN bus the amplitude of the differential signal  $V_{\rm Diff}$  is higher than or equal to 1.5 V. To receive a recessive signal from the CAN bus the amplitude of the differential  $V_{\rm Diff}$  is lower than or equal to 0.5 V.

In partially-supplied high speed CAN network, the bus nodes of one common network have different power supply conditions. Some nodes are connected to the power supply, while other nodes are disconnected from the power supply and in power-down state. Regardless of whether the CAN bus subscriber is supplied or not, each subscriber connected to the common bus media must not interfere with the communication. The TLE9351BSJ is designed to support partially-supplied networks. In power-down state, the receiver input resistors are switched off and the transceiver input has a high resistance.

For permanently supplied ECUs, the HS CAN transceiver TLE9351BSJ provides a standby mode. In standby mode, the power consumption of the TLE9351BSJ is optimized to a minimum, while the device is still able to recognize wake-up patterns on the CAN bus and signal the wake-up event to the external microcontroller.

The voltage level on the digital input TxD and the digital output RxD is determined by the power supply level at the  $V_{\rm CC}$  pin. Depending on the voltage level at the  $V_{\rm CC}$  pin, the signal levels on the logic pins (STB, TxD and RxD) are compatible with microcontrollers having a 5 V I/O supply.

5 Modes of operation

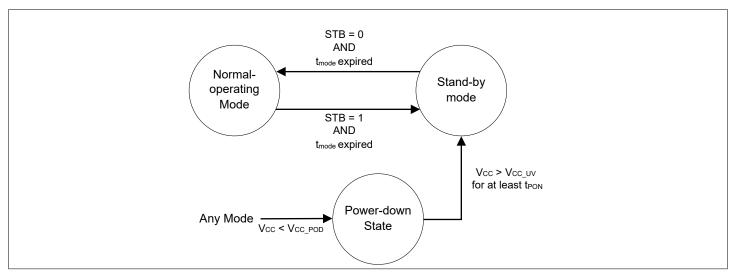

## 5 Modes of operation

The TLE9351BSJ supports the following modes of operation):

- Normal-operating mode

- · Standby mode

The mode selection input pin STB triggers mode changes. If a wake-up event occurs on the HS CAN bus, then the device indicates that on the RxD output pin in standby mode, but it does not trigger a mode change. An power down event on the supply  $V_{CC}$  powers down the device.

Figure 4 Mode state diagram

## 5.1 Normal-operating mode

In normal-operating mode all functions of the device are available and the device is fully functional. Data can be received from the HS *CAN* bus as well as transmitted to the HS CAN bus.

- The transmitter is enabled and drives the serial data stream on the TxD input pin to the bus pins CANH and CANL.

- The receiver is enabled and converts the signal from the bus to a serial data stream on the RxD output pin.

- The bus biasing is connected to  $V_{CC}/2$  for  $V_{CC} > V_{CC}$  UV

- The TxD timeout function is enabled (see Chapter 6.4).

- The overtemperature protection is enabled (see Chapter 6.6).

- The undervoltage detection on  $V_{CC}$  is enabled (see Chapter 6.3).

The device enters normal-operating mode by setting the mode selection pin STB to "low", see Figure 4. Normal-operating mode can be entered if the device supply  $V_{\rm CC}$  is higher than  $V_{\rm CC\_POD}$ . The device enters normal-operating mode after  $t_{\rm mode}$  expires.

Note:

If the device recognizes a recessive signal on the TxD input pin during a mode change from any mode to normal-operating mode, then it enables the transmit path after the mode change.

If the device recognizes a dominant signal on the TxD input pin during a mode change to normal-operating mode, then it keeps the transmit path disabled and it blocks the dominant signal in order to not disturb the bus communication. As soon as the device recognizes a recessive signal on the TxD input pin, it enables the transmit path again.

# 5.2 Standby mode

The standby mode is a low power mode of the TLE9351BSJ. In standby mode the transceiver can neither send data to the HS *CAN* bus nor receive data from the HS CAN bus. In standby mode the current consumption is reduced to a minimum while the device can still detect a wake-up pattern (*WUP*) on the HS CAN Bus.

#### 5 Modes of operation

- The transmitter is disabled and the data available on the TxD input is blocked.

- The low power receiver is enabled and monitors the HS CAN bus for a valid wake-up pattern (WUP). The RxD output pin indicates the detection of a valid wake-up pattern (Chapter 5.4). As long as no wake-up event is detected, the default of the RxD output is "high". After detecting a wake-up, the RxD follows the bus with a certain delay (see Figure 7).

- TxD timeout function is disabled.

- The overtemperature protection is disabled.

- The power down detection on  $V_{CC}$  is enabled (see Chapter 6.3).

The standby mode can be entered from normal-operating mode by setting the STB pin to "high".

To enter standby mode the supply  $V_{CC}$  must be available ( $V_{CC} > V_{CC\_POD}$ ). The device enters standby mode after  $t_{mode}$  expires.

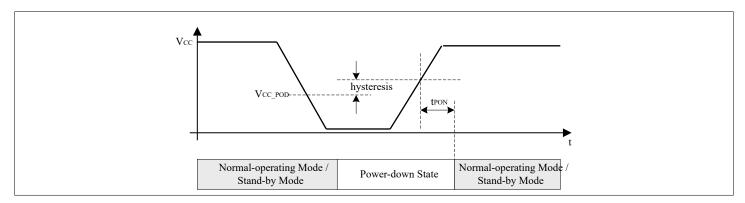

#### 5.3 Power-down state

If the supply voltage  $V_{\rm CC\_POD}$ , then the device powers down independently of Independent of STB (see Figure 5). In power-down state all functions of the device are disabled and the device is switched off. The input resistors of the receiver are disconnected. The CANH and CANL bus interface of the device is floating and acts as a high impedance input with a very low leakage current. The high impedance input does not influence the recessive level of the *CAN* and allows an optimized *EME* performance of the entire network. In power-down state the transceiver is an invisible node to the bus.  $t_{\rm pon}$  must expire as a prerequisite for the device to exit power-down state.

- The transmitter and receiver are disabled.

- The bus biasing is connected to high impedance.

- The TxD timeout function is disabled.

- The overtemperature protection is disabled.

- The power down detection on  $V_{CC}$  is enabled.

Figure 5 Power-down and power-up behavior and  $V_{CC}$

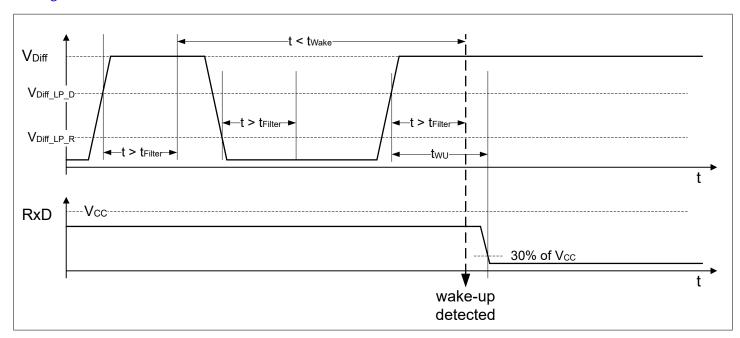

### 5.4 Wake-up pattern (WUP) detection

In standby mode the TLE9351BSJ offers the wake-up pattern (*WUP*) detection according to the ISO 11898-2:2016. In standby mode the low-power receiver monitors the activity on the *CAN* bus. If it detects a wake-up pattern, then it indicates the wake-up event on the RxD output pin.

In standby mode the device indicates a wake-up event on the HS CAN bus on the RxD output pin. The transceiver remains in its current mode of operation. The device does not perform a mode change due to the wake-up event.

The wake-up pattern contains the following sequence of signals:

- dominant with the pulse width t > t<sub>Filter</sub>

- recessive with the pulse width t > t<sub>Filter</sub>

- dominant with the pulse width t > t<sub>Filter</sub>

5 Modes of operation

The subsequent recessive and dominant pulses must occur within  $t_{\text{Wake}}$  to fulfill a wake-up pattern.  $t_{\text{Wake}}$  starts with the first valid dominant pulse that has a pulse width >  $t_{\text{Filter}}$ .

See Figure 6.

Figure 6 Wake-up pattern (WUP)

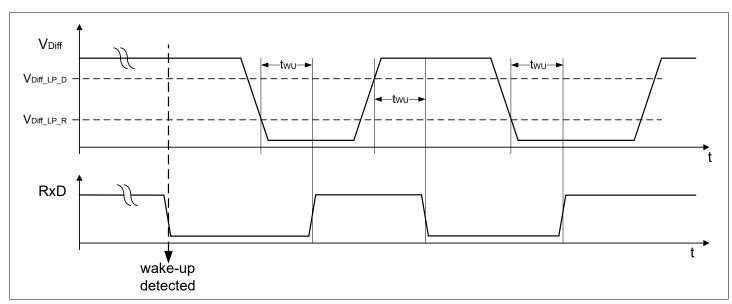

After the device detects a wake-up event the RxD output follows the CANH/CANL input pins. Dominant and recessive signals are indicated on the RxD output as "high" and "low" with the delay of  $t_{WU}$  as long as their pulse width exceeds the filter time  $t_{Filter}$  (see also Figure 7).

Figure 7 RxD signal after wake-up detection

#### 6 Fail safe functions

## 6.1 Short circuit protection

The CANH and CANL bus outputs are short circuit proof to *GND* and short circuit proof to a supply voltage. The current limiting circuit is designed to protect the transceiver from damage. If the device heats up due to a continuous short on the CANH or CANL, then the internal overtemperature protection switches off the bus transmitter.

## 6.2 Unconnected logic pins

All logic input pins have an internal pull-up resistor to  $V_{\rm CC}$ . If the  $V_{\rm CC}$  supply is active and the logical pins are open, the device enters the standby mode by default.

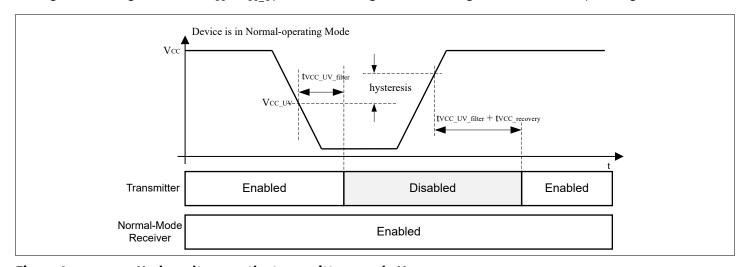

## $V_{CC}$ undervoltage

If the transmitter supply is in undervoltage condition  $V_{CC} < V_{CC\_UV}$ , then the device might not be able to provide the correct bus levels on the CANH and CANL output pins. During this time the transmitter is blocked in normal-operating mode, to avoid any interference with the network.

During undervoltage condition  $V_{CC} < V_{CC}$  UV, the bus biasing is switched to ground in normal-operating mode.

Figure 8 Undervoltage on the transmitter supply  $V_{\rm CC}$

## 6.4 TxD timeout feature

The TxD timeout feature protects the *CAN* bus against permanent blocking in case the logical signal on the TxD pin is continuously "low". A continuous "low" signal on the TxD pin might have its root cause in a locked-up microcontroller or in a short circuit on the printed circuit board, for example.

In normal-operating mode, a "low" signal on the TxD pin for the time  $t > t_{TxD}$  enables the TxD timeout feature and the device disables the transmitter, see Figure 9. The receiver is still active and the device continues to monitor data on the bus via the RxD output pin.

6 Fail safe functions

Figure 9 TxD timeout function

shows how the transmitter is deactivated and activated again. A permanent "low" signal on the TxD input pin activates the TxD timeout and deactivates the transmitter. To release the transmitter after a TxD timeout event, the device requires a signal change on the TxD input pin from "low" to "high".

## 6.5 Delay time for mode change

The device changes the mode of operation within the time window  $t_{\rm Mode}$ . During the mode change from standby mode to non-low power mode the device sets the RxD output "high" permanently, so it does not reflect the status on the CANH and CANL input pins.

After the mode change is completed, the device releases the RxD output pin.

## 6.6 Overtemperature protection

The TLE9351BSJ has an integrated overtemperature detection, which is designed to protect the device against thermal overstress of the transmitter. The overtemperature protection is only active in normal-operating mode. In case of an overtemperature condition, the temperature sensor disables the transmitter while the transceiver remains in normal-operating mode. After the device cools down it enables the transmitter again (see Figure 10). A hysteresis is implemented within the temperature sensor.

6 Fail safe functions

Figure 10 Overtemperature protection

7 Electrical characteristics

## 7 Electrical characteristics

# 7.1 Power supply interface

# **7.1.1** Electrical characteristics current consumption

#### Table 5 Electrical characteristics current consumption

$4.5 \text{ V} < V_{CC} < 5.5 \text{ V}$ ;  $R_L = 60 \Omega$ ;  $-40 ^{\circ}\text{C} < T_j < 150 ^{\circ}\text{C}$ ; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                                                 | Symbol                | Values |      |      |    | Note or Test Condition                                                | Number  |

|---------------------------------------------------------------------------|-----------------------|--------|------|------|----|-----------------------------------------------------------------------|---------|

|                                                                           |                       | Min.   | Тур. | Max. |    |                                                                       |         |

| Current consumption at $V_{CC}$ normal-operating mode, recessive state    | I <sub>CC_R</sub>     | -      | 1.4  | 4    | mA | $V_{TxD} = V_{CC}$ ;<br>V = 0  V;<br>$V_{CANH} = V_{CANL} = V_{CC}/2$ | P_8.1.1 |

| Current consumption at $V_{\rm CC}$ normal-operating mode, dominant state | I <sub>CC_D</sub>     | -      | 34   | 48   | mA | $V_{TxD} = V = 0 V;$                                                  | P_8.1.2 |

| Current consumption at $V_{CC}$ standby mode                              | I <sub>CC (STB)</sub> | -      | 5    | 18   | μΑ | $V_{TXD} = V_{STB} = V_{CC}$                                          | P_8.1.4 |

7 Electrical characteristics

# 7.1.2 Electrical characteristics undervoltage detection

## Table 6 Electrical characteristics undervoltage detection

4.5 V <  $V_{\rm CC}$  < 5.5 V;  $R_{\rm L}$  = 60  $\Omega$ ; -40°C <  $T_{\rm j}$  < 150°C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                             | Symbol                     | Values |      | Unit | Note or Test Condition | Number                     |          |

|-------------------------------------------------------|----------------------------|--------|------|------|------------------------|----------------------------|----------|

|                                                       |                            | Min.   | Тур. | Max. |                        |                            |          |

| V <sub>CC</sub> undervoltage threshold                | V <sub>CC_UV</sub>         | 3.8    | 4.2  | 4.5  | V                      | See Figure 8               | P_8.1.11 |

| $V_{\rm CC}$ undervoltage filter time                 | t <sub>VCC_UV_filter</sub> | 4      | 6    | 10   | μs                     | <sup>1)</sup> See Figure 8 | P_8.1.13 |

| $\overline{V_{\text{CC}}}$ undervoltage recovery time | t <sub>VCC_recovery</sub>  | _      | 7    | 70   | μs                     | <sup>1)</sup> See Figure 8 | P_8.1.14 |

| V <sub>CC</sub> power-down threshold                  | V <sub>CC_POD</sub>        | 2.0    | 2.5  | 3.0  | V                      | See Figure 5               | P_8.1.17 |

| V <sub>CC</sub> delay time power-up                   | $t_{PON}$                  | _      | 40   | 280  | μs                     | <sup>1)</sup> See Figure 5 | P_8.1.19 |

<sup>1)</sup> Not subject to production test, specified by design.

7 Electrical characteristics

# 7.2 Electrical characteristics CAN controller interface

### Table 7 Electrical characteristics CAN controller interface

$4.5 \text{ V} < V_{CC} < 5.5 \text{ V}; R_L = 60 \Omega; -40 ^{\circ}\text{C} < T_j < 150 ^{\circ}\text{C};$  all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                      | Symbol             | Symbol Values  |      |                   | Unit | Note or Test Condition                                                                 | Number   |

|--------------------------------|--------------------|----------------|------|-------------------|------|----------------------------------------------------------------------------------------|----------|

|                                |                    | Min.           | Тур. | Мах.              |      |                                                                                        |          |

| Receiver output RxD            |                    | •              |      |                   |      |                                                                                        |          |

| "High" level output current    | I <sub>RxD_H</sub> | -              | -2.5 | -1                | mA   | $V_{\text{RxD}} = V_{\text{CC}} - 0.4 \text{ V};$<br>$V_{\text{Diff}} < 0.5 \text{ V}$ | P_8.2.1  |

| "Low" level output current     | I <sub>RxD_L</sub> | 1              | 2.5  | _                 | mA   | $V_{\text{RxD}} = 0.4 \text{ V};$<br>$V_{\text{Diff}} > 0.9 \text{ V}$                 | P_8.2.2  |

| Transmission input TxD         | ·                  |                |      |                   |      |                                                                                        |          |

| "High" level input voltage     | $V_{TxD_{H}}$      | 0.7 × <i>V</i> | _    | 6.0               | V    | Recessive state                                                                        | P_8.2.3  |

| "Low" level input voltage      | $V_{TxD\_L}$       | -0.3           | _    | 0.3 × <i>V</i> cc | V    | Dominant state                                                                         | P_8.2.4  |

| Internal pull-up resistor TxD  | $R_{TxD}$          | 35             | 55   | 70                | kΩ   | _                                                                                      | P_8.2.7  |

| Input capacitance              | $C_{TxD}$          | _              | _    | 10                | pF   | 1)                                                                                     | P_8.2.8  |

| TxD permanent dominant timeout | $t_{TxD}$          | 1              | 2.3  | 4                 | ms   | Normal-operating mode                                                                  | P_8.2.9  |

| Standby input STB              | <u>'</u>           | •              |      |                   |      |                                                                                        |          |

| "High" level input voltage     | V <sub>STB_H</sub> | 0.7 × <i>V</i> | _    | 6.0               | V    | standby mode                                                                           | P_8.2.13 |

| "Low" level input voltage      | V <sub>STB_L</sub> | -0.3           | -    | 0.3 × <i>V</i> cc | V    | Normal-operating mode                                                                  | P_8.2.14 |

| Internal pull-up resistor STB  | R <sub>STB</sub>   | 35             | 55   | 70                | kΩ   | -                                                                                      | P_8.2.16 |

| Input capacitance              | C (STB)            | _              | _    | 10                | pF   | 1)                                                                                     | P_8.2.20 |

<sup>1)</sup> Not subject to production test, specified by design.

7 Electrical characteristics

# 7.3 Electrical characteristics receiver

### Table 8 Electrical characteristics receiver

$4.5 \text{ V} < V_{\text{CC}} < 5.5 \text{ V}; R_{\text{L}} = 60 \Omega; -40 ^{\circ}\text{C} < T_{\text{j}} < 150 ^{\circ}\text{C};$  all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                          | Symbol                                  |      | Values |      |    | Note or Test Condition                                                                                                           | Number   |

|----------------------------------------------------|-----------------------------------------|------|--------|------|----|----------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                    |                                         | Min. | Тур.   | Max. |    |                                                                                                                                  |          |

| Differential range dominant normal-operating mode  | V <sub>Diff_D_Range</sub>               | 0.9  | -      | 8.0  | V  | $^{1)}$ -12 V $\leq V_{\rm CMR} \leq 12$ V                                                                                       | P_8.3.3  |

| Differential range recessive normal-operating mode | V <sub>Diff_R_Range</sub>               | -3.0 | _      | 0.5  | V  | $^{1)}$ -12V $\leq V_{\rm CMR} \leq 12$ V                                                                                        | P_8.3.5  |

| Differential range dominant standby mode           | V <sub>Diff_D_STB_Range</sub>           | 1.15 | 3.0    | 8.0  | V  | $^{1)}$ -12 V $\leq V_{\rm CMR} \leq 12$ V                                                                                       | P_8.3.7  |

| Differential range recessive standby mode          | V <sub>Diff_R_STB_Range</sub>           | -3.0 | 0      | 0.4  | V  | $^{1)}$ -12 V $\leq V_{\rm CMR} \leq 12$ V                                                                                       | P_8.3.9  |

| Common mode voltage                                | $V_{CMR}$                               | -12  | _      | 12   | V  | -                                                                                                                                | P_8.3.11 |

| Single ended internal resistance                   | R <sub>CAN_H</sub> , R <sub>CAN_L</sub> | 6    | 40     | 50   | kΩ | 1) Recessive state;<br>$-2 \text{ V} \le V_{\text{CANH}} \le 7 \text{ V};$<br>$-2 \text{ V} \le V_{\text{CANL}} \le 7 \text{ V}$ | P_8.3.12 |

| Differential internal resistance                   | R <sub>Diff</sub>                       | 12   | 80     | 100  | kΩ | 1) Recessive state;<br>$-2 \text{ V} \le V_{\text{CANH}} \le 7 \text{ V};$<br>$-2 \text{ V} \le V_{\text{CANL}} \le 7 \text{ V}$ | P_8.3.14 |

| Input resistance deviation between CANH and CANL   | $\Delta R_{\rm i}$                      | -2   | _      | 2    | %  | <sup>1)</sup> Recessive state;<br>$V_{\text{CANH}} = V_{\text{CANL}} = 5 \text{ V}$                                              | P_8.3.16 |

| Input capacitance CANH, CANL versus <i>GND</i>     | C <sub>In</sub>                         | -    | -      | 40   | pF | <sup>1) 2)</sup> Recessive state;<br>normal-operating mode                                                                       | P_8.3.17 |

| Differential input capacitance                     | C <sub>InDiff</sub>                     | _    | 4      | 20   | pF | <sup>1) 2)</sup> Recessive state;<br>normal-operating mode                                                                       | P_8.3.18 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> S2P-method; f = 10 MHz.

7 Electrical characteristics

# 7.4 Electrical characteristics transmitter

## Table 9 Electrical characteristics transmitter

4.5 V <  $V_{CC}$  < 5.5 V;  $R_L$  = 60  $\Omega$ ; -40°C <  $T_j$  < 150°C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                                                                                      | Symbol Values                                                 |                          |                       | <b>.</b>              | Unit | Note or Test Condition                                                                                                  | Number   |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------|-----------------------|-----------------------|------|-------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                                                |                                                               | Min.                     | Тур.                  | Max.                  |      |                                                                                                                         |          |

| CANL, CANH recessive<br>output voltage<br>normal-operating mode                                                | V <sub>CANL,H</sub>                                           | 2.0                      | 2.5                   | 3.0                   | V    | $V_{TxD} = V_{CC}$ ;<br>no load                                                                                         | P_8.4.1  |

| CANH, CANL recessive<br>output voltage difference<br>normal-operating mode                                     | V <sub>Diff_R_NM</sub> = V <sub>CANH</sub> -V <sub>CANL</sub> | -50                      | -10                   | 50                    | mV   | V <sub>TxD</sub> = V;<br>no load                                                                                        | P_8.4.2  |

| CANL dominant<br>output voltage<br>normal-operating mode                                                       | V <sub>CANL</sub>                                             | 0.5                      | 1.5                   | 2.25                  | V    | $V_{\text{TxD}} = 0 \text{ V};$<br>$50 \Omega < R_{\text{L}} < 65 \Omega$                                               | P_8.4.3  |

| CANH dominant<br>output voltage<br>normal-operating mode                                                       | V <sub>CANH</sub>                                             | 2.75                     | 3.4                   | 4.5                   | V    | $V_{\text{TxD}} = 0 \text{ V};$<br>$50 \Omega < R_{\text{L}} < 65 \Omega$                                               | P_8.4.4  |

| Differential voltage dominant normal-operating mode  V <sub>Diff</sub> = V <sub>CANH</sub> - V <sub>CANL</sub> | $V_{\mathrm{Diff\_D\_NM}}$                                    | 1.5                      | 1.9                   | 2.5                   | V    | $V_{TxD} = 0 \text{ V};$<br>$50 \Omega < R_L < 65 \Omega;$<br>$4.75 \text{ V} < V_{CC} < 5.25 \text{ V}$                | P_8.4.5  |

| Differential voltage dominant<br>extended bus load<br>normal-operating mode                                    | V <sub>Diff_EXT_BL</sub>                                      | 1.4                      | 1.9                   | 3.3                   | V    | $V_{TxD} = 0 \text{ V};$<br>$45 \Omega < R_L < 70 \Omega;$<br>$4.75 \text{ V} < V_{CC} < 5.25 \text{ V}$                | P_8.4.6  |

| Differential voltage dominant<br>high extended bus load<br>normal-operating mode                               | V <sub>Diff_HEXT_BL</sub>                                     | 1.5                      | 3.5                   | 5.0                   | V    | 1) $V_{TxD} = 0 \text{ V}$ ;<br>$R_L = 2240 \Omega$ ;<br>static behavior;<br>$4.75 \text{ V} < V_{CC} < 5.25 \text{ V}$ | P_8.4.7  |

| CANH, CANL recessive<br>output voltage difference<br>standby mode                                              | V <sub>Diff_STB</sub>                                         | -0.2                     | 0                     | 0.2                   | V    | No load                                                                                                                 | P_8.4.8  |

| CANL, CANH recessive<br>output voltage<br>standby mode                                                         | V <sub>CANL,H_STB</sub>                                       | -0.1                     | 0                     | 0.1                   | V    | No load                                                                                                                 | P_8.4.9  |

| Driver symmetry ( $V_{\text{SYM}} = V_{\text{CANH}} + V_{\text{CANL}}$ )                                       | $V_{SYM}$                                                     | 0.9 ×<br>V <sub>CC</sub> | 1.0 × V <sub>CC</sub> | 1.1 × V <sub>CC</sub> | V    | $^{1)} {}^{2)} C_1 = 4.7 \text{ nF}$                                                                                    | P_8.4.10 |

| CANL short circuit current                                                                                     | I <sub>CANLsc</sub>                                           | -115                     | 90                    | 115                   | mA   | 1) -3 V < $V_{CANLshort}$ < 18 V;<br>$t < t_{TxD}$ ;<br>$V_{TxD} = 0$ V                                                 | P_8.4.11 |

|                                                                                                                |                                                               | 1                        |                       |                       |      |                                                                                                                         |          |

(table continues...)

#### **Datasheet**

7 Electrical characteristics

## Table 9 (continued) Electrical characteristics transmitter

$4.5 \text{ V} < V_{CC} < 5.5 \text{ V}$ ;  $R_L = 60 \Omega$ ;  $-40 ^{\circ}\text{C} < T_j < 150 ^{\circ}\text{C}$ ; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                                               | Symbol                     | Values    |     |      | Unit | Note or Test Condition                                                                                                                           | Number   |  |

|-------------------------------------------------------------------------|----------------------------|-----------|-----|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

|                                                                         |                            | Min. Typ. |     | Max. |      |                                                                                                                                                  |          |  |

| CANH short circuit current                                              | I <sub>CANHsc</sub>        | -115      | -90 | 115  | mA   | 1) -3 < V <sub>CANHshort</sub> < 18 V                                                                                                            | P_8.4.13 |  |

| Leakage current, CANH                                                   | I <sub>CANH,lk</sub>       | -5        | 1   | 5    | μΑ   | $V_{CC} = 0 \text{ V};$<br>$0 \text{ V} < V_{CANH} \le 5 \text{ V};$<br>$V_{CANH} = V_{CANL}$                                                    | P_8.4.19 |  |

| Leakage current, CANL                                                   | I <sub>CANL,Ik</sub>       | -5        | 1   | 5    | μΑ   | $V_{CC} = 0 \text{ V};$<br>$0 \text{ V} < V_{CANL} \le 5 \text{ V};$<br>$V_{CANH} = V_{CANL}$                                                    | P_8.4.20 |  |

| CANH, CANL output voltage<br>difference slope, recessive to<br>dominant | V <sub>diff_slope_rd</sub> | -         | 42  | 70   | V/µs | $^{1)}$ 30% to 70% of measured differential bus voltage; $C_2 = 100 \text{ pF}$ ; $R_L = 60 \Omega$ ; 4.75 V < $V_{CC}$ < 5.25 V                 | P_8.4.21 |  |

| CANH, CANL output voltage difference slope, dominant to recessive       | V <sub>diff_slope_dr</sub> | -70       | -42 | -    | V/µs | $^{1)}$ 70% to 30% of measured differential bus voltage; $C_2 = 100 \text{ pF}$ ; $R_L = 60 \Omega$ ; $4.75 \text{ V} < V_{CC} < 5.25 \text{ V}$ | P_8.4.22 |  |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup>  $V_{\text{SYM}}$  is observed during dominant and recessive state and also during the transition from dominant to recessive state and vice versa, while TxD is stimulated by a square wave signal with a frequency of 1 MHz.

7 Electrical characteristics

# 7.5 Electrical characteristics dynamic transceiver parameters

## Table 10 Electrical characteristics dynamic transceiver parameters

$4.5 \text{ V} < V_{CC} < 5.5 \text{ V}$ ;  $R_L = 60 \Omega$ ;  $-40 ^{\circ}\text{C} < T_j < 150 ^{\circ}\text{C}$ ; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                              | Symbol                                         | Values                                                                                              |     |         | Unit | Note or Test Condition                                                                               | Number   |

|--------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----|---------|------|------------------------------------------------------------------------------------------------------|----------|

|                                                        |                                                | Min. Typ.                                                                                           |     | Max.    |      |                                                                                                      |          |

| Propagation delay TxD-to-RxD                           | $t_{Loop}$                                     | 80 150 235 ns $C_1 = 0 \text{ pF};$ $C_2 = 100 \text{ pF};$ $C_2 = 150 \text{ pF};$ (see Figure 12) |     | P_8.5.1 |      |                                                                                                      |          |

| Propagation delay increased load TxD-to-RxD            | $t_{ m Loop\_150}$                             | 80                                                                                                  | 180 | 330     | ns   | $C_1 = 0 \text{ pF};$<br>$C_2 = 100 \text{ pF};$<br>$C_{RXD} = 15 \text{ pF};$<br>$R_L = 150 \Omega$ | P_8.5.2  |

| Propagation delay TxD to bus "low" to dominant         | $t_{ m d(L)\_T}$                               | 30                                                                                                  | 70  | 140     | ns   | $C_1 = 0 \text{ pF};$<br>$C_2 = 100 \text{ pF};$<br>$C_{RXD} = 15 \text{ pF};$<br>(see Figure 12)    | P_8.5.3  |

| Propagation delay TxD to bus "high" to recessive       | $t_{ m d(H)\_T}$                               | 30                                                                                                  | 90  | 140     | ns   | $C_1 = 0 \text{ pF};$<br>$C_2 = 100 \text{ pF};$<br>$C_{RXD} = 15 \text{ pF};$<br>(see Figure 12)    | P_8.5.4  |

| Propagation delay<br>bus to RxD<br>dominant to "low"   | $t_{d(L)_{L}R}$                                | 30                                                                                                  | 90  | 140     | ns   | $C_{RxD}$ = 15 pF;<br>Independent of $t_{Bit}$ ;<br>(see Figure 12)                                  | P_8.5.5  |

| Propagation delay<br>bus to RxD<br>recessive to "high" | t <sub>d(H)_R</sub>                            | 30                                                                                                  | 100 | 140     | ns   | $C_{\text{RxD}} = 15 \text{ pF};$<br>Independent of $t_{\text{Bit}}$ ;<br>(see Figure 12)            | P_8.5.6  |

| Delay times                                            |                                                |                                                                                                     |     |         |      |                                                                                                      |          |

| Delay time for mode change                             | mode change $t_{Mode}$ – 12 20 $\mu s$ $^{1)}$ |                                                                                                     | 1)  | P_8.5.7 |      |                                                                                                      |          |

| CAN activity filter time                               | t <sub>Filter</sub>                            | 0.5                                                                                                 | 1.2 | 1.8     | μs   | See Figure 6                                                                                         | P_8.5.10 |

| Bus wake-up timeout                                    | $t_{Wake}$                                     | 0.8                                                                                                 | 1.5 | 10      | ms   | <sup>1)</sup> See Figure 6                                                                           | P_8.5.11 |

| Bus wake-up delay time  (table continues)              | $t_{WU}$                                       | _                                                                                                   | 2.5 | 5       | μs   | See Figure 6 and Figure 7                                                                            | P_8.5.12 |

(table continues...)

### **Datasheet**

# Table 10 (continued) Electrical characteristics dynamic transceiver parameters

$4.5 \text{ V} < V_{CC} < 5.5 \text{ V}$ ;  $R_L = 60 \Omega$ ;  $-40 ^{\circ}\text{C} < T_j < 150 ^{\circ}\text{C}$ ; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                                                                                                             | Symbol                                                      | Values |                                                                                                                                                      |          | Unit | Note or Test Condition                                                                                                                               | Number   |  |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

|                                                                                                                                       |                                                             | Min.   | Тур.                                                                                                                                                 | Max.     |      |                                                                                                                                                      |          |  |

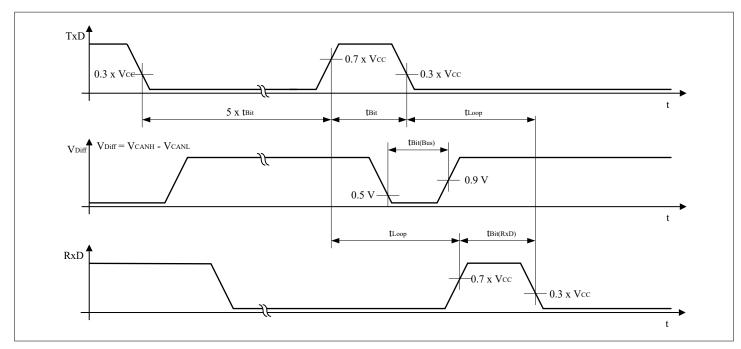

| CAN FD characteristics                                                                                                                |                                                             |        |                                                                                                                                                      |          |      |                                                                                                                                                      |          |  |

| Received recessive bit width variation up to 2 Mbit/s                                                                                 | t <sub>Bit(RxD)_2M</sub>                                    | -100   | _                                                                                                                                                    | 50       | ns   | $C_2$ = 100 pF;<br>$C_{RXD}$ = 15 pF;<br>$t_{Bit}$ = 500 ns;<br>see Figure 13                                                                        | P_8.5.13 |  |

| Received recessive bit width variation up to 5 Mbit/s                                                                                 | t <sub>Bit(RxD)_5M</sub>                                    | -80    | _                                                                                                                                                    | 20       | ns   | $C_2 = 100 \text{ pF};$<br>$C_{RxD} = 15 \text{ pF};$<br>$t_{Bit} = 200 \text{ ns};$<br>see Figure 13                                                | P_8.5.14 |  |

| Transmitted recessive bit width variation up to 2 Mbit/s                                                                              | t <sub>Bit(Bus)_2M</sub>                                    | -45    | -                                                                                                                                                    | 10       | ns   | $C_2 = 100 \text{ pF};$ $C_{RXD} = 15 \text{ pF};$ $t_{Bit} = 500 \text{ ns};$ see Figure 13                                                         | P_8.5.15 |  |

| Transmitted recessive bit width variation up to 5 Mbit/s                                                                              | t <sub>Bit(Bus)_5M</sub>                                    | -45    | -                                                                                                                                                    | 10       | ns   | $C_2 = 100 \text{ pF};$ $C_{RXD} = 15 \text{ pF};$ $t_{Bit} = 200 \text{ ns};$ see Figure 13                                                         | P_8.5.16 |  |

| Receiver timing symmetry up to 2 Mbit/s $\Delta t_{\text{Rec}\_2M} = t_{\text{Bit}(\text{RxD})\_2M} - t_{\text{Bit}(\text{Bus})\_2M}$ | $\Delta t_{ m Rec\_2M}$                                     | -45    | -23                                                                                                                                                  | 15       | ns   | $C_2 = 100 \text{ pF};$<br>$C_{RxD} = 15 \text{ pF};$<br>$t_{Bit} = 500 \text{ ns};$<br>$4.75 \text{ V} < V_{CC} < 5.25 \text{ V};$<br>see Figure 13 | P_8.5.17 |  |

| Receiver timing symmetry up to 5 Mbit/s                                                                                               | timing symmetry up to $\Delta t_{ m Rec\_5M}$ -45 -23 15 ns |        | $C_2 = 100 \text{ pF};$<br>$C_{RxD} = 15 \text{ pF};$<br>$t_{Bit} = 200 \text{ ns};$<br>$4.75 \text{ V} < V_{CC} < 5.25 \text{ V};$<br>see Figure 13 | P_8.5.18 |      |                                                                                                                                                      |          |  |

<sup>1)</sup> Not subject to production test, specified by design.

7 Electrical characteristics

# 7.6 Diagrams

Figure 11 Test circuit

Figure 12 Timing diagrams for dynamic characteristics

7 Electrical characteristics

Figure 13 Recessive bit time for five dominant bits followed by one recessive bit

#### **Datasheet**

8 Application information

# 8 Application information

# 8.1 ESD robustness according to IEC 61000-4-2

Tests for *ESD* robustness according to IEC 61000-4-2 Gun test (150 pF, 330  $\Omega$ ) have been performed. The results and test conditions are available in a separate test report.

Table 11 ESD robustness according to IEC 61000-4-2

| Performed test                                                         | Result | Unit | Remarks           |

|------------------------------------------------------------------------|--------|------|-------------------|

| Electrostatic discharge voltage at pin CANH and CANL versus <i>GND</i> | ≥+8    | kV   | 1) Positive pulse |

| Electrostatic discharge voltage at pin CANH and CANL versus GND        | ≤ -8   | kV   | 1) Negative pulse |

<sup>1)</sup> Not subject to production test. ESD robustness "ESD GUN" according to GIFT/ICT paper: "*EMC* Evaluation of *CAN* Transceivers, version IEC TS62228", section 4.3. (DIN EN61000-4-2)

Tested by external test facility (IBEE Zwickau).

8 Application information

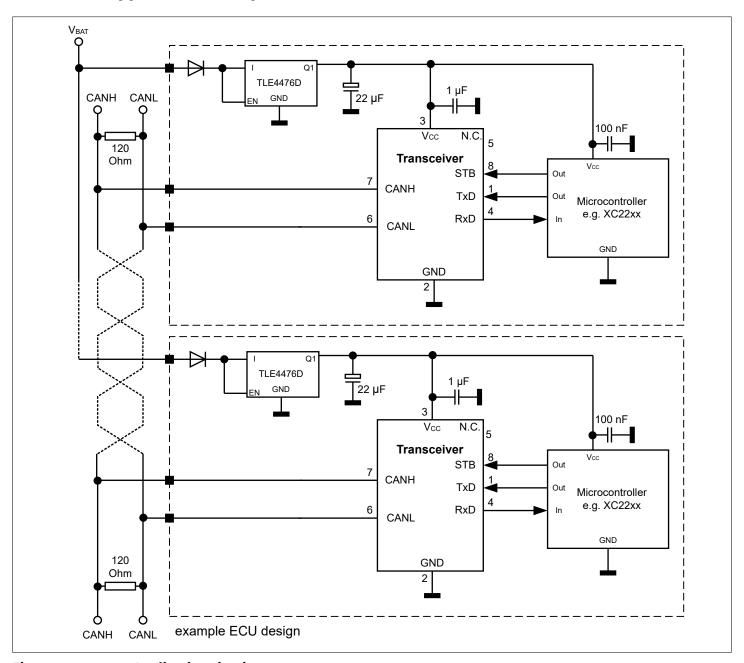

# 8.2 Application example

Figure 14 Application circuit

# 8.3 Further application information

For further information you may visit: https://www.infineon.com/automotive-transceiver

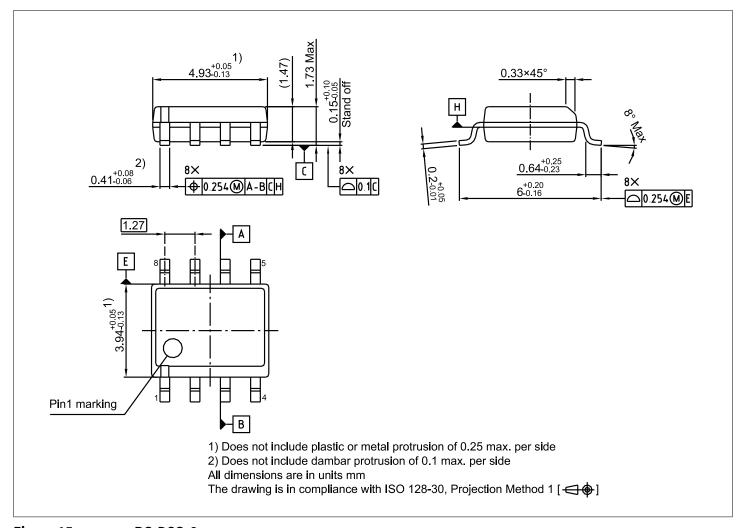

9 Package information

## 9 Package information

Figure 15 PG-DSO-8

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations, the device is available as a Green Product. Green Products are RoHS compliant (Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

#### Information on packages

For more information on packages, such as recommendations on assembly, refer to www.infineon.com/packages.

28

#### **Datasheet**

Glossary

# **Glossary**

#### CAN

controller area network (CAN)

#### **CDM**

charged device model (CDM)

A model for characterizing the susceptibility of an electronic device to damage from electrostatic discharge (ESD).

#### **EMC**

electromagnetic compatibility (EMC)

The ability of electrical equipment and systems to function acceptably in their electromagnetic environment, by limiting the unintentional generation, propagation and reception of electromagnetic energy which may cause unwanted effects such as electromagnetic interference (EMI) or even physical damage in operational equipment.

#### **EME**

electromagnetic emission (EME)

An emission within the electromagnetic spectrum.

#### **ESD**

electrostatic discharge (ESD)

A sudden and momentary flow of electric current between two electrically charged objects caused by contact, an electrical short or dielectric breakdown.

#### **GND**

ground (GND)

#### **HBM**

human body model (HBM)

A model for characterizing the susceptibility of an electronic device to damage from electrostatic discharge (ESD) based on a human body.

#### 1/0

input/output (I/O)

The communication between an information processing system and another information processing system.

#### IC

integrated circuit (IC)

A miniature electronic circuit built on the surface of a thin substrate of a semiconductor material.

#### **OEM**

original equipment manufacturer (OEM)

#### RoHS

Restriction of Hazardous Substances in Electrical and Electronic Equipment (RoHS)

European Union (EU) rules restricting the use of hazardous substances in electrical and electronic equipment to protect the environment and public health.

### **Datasheet**

### WUP

wake-up pattern (WUP)

A specific sequence of signals that triggers a device to transition from a low-power sleep mode to a higher-power operating mode.

### **Datasheet**

Revision history

# **Revision history**

| Revision | Date       | Changes                                                                                        |

|----------|------------|------------------------------------------------------------------------------------------------|

| 1.01     | 2025-10-17 | <ul> <li>Datasheet updated according to ISO 11898-2:2024</li> <li>Editorial changes</li> </ul> |

| 1.00     | 2023-08-11 | Datasheet created                                                                              |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2025-10-17 Published by Infineon Technologies AG 81726 Munich, Germany

© 2025 Infineon Technologies AG All Rights Reserved.

Do you have a question about any aspect of this document?

${\bf Email: erratum@infineon.com}$

Document reference IFX-drr1752764627661 Z8F80194933

#### Important notice

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### Warnings

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.