#### **About this document**

#### **Scope and purpose**

This application note discusses the basic parameters of silicon carbide (SiC) MOSFETs and derives gate drive requirements. The document covers the following EiceDRIVER™ isolated and level-shift gate driver ICs:

- EiceDRIVER™ Compact isolated gate driver:

- o <u>1ED3122MC12H</u>, <u>1ED3124MC12H</u>, <u>1ED3124MU12F</u>, <u>1ED3127MU12F</u>, <u>1ED3142MU12F</u>, <u>1ED3241MC12H</u>, <u>1ED3251MC12H</u>

- EiceDRIVER™ Enhanced isolated gate driver:

- o <u>1ED3321MC12N</u>, <u>1ED3491MC12M</u>, <u>1ED3890MC12M</u>

- EiceDRIVER™ silicon-on-insulator (SOI) level-shift gate driver:

- o <u>2ED1323S12P</u>

These gate driver IC families provide galvanic isolation based on a coreless transformer, or junction isolation based on silicon-on-insulator. Power transistors rated up to 2300 V with ultrafast switching capability can be handled optimally through these gate drivers. Therefore, this document concentrates mainly on suitable levelshift (1200 V) and galvanically isolated gate driver ICs (2300 V).

Please note that Infineon's advanced CoolSiC<sup>™</sup> Trench MOSFET technology offers various benefits that reduce the complexity of gate driving. These benefits are mentioned in detail in this document. Also refer to other application notes that highlight the properties of CoolSiC<sup>™</sup>.

Note: This document does not refer to the SiC bipolar transistors or the SiC JFETs.

#### **Intended audience**

The intended audiences for this document are design engineers, technicians, and developers of electronic systems.

# Advanced gate drive options for silicon carbide (SiC) MOSFETs using EiceDRIVER $^{\text{\tiny{TM}}}$

#### **Table of contents**

### **Table of contents**

| Abou  | ut this document                                                                      | 1               |

|-------|---------------------------------------------------------------------------------------|-----------------|

| Table | e of contents                                                                         | 2               |

| 1     | Overview                                                                              | 3               |

| 2     | SiC MOSFET gate drive requirements and options                                        | 5               |

| 2.1   | Synchronous rectification                                                             |                 |

| 2.2   | Enable short dead time for higher efficiency                                          | 5               |

| 2.2.1 | Precise propagation delay matching                                                    | 6               |

| 2.2.2 | Precise integrated filters                                                            | 6               |

| 2.3   | Negative gate voltage                                                                 | 7               |

| 2.4   | Wide range of gate voltages                                                           | 8               |

| 2.5   | Extended common mode transient immunity(CMTI) capability                              | 10              |

| 2.6   | Fast DESAT detection and overcurrent protection                                       | 10              |

| 2.7   | Active Miller clamping                                                                | 14              |

| 3     | Power dissipation                                                                     | 16              |

| 3.1   | Isolated gate driver power dissipation                                                | 16              |

| 3.2   | Level-shift gate driver power dissipation                                             | 17              |

| 4     | Considerations for single transistor topologies and applications with low dV/dt stres | s during an OFF |

|       | state                                                                                 | _               |

| 5     | Summary                                                                               | 20              |

| Refe  | rences                                                                                | 21              |

| Revis | sion history                                                                          | 22              |

|       | laimer                                                                                |                 |

|       |                                                                                       |                 |

# Advanced gate drive options for silicon carbide (SiC) MOSFETs using EiceDRIVER™

#### 1 Overview

### 1 Overview

For each gate driver, the functionalities required for driving a SiC MOSFET are listed in Table 1. The most important parameters are:

- Tight propagation delay matching

- Precise input filters

- Wide output side supply range

- Negative gate voltage capability

- Extended common mode transient immunity (CMTI) capability

- Active Miller clamp

- Fast desaturation (DESAT) protection

Table 1 Gate driver functionalities important for SiC MOSFETs

|                                    | X3 Compact family                                                |              |               |              | F3<br>family       | 2L-S            | SRC<br>nily                              |                 | log/ X3<br>family | Level-<br>shift SOI<br>family |             |

|------------------------------------|------------------------------------------------------------------|--------------|---------------|--------------|--------------------|-----------------|------------------------------------------|-----------------|-------------------|-------------------------------|-------------|

| Function/property                  | 1ED3122MC12H                                                     | 1ED3124MC12H | 1ED3124MU12F  | 1ED3127MU12F | 1ED3142MU12F       | 1ED3321MC12N    | 1ED3241MC12H                             | 1ED3251MC12H    | 1ED3491MC12M      | 1ED3890MC12M                  | 2ED1323S12P |

| Propagation delay matching < 15 ns | ✓                                                                | ✓            | ✓             | ✓            | ✓                  | ✓               | <b>✓</b>                                 | ✓               | _                 | _                             | _           |

| Precise input filters < 150 ns     | ✓                                                                | ✓            | ✓             | ✓            | ✓                  | ✓               | _                                        | _               | _                 | _                             | ✓           |

| Wide output supply range           | ✓                                                                | ✓            | ✓             | ✓            | ✓                  | ✓               | ✓                                        | ✓               | ✓                 | ✓                             | ✓           |

| Negative gate voltage              | ✓                                                                | ✓            | ✓             | ✓            | ✓                  | ✓               | ✓                                        | ✓               | ✓                 | ✓                             | _           |

| Extended CMTI ( > 200 kV/μs)       | ✓                                                                | <b>✓</b>     | <b>✓</b>      | ✓            | <b>✓</b>           | ✓               | ✓                                        | <b>✓</b>        | <b>✓</b>          | ✓                             | N.A.        |

| Fast DESAT                         | _                                                                | ı            | ١             | _            | ı                  | ✓               | _                                        | ı               | <b>✓</b>          | ✓                             | _           |

| Fast OCP                           | _                                                                | 1            | ı             | _            | 1                  | -               | _                                        | 1               | 1                 | _                             | ✓           |

| Slew rate control                  | _                                                                | 1            | 1             | _            | 1                  | -               | ✓                                        | ✓               | 1                 | _                             | _           |

| UVLO <sub>oN</sub> ≥ 12 V          | _                                                                | ✓            | ✓             | ✓            | ✓                  | ✓               | ✓                                        | ✓               | ✓                 | ✓                             | ✓           |

| Active Miller clamp                | ✓                                                                | 1            | 1             | ✓            | 1                  | ✓               | _                                        | ✓               | ✓                 | ✓                             | ✓           |

| Separate output source and sink    | _                                                                | ✓            | ✓             | _            | ✓                  | ✓               |                                          | _               | ✓                 | ✓                             | _           |

| Best use for                       | Best price performance ratio, Miller clamp/negative gate voltage |              | Fast<br>DESAT | ra           | ew<br>Ite<br>Itrol | parai<br>and co | gurable<br>meters<br>ondition<br>itoring | Half-<br>bridge |                   |                               |             |

# Advanced gate drive options for silicon carbide (SiC) MOSFETs using EiceDRIVER™

#### 1 Overview

Most popular power converter topologies used in industrial applications consist of power transistors connected in a half-bridge configuration. For such a configuration, the most simple and cost-effective choice is the EiceDRIVER™ X3 Compact (1ED31xx) or the SOI gate driver (2ED1323S12P) with 2-channel output. If no short circuit protection is required from the gate driver, EiceDRIVER™ X3 Compact (1ED31xx) in both DSO-8 150 mil and 300 mil are the most suitable for driving the SiC MOSFETs. However, when fast short circuit protection is required, EiceDRIVER™ Enhanced 1ED3321MC12N, 1ED3491MC12M, 1ED3890MC12M, and2ED1323S12P fit best. 1ED3491MC12M and 1ED3890MC12M belong to the X3 family and offer advanced functionalities that enable high level of configurability and parameter monitoring. This in turn enables flexible design and condition monitoring.

Single-transistor converter topologies, such as boost, buck, forward, or flyback, that use CoolSiC™ MOSFETs might benefit the most from parts that have separate source and sink output configurations.

#### 2 SiC MOSFET gate drive requirements and options

### 2 SiC MOSFET gate drive requirements and options

#### 2.1 Synchronous rectification

When operating inductive loads such as motors in pulse-width modulation (PWM) mode, half-bridge configurations need a freewheeling path during the dead time and the off-state interval of the switch. The freewheeling path is automatically provided by the SiC MOSFET body diode. It is a good practice to support the body diode's forward operation by turning on the transistor part of the MOSFET, where the MOSFET's channel operates in the reverse direction. This kind of half-bridge control opens a path parallel to the body diode through the MOSFET channel. This is called synchronous rectification.

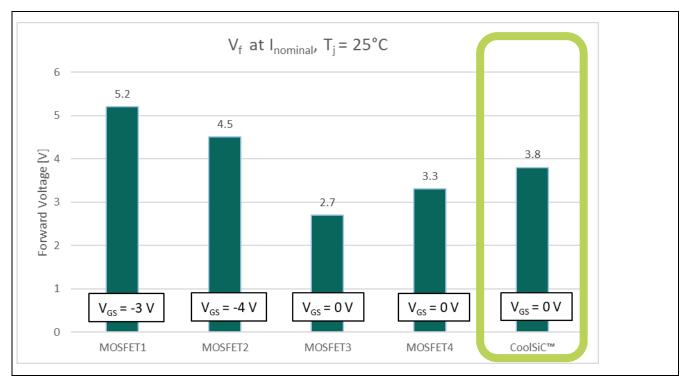

The advantage of this mode of operation is that the voltage drop of the channel is much lower than the forward voltage of the body diode. This reduces the voltage drop from the freewheeling current to a large extent, thereby reducing the conduction losses in the MOSFET. This operation mode is important for SiC MOSFETs because the forward voltage of the body diode is relatively high, as can be seen in Figure 1. To achieve high system efficiency, it is mandatory to avoid, as much as possible, a mode in which only the diode conducts.

Figure 1 Forward voltage of the SiC MOSFET body diode at lowest gate voltage conditions

### 2.2 Enable short dead time for higher efficiency

In half-bridge topologies, the dead time inhibits shoot-through and cross-conduction. It is an important safety feature in any half-bridge application. However, long dead times can lead to low efficiency. During dead time, the current conducts only through the body diode or output power limitation because no energy is converted into load during the dead time. Achieving as short a dead time as possible without shoot-through is essential for high-performing power applications. The most important parameters of a gate driver to help achieve this goal are precise propagation delay matching and precise integrated filters. These are explained in the following sections.

#### 2 SiC MOSFET gate drive requirements and options

### 2.2.1 Precise propagation delay matching

The gate driver parameters for calculating dead time are propagation delay and rise and fall time. As the rise and fall time are mostly insignificant (in single digit nanoseconds range), they are not generally considered. It is, however, different in the case of propagation delay of the control signal from the input to the output of the driver. The difference in propagation delay between any two components, under the same conditions, is called propagation delay matching. To reduce dead time, tight propagation delay matching of the gate driver is mandatory.

The datasheet specifications of EiceDRIVER™ isolated gate drivers include parameter variations over temperature and lifetime. This means that the datasheets consider the worst-case scenario. In real-world operating conditions, propagation delay matching is, typically, much smaller than the maximum value specified in the datasheet.

The EiceDRIVER™ gate drivers listed in Table 2 have extremely tight propagation delay matching. They enable high efficiency by reducing the required dead time.

Table 2 Maximum propagation delay matching

| Gate driver                                | Maximum part-to-part propagation delay |

|--------------------------------------------|----------------------------------------|

| EiceDRIVER™ X3 Compact (1ED31xx)           | 7 ns                                   |

| EiceDRIVER™ F3 (1ED332x)                   | 15 ns                                  |

| EiceDRIVER™ 2L-SRC Compact (1ED32xx)       | 15 ns                                  |

| EiceDRIVER™ X3 Analog/Digital (1ED34/38xx) | 30 ns                                  |

It is important to know that individual combinations of a SiC MOSFET and gate driver must be evaluated carefully for properly dimensioning the dead time. Turn-on and turn-off propagation delays of the power transistor very often differ much more over the operating conditions (e.g., the gate voltage range, drain-source voltage  $V_{\rm ds}$ , junction temperature  $T_{\rm vj}$ , or gate resistance) than over the propagation delay of the gate driver. The parameters of the SiC MOSFET can, thus, dominate the dead time calculation.

### 2.2.2 Precise integrated filters

Filtering of input control signals is a state-of-the-art method to avoid false triggering caused by electrical noise. Two ways of filtering are often used in power electronics:

- RC filters at input terminals

- Combination of a short-time RC filter and a precise integrated filter in the gate driver itself

An external RC filter helps ensure that the voltages on the gate driver IC's input pins stay within the absolute maximum voltage ratings. These ratings are usually specified for a negative voltage of only -0.3 V. There is a high risk that any coupling might violate this rating if an RC filter is not used. The capacitive portion of the filter keeps the voltage within the operating range, while the resistive portion limits the coupled currents that stress the IC pins. Therefore, the best way to design an RC filter is to have a short filter time constant (in the range of a few nanoseconds) and the capacitor close to the IC's terminals. The IC itself should filter larger disturbances.

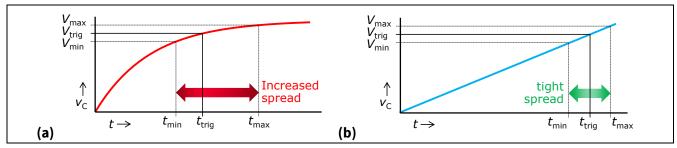

The two filtering methods are investigated here in a case study. The first method suffers from a relatively flat branch of the RC charging curve as shown in the Figure 2 (a). The component tolerances of the filter resistor and filter capacitor have a big influence on the filter time. The graph shows the influence of component

#### 2 SiC MOSFET gate drive requirements and options

tolerances on the filter time tolerance. It can be seen that the minimum to maximum spread,  $t_{max}$  to  $t_{min}$  is not symmetrical with respect to the target value,  $t_{trig}$ .

Figure 2 Filter topologies (a) RC filter (b) Integrated filter with a short-time RC filter

The Figure 2 (b) shows the time behavior of an RC filter with a short filter time combined with a dominant integrated filter. The spread of filter time against the target value is rather symmetric here and tighter than that with only a single RC filter. Therefore, the solution with an integrated filter is superior to the solution.

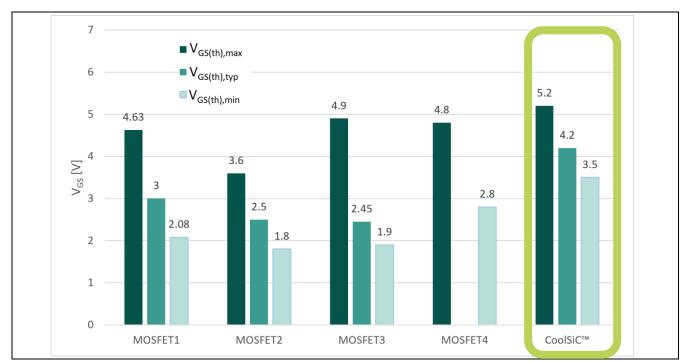

#### 2.3 Negative gate voltage

Figure 3 gives an overview of the gate-source threshold voltage,  $V_{GS(th)}$ , of a few selected SiC MOSFETs in the market. It can be seen that Infineon's CoolSiC<sup>TM</sup> technology offers the highest gate-source threshold voltage levels. The advantage of the high gate-source threshold voltage level is that it can enable CoolSiC<sup>TM</sup> MOSFETs to operate with only unipolar gate voltages. Examples and conditions for operating in that mode are explained in Chapter 4.

Figure 3 Gate-source threshold voltage range of SiC MOSFET devices

The minimum  $V_{GS(th)}$  of SiC MOSFET devices from other manufacturers can be lower than 2 V at 25°C in some cases. There, even a minor ground bouncing can lead to a false and uncontrolled turn-on of the MOSFET at 0 V OFF state voltage. This situation gets more critical if the negative temperature drift of the gate-source voltage

#### 2 SiC MOSFET gate drive requirements and options

threshold is taken into account. A negative turn-off gate voltage can improve this situation and keep the MOSFET in an OFF state even in noisy environments. The level of the negative gate voltage depends on the gate-source threshold voltage, the ratio of the gate-to-drain capacitance, and the gate-to-source capacitance of the MOSFET.

Thus, driver ICs for SiC MOSFETs should, preferably, have the capability of operating with negative gate voltage to provide a safe and stable OFF state condition for the SiC MOSFET.

As long as the absolute maximum ratings of the IC are not exceeded, any EiceDRIVER<sup>TM</sup> isolated and level-shift gate driver IC can be used to drive the SiC MOSFETs. Nevertheless, using driver ICs capable of working with negative gate voltages is recommended. Table 3 shows the maximum ratings of EiceDRIVER<sup>TM</sup> isolated and level-shift gate driver ICs for the maximum output supply voltage range  $V_{VCC2} - V_{VEE2}$ ,  $V_{VCC2} - V_{GND2}$ , and  $V_{VCC} - V_{COM}$  respectively.

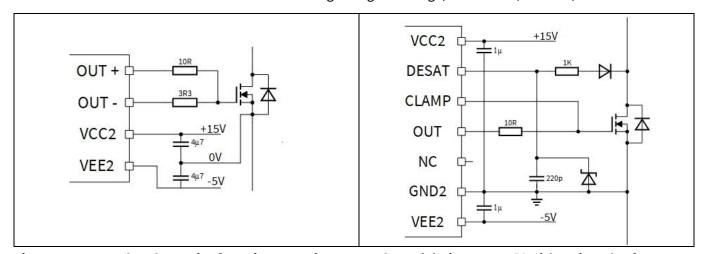

Sample circuits for using gate drivers with bipolar supply voltage are shown in Figure 4. Figure 4 (a) represents an implementation in case the EiceDRIVER™ isolated gate driver IC does not provide specific terminals for negative gate-source voltage, such as the X3 Compact (1ED31xx) devices. Figure 4 (b) depicts the gate drive circuit of a driver IC with dedicated terminals for negative gate voltage, such as F3 (1ED332x) devices.

Figure 4 Sample schematics for using negative gate voltage (a) EiceDRIVER™ with a virtual reference point, (b) EiceDRIVER™ with negative gate voltage capability

The output side voltages of the gate driver can be generated easily with an isolated switched mode power supply (SMPS). The power supply for the high side can also be generated through bootstrapping when only a unipolar voltage is used for the gate drive. However, realizing a bipolar voltage for the gate drive normally requires an SMPS. The principles of such SMPS are discussed in [1] and [3]. However, those examples are designed for gate voltage ranges suitable for IGBTs and thus, cannot be used directly for SiC MOSFETs. It should be noted that considerable displacement currents can flow through the parasitic coupling capacitances of such SMPS transformers. Such currents can have a negative influence on the application's sensing functions. 2ED1323S12P cannot operate with a negative voltage. However, it can drive SiC MOSFETs even when only a unipolar voltage is used while reducing pinout complexity (the VEE2 pin is not required). When using unipolar voltage to drive SiC MOSFETs, using the active Miller clamp from the gate driver is highly recommended.

### 2.4 Wide range of gate voltages

The positive gate-source voltage defines the ON state  $R_{DS(on)}$  of the SiC MOSFET. As Figure 5 shows, Infineon's CoolSiC<sup>TM</sup> MOSFETs achieve their nominal ON state  $R_{DS(on)}$  at a gate voltage of 15 V. This is a big advantage in

#### 2 SiC MOSFET gate drive requirements and options

numerous applications, because no changes need to be made in the positive gate voltage supply design unlike in the case of IGBTs or even conventional silicon MOSFETs.

Other SiC MOSFETs that were reviewed required a relatively high gate voltage, compared to even IGBTs or conventional silicon MOSFETs. A lower gate voltage level is of course possible, but it results in an increase in the steady-state channel resistivity and, therefore, in higher conduction losses. Figure 5 shows the absolute maximum ratings of the gate-source voltage,  $V_{GS}$ , of the selected SiC MOSFETs. The orange bars represent negative gate-source voltage and the green bars represent positive gate-source voltage. The bars in lighter shade depict the recommended gate-source voltage levels as per each device's datasheet. A gate driver IC has to cover the entire range of positive and the negative gate voltages for optimized operation of the SiC MOSFET.

Gate-source voltage range of SiC MOSFETs (dark shade: absolute maximum ratings, light Figure 5 shade: recommended range as per the datasheet)

As seen in Figure 5, the highest recommended gate voltage for MOSFET 3 is 22 V. MOSFET 1 and MOSFET 2 also have a range beyond 19 V. However, CoolSiC<sup>™</sup> can be driven with a total supply voltage range of below V<sub>GS(on)</sub> –  $V_{\rm GS(off)}$  = 20 V and without the necessity of a negative voltage during turn-off. This can be achieved, theoretically, by any EiceDRIVER™ with a maximum supply voltage rating of 20 V. Voltage spikes can easily exceed this maximum rating, even if only for very short durations. Therefore, selecting EiceDRIVER™ isolated or level-shift gate driver ICs with a rating of at least 25 V is recommended for output supply ranges (V<sub>VCC2</sub> - V<sub>VEE2</sub>, V<sub>VCC2</sub> - V<sub>GND2</sub>, or  $V_{VCC}$  -  $V_{COM}$ ) for a reliable gate drive circuit design. Table 3 lists these parameters for the products under discussion.

#### 2 SiC MOSFET gate drive requirements and options

Table 3 Output voltage parameters relevant for driving SiC MOSFETs

| Gate driver                    | Maximum output supply range                                                                                         | Minimum negative gate voltage |  |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|

|                                | $V_{\text{VCC2}}$ - $V_{\text{VEE2}}$ / $V_{\text{VCC2}}$ - $V_{\text{GND2}}$ / $V_{\text{VCC}}$ - $V_{\text{COM}}$ |                               |  |  |

| X3 Compact (1ED312x)           | 40 V                                                                                                                | V <sub>VCC2</sub> – 40 V      |  |  |

| X3 Compact (1ED314x)           | 35 V                                                                                                                | V <sub>VCC2</sub> – 35 V      |  |  |

| F3 (1ED332x)                   | 40 V                                                                                                                | -22 V                         |  |  |

| 2L-SRC Compact (1ED32xx)       | 40 V                                                                                                                | V <sub>VCC2</sub> – 40 V      |  |  |

| X3 Analog/Digital (1ED34/38xx) | 40 V                                                                                                                | -40 V                         |  |  |

| 2ED1323S12P                    | 25 V                                                                                                                | 0 V                           |  |  |

### 2.5 Extended common mode transient immunity(CMTI) capability

SiC MOSFETs are capable of switching extremely fast. This fast switching of voltages causes a common mode noise injection from the output side to the input side of the galvanically isolated gate drivers, requiring a high CMTI robustness rating from the gate driver IC.

EiceDRIVER™ isolated gate driver ICs that use the coreless transformer technology for galvanic isolation between the input and output are very robust against voltage disturbances. As a result, these gate drivers have the best-in-class CMTI performance and rating in the market, reaching up to 300 kV/μs. The current standard IEC 60747-17 for magnetic and capacitive couplers specifies a measurement procedure. It requires CMTI tests with rising and falling edges of the applied voltage slope. This ensures a good comparability between CMTI specifications of various driver ICs.

Table 4 EiceDRIVER™ CMTI capability

| CMTI canability | Device family           |                             |                                       |  |  |  |  |

|-----------------|-------------------------|-----------------------------|---------------------------------------|--|--|--|--|

| CMTI capability | EiceDRIVER™ Comp        | act                         | EiceDRIVER™ Enhanced                  |  |  |  |  |

| 200 V/ns        | X3 Compact<br>(1ED312x) | 2L-SRC Compact<br>(1ED32xx) | X3 Analog (1ED34x1) X3 Digitl (1ED38x |  |  |  |  |

| 300 V/ns        | X3 Compact (1ED314      | 4x)                         | F3 (1ED332x)                          |  |  |  |  |

For level-shift products, CMTI tests are not required because of the different input to output junction isolation (these devices are not galvanically isolated).

### 2.6 Fast DESAT detection and overcurrent protection

SiC MOSFETs do not have a sharp saturation behavior under excessive current conditions. Short circuit current levels can, therefore, easily reach ten times the nominal current rating. Thus, the behavior of SiC MOSFETs during a short circuit condition is unlike that of an IGBT, which undergoes desaturation and the short circuit current is limited to four times the nominal current. The short circuit withstand time of CoolSiC $^{\text{TM}}$  is approximately 2 to 3  $\mu$ s, which is relatively short. Fast detection and a fast shutdown are mandatory for the reliable operation of SiC MOSFETs and a long lifetime. Suitable techniques for overload handling in SiC MOSFETs are a fast DESAT function and overcurrent protection.

The well-known desaturation detection circuit for IGBTs can also be used for SiC MOSFETs if the DESAT circuit is designed to react fast enough. It is based on monitoring the drain-source voltage during the ON state of an IGBT. A leading-edge blanking is needed during turn-on of the IGBT to prevent false triggering of the DESAT by

#### 2 SiC MOSFET gate drive requirements and options

the spike in the collector current caused by the diode's reverse recovery. Further, several parasitic effects of power diodes and the IGBT itself, as well as the layout crosstalk during current commutation, require a so-called DESAT blanking time in the range of a few  $\mu s$ . Such a long blanking time is not acceptable for SiC MOSFET as described earlier. The gate driver for SiC MOSFETs should have the capability to react fast and the circuit should be designed to activate the protection in typically 1  $\mu s$  – 3  $\mu s$  time in case of a short circuit. A well optimized layout is mandatory to detect the short circuit condition safely and to avoid false DESAT triggers through ground bounce or signal cross talk. Refer to the technical description of the driver IC used for further information about adjusting the DESAT components:  $R_{DESAT}$ ,  $C_{DESAT}$ , and  $D_{DESAT}$ .

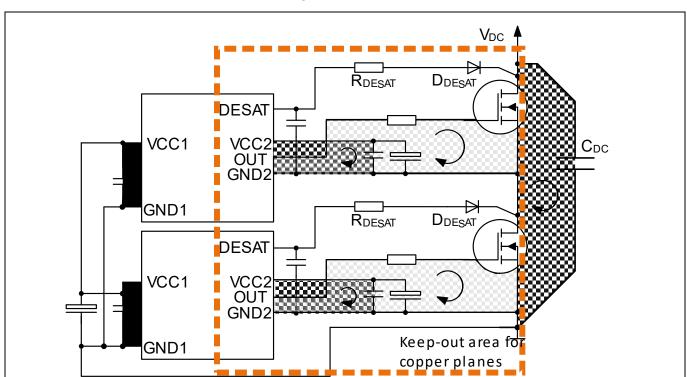

A suitable way to avoid such effects is to apply all rules of a good PCB layout. One of these rules is to optimize for small PCB track loops. This will decouple the gate driver IC's power supplies in the MOSFET gate current paths and in the main current paths that include the DC link, as shown in Figure 6. This prevents parasitic stray inductances that could lead to inductive coupling of switched currents.

Figure 6 Example of a suitable layout for a fast DESAT-detection function

Specific care should be taken to avoid parasitic capacitive coupling. The fast-switching speed of a SiC MOSFET cannot be compared with the switching speed of IGBT. It is, therefore, recommended that the area of the gate drives circuit be kept free of planes that are connected to GND1, GND2, or  $V_{DC}$ . This prevents unnecessary capacitive coupling with high dV/dt. Note, however, that this approach can create a conflict with the cooling demands of the gate driver IC that might require specific copper areas.

The placement of the DESAT diode,  $D_{DESAT}$ , and the resistor,  $R_{DESAT}$ , and the routing of the DESAT sense track should avoid both inductive and capacitive coupling to generate a DESAT signal with minimum interferences and delays.

#### 2 SiC MOSFET gate drive requirements and options

The following gate driver products in the EiceDRIVER™ Enhanced family provide the DESAT function:

- F3 (1ED332x)

- X3 Analog (1ED34xx)

- X3 Digital (1ED38xx)

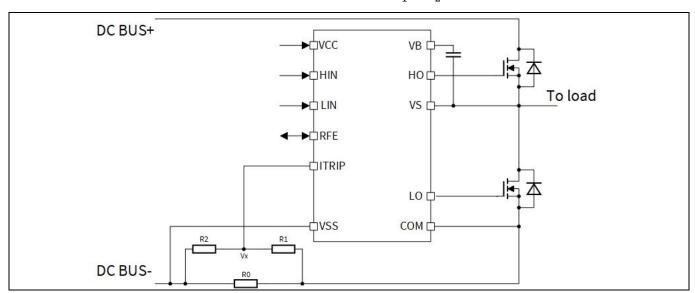

The EiceDRIVER™ SOI gate driver, 2ED1323S12P, uses another protection feature for short circuit events: overcurrent protection (ITRIP input pin). It can sense overcurrent events in the DC bus. When the IC detects an overcurrent event, the outputs are shut down and a fault-enable pin (RFE) is pulled to VSS.

The level of current at which the overcurrent protection is initiated is determined by the resistor network (i.e.,  $R_0$ ,  $R_1$ , and  $R_2$ ) connected to ITRIP as (shown in Figure 7) and the ITRIP threshold,  $V_{th,OCP}$ . The circuit designer will need to determine the maximum allowable level of current in the DC bus and select R<sub>0</sub>, R<sub>1</sub>, and R<sub>2</sub> such that the voltage at node Vx reaches the overcurrent threshold,  $V_{th,OCP}$ , at that current level.

$$V_{th,OCP} = R_0 * I_{DC-} * \frac{R_1}{R_1 + R_2}$$

Figure 7 **Programming overcurrent protection**

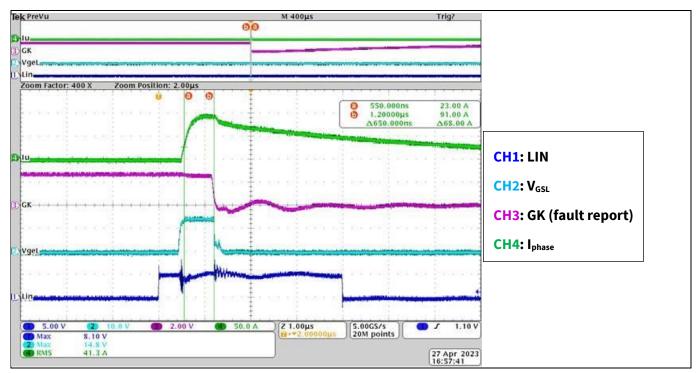

In motor control applications, a typical value for resistor R<sub>0</sub> would be 50 mΩ. This protection has a fast (650 ns) response, as can be seen in the oscilloscope snapshot in Figure 8.

#### 2 SiC MOSFET gate drive requirements and options

Figure 8 ITRIP lab measurement response

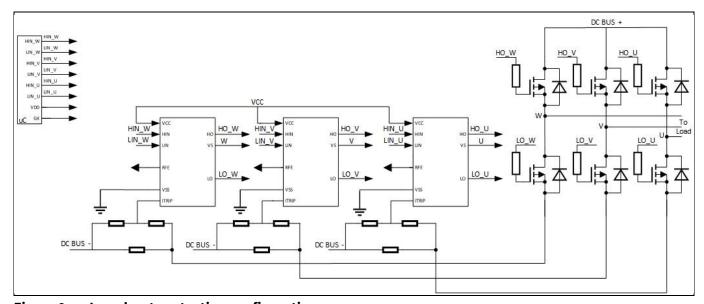

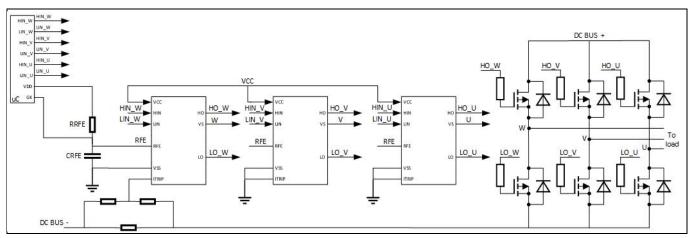

In applications that require more than one device, such as 3-phase circuits, this protection can be implemented in two different ways: leg-shunt protection or single-shunt protection.

The leg-shunt protection configuration, shown in Figure 9, implies overcurrent detection for every leg. This implementation requires a network of resistors for every leg, and every single device can, independently from the others gate drivers, shut down its own output when a failure occurs.

Figure 9 Leg-shunt protection configuration

#### 2 SiC MOSFET gate drive requirements and options

On the other hand, the single-shunt protection configuration reduces the number of external resistors relying on the RFE pin and the daisy chain configuration.

The gate drivers can be daisy chained, as shown in Figure 10. The three fault-enable RFE pins are connected together. ITRIP sensing is only used on the first IC and the other two ITRIP pins are disabled by tying them to VSS. The programmable fault clear timing components,  $R_{\text{RFE}}$  and  $C_{\text{RFE}}$ , are populated only once for the RFE pin. When a fault occurs, either from ITRIP or UVLO, or an external command, all the three HVICs are disabled by pulling the daisy-chained RFE pin low to VSS.

Figure 10 Single-shunt and daisy chain configuration

The overcurrent protection feature is implemented in the EiceDRIVER™ level-shift SOI device, 2ED1323S12P.

### 2.7 Active Miller clamping

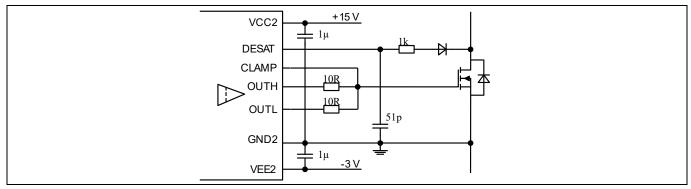

Active Miller clamping is a well-known technique to avoid parasitic dV/dt induced turn-on. This function uses a CLAMP terminal directly connected to the power transistor's gate terminal, as shown in Figure 11. It pulls down the gate during OFF state. The OFF state condition is monitored by sensing the gate voltage with the same terminal. The clamp function is activated as soon as the gate voltage drops below a specified threshold, which is typically  $V_{\text{CLAMP}} = V_{\text{VEE2}} + 2 \text{ V or } V_{\text{COM}} + 2 \text{ V}$ .

Figure 11 Schematic example for implementation of the active Miller clamp function

# Advanced gate drive options for silicon carbide (SiC) MOSFETs using EiceDRIVER™

#### 2 SiC MOSFET gate drive requirements and options

The monitoring comparator threshold,  $V_{\text{CLAMP}}$ , is referenced to the lowest available voltage inside the IC. The lowest voltage occurs at terminal VEE2 of the EiceDRIVER<sup>TM</sup> isolated gate driver family or at the terminal COM of the family and 2ED1323S12P.

EiceDRIVER™ Compact isolated gate driver ICs with active Miller clamp are:

X3 Compact: 1ED3122MC12H, 1ED3127MU12F

2L-SRC Compact: 1ED3251MC12H

Products from the EiceDRIVER™ Enhanced isolated gate driver IC families that offer active Miller clamp in combination with a DESAT function are:

- F3 (1ED332x)

- X3 Analog (1ED34x1)

- X3 Digital (1ED38x0)

Gate drivers 1ED3491 from the X3 Analog and 1ED3890 from the X3 Digital family offer a Miller clamp driver instead of an internal Miller clamp. The miller clamp driver drives an external MOSFET that can be placed very close to the gate and source terminals of the SiC MOSFET on the PCB. As a result, the active Miller clamp function improves significantly in the application, especially, when the gate driver is placed at some distance from the SiC MOSFET on the PCB.

Lastly, the 2ED1323S12P level-shift gate driver provides both an active Miller clamp function and overcurrent (ITRIP) protection.

These gate driver ICs with integrated active Miller clamp function are a good choice in applications where switching involves high dV/dt and in applications where only unipolar voltage is used for the gate drive.

#### 3 Power dissipation

### 3 Power dissipation

#### 3.1 Isolated gate driver power dissipation

Calculating the power dissipated of a gate driver IC is important to prevent very high operating conditions. This section describes how to calculate the power dissipated by gate driver ICs in general.

Regarding EiceDRIVER™ products, the main contributors for power dissipation are:

- The input side operating supply current

- The input side input bias currents

- The output side quiescent current

- The output side gate charge losses

These individual values can be calculated through the following equations:

1. Measure the operating current,  $I_{q,in}$ , to get the maximum switching frequency of the application. The power transistors should not be connected.

$$P_{\rm d,VCC1} = I_{\rm q,in} \cdot V_{\rm VCC1,max} \tag{1}$$

The input bias currents of the logic input terminals contribute with:

$$P_{\text{d.bias}} = n \cdot I_{\text{IN}} \cdot V_{\text{VCC1.max}}$$

(2)

Here *n* is the number of input terminals of the gate driver IC. This portion of the dissipated power is usually very small compared to the portion contributed by the supply voltage.

2. The output side section continuously dissipates power with respect to the quiescent current,  $I_{q,out}$ . This is given by:

$$P_{\text{d,VCC2}} = I_{\text{d,out}} \cdot (V_{\text{VCC2}} - V_{\text{VEE2}})$$

(3)

The output side quiescent current value should also be measured at the maximum switching frequency without connecting the power transistors.

- 3. Calculate the losses of the output section through the total gate charge of the power transistor,  $Q_{\text{Gtot}}$ , the supply voltage  $V_{\text{VCC2}} V_{\text{VEE2}}$ , the switching frequency  $f_{\text{S}}$ , and the external gate resistor. Different cases for turn-on and turn-off have to be considered, because many designs use different resistors for turn-on and turn-off. This leads to a specific distribution of losses that depends on:

- The external gate resistors R<sub>Gon,ext</sub> and R<sub>Goff,ext</sub>

- o The internal resistances of the output section of the gate driver, R<sub>Gon,IC</sub> and R<sub>Goff,IC</sub>

- The internal gate resistance of the SiC MOSFET, R<sub>G,int</sub>

$$P_{\rm d,on} = \frac{1}{2} Q_{\rm G,tot} \cdot (V_{\rm VCC2} - V_{\rm VEE2}) \cdot f_{\rm S} \cdot \frac{R_{\rm Gon,IC}}{R_{\rm Gon,ext} + R_{\rm Gon,IC} + R_{\rm G,int}} \quad , \text{for turn-on}$$

#### 3 Power dissipation

$$P_{\rm d,off} = \frac{1}{2} Q_{\rm G,tot} \cdot (V_{\rm VCC2} - V_{\rm VEE2}) \cdot f_{\rm S} \cdot \frac{R_{\rm Goff,IC}}{R_{\rm Goff,ext} + R_{\rm Goff,IC} + R_{\rm G,int}} \quad , \text{for turn-off}$$

(5)

The sum of  $P_{d,on}$  and  $P_{d,off}$  is the output stage loss due to the gate drive.

4. The final power dissipation during operation at highest switching frequency is then the sum of both the contributions:

$$P_d = P_{d,VCC1} + P_{d,bias} + P_{d,VCC2} + P_{d,on} + P_{d,off} + P_{d,add}$$

(6)

5. Some gate drivers may have additional portions of dissipated power or a different partitioning of losses, such as the DESAT function or the active Miller clamping. This portion is represented by the term  $P_{d,add}$  in equation (6). It is important to analyze the individual effect of each of these functions with respect to power dissipation.

The datasheet shows specific layouts for which the given thermal resistance junction to ambient ( $R_{th(j-a)}$ ) is valid. Note that different layouts may lead to different thermal resistances. Therefore, it is always a good engineering practice to additionally examine the package temperature through experiments.

#### 3.2 Level-shift gate driver power dissipation

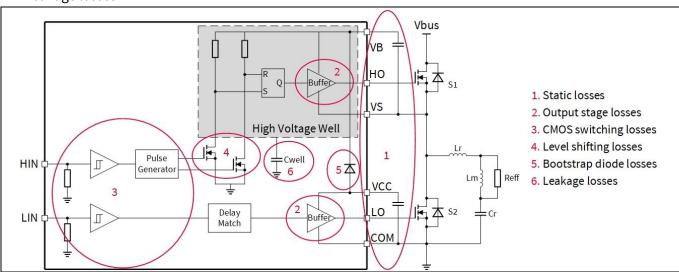

In level-shift products, the power dissipated by the driver IC is a combination of several sources such as:

- Static losses

- Output stage losses

- CMOS losses

- Level-shift losses

- Bootstrap diode losses

- Leakage losses

Figure 12 Different power losses within the level-shift gate driver

The output stage is the major contributor to the power dissipated by the gate driver IC. The external gate resistors also contribute to the power dissipated by the gate driver IC. The bigger the external gate resistor, the smaller the power dissipated by the gate driver.

#### 3 Power dissipation

Within the gate driver IC, the different losses include:

1. Static losses are calculated for a given supply voltage and quiescent/bootstrap charging currents:

Static losses in the low side =

$$V_{\rm CC} \times I_{\rm OCC}$$

(7)

Static losses in the high side =

$$V_{\rm BS} \times I_{\rm QBS}$$

(8)

Static losses at input stage =

$$\frac{1}{2} \times \frac{V_{\text{CC}} \times V_{\text{CC}}}{R_{\text{pullup}}}$$

(9)

2. Output stage losses are calculated through the total gate charge of the SiC MOSFET. It drives  $Q_{G,tot}$ , the supply voltage  $V_{VCC}$ , the switching frequency  $f_s$ , the external gate resistor  $R_{Gon,ext}$  and  $R_{Goff,ext}$ , and the internal resistor of the SiC MOSFET  $R_{G,int}$ . Different cases of turn-on and turn-off must be considered, because many designs use different resistors for turn-on and turn-off. This leads to a specific distribution of losses from the output section:

$$Turn \ on \ losses: P_{d,on} = \frac{1}{2} \times Q_{G,tot} \times V_{CC} \times f_s \times \frac{R_{Gon,IC}}{R_{Gon,ext} + R_{Gon,IC} + R_{G,int}}$$

(10)

$$Turn \ off \ losses: P_{d,off} = \frac{1}{2} \times Q_{G,tot} \times V_{CC} \times f_s \times \frac{R_{Gon,IC}}{R_{Gon,ext} + R_{Gon,IC} + R_{G,int}}$$

(11)

3. CMOS losses are calculated for a given switching frequency and supply voltage:

$$CMOS \ losses = Q_{COMS} \times V_{CC} \times f_{S}$$

(12)

Junction capacitance switching losses =

$$\frac{1}{2} \times C_{\rm J} \times V_{\rm BUS}^2 \times f_{\rm s}$$

(13)

4. Level-shift losses are calculated for a given switching frequency and supply voltages:

Loss per level shifter

$$(ON) = (V_{BUS} + V_{CC}) \times I_{LSON} \times t_{on} \times f_{s}$$

Loss per level shifter (OFF) =

$$(V_{BUS} + V_{CC}) \times I_{LSOFF} \times t_{off} \times f_{s}$$

(15)

5. Bootstrap diode losses are calculated for given switching frequency and supply voltages:

Dynamic losses in boot diode =

$$EB \times f_s \times 2 \times \frac{I_{QBS} + (Q_{G,tot} \times f_s)}{10^{-3} \times \frac{V_{BUS}}{400}}$$

(16)

$$Static\ losses\ in\ boot\ diode = \frac{\left(V_{\rm TH} + 2 \times \left[I_{\rm QBS} + \left(Q_{\rm G,tot} \times f_{\rm s}\right)\right] \times R_{\rm D}\right) \times 2 \times \left[I_{\rm QBS} + \left(Q_{\rm G,tot} \times f_{\rm s}\right)\right]}{2} \quad \textbf{(17)}$$

6. Leakage losses are calculated for a given switching frequency and supply voltages:

$$Leakage\ loss = I_{LEAK} \times V_{BUS}$$

(10)

Similar to the case of the isolated gate driver, any other contribution related to specific functions such as DESAT or active Miller clamp should be analyzed individually.

(14)

### Advanced gate drive options for silicon carbide (SiC) MOSFETs using EiceDRIVER™

4 Considerations for single transistor topologies and applications with low dV/dt stress during an OFF state

#### Considerations for single transistor topologies and 4 applications with low dV/dt stress during an OFF state

This chapter explains special conditions for SiC MOSFET gate drives in single-transistor topologies. Popular topologies using a single SiC MOSFET are boost, buck, or flyback converters. The low-side referenced switch, e.g., of a boost topology, does not necessarily require an isolated gate driver. However, the non-isolated drivers can often suffer from heavy ground bouncing. This can lead to a latch-up of the driver IC or to additional switching losses due to stray inductances that hinder a proper switching process. Isolated gate drivers, on the other hand, do not suffer from ground bouncing due to the large offset voltage range that provides extra gate drive performance, particularly in single transistor topologies. New level-shift products are more reliable with respect to ground bouncing (transient negative VS). It is, thus, better to do a case-by-case evaluation of the application conditions is.

A parasitic turn-on of a MOSFET that can be a challenge for half-bridge configurations is not a problem in single transistor topologies. Therefore, only a unipolar gate voltage is often sufficient to control the SiC MOSFET. CoolSiC™ MOSFETs have special benefits because the gate-source threshold voltage, v<sub>GS,th</sub>, is high (as discussed in Section 2.3). Therefore, these devices are very robust against turn-on triggered by noise. This simplifies the gate drive circuits to a large extent because a unipolar non-isolated power supply is sufficient e.g., for boost or flyback converters.

A unipolar gate driver power supply can be used in drive applications where the switching speed is limited. The dV/dt is often limited to 5 V/ns in such applications due to motor lifetime considerations. Infineon's CoolSiC™ transistors offer a relatively high gate-source threshold voltage, as shown in Figure 3. Therefore, the parasitic turn-on triggered by dV/dt is very unlikely even in half-bridge configurations. Additionally, applications using only a positive gate voltage can be supported by active Miller clamping, explained in Section 2.7.

# Advanced gate drive options for silicon carbide (SiC) MOSFETs using EiceDRIVER™

**5 Summary**

### 5 Summary

SiC MOSFETs offer several advantages over traditional silicon-based systems, including higher efficiency and power density. Gate drivers are key components in any power electronic system and to take full advantage of the SiC MOSFETs, choosing the right gate driver is crucial for any design. EiceDRIVER™ gate drivers from Infineon offer all the features required for driving SiC MOSFETs; such as high gate currents, active Miller clamp, fast DESAT protection, excellent part-to-part matching of propagation delay, and best-in-class CMTI performance. EiceDRIVER™ gate drivers when used with CoolSiC™ MOSFETs from Infineon enable the system to provide the best possible performance.

# Advanced gate drive options for silicon carbide (SiC) MOSFETs using EiceDRIVER™

Application note

References

#### References

- [1] Infineon Technologies: EVAL-1ED3142MU12F-SIC, Evaluation board description, 2023.

- [2] Infineon Technologies: EVAL-1ED3124Mx12H, Evaluation board description, 2019.

- [3] Infineon Technologies: EVAL-1ED3122Mx12H, Evaluation board description, 2019.

- [4] Infineon Technologies: EVAL-1ED3121Mx12H, Evaluation board description, 2019.

- [5] Infineon Technologies: EVAL-1ED32xxMC12H, Evaluation board description, 2021.

- [6] Infineon Technologies: EVAL-1ED32xxMC12H, Evaluation board description, 2021.

- [7] Infineon Technologies: EVAL-1ED3321MC12N, Evaluation board description, 2022.

- [8] Infineon Technologies: EVAL-1ED3890Mx12M, Evaluation board description, 2021.

- [9] Infineon Technologies: EVAL-1ED38x0DCT, Evaluation board description, 2021.

- [10] Infineon Technologies: EVAL-1ED3491Mx12M, Evaluation board description, 2020.

- [11] Infineon Technologies: Advantages of Infineon's high-voltage gate driver ICs (HVICSs) based on its silicon-on-insulator (SOI) technology, Silicon-on-insulator level-shift gate driver description, 2019.

# Advanced gate drive options for silicon carbide (SiC) MOSFETs using EiceDRIVER $^{\mbox{\tiny MOSFETS}}$

Application **note**Revision history

### **Revision history**

| Document revision | Date       | Description of changes                                   |

|-------------------|------------|----------------------------------------------------------|

| V1.0              | 2017-04-05 | Initial release                                          |

| V1.1              | 2018-06-24 | Update product range for 1EDC-family and 1EDS-SRC family |

| V1.2              | 2024-04-22 | Updated with new parts                                   |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2024-04-12 Published by

Infineon Technologies AG 81726 Munich, Germany

© 2024 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference AN2017-04

#### Important notice

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### Narnings

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.