### HYPERBUS™ interface, multi-chip package, 1.8 V/3.0 V

### **Features**

- SEMPER™ Flash and HYPERRAM™ 2.0 with HYPERBUS™ interface in multi-chip package (MCP)

- 1.8 V, 512Mb SEMPER™ Flash and 64Mb HYPERRAM™ 2.0 (S76HS512TC0)

- 3.0 V, 512Mb SEMPER™ Flash and 64Mb HYPERRAM™ 2.0 (S76HL512TC0)

- FBGA 24-ball, 8 × 8 × 1.2 mm packages

- HYPERBUS™ interface

- 1.8 V I/O (S76HS-TC0)

- 3.0 V I/O (S76HL-TC0)

- Chip select (CS#)

- 8-bit data bus (DQ[7:0])

- Data strobe (DS/RWDS)

- Bidirectional DS/mask

- Output at the start of all transactions to indicate refresh latency

- Output during read transactions as read DS

- Input during write transactions as write data mask (HYPERRAM™ only)

- · Optional signals

- INT# output to generate external interrupt

- Busy to ready transition

- RSTO# output to generate system level power-on-reset (POR)

- User configurable RSTO# LOW period

- · High-performance

- DDR

- Two data transfers per clock

- Up to 200 MHz clock rate (400-MBps) at 1.8  $VV_{CC}$

- Up to 166 MHz clock rate (333-MBps) at 3.0 V V<sub>CC</sub>

## HYPERBUS™ interface, multi-chip package, 1.8 V/3.0 V

Table of contents

### Table of contents

| Features                                                  | 1  |

|-----------------------------------------------------------|----|

| Table of contents                                         | 2  |

| 1 General description                                     | 3  |

| 1.1 HYPERBUS™ MCP family with SEMPER™ Flash and HYPERRAM™ |    |

| 2 HYPERBUS™ MCP signal description                        | 4  |

| 3 HYPERBUS™ MCP block diagram                             |    |

| 4 Physical interface                                      |    |

| 4.1 HYPERBUS™ MCP — FBGA 24-ball, 5 × 5 footprint         |    |

| 5 Electrical specifications                               |    |

| 5.1 Absolute maximum ratings                              | 8  |

| 5.2 DC characteristics                                    | 8  |

| 5.3 Capacitance characteristics                           | 11 |

| 5.4 Thermal resistance                                    |    |

| 6 Package diagram                                         | 12 |

| 7 Ordering information                                    | 13 |

| 7.1 Ordering code definition                              |    |

| 7.2 Valid combinations — Standard                         |    |

| 7.3 Valid combinations — Automotive grade / AEC-Q100      | 14 |

| Revision history                                          |    |

|                                                           |    |

2022-09-21

infineon

General description

### 1 General description

This supplementary datasheet provides MCP device related information for HYPERBUS™ MCP family, incorporating both SEMPER™ Flash and HYPERRAM™ with HYPERBUS™ interface memories. The document describes how the features, operation, and ordering options of the related memories have been enhanced or changed from the standard memory devices incorporated in the MCP. The information contained in this document modifies any information on the same topics established by the documents listed in **Table 1**, and should be used in conjunction with those documents. This document may also contain information that was not previously covered by the listed documents. The information is intended for hardware system designers and software developers of applications, operating systems, or tools.

Table 1 Affected documents/related documents

| Title                                                                                                                           | Infineon publication number |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| S26HS256T, S26HS512T, S26HS01GT, S26HL256T, S26HL512T, S26HL01GT 256Mb/512Mb/1Gb SEMPER™ Flash HYPERBUS™ interface, 1.8 V/3.0 V | 002-12337                   |

| S27KL0642, S27KS0642 64Mb HYPERRAM™ self-refresh DRAM (PSRAM)<br>HYPERBUS™ interface, 1.8 V/3.0 V                               | 002-24692                   |

### 1.1 HYPERBUS™ MCP family with SEMPER™ Flash and HYPERRAM™

For systems needing both Flash and self-refresh DRAM, the HYPERBUS™ product family includes MCP devices that combine SEMPER™ Flash and HYPERRAM™ in single package. A HYPERBUS™ MCP reduces board space and printed circuit board (PCB) signal routing congestion while also maintaining or improving signal integrity over separately packaged memory configurations.

The HYPERBUS™ MCP family offers 1.8 V/3.0 V interface SEMPER™ Flash densities of 512Mb (64MB) in combination with HYPERRAM™ 64Mb (8MB).

The SEMPER™ Flash default configuration is HYPERBUS™ interface with configuration bit INTFTP = 1.

This supplement datasheet addresses only the MCP related differences from the HYPERBUS™ specification and the individual SEMPER™ Flash and HYPERRAM™ datasheets. For other information related to the individual memories in the MCP, refer to the SEMPER™ Flash, and HYPERRAM™ datasheets with HYPERBUS™ interface.

HYPERBUS™ interface, multi-chip package, 1.8 V/3.0 V

infineon

HYPERBUS™ MCP signal description

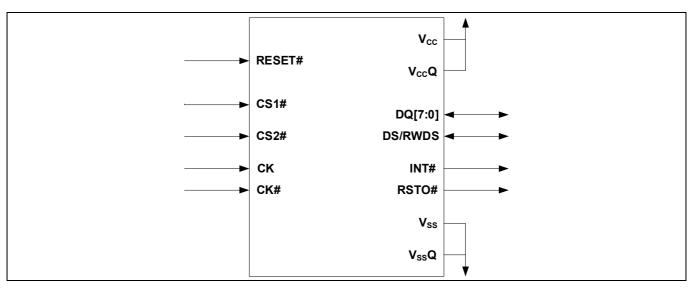

# 2 HYPERBUS™ MCP signal description

Figure 1 HYPERBUS™ MCP signal diagram

HYPERBUS™ MCP signal description

| Table 2 | Signal des | scription |

|---------|------------|-----------|

|---------|------------|-----------|

| Symbol            | Туре                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS1#              | Input                  | Chip select 1. Chip select for the SEMPER™ Flash memory. HYPERBUS™ transactions are initiated with a HIGH-to-LOW transition. HYPERBUS™ transactions are terminated with a LOW- to-HIGH transition.                                                                                                                                                                                                                                                                                                              |

| CS2#              | Input                  | <b>Chip select 2.</b> Chip select for the HYPERRAM™ memory. HYPERBUS™ transactions are initiated with a HIGH-to-LOW transition. HYPERBUS™ transactions are terminated with a LOW-to-HIGH transition.                                                                                                                                                                                                                                                                                                            |

| CK                | Input                  | <b>Single-ended clock.</b> Command-address/data information is input or output with respect to the edges of the CK.                                                                                                                                                                                                                                                                                                                                                                                             |

| CK#               | Input                  | <b>Differential clock</b> . Command-address/data information is input or output with respect to the crossing edges of the CK/CK# pair (Optional).                                                                                                                                                                                                                                                                                                                                                               |

| DS / RWDS         | Input /<br>Output      | Read data strobe (DS). DS is used for SEMPER™ Flash data read operations only and indicates output data valid for the HYPERBUS™ interface. During a read transaction, while CS# is LOW, DS toggles to synchronize the data output until CS# goes HIGH. Output data during read transactions is edge-aligned with DS.  Read-write data strobe (RWDS): Output data during HYPERRAM™ read transactions is edge-aligned with RWDS. RWDS is an input during write transactions to function as a HYPERRAM™ data mask. |

| DQ[7:0]           | Input /<br>Output      | <b>Data input/output.</b> Command-address/data information is transferred on these DQs during read and write transactions.                                                                                                                                                                                                                                                                                                                                                                                      |

| INT#              | Output<br>(open drain) | <b>INT output (optional).</b> When LOW, the SEMPER™ Flash device is indicating that an internal event has occurred. This signal is intended to be used as a system-level interrupt for the device to indicate that an on-chip event has occurred. INT# is an open-drain output.                                                                                                                                                                                                                                 |

| RESET#            | Input                  | Hardware RESET (optional). When LOW, the SEMPER™ Flash and HYPERFLASH™ memory's will self-initialize and return to the idle state.  DS/RWDS and DQ[7:0] is placed into the High-Z state when RESET# is LOW. RESET# includes a weak pull-up; if RESET# is left unconnected, it will be pulled up to the HIGH state.                                                                                                                                                                                              |

| RSTO#             | Output<br>(open drain) | RSTO# output (optional). RSTO# is an open-drain output used to indicate when a POR is occurring within the SEMPER™ Flash memory and can be used as a system-level reset signal. Upon completion of the internal POR, the RSTO# signal will transition from LOW to HIGH-Z after a user-defined timeout period has elapsed. Upon transition to the HIGH-Z state, the external pull-up resistance will pull RSTO# HIGH and the device immediately is placed into the IDLE state.                                   |

| V <sub>CC</sub>   | Power<br>supply        | Core power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CC</sub> Q | Power supply           | Input/output power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>SS</sub>   | Power<br>supply        | Core ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>SS</sub> Q | Power<br>supply        | Input/output ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

HYPERBUS™ MCP block diagram

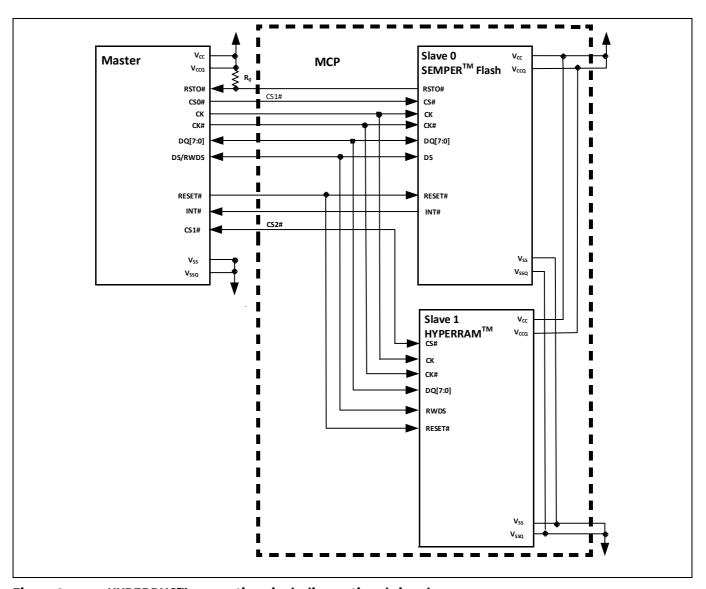

## 3 HYPERBUS™ MCP block diagram

Figure 2 HYPERBUS™ connections including optional signals

infineon

Physical interface

## 4 Physical interface

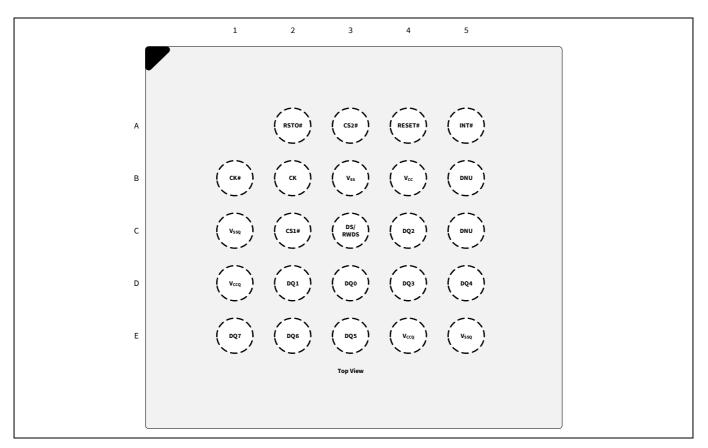

## 4.1 HYPERBUS™ MCP — FBGA 24-ball, 5 × 5 footprint

Figure 3 24-ball FBGA, 8 × 8 mm, 5 × 5 ball footprint (top view)

#### Notes

1. C2 and A3 are chip select (CS#) signals 1 and 2 used for SEMPER™ Flash and HYPERRAM™ devices respectively.

2.  $V_{SS}$  and  $V_{SS}Q$  are internally connected.

infineon

**Electrical specifications**

## 5 Electrical specifications

The following section describes the device dependent aspects of electrical specifications.

### 5.1 Absolute maximum ratings

Ambient temperature with power applied: -65°C to +115°C.

### **5.2 DC** characteristics

Only one memory may have its Chip Select active (LOW) at any point in time. For each condition below, refer to the SEMPER™ Flash and HYPERRAM™ datasheets for the most accurate information:

- Active core read or write current will be that of the selected device plus the standby current of the non-selected device. However, the added standby current is generally not significant because it is less than 300 μA.

- Active I/O read current will be that of the selected device.

- Active clock stop current will be that of the selected device plus the standby current of the non-selected device. However, the added standby current is generally not significant because it is less than 300 µA.

- Program or erase current will be that of the SEMPER™ Flash device. Note however, that program and erase operations are long-time-frame events that extend beyond the duration of a SEMPER™ Flash Chip Select period. Thus, if the HYPERRAM™ is selected for read or write during an on going SEMPER™ Flash program or erase operation, the active current will be the sum of the SEMPER™ Flash program or erase operation and the HYPERRAM™ read or write current.

- Standby current, when neither memory is selected and no embedded flash operation is in progress, is the sum of the memory standby currents.

- Deep power down (DPD) current is the sum of the memory DPD currents.

- POR current is the sum of the memory standby currents.

- Input leakage current is the sum of the memory input leakage currents.

For reference purpose, **Table 3** aids in the estimation of the current consumption in these operating conditions. However, see the SEMPER™ Flash and HYPERRAM™ datasheets for the most accurate information.

**Electrical specifications**

Table 3 3.0 V DC characteristics (CMOS compatible)

| Parameter            | Description                                                          | Test conditions                                                    | Min | <b>Typ</b> <sup>[6]</sup> | Max     | Unit |  |

|----------------------|----------------------------------------------------------------------|--------------------------------------------------------------------|-----|---------------------------|---------|------|--|

|                      | Input leakage current<br>(RESET# HIGH)                               | $V_{IN} = V_{SS}$ to $V_{CC}$ ,<br>$V_{CC} = V_{CC}$ max           | -   | -                         | ±3.1    |      |  |

| <u>լ</u> լ           | Input leakage current (RESET# LOW)                                   | $V_{IN} = V_{SS}$ to $V_{CC}$ ,<br>$V_{CC} = V_{CC}$ max           | -   | -                         | +18.0   | μΑ   |  |

| I <sub>LO</sub>      | Output leakage current                                               | $V_{OUT} = V_{SS}$ to $V_{CC}$ ,<br>$V_{CC} = V_{CC}$ max          | -   | -                         | ±3.1    |      |  |

| 1                    | V <sub>CC</sub> active read current -<br>SEMPER™ Flash reading (core | CS# = V <sub>IL</sub> , @ 166 MHz,<br>V <sub>CC</sub> = 3.60 V     | -   | 156                       | 173     |      |  |

| I <sub>CC1HF</sub>   | current only, I/O switching current is not included)                 | $CS# = V_{IL}$ , @ 200 MHz,<br>$V_{CC} = 2.00 V$                   | -   | 156                       | 173     |      |  |

| 1                    | V <sub>CC</sub> active read current -                                | CS# = V <sub>IL</sub> , @ 166 MHz,<br>V <sub>CC</sub> = 3.60 V     | -   | 15                        | 28      |      |  |

| I <sub>CC1HR</sub>   | HYPERRAM™ reading                                                    | CS# = V <sub>IL</sub> , @ 200 MHz,<br>V <sub>CC</sub> = 2.00 V     | -   | 15                        | 25      |      |  |

| . V                  | V <sub>CC</sub> active write current -                               | CS# = V <sub>IL</sub> , @ 166 MHz,<br>V <sub>CC</sub> = 3.60 V     | -   | 15                        | 28      |      |  |

| I <sub>CC2HR</sub>   | HYPERRAM™ writing                                                    | $CS# = V_{IL}$ , @ 200 MHz,<br>$V_{CC} = 2.00 V$                   | -   | 15                        | 25      | m 1  |  |

| 1                    | V <sub>CC</sub> active program / erase<br>current - SEMPER™ Flash    | CS# = V <sub>IL</sub> , @ 166 MHz,<br>V <sub>CC</sub> = 3.60 V     | -   | 65                        | 92      | - mA |  |

| I <sub>CC1HFHR</sub> | embedded operation plus<br>HYPERRAM™ reading <sup>[4]</sup>          | CS# = V <sub>IL</sub> , @ 200 MHz,<br>V <sub>CC</sub> = 2.00 V     | -   | 65                        | 91      |      |  |

| 1                    | V <sub>CC</sub> active write current -<br>SEMPER™ Flash embedded     | CS# = V <sub>IL</sub> , @ 100 MHz,<br>V <sub>CC</sub> = 3.60 V     | -   | 75                        | 135     | -    |  |

| I <sub>CC2HFHR</sub> | operation plus HYPERRAM™<br>writing <sup>[4]</sup>                   | CS# = V <sub>IL</sub> , @ 166 MHz,<br>V <sub>CC</sub> = 2.00 V     | -   | 75                        | 160     | -    |  |

| I <sub>CC3P</sub>    | V <sub>CC</sub> active program current <sup>[3,4]</sup> (512T/01GT)  | V <sub>CC</sub> = V <sub>CC</sub> max                              | -   | 50                        | 55/66   |      |  |

| I <sub>CC3E</sub>    | V <sub>CC</sub> active erase current <sup>[3, 4]</sup> (512T/01GT)   | V <sub>CC</sub> = V <sub>CC</sub> max                              | -   | 50                        | 55/66   |      |  |

|                      | V <sub>CC</sub> standby current                                      | CS#, RESET# = V <sub>CC</sub> ,<br>V <sub>CC</sub> = 2.00 V, 85°C  | -   | 91                        | 333/333 |      |  |

|                      | (512T/01GT)                                                          | CS#, RESET# = V <sub>CC</sub> ,<br>V <sub>CC</sub> = 2.00 V, 105°C | -   | 91                        | 518/550 | 4    |  |

| I <sub>CC4I</sub>    | V <sub>CC</sub> standby current                                      | CS#, RESET# = V <sub>CC</sub> ,<br>V <sub>CC</sub> = 3.60 V, 85°C  | -   | 104                       | 376/376 | μΑ   |  |

|                      | (512T/01GT)                                                          | CS#, RESET# = V <sub>CC</sub> ,<br>V <sub>CC</sub> = 3.60 V, 105°C | -   | 104                       | 548/548 |      |  |

### **Notes**

- 3. I<sub>CC</sub> active while embedded algorithm (EA) is in progress.

- 4. Not 100% tested.

- 5. Active Clock Stop mode enables the lower power mode when the CK signals remain stable for  $t_{ACC}$  + 30 ns.

- 6. Typical  $I_{CC}$  values are measured at  $t_{AI}$  = 25°C and  $V_{CC}$  =  $V_{CC}Q$  = 1.8 V/3.0 V (not applicable to  $I_{DPD}$  for 85°C and 105°C).

- 7. Current specification includes both the SEMPER™ Flash and HYPERRAM™ die current consumption per the mode of operation of each die.

**Electrical specifications**

3.0 V DC characteristics (CMOS compatible) (Continued) Table 3

| Parameter        | Description                                     | Test conditions                                                                                                  | Min | <b>Typ</b> <sup>[6]</sup> | Max   | Unit |

|------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|---------------------------|-------|------|

| I <sub>CC6</sub> | Active clock Stop mode <sup>[5]</sup>           | $V_{IH} = V_{CC}, V_{IL} = V_{SS}, V_{CC} = 2.00 \text{ V}/3.6 \text{ V}, 85^{\circ}\text{C}$                    |     | 5                         | 8     |      |

|                  | Active clock Stop mode-                         | V <sub>IH</sub> = V <sub>CC</sub> , V <sub>IL</sub> = V <sub>SS</sub> ,<br>V <sub>CC</sub> = 2.00 V/3.6 V, 105°C | 1   | 8                         | 12    | mA   |

| I <sub>CC7</sub> | V <sub>CC</sub> current during power-up (POR)   | CS# = X,<br>V <sub>CC</sub> = V <sub>CC</sub> max                                                                | 1   | _                         | 115   |      |

|                  |                                                 | CS#, RESET#,<br>V <sub>CC</sub> = 2.0 V, 85°C                                                                    | 1   | _                         | 28/34 |      |

| I <sub>DPD</sub> | DPD current<br>SEMPER™ Flash + HYPERRAM™        | CS#, RESET#,<br>V <sub>CC</sub> = 2.0 V, 105°C                                                                   | 1   | _                         | 30/58 |      |

|                  | in DPD (512T / 01GT)                            | CS#, RESET#,<br>V <sub>CC</sub> = 3.6 V, 85°C                                                                    | -   | _                         | 30/36 |      |

|                  |                                                 | CS#, RESET#,<br>V <sub>CC</sub> = 3.6 V, 105°C                                                                   | -   | _                         | 33/61 |      |

|                  | Hybrid sleep current<br>HYPERRAM™ SEMPER™ Flash | CS# = V <sub>CC</sub> ,<br>V <sub>CC</sub> = 2.0 V;<br>Full array                                                | 1   | 27                        | 218   |      |

|                  | in DPD<br>(-40°C to +85°C) (512T)               | CS# = V <sub>CC</sub> ,<br>V <sub>CC</sub> = 3.6 V;<br>Full array                                                | -   | 37                        | 318   | μА   |

| lнs              | Hybrid sleep current<br>HYPERRAM™ SEMPER™ Flash | CS# = V <sub>CC</sub> ,<br>V <sub>CC</sub> = 2.0 V;<br>Full array                                                | -   | 27                        | 248   |      |

|                  | in DPD<br>(-40°C to +105°C) (512T)              | CS# = V <sub>CC</sub> ,<br>V <sub>CC</sub> = 3.6 V;<br>Full array                                                | -   | 37                        | 348   |      |

### **Notes**

- 3. I<sub>CC</sub> active while embedded algorithm (EA) is in progress.

- 4. Not 100% tested.

- 5. Active Clock Stop mode enables the lower power mode when the CK signals remain stable for  $t_{ACC}$  + 30 ns.

- 6. Typical  $I_{CC}$  values are measured at  $t_{AI}$  = 25°C and  $V_{CC}$  =  $V_{CC}Q$  = 1.8 V/3.0 V (not applicable to  $I_{DPD}$  for 85°C and 105°C).

- 7. Current specification includes both the SEMPER™ Flash and HYPERRAM™ die current consumption per the mode of operation of each die.

**(infineon**

**Electrical specifications**

### **5.3** Capacitance characteristics

### Table 4 1.8 V/3.0 V capacitive characteristics

| Description                                         | Parameter | Min | Max  | Unit |

|-----------------------------------------------------|-----------|-----|------|------|

| Input capacitance (CK, CK#) <sup>[8-10]</sup>       | CI        | 6.0 | 10.5 |      |

| Output capacitance (DS/RWDS) <sup>[8-10]</sup>      | СО        | 9.5 | 10.5 |      |

| I/O pin capacitance (DQx) <sup>[8-10]</sup>         | CIO       | 9.5 | 10.5 | pF   |

| I/O pin capacitance delta (DQx) <sup>[8-10]</sup>   | CIOD      | -   | 0.25 |      |

| INT#, RSTO# pin capacitance, RST# <sup>[8-10]</sup> | СОР       | 9.5 | 10.5 |      |

#### Notes

- 8. These values are guaranteed by design and are tested on a sample basis only.

- 9. Pin capacitance is measured according to JEP147 procedure for measuring capacitance using a vector network analyzer.  $V_{CC}$ ,  $V_{CC}Q$  are applied and all other pins (except the pin under test) floating. DQs should be in the HIGH-Z state.

- 10. The capacitance values for the CK, CK#, RWDS and DQx pins must have similar capacitance values to allow for signal propagation time matching in the system. The capacitance value for CS# is not as critical because there are no critical timings between CS# going active (LOW) and data being presented on the DQs bus.

### 5.4 Thermal resistance

Table 5 Thermal resistance

| Parameter | Description                                 | Test condition                                                                | 24-ball BGA | Unit |

|-----------|---------------------------------------------|-------------------------------------------------------------------------------|-------------|------|

| Theta JA  | Thermal resistance<br>(Junction to ambient) | Test conditions follow standard test methods                                  | 53.6        |      |

| Theta JB  | Thermal resistance<br>(Junction to board)   | and procedures for measuring thermal impedance in accordance with EIA/JESD51. | 28.3        | °C/W |

| Theta JC  | Thermal resistance<br>(Junction to case)    | With Still Air (0 m/s)                                                        | 16.2        |      |

Package diagram

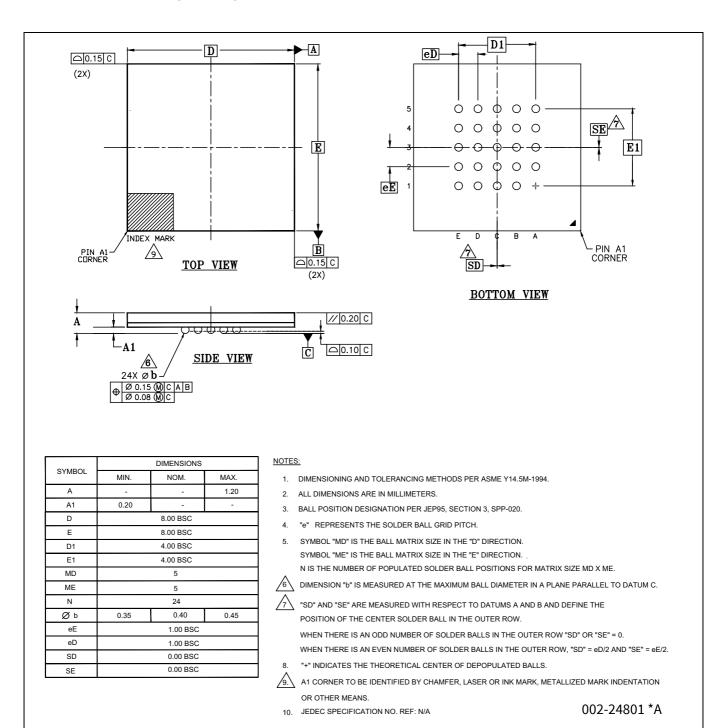

## 6 Package diagram

Figure 4 24-ball BGA (8 × 8 × 1.2 mm) package outline, 002-24801

HYPERBUS™ interface, multi-chip package, 1.8 V/3.0 V

Ordering information

#### **Ordering information** 7

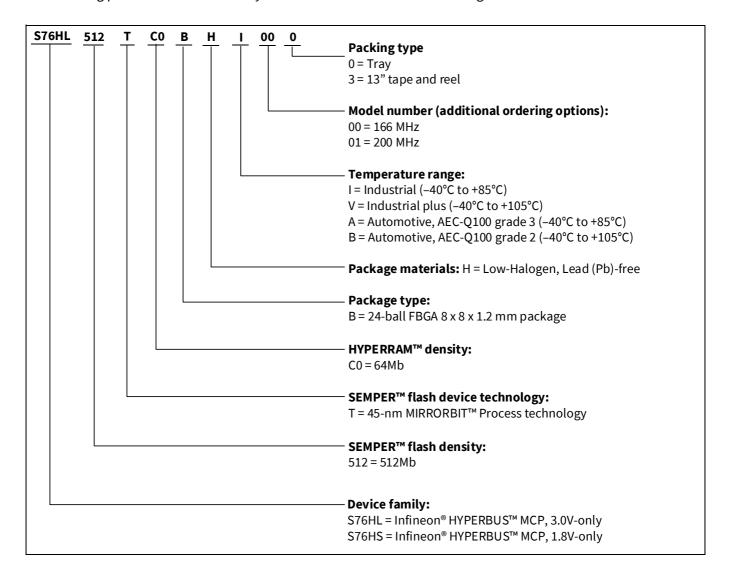

#### **Ordering code definition** 7.1

The ordering part number is formed by a valid combination of the following:

HYPERBUS™ interface, multi-chip package, 1.8 V/3.0 V

Ordering information

### 7.2 Valid combinations — Standard

**Table 6** lists configurations planned to be available in volume. The table will be updated as new combinations are released. Contact your local sales representative to confirm availability of specific combinations and to check on newly released combinations.

Table 6 Valid combinations — Standard (Contact Sales)

| Device<br>number | HYPERRAM™<br>density | Package<br>and<br>material | Temperature range | Model<br>number | Packing<br>type   | Ordering<br>part number<br>(x = Packing type) | Package<br>marking |   |    |    |        |        |                   |              |

|------------------|----------------------|----------------------------|-------------------|-----------------|-------------------|-----------------------------------------------|--------------------|---|----|----|--------|--------|-------------------|--------------|

| S76HL512T        | CO                   | ВН                         | I                 | 00              | 0,3               | S76HL512TC0BHI00x                             | 6HL512TC0I00       |   |    |    |        |        |                   |              |

| 3/60123121       | CO DII               | Co                         | вн                | ВΠ              | Dil               | V Bii                                         | DIT                | V | 00 | 00 | 00   0 | 00 0,3 | S76HL512TC0BHV00x | 6HL512TC0V00 |

| S76HS512T        | CO                   | DЦ                         | I                 | 01              | 0.2               | S76HS512TC0BHI01x                             | 6HS512TC0I01       |   |    |    |        |        |                   |              |

| 310033121        | S512T C0 B           | ВП                         | C0 BH V 01 0,5    | 0,3             | S76HS512TC0BHV01x | 6HS512TC0V01                                  |                    |   |    |    |        |        |                   |              |

### 7.3 Valid combinations — Automotive grade / AEC-Q100

**Table 8** lists configurations that are Automotive grade / AEC-Q100 qualified and are planned to be available in volume. The table will be updated as new combinations are released. Consult your local sales representative to confirm availability of specific combinations and to check on newly released combinations.

Production part approval process (PPAP) support is only provided for AEC-Q100 grade products.

Products to be used in end-use applications that require ISO/TS-16949 compliance must be AEC-Q100 grade products in combination with PPAP. Non–AEC-Q100 grade products are not manufactured or documented in full compliance with ISO/TS-16949 requirements.

AEC-Q100 grade products are also offered without PPAP support for end-use applications that do not require ISO/TS-16949 compliance.

Table 7 Valid combinations — Automotive grade / AEC-Q100 (In Production)

| Device<br>number | HYPERRAM™<br>density | Package<br>and<br>material | Temperature range | Model<br>number | Packing<br>type | Ordering part number (x = Packing type) | Package<br>marking |

|------------------|----------------------|----------------------------|-------------------|-----------------|-----------------|-----------------------------------------|--------------------|

| S76HL512T        | C0                   | ВН                         | В                 | 00              | 0,3             | S76HL512TC0BHB00x                       | 6HL512TC0B00       |

| S76HS512T        | C0                   | ВН                         | В                 | 01              | 0,3             | S76HS512TC0BHB01x                       | 6HS512TC0B01       |

Table 8 Valid combinations — Automotive grade / AEC-Q100 (Contact Sales)

| Device<br>number | HYPERRAM™<br>density | Package<br>and<br>material | Temperature range | Model<br>number | Packing<br>type | Ordering part number (x = Packing type) | Package<br>marking |

|------------------|----------------------|----------------------------|-------------------|-----------------|-----------------|-----------------------------------------|--------------------|

| S76HL512T        | CO                   | ВН                         | Α                 | 00              | 0,3             | S76HL512TC0BHA00x                       | 6HL512TC0A00       |

| S76HS512T        | C0                   | ВН                         | A                 | 01              | 0,3             | S76HS512TC0BHA01x                       | 6HS512TC0A01       |

HYPERBUS™ interface, multi-chip package, 1.8 V/3.0 V

Revision history

## **Revision history**

| Document revision | Date       | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **                | 2021-02-05 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *A                | 2021-11-18 | Updated HYPERBUS™ MCP signal description: Updated Figure 1. Updated Table 2: Updated Description for CK#. Updated HYPERBUS™ MCP block diagram: Updated Figure 2. Updated Electrical specifications: Updated DC characteristics: Updated Table 3: Updated Description for I <sub>LI</sub> . Updated Max. value for I <sub>CC2HR</sub> and I <sub>HS</sub> . Added Thermal resistance. Updated Package diagram: spec 002-24801 – Changed revision from ** to *A.                                                                                                                                              |

| *B                | 2022-09-21 | Changed status from "Preliminary Supplement" to "Supplement".  Updated Document Title to read as "S76HS512TC0, S76HL512TC0, 512Mb SEMPER™ Flash and 64Mb HYPERRAM™ 2.0 HYPERBUS™ interface, multi-chip package, 1.8 V/3.0 V".  Remove 1Gb SEMPER™ Flash related information in all instances across the document.  Updated General description:  Updated Table 1.  Updated Table 1.  Updated DC characteristics:  Updated Table 3.  Updated Ordering information:  Updated Valid combinations — Standard:  Updated Table 6.  Updated Table 6.  Updated Table 7.  Updated Table 8.  Updated to new template. |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2022-09-21 Published by Infineon Technologies AG 81726 Munich, Germany

© 2022 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Go to www.infineon.com/support

Document reference 002-31140 Rev. \*B

### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.