## S26HS02GT, S26HS04GT, S26HL02GT, S26HL04GT

# 2Gb/4Gb SEMPER™ Flash

## HYPERBUS™ interface, 1.8V/3.0V

## **Device** overview

#### Architecture

- Infineon® 45-nm MIRRORBIT™ technology that stores two data bits in each memory array cell

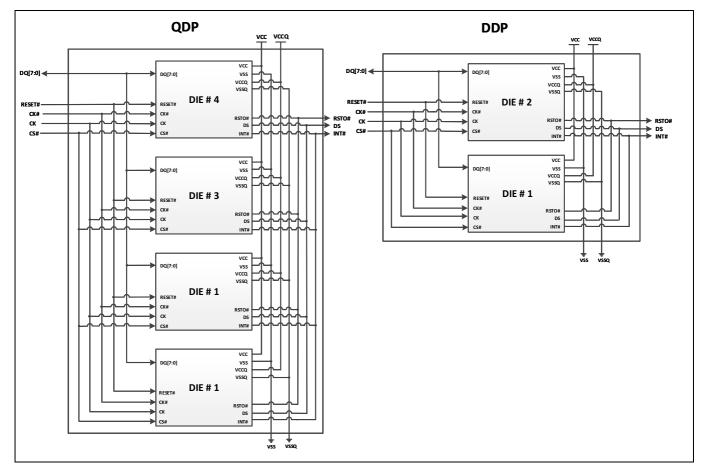

- Multi-chip package (MCP)

- 02GT Dual die package (DDP) 2 × 1 Gb die

- 04GT Quad die package (QDP) 4 × 1 Gb die

- Sector architecture options

- Uniform: Address space consists of all 256 KB sectors

- Hybrid

Configuration 1: Address space consists of thirty-two 4 KB sectors grouped either on the top or the bottom while the remaining sectors are all 256 KB

Configuration 2: Address space consists of thirty-two 4 KB sectors at the top and bottom while the remaining sectors are all 256 KB

- Page programming buffer of 256 or 512 bytes

- OTP secure silicon region (SSR) of 1024-bytes (32 × 32 bytes)

#### Interface

- HYPERBUS™ interface

- JEDEC eXpanded SPI (JESD251) compliant

- DDR option runs up to 332 MBps (166 MHz clock speed)

- Supports data strobe (DS) to simplify the read data capture in high-speed systems

- Legacy (×1) SPI (1S-1S-1S)

- JEDEC eXpanded SPI (JESD251) compliant

- SDR option runs up to 21 MBps (166 MHz clock speed)

- SEMPER™ Flash with HYPERBUS™ interface devices support default boot in legacy SPI (×1) or HYPERBUS™ interface (×8)

#### Highlights

- Safety features

- Functional safety with the industry's first ISO26262 ASIL B compliant and ASIL D ready NOR Flash

- Infineon Endurance flex architecture provides high-endurance and long retention partitions

- Interface CRC detects errors on communication interface between host controller and SEMPER™ Flash device

- Data integrity CRC detects errors in memory array

- SafeBoot reports device initialization failures, detects configuration corruption and provides recovery options

- Built-in error correcting code (ECC) corrects single-bit error and detects double-bit error (SECDED) on memory array data

- Sector erase status indicator for power loss during erase

- Protection features

- Advanced sector protection for individual memory array sector based protection

- Hardware reset through CS# signaling method (JEDEC) and individual RESET# pin

#### Identification

- Serial flash discoverable parameters (SFDP) describing device functions and features

- Device identification, manufacturer identification, and unique identification

#### \_\_\_\_\_

Device overview

## Data integrity

- Minimum 2,560,000 program-erase cycles for the main array

- Minimum 300,000 program-erase cycles for the 4 KB sectors

- Minimum 25 years data retention

## Supply voltage

- 1.7-V to 2.0-V (HS-T)

- 2.7-V to 3.6-V (HL-T)

#### • Grade / Temperature range

- Industrial (-40 °C to +85 °C)

- Industrial Plus (-40 °C to +105 °C)

- Automotive AEC-Q100 grade 3 (-40 °C to +85 °C)

- Automotive AEC-Q100 grade 2 (-40 °C to +105 °C)

- Automotive AEC-Q100 grade 1 (-40 °C to +125 °C)

## Packages

- 24-ball BGA 8 × 8 mm

**(infineon**

Performance summary

# **Performance summary**

## **Maximum read rates**

| Transaction               | Initial access latency (cycles) | Clock rate (MHz) | MBps  |

|---------------------------|---------------------------------|------------------|-------|

| SPI read                  | 0                               | 50               | 6.25  |

| SPI fast read             | 10                              | 166              | 20.75 |

| HYPERBUS™ read DDR (HS-T) | 14                              | 166              | 332   |

| HYPERBUS™ read DDR (HL-T) | 12                              | 133              | 266   |

## Typical program and erase rates

| Operation                                           | KBps      |

|-----------------------------------------------------|-----------|

| 256B page programming (4 KB sector / 256 KB sector) | 595 / 533 |

| 512B page programming (4 KB sector / 256 KB sector) | 753 / 898 |

| 256 KB sector erase                                 | 331       |

| 4 KB sector erase                                   | 95        |

## **Typical current consumption DDP**

| Operation            | HL-T current (mA) | HS-T current (mA) |

|----------------------|-------------------|-------------------|

| SDR read 50 MHz      | 31                | 31                |

| DDR read (HYPERBUS™) | 110               | 99                |

| Program              | 50                | 50                |

| Erase                | 50                | 50                |

| Standby              | 0.028             | 0.022             |

| Deep power down      | 0.0044            | 0.0026            |

## **Typical current consumption QDP**

| Operation            | HL-T current (mA) | HS-T current (mA) |

|----------------------|-------------------|-------------------|

| SDR read 50 MHz      | 31                | 31                |

| DDR read (HYPERBUS™) | 110               | 99                |

| Program              | 50                | 50                |

| Erase                | 50                | 50                |

| Standby              | 0.056             | 0.044             |

| Deep power down      | 0.0088            | 0.0052            |

Table of contents

## **Table of contents**

| Device overview                 | 1  |

|---------------------------------|----|

| Performance summary             |    |

| Table of contents               |    |

| 1 Pinout and signal description |    |

| 2 Interface overview            |    |

| 2.1 General description         |    |

| 3 Ordering information          | 11 |

| Revision history                | 12 |

Pinout and signal description

# 1 Pinout and signal description

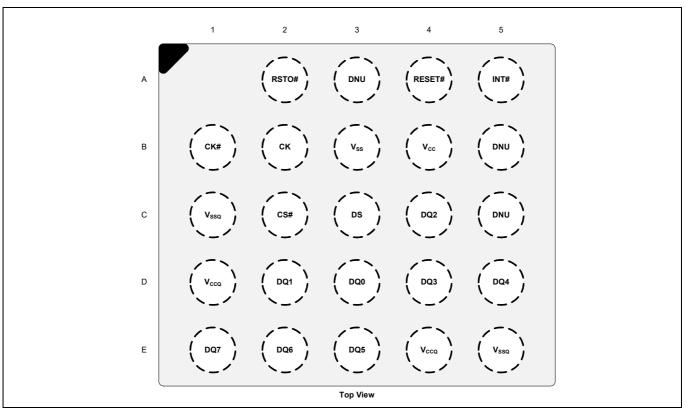

Figure 1 24-ball BGA pinout configuration<sup>[1]</sup>

#### Note

1. Flash memory devices in BGA packages can be damaged if exposed to ultrasonic cleaning methods. The package, data integrity, or both may be compromised if the package body is exposed to temperatures above 150 °C for prolonged periods of time.

Pinout and signal description

| Table 1 Signal des | cription |

|--------------------|----------|

|--------------------|----------|

| Table 1                   | Signal descrip         | tion                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------|------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                    | Туре                   | Mandatory/<br>optional | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CS#                       | Input                  | Mandatory              | Chip Select (CS#). All bus transactions are initiated with a HIGH to LOW transition on CS# and terminated with a LOW to HIGH transition on CS#. Driving CS# LOW enables the device, placing it in the active mode. When CS# is driven HIGH, the device enters standby mode, unless an internal embedded operation is in progress. All other input pins are ignored and the output pins are put in high impedance state.                                                                                                                                                                                                                                                                                                                                                                                             |

| CK, CK# <sup>[2, 3]</sup> | Input                  | Mandatory              | Clock (CK, CK#). Clock provides the timing of the serial interface. Single ended and differential clock modes are offered. Transactions are latched either on the rising edge of CK signal (single ended) or on the crossing of the CK and CK# signals (differential). In legacy (x1) SPI interface, command, address and data inputs are latched on rising edge of the clock, and data is output on the falling edge of the clock. In HYPERBUS™ (×8) interface, for single ended clock, command, address and data input are latched with respect to the rising edge of the CK. In differential clock mode, command, address and data inputs are latched with respect to the crossing of CK and CK#. Differential Clock. CK and CK# are used.  Single Ended. CK is used (CK# is not used and can be left floating). |

| DS                        | Output                 | Mandatory              | Read Data Strobe (DS). DS is used for data read operations only and indicates output data valid for HYPERBUS™ interface. During a read transaction while CS# is LOW, DS toggles to synchronize data output until CS# goes HIGH. Output data during read transactions are edge aligned with DS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DQ[7:0]                   | Input/<br>output       | Mandatory              | Serial Data (DQ[7:0]). Bidirectional signals that transfer command, address and data information.  Legacy (x1) SPI Interface. DQ[0] is an input (SI) and DQ[1] is an output (SO).  HYPERBUS™ (×8) Interface. DQ[7:0] are input and output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RESET#                    | Input<br>(Weak pullup) | Optional               | Hardware Reset (RESET#). When LOW, the device will self initialize and return to the array read state. DS and DQ[7:0] are placed into the HIGH-Z state when RESET# is LOW. RESET# includes a weak pullup, meaning, if RESET# is left unconnected it will be pulled up to the HIGH state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| INT#                      | Output<br>(Open drain) | Optional               | <b>System Interrupt (INT#).</b> When LOW, the device is indicating that an internal event has occurred. This signal is intended to be used as a system level interrupt for the device to indicate that an on-chip event has occurred. INT# is an open-drain output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## Notes

The clock is not required to be free running.

CK and CK# are not true differential signals. They are compliment signals. Care must be taken to ensure system level terminations are properly designed in.

Pinout and signal description

Table 1 Signal description (Continued)

| Symbol           | Туре                   | Mandatory/<br>optional | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSTO#            | Output<br>(Open drain) | Optional               | Reset output (RSTO#). RSTO# is an open-drain output used to indicate when a POR is occurring within the device and can be used as a system level reset signal. Upon completion of the internal POR the RSTO# signal will transition from Low to high impedance after a user defined timeout period has elapsed. Upon transition to the high impedance state the external pull-up resistance will pull RSTO# HIGH and the device immediately is placed into the Standby state. Transactions are blocked when RSTO# is LOW. During this period, the device cannot be selected, will not accept any transactions, and does not drive outputs other than RSTO#. |

| V <sub>CC</sub>  | Power supply           | Mandatory              | Core power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>CCQ</sub> | Power supply           | Mandatory              | Input / output power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>SS</sub>  | Ground supply          | Mandatory              | Core ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>SSQ</sub> | Ground supply          | Mandatory              | Input / output ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DNU              | _                      | -                      | Do not use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

The clock is not required to be free running.

CK and CK# are not true differential signals. They are compliment signals. Care must be taken to ensure system level terminations are properly designed in.

Interface overview

## 2 Interface overview

## 2.1 General description

The Infineon® SEMPER™ Flash family of products are high-speed CMOS, MIRRORBIT™ NOR Flash devices that are compliant with the JEDEC JESD251 eXpanded SPI (xSPI) specification. SEMPER™ Flash is designed for functional safety with development according to ISO 26262 standard to achieve ASIL-B compliance and ASIL-D readiness.

SEMPER™ Flash with HYPERBUS™ interface devices support both the HYPERBUS™ interface as well as legacy (×1) SPI. Both interfaces serially transfer transactions reducing the number of interface connection signals. SPI supports SDR whereas HYPERBUS™ supports DDR.

The HYPERBUS™ interface DDR transfers two data bytes per clock cycle on the data (DQ) signals. A read or program/write access consists of a series of 16-bit wide, one clock cycle data transfers at the internal HYPERFLASH™ core and two corresponding 8-bit wide, one-half-clock-cycle data transfers on the DQ signals. Both data and command/address information are transferred in DDR fashion over the 8-bit data bus. The clock input signals are used for signal capture by SEMPER™ Flash when receiving command/address/data information on the DQ signals. The read data strobe (DS) is an output from SEMPER™ Flash that indicates when data is being transferred from the memory. DS is referenced to the rising and falling edges of CK during the data transfer portion of read operations. Command/address/write-data values are center aligned with the clock edges and read-data values are edge aligned with the transitions of DS.

Read and program/write operations to SEMPER™ Flash are burst oriented. Read transactions can be specified to use either a wrapped or linear burst. During wrapped operation, accesses start at a selected location and continue for a configured number of locations in a group wrap sequence. During linear operation, accesses start at a selected location and continue in a sequential manner until the read operation is terminated, when CS# returns HIGH. Write transactions transfer one or more16-bit values.

Each random read accesses a 32-byte length and aligned set of data called a page. Each page consists of a pair of 16-byte aligned groups of array data called half-pages. Half-pages are aligned on 16-byte address boundaries. A read access requires two clock cycles to define the target half-page address and the burst type, then an additional initial latency. During the initial latency period, the third clock cycle will specify the starting address within the target half-page. After the initial data value has been output, additional data can be read from the page on subsequent clock cycles in either a wrapped or linear manner. When configured in linear burst mode, while a page is being burst out, the device will automatically fetch the next sequential page from the MIRRORBIT™ Flash memory array. This simultaneous burst output while fetching from the array allows for a linear sequential burst operation that can provide a sustained output of 266/332 MBps data rate:

[1-byte (8-bit data bus) \* 2 (data on both clock edges) \* 133/166 MHz = 266/332 MBps].

The erased state of each memory bit is a logic 1. Programming changes a logic 1 (HIGH) to a logic 0 (LOW). Only an erase operation can change a memory bit from a 0 to a 1. An erase operation must be performed on a complete sector (4 KBs or 256 KBs).

SEMPER™ Flash provides a flexible sector architecture. The address space can be configured as either a uniform 256 KB sector array, or a hybrid grouped array where thirty-two 4 KB sectors are either grouped at the top or at the bottom while the remaining sectors are all 256 KB, or a hybrid split array where the thirty-two 4 KB sectors are at both the top and the bottom while the remaining sectors are all 256 KB.

The page programming buffer used during a single programming operation is configurable to either 256 bytes or 512 bytes. The 512 byte option provides the highest programming throughput.

This device is an MCP with DDP or QDP stacked die, with the control signals for all dies tied together internally in the package.

Interface overview

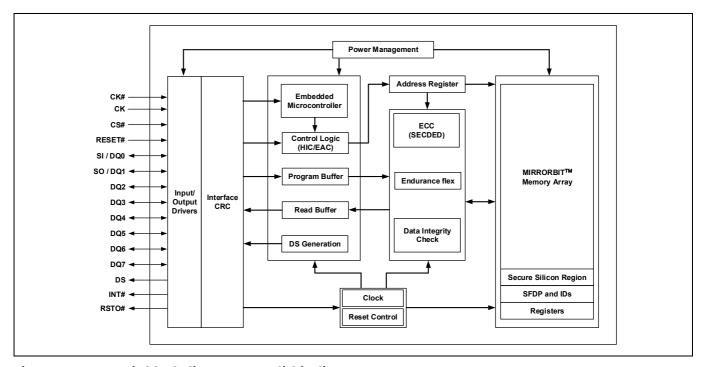

Figure 2 Logic block diagram monolithic die

Figure 3 MCP diagram

infineon

Interface overview

The SEMPER™ Flash family consists of multiple densities with, 1.8 V and 3.0 V core and I/O voltage options.

The device control logic is subdivided into two parallel operating sections: the host interface controller (HIC) and the embedded algorithm controller (EAC). The HIC monitors signal levels on the device inputs and drives outputs as needed to complete read, program, and write data transfers with the host system. The HIC delivers data from the currently entered address map on read transfers; places write transfer address and data information into the EAC command memory, and notifies the EAC of power transition and write transfers. The EAC interrogates the command memory, after a program or write transfer, for legal command sequences and performs the related embedded algorithms.

Changing the nonvolatile data in the memory array requires a sequence of operations that are part of embedded algorithms (EA). The algorithms are managed entirely by the internal EAC. The main algorithms perform programming and erase of the main flash array data. The host system writes command codes to the flash device. The EAC receives the command, performs all the necessary steps to complete the transaction, and provides status information during the progress of an EA.

In addition to the mandatory signals CS#, CK, SI/DQ0, SO/DQ1, DQ [7:2] and DS, the SEMPER™ Flash devices also include optional signals CK#, RESET#, INT# and RSTO#. When RESET# transitions from LOW to HIGH, the device returns to the default state that occurs after an internal power-on reset (POR). The DS is synchronized with the output data during read transactions enabling host system to capture data at high clock frequency operation. The INT# is an open-drain output can provide an interrupt to the HYPERFLASH™ master to indicate when the HYPERFLASH™ transitions from busy to ready at the end of a program or erase operation or to indicate the detection of an ECC error during read. The RSTO# is an open-drain output used to indicate when a POR is occurring within the device and can be used as a system level reset signal. Upon completion of the internal POR, the RSTO# signal will transition from Low to high impedance after a user defined timeout period has expired. Upon transition to the high impedance state, the external pull-up resistance will pull RSTO# HIGH and the device immediately is placed into the Standby state.

Infineon endurance flex architecture provides system designers the ability to customize SEMPER™ Flash's endurance and retention for their specific application. The host defines partitions for high endurance or long retention, providing up to 1+ million cycles or 25 years of data retention.

SEMPER™ Flash devices support error detection and correction by generating an embedded hamming error correction code (ECC) during memory array programming. This ECC code is then used for single-bit and double-bit error detection and single-bit correction during read.

SEMPER™ Flash devices have built-in diagnostic features providing the host system with the device status:

- Program and erase operation: Reporting of program or erase success, failure and suspend status

- Error detection and correction: 1-bit and/or 2-bit error status with address trapping and error count

- Data integrity check: Error detection over memory array contents

- Interface cyclic redundancy check (CRC): Error detection over interface transactions

- SafeBoot: Reporting of proper flash device initialization and configuration corruption recovery

- Sector erase status: Reporting of erase success or failure status per sector

- Sector erase counter: Counts the number of erase cycles per sector

Ordering information

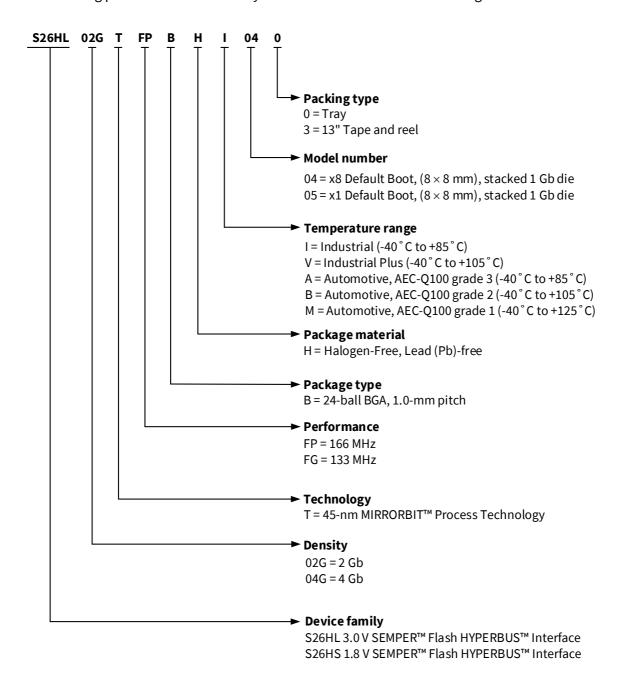

# **3** Ordering information

Register for the SEMPER™ Access Program and get access to Software and Evaluation kits, models, datasheets, and application notes.

The ordering part number is formed by a valid combination of the following:

Revision history

# **Revision history**

| Document version | Date of release | Description of changes |  |

|------------------|-----------------|------------------------|--|

| **               | 2022-02-01      | Initial release        |  |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2022-02-01 Published by Infineon Technologies AG 81726 Munich, Germany

© 2022 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Go to www.infineon.com/support

Document reference 002-34696 Rev. \*\*

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.