# 10 kW 3-level NPC2 inverter reference design

## REF-10KW3LNPC2

### About this document

## Scope and purpose

This user guide describes the NPC2 inverter reference design REF-10KW3LNPC2 and its main features, key data, pin assignments, mechanical dimensions, and electrical interfaces.

### Intended audience

This user guide is meant for engineers and technical specialists working on solar photovoltaic solutions and similar domains. The concept of this power conversion reference design is modular so that the hardware can be reused for various power converter applications and use cases, with a special focus on solar photovoltaic solutions.

### Reference design

This reference design is not a qualified and certified commercial product. The hardware does not necessarily meet any safety, EMI, or quality standard (for example, UL, CE) requirements.

Power conversion board REF-10KW3LNPC2

# 10 kW 3-level NPC2 inverter reference design

REF-10KW3LNPC2

Important notice

## **Important notice**

"Evaluation Boards and Reference Boards" shall mean products embedded on a printed circuit board (PCB) for demonstration and/or evaluation purposes, which include, without limitation, demonstration, reference and evaluation boards, kits and design (collectively referred to as "Reference Board").

Environmental conditions have been considered in the design of the Evaluation Boards and Reference Boards provided by Infineon Technologies. The design of the Evaluation Boards and Reference Boards has been tested by Infineon Technologies only as described in this document. The design is not qualified in terms of safety requirements, manufacturing and operation over the entire operating temperature range or lifetime.

The Evaluation Boards and Reference Boards provided by Infineon Technologies are subject to functional testing only under typical load conditions. Evaluation Boards and Reference Boards are not subject to the same procedures as regular products regarding returned material analysis (RMA), process change notification (PCN) and product discontinuation (PD).

Evaluation Boards and Reference Boards are not commercialized products, and are solely intended for evaluation and testing purposes. In particular, they shall not be used for reliability testing or production. The Evaluation Boards and Reference Boards may therefore not comply with CE or similar standards (including but not limited to the EMC Directive 2004/EC/108 and the EMC Act) and may not fulfill other requirements of the country in which they are operated by the customer. The customer shall ensure that all Evaluation Boards and Reference Boards will be handled in a way which is compliant with the relevant requirements and standards of the country in which they are operated.

The Evaluation Boards and Reference Boards as well as the information provided in this document are addressed only to qualified and skilled technical staff, for laboratory usage, and shall be used and managed according to the terms and conditions set forth in this document and in other related documentation supplied with the respective Evaluation Board or Reference Board.

It is the responsibility of the customer's technical departments to evaluate the suitability of the Evaluation Boards and Reference Boards for the intended application, and to evaluate the completeness and correctness of the information provided in this document with respect to such application.

The customer is obliged to ensure that the use of the Evaluation Boards and Reference Boards does not cause any harm to persons or third party property.

The Evaluation Boards and Reference Boards and any information in this document is provided "as is" and Infineon Technologies disclaims any warranties, express or implied, including but not limited to warranties of non-infringement of third party rights and implied warranties of fitness for any purpose, or for merchantability.

Infineon Technologies shall not be responsible for any damages resulting from the use of the Evaluation Boards and Reference Boards and/or from any information provided in this document. The customer is obliged to defend, indemnify and hold Infineon Technologies harmless from and against any claims or damages arising out of or resulting from any use thereof.

Infineon Technologies reserves the right to modify this document and/or any information provided herein at any time without further notice.

# 10 kW 3-level NPC2 inverter reference design

### **REF-10KW3LNPC2**

**Safety precautions**

## Safety precautions

Note: Please note the following warnings regarding the hazards associated with development systems.

| Table 1 | Safety precautions |

|---------|--------------------|

|---------|--------------------|

| 4 |  |

|---|--|

| • |  |

**Warning:** The DC link potential of this board is up to 1000 VDC. When measuring voltage waveforms by oscilloscope, high voltage differential probes must be used. Failure to do so may result in personal injury or death.

**Warning:** controller board must be connected to the main power board before powering the DC bus.

**Warning**: The evaluation or reference board contains DC bus capacitors which take time to discharge after removal of the main supply. Before working on the system, wait five minutes for capacitors to discharge to safe voltage levels. Failure to do so may result in personal injury or death. Darkened display LEDs are not an indication that capacitors have discharged to safe voltage levels.

**Caution:** The heat sink and device surfaces of the evaluation or reference board may become hot during testing. Hence, necessary precautions are required while handling the board. Failure to comply may cause injury.

**Caution:** Only personnel familiar with power electronics should plan, install, commission and subsequently service the system. Failure to comply may result in personal injury and/or equipment damage.

**Caution:** The evaluation or reference board contains parts and assemblies sensitive to electrostatic discharge (ESD). Electrostatic control precautions are required when installing, testing, servicing or repairing the assembly. Component damage may result if ESD control procedures are not followed. If you are not familiar with electrostatic control procedures, refer to the applicable ESD protection handbooks and guidelines.

**Caution:** The reference board is shipped with packing materials that need to be removed prior to installation. Failure to remove all packing materials that are unnecessary for system installation may result in overheating or abnormal operating conditions.

## **Table of contents**

## **Table of contents**

| REF-10         | OKW3LNPC2                                                                     | 1  |

|----------------|-------------------------------------------------------------------------------|----|

| About t        | his documenthis document                                                      | 1  |

| mport          | ant notice                                                                    | 2  |

| Safety         | precautions                                                                   | 3  |

|                | f contents                                                                    |    |

|                | he power conversion board at a glance                                         |    |

| L.1            | Introduction                                                                  |    |

| L.2            | Top level specifications                                                      |    |

| L.3            | Key design building blocks                                                    |    |

| L.4            | Preferred components                                                          |    |

|                | oard functional description                                                   |    |

| <b>2.1</b>     | Description of the functional blocks                                          |    |

| 2.1<br>2.1.1   | Switching devices                                                             |    |

| 2.1.1          | Gate driver                                                                   |    |

| 2.1.2          | Internal power supplies                                                       |    |

| 2.1.3<br>2.1.4 | Sensing and protection                                                        |    |

| 2.1.4.1        | Current sense                                                                 |    |

| 2.1.4.2        | Voltage sense                                                                 |    |

| 2.1.4.3        | Temperature sense                                                             |    |

| 2.1.4.4        | Fault and latch circuit                                                       |    |

| 2.1.5          | Fan control                                                                   |    |

| 2.1.6          | Connectors                                                                    |    |

| 2.1.6.1        | Extended interface-voltage sense                                              |    |

| 2.1.6.2        | Enhanced interface-Measure                                                    |    |

| 2.1.6.3        | Enhanced interface-control                                                    |    |

| 2.7            | Isolation coordination                                                        |    |

|                | esting                                                                        |    |

| 3.1            | Flashing the firmware                                                         |    |

| 3.2            | Control                                                                       |    |

| 3.3            | GUI                                                                           |    |

| 3.3.1          | Establishing communication                                                    |    |

| 3.3.2          | GUI parameters                                                                |    |

| 3.4            | Open-loop test results                                                        |    |

| 3.4.1          | Bench setup                                                                   |    |

| 3.4.2          | Output AC voltage against different DC input voltages                         |    |

| 3.4.3          | Auxiliary power supply output voltage against input DC-link voltage variation |    |

| 3.4.4          | Over current protection                                                       |    |

| 3.4.5          | Efficiency measurement                                                        |    |

| 4 B            | oard layout                                                                   |    |

| 4.1            | REF-10KW3LNPC2                                                                |    |

| 4.2            | ISODRV-3240C4P15N05-1                                                         |    |

| 1.3            | PB-APS-24V-5V ISO                                                             |    |

| 1.4            | REF-10KW3LNPC2-Filter                                                         |    |

| 1.5            | PB-CAPTANK-1.1KV                                                              |    |

|                | ill of kev materials                                                          |    |

|                | vv IMW                                                                        | TU |

## **Table of contents**

| Revision history | 47 |

|------------------|----|

|------------------|----|

# 1 The power conversion board at a glance

### 1.1 Introduction

REF-10KW3LNPC2 comes as a kit and includes different boards that can help the user to build and operate an NPC2 inverter power stage:

- REF-10KW3LNPC2: NPC2 inverter power stage main board

- ISODRV-3240C4P15N05-1: 4-channel gate driver boards for each leg of the NPC2 type

- PB-APS-24V-5V ISO: Isolated auxiliary power supply

- REF-10KW3LNPC2-Filter: LCL filter board

- PB-CAPTANK-1.1KV: DC-link capacitor board

The REF-10KW3LNPC2 main board consists of a 3-phase 3-level NPC2 power stage and carries power semiconductors, gate drivers and auxiliary power supply. It also offers connectors that the user can connect their own passives (filters and DC-link capacitors).

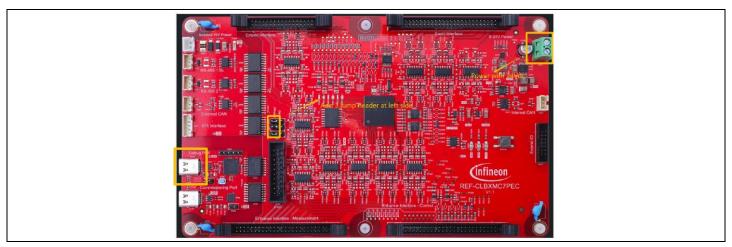

The user can also get separately an XMC7200-based control board which comes with all the signal conditioning circuits, power conversion software and a GUI that can allow the user to operate the inverter in open-loop configuration.

The XMC7200 control board is available under the name REF-CLBXMC7PEC.

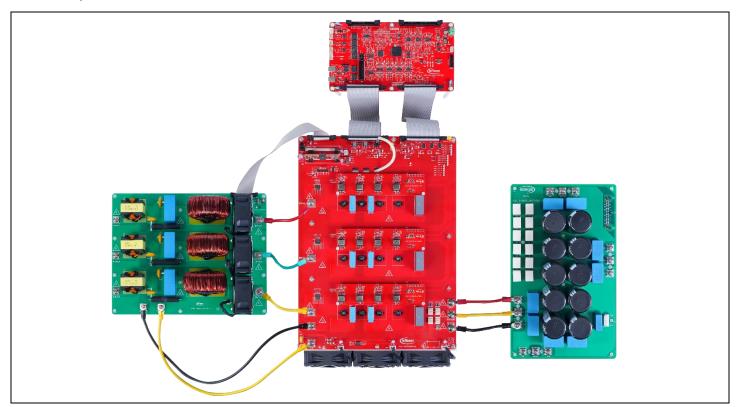

Figure 1 shows the completely assembled 10 kW 3-level NPC2 inverter reference design.

Figure 1 Power conversion reference design REF-10KW3LNPC2

#### Top level specifications 1.2

**Specifications** Table 2

| Parameter           | Typical | Maximum | Unit                |

|---------------------|---------|---------|---------------------|

| Input voltage       | 650     | 850     | $V_{dc}$            |

| Output voltage      | 380     | 400     | $V_{ll\text{-rms}}$ |

| Output current      |         | 15.2    | А                   |

| Output power        |         | 10      | kW                  |

| Switching frequency | 24      | 24      | kHz                 |

| Output frequency    | 50      | 65      | Hz                  |

#### **Key design building blocks** 1.3

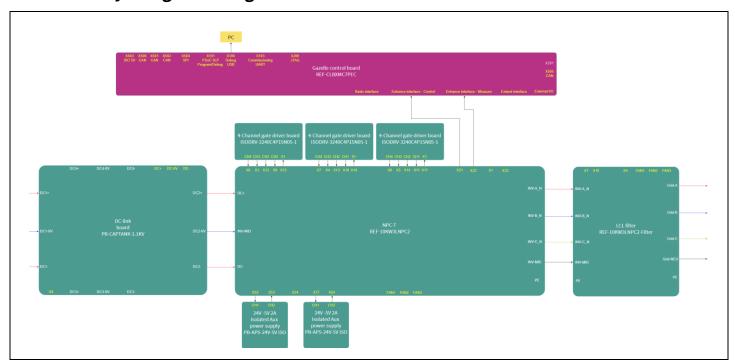

Figure 2 **Assembly diagram**

Figure 2 shows how the different boards are connected to construct the NPC2 inverter. Starting from the left, the DC power supply is connected to the DC-link board. The output three terminals (Positive, neutral and negative) are then connected to the power board. A total of three 4-channel gate driver boards are mounted on the top of the power board. An isolated power supply subsidiary card is also mounted on the top of the power board to provide an isolated 5V rail. A second isolated power supply card is also mounted but is not necessary for operation. On the other side the 3-phases and the mid-point of the DC-link are connected to the filter board. The filter board contains an LCL filter and an EMI filter.

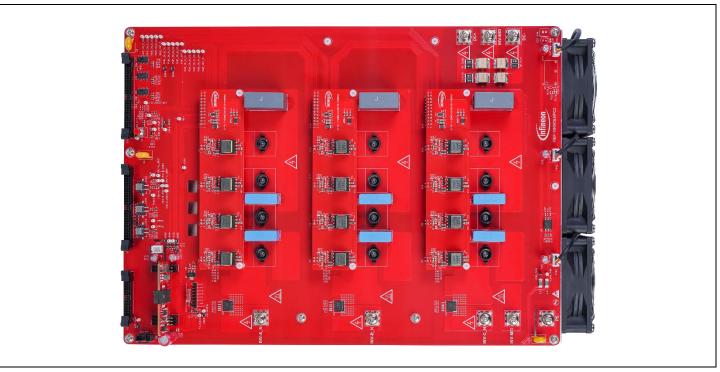

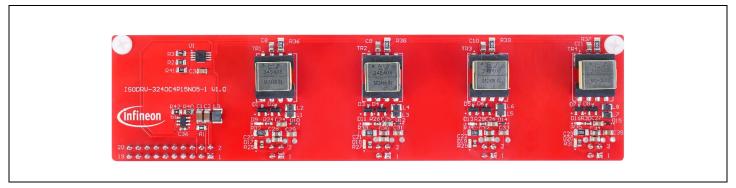

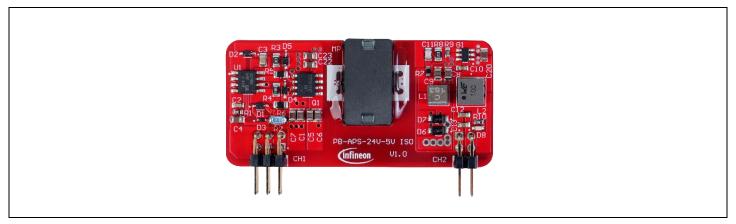

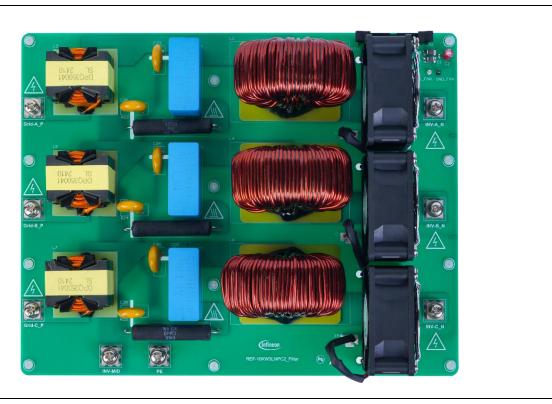

Figures 3,4,5,6 and 7 show the stand-alone REF-10KW3LNPC2, ISODRV-3240C4P15N05-1, PB-APS-24V-5V ISO, REF-10KW3LNPC2-Filter and PB-CAPTANK-1.1KV.

Figure 3 REF-10KW3LNPC2

Figure 4 ISODRV-3240C4P15N05-1

Figure 5 PB-APS-24V-5V ISO

Figure 6 **REF-10KW3LNPC2-Filter**

Figure 7 PB-CAPTANK-1.1KV

## 1.4 Preferred components

Figure 8 **Preferred Infineon components**

Figure 8 shows the main semiconductors offered in the 10 kW NPC2 inverter reference design.

- Power semiconductors:

- o TRENCHSTOP™ IGBT7 H7: <u>IKZA40N120CH7</u>

- TRENCHSTOP™ IGBT7 H7: <u>IKZA40N65EH7</u>

- Gate driver:

- o Single channel isolated gate driver with 2-level slew rate control: <u>1ED3240MC12H</u>

- Current sensor:

- o XENSIV<sup>™</sup> magnetic current sensor: <u>TLI4971</u>

- Auxiliary power supply:

- o 2EP130R: Full-bridge transformer driver

- IRS27952: Half Bridge controller IC

- IRF7351: 60V dual N-channel HEXFET power MOSFET

# 2 Board functional description

This chapter lists the features available for the 10 kW NPC2 inverter reference design.

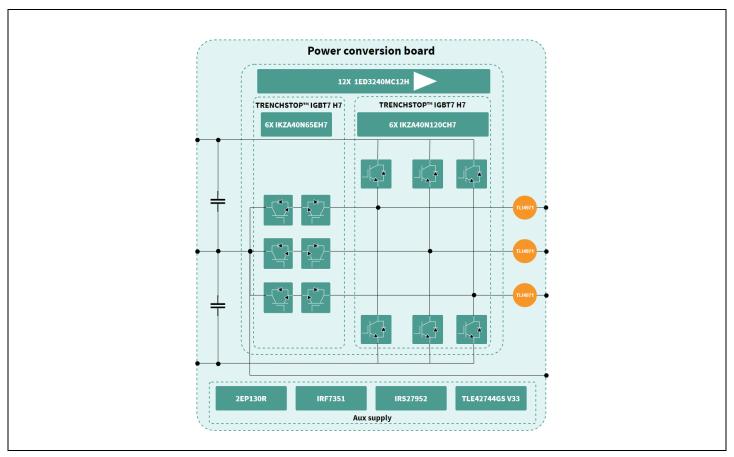

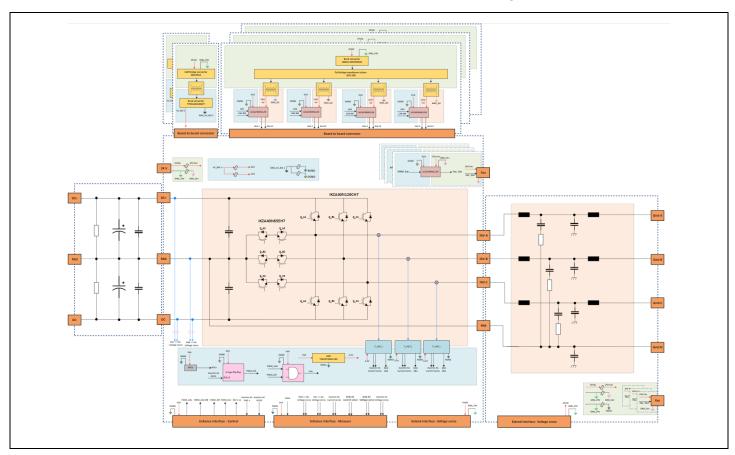

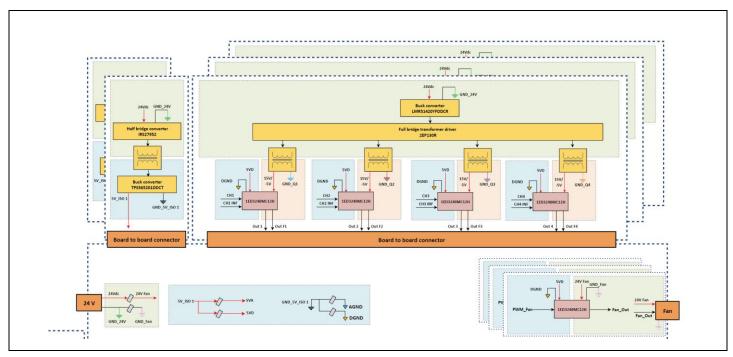

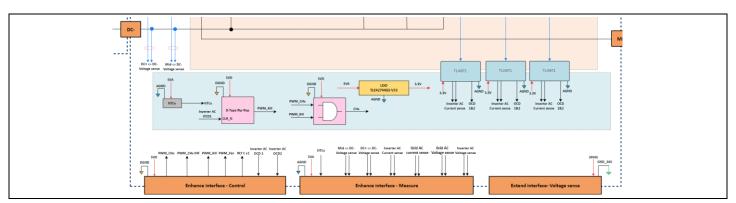

Figure 9 Block diagram of REF-10KW3LNPC2

# 2.1 Description of the functional blocks

# 2.1.1 Switching devices

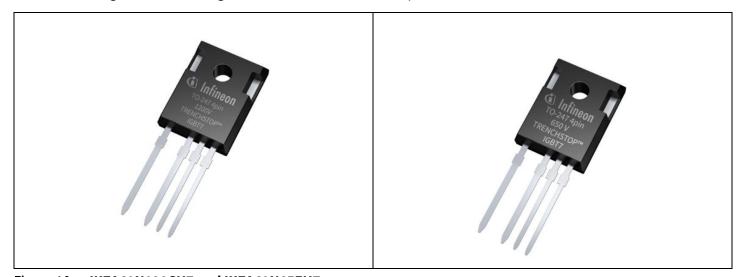

The inverter stage is realized using the TRENCHSTOP™ IGBT7 H7 products <a href="IKZA40N120CH7">IKZA40N120CH7</a> and <a href="IKZA40N65EH7">IKZA40N120CH7</a> and <a href="IKZA40N65EH7">IKZA40N120CH7</a> and <a href="IKZA40N65EH7">IKZA40N120CH7</a> and <a href="IKZA40N65EH7">IKZA40N120CH7</a> and <a href="IKZA40N65EH7">IKZA40N65EH7</a>.

Figure 10 IKZA40N120CH7 and IKZA40N65EH7

IKZA40N120CH7 and IKZA40N65EH7 belong to the TRENCHSTOP™ IGBT7 H7 family. They come in discrete in TO-247 4pin package technology that has been developed to fulfill the demand in applications focusing on decarbonization such as solar photovoltaic, uninterruptible power supplies and battery chargers.

#### 2.1.2 **Gate driver**

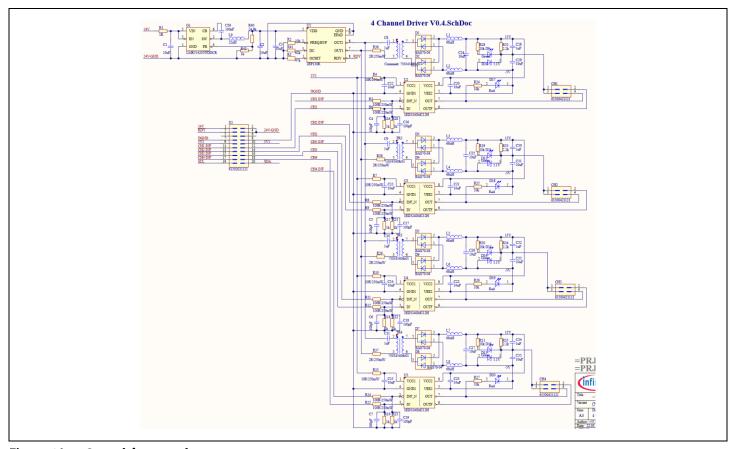

Figure 11 Gate driver card functional block diagram

Four gate single-channel isolated gate drivers are used to drive the 4 IGBTs. The gate driver used is 1ED3240MC12H.

Figure 12 1ED3240MC12H

<u>1ED3240MC12H</u> belongs to the EiceDRIVER™ 2L-SRC Compact 1ED32xx family and is a single-channel isolated gate driver with two-level slew-rate control (2L-SRC) and 10 A typical sinking and sourcing peak output current in DSO-8 wide-body package with large creepage distance (>8 mm) for IGBTs, MOSFETs and SiC MOSFETs. 1ED3240MC12H offers two separate outputs with 10 A typical peak output current to control two independent gate resistances for both turnon and turn-off thus enabling two-level slew-rate control. The driver can operate over a wide supply voltage range, either unipolar or bipolar.

Figure 13 **Gate driver card**

The 24 V and the PWM signals come from the power board and are used as an input to the gate drive card. The 24 V is then stepped down and used as an input to the 2EP130R full-bridge transformer driver. A transformer is then used to provide functional isolation and the voltages 15 V and -5V are then generated on the rectifier side to be used as the positive and negative voltage for driving the IGBTs on the power board. The gate resistors are located on the power board.

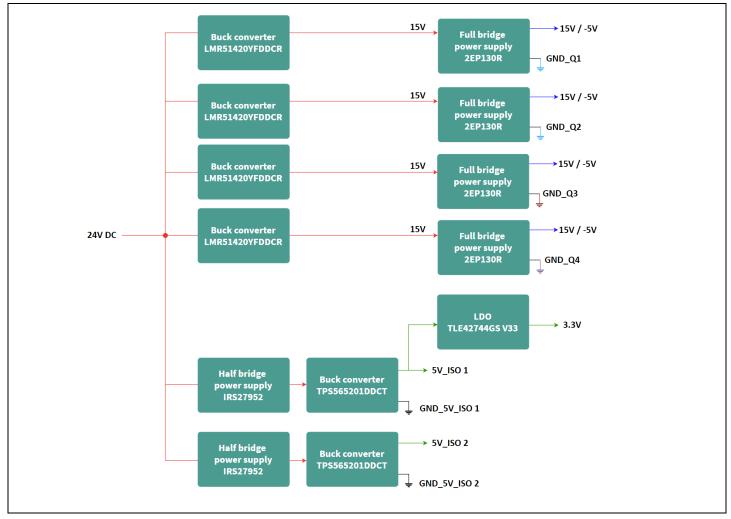

#### 2.1.3 **Internal power supplies**

24V needs to be supplied externally by the user to the power board. The 24 V are then fed to a power supply card which generates an isolated 5V. The 24 V is fed to the gate driver card which generates the isolated 15V / -5V needed to drive the IGBTs. The isolated 5 V is fed to the primary side of the gate driver.

Figure 14 **Auxiliary power supply tree**

The specifications of the power supply card are as follows:

Table 3 Specifications of the power supply card

| Parameter           | Minimum | Typical  | Maximum | Unit     |

|---------------------|---------|----------|---------|----------|

| Input voltage       | 21.6    | 24       | 26.4    | $V_{dc}$ |

| Input current       |         |          | 0.5     | А        |

| Output voltage      | 4.75    | 5        | 5.25    | $V_{dc}$ |

| Output current      |         |          | 2       | А        |

| Switching frequency |         | 226      |         | kHz      |

| Half bridge IC used |         | IRS27952 |         | -        |

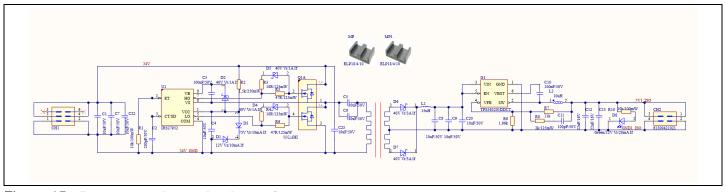

Figure 15 **Power supply card schematics**

#### 2.1.4 Sensing and protection

Figure 16 Functional block diagram of the measurement signals on the power board

#### 2.1.4.1 **Current sense**

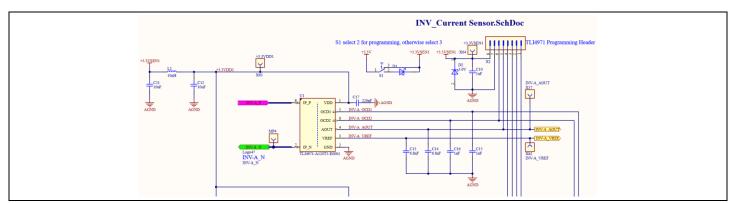

The inductor currents are sensed using <u>TLI4971</u> current sensor.

XENSIV<sup>™</sup> TLI4971-A120T5-U-E0001 is an Infineon high precision miniature coreless magnetic current sensor for AC and DC measurements with analog interface and dual fast over-current detection outputs. The two over current detection (OCD) pins are used to implement protection on hardware and software levels.

Figure 17 **Current sense circuit**

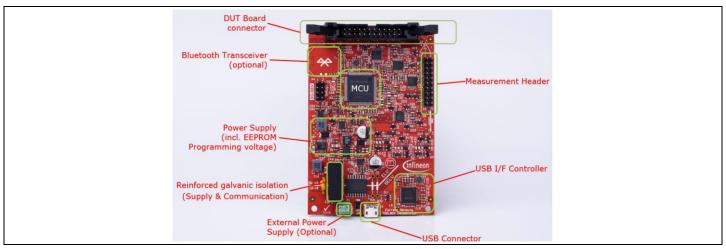

One way to reprogram the current sensor if needed is by using the XENSIV™ - TLI4971, TLE4972 current sensor programmer board. Details can be found in the board user guide.

Figure 18 Current sensor programmer board

The board needs to be connected to the user's PC and the DUT board connector needs to be interfaced with the power board.

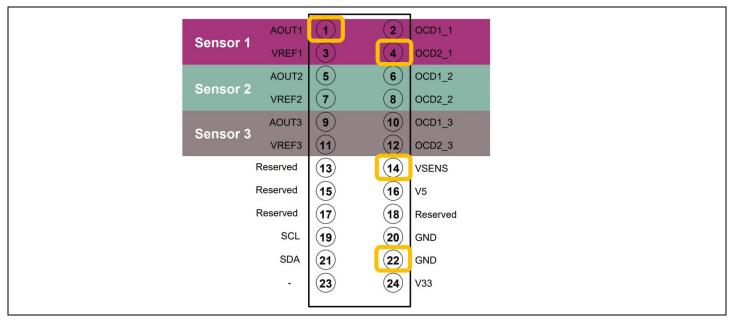

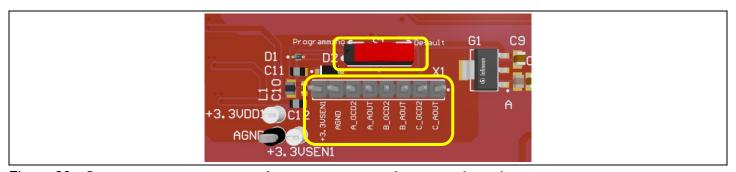

Figure 19 DUT board connector on the programmer board

Figure 20 Current sensor programming connector on the power board

The previous two figures show the two connectors that need to be interfaced together on the programming board and the power board.

## Steps to reprogram the current sensor:

- 1. Connect the programmer board with X1 on the power board and also with a USB cable to PC

- Place the switch S1 in programming mode

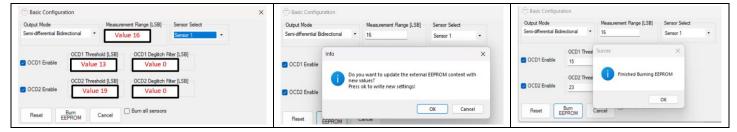

- Start the TLI4971 programming software

- In the GUI, go to memory and then basic configuration

- Set all the data, and press 'Burn EEPROM'

- Repeat the previous steps to program the other current sensors 6.

- 7. Remove all connections

- Place the switch S1 back in default mode

Figure 21 **GUI**

Figure 22 **GUI**

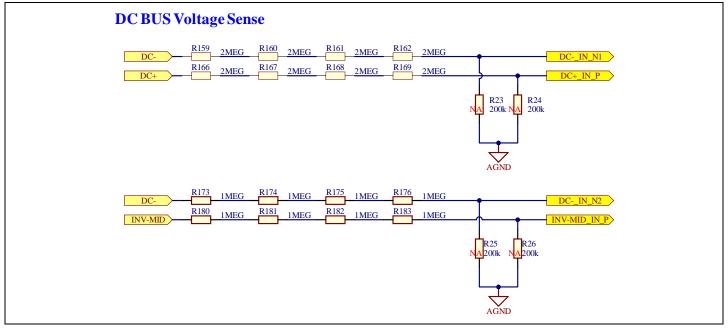

#### 2.1.4.2 Voltage sense

The DC-link voltages are measured on the power board.

**Warning**: controller board has to be connected with the main power board before powering the power board. Failure to do so can lead to a hazardous situation.

Figure 23 DC bus voltage sense

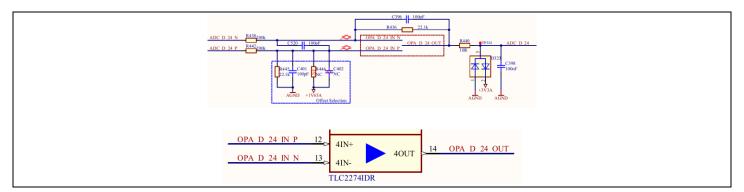

Figure 24 Signal conditioning circuit used on the control board

#### 2.1.4.3 **Temperature sense**

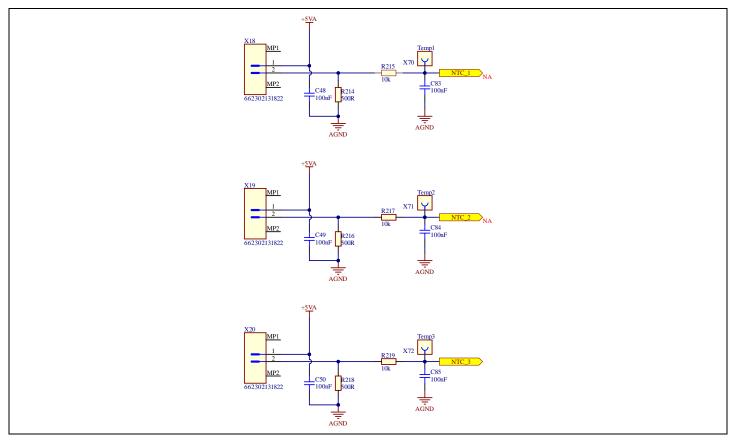

Three temperature measurements are provided on the power board using NTCs. The NTCs can be connected to the heat sink to measure the temperature and feed it back to the connector which can be connected to a control board.

Figure 25 Temperature sense circuit

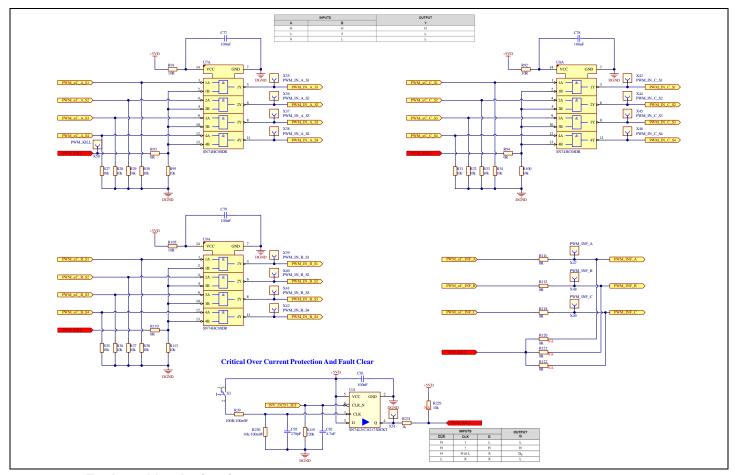

## 2.1.4.4 Fault and latch circuit

Fault and latch circuits are provided to disable the PWMs in the case of a fault which can be seen in the following figure:

Figure 26 Fault and latch circuit

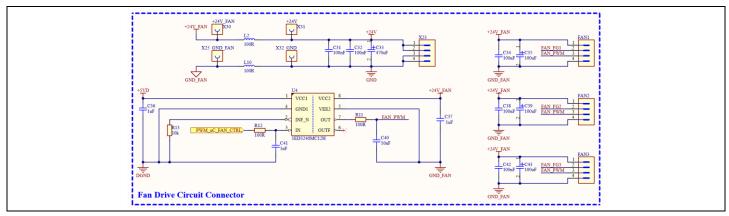

#### 2.1.5 Fan control

Additional fan control circuits are also provided in case the user needs to use forced air-cooling during evaluation.

Figure 27 Fan control circuits

#### 2.1.6 **Connectors**

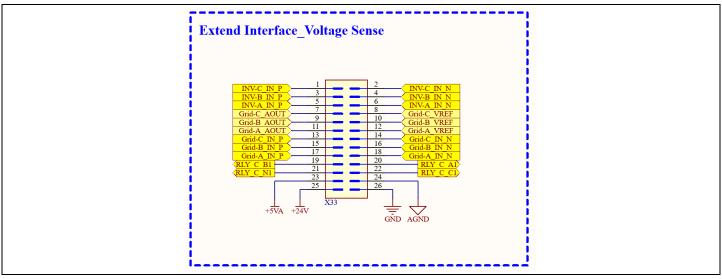

#### **Extended interface-voltage sense** 2.1.6.1

The connector is used to interface the filter board with the power board to power up the fans. It is also suitable for <u>future modifications</u> in order to sense the AC voltages and currents.

Figure 28 Extended interface-voltage sense

**Extended interface-voltage sense** Table 4

| Input voltage sense interface |             |                            |  |

|-------------------------------|-------------|----------------------------|--|

| Pin                           | Signal      | Description                |  |

| 1                             | INV-C_IN_P  | Inverter Phase C Voltage P |  |

| 2                             | INV-C_IN_N  | Inverter Phase C Voltage N |  |

| 3                             | INV-B_IN_P  | Inverter Phase B Voltage P |  |

| 4                             | INV-B_IN_N  | Inverter Phase B Voltage N |  |

| 5                             | INV-A_IN_P  | Inverter Phase A Voltage P |  |

| 6                             | INV-A_IN_N  | Inverter Phase A Voltage N |  |

| 7                             | Grid-C_AOUT | Grid Phase C Current P     |  |

| 8                             | Grid-C_VREF | Grid Phase C Current N     |  |

| 9                             | Grid-B_AOUT | Grid Phase B Current P     |  |

| 10                            | Grid-B_VREF | Grid Phase B Current N     |  |

| 11                            | Grid-A_AOUT | Grid Phase A Current P     |  |

| 12                            | Grid-A_VREF | Grid Phase A Current N     |  |

| 13                            | Grid-C_IN_P | Grid Phase C Voltage P     |  |

| 14                            | Grid-C_IN_N | Grid Phase C Voltage N     |  |

| 15                            | Grid-B_IN_P | Grid Phase B Voltage P     |  |

| 16                            | Grid-B_IN_N | Grid Phase B Voltage N     |  |

| 17                            | Grid-A_IN_P | Grid Phase A Voltage P     |  |

| 18                            | Grid-A_IN_N | Grid Phase A Voltage N     |  |

| 19                            | RLY_C_B1    | Grid Phase B Relay Control |  |

| 20                            | RLY_C_A1    | Grid Phase A Relay Control |  |

| 21                            | RLY_C_N1    | Grid Phase N Relay Control |  |

| 22                            | RLY_C_C1    | Grid Phase C Relay Control |  |

| 23                            | +5VA        | Analog Power               |  |

| 24                            | AGND        | Analog Power               |  |

| 25                            | +24V        | Power                      |  |

| 26                            | GND         | Power                      |  |

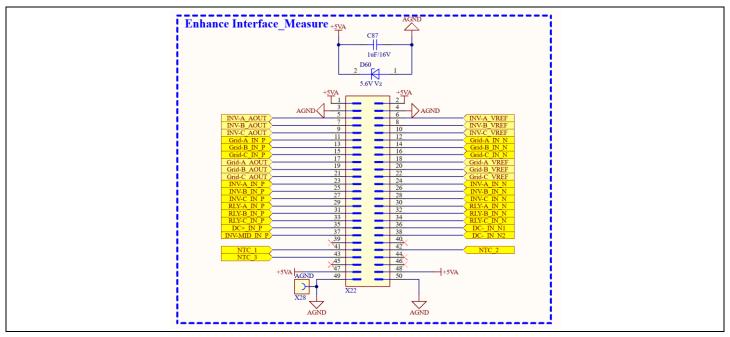

#### **Enhanced interface-Measure** 2.1.6.2

All the measurement signals are fed to the control board using connector X22 located on the power board.

Figure 29 Enhanced interface-Measure

Table 5 **Enhanced interface-Measure**

| Basic interface |             |                            |  |

|-----------------|-------------|----------------------------|--|

| Pin             | Signal      | Description                |  |

| 1               | +5VA        | Analog Power               |  |

| 2               | +5VA        | Analog Power               |  |

| 3               | AGND        | Analog Power               |  |

| 4               | AGND        | Analog Power               |  |

| 5               | INV-A AOUT  | Inverter Phase A Current P |  |

| 6               | INV-A VREF  | Inverter Phase A Current N |  |

| 7               | INV-B AOUT  | Inverter Phase B Current P |  |

| 8               | INV-B VREF  | Inverter Phase B Current N |  |

| 9               | INV-C AOUT  | Inverter Phase C Current P |  |

| 10              | INV-C VREF  | Inverter Phase C Current N |  |

| 11              | Grid-A_IN_P | Grid Phase A Voltage P     |  |

| 12              | Grid-A_IN_N | Grid Phase A Voltage N     |  |

| 13              | Grid-B_IN_P | Grid Phase B Voltage P     |  |

| 14              | Grid-B_IN_N | Grid Phase B Voltage N     |  |

| 15              | Grid-C_IN_P | Grid Phase C Voltage P     |  |

| 16              | Grid-C_IN_N | Grid Phase C Voltage N     |  |

| 17              | Grid-A AOUT | Grid Phase A Current P     |  |

| 18              | Grid-A VREF | Grid Phase A Current N     |  |

| 19              | Grid-B AOUT | Grid Phase B Current P     |  |

| 20              | Grid-B VREF | Grid Phase B Current N     |  |

| 21 | Grid-C AOUT  | Grid Phase C Current P     |

|----|--------------|----------------------------|

| 22 | Grid-C VREF  | Grid Phase C Current N     |

| 23 | INV-A_IN_P   | Inverter Phase A Voltage P |

| 24 | INV-A_IN_N   | Inverter Phase A Voltage N |

| 25 | INV-B_IN_P   | Inverter Phase B Voltage P |

| 26 | INV-B_IN_N   | Inverter Phase B Voltage N |

| 27 | INV-C_IN_P   | Inverter Phase C Voltage P |

| 28 | INV-C_IN_N   | Inverter Phase C Voltage N |

| 29 | RLY-A_IN_P   | Relay Phase A Voltage P    |

| 30 | RLY-A_IN_N   | Relay Phase A Voltage N    |

| 31 | RLY-B_IN_P   | Relay Phase B Voltage P    |

| 32 | RLY-B_IN_N   | Relay Phase B Voltage N    |

| 33 | RLY-C_IN_P   | Relay Phase C Voltage P    |

| 34 | RLY-C_IN_N   | Relay Phase C Voltage N    |

| 35 | DC+_IN_P     | Bus+ Voltage P             |

| 36 | DCIN_N1      | Bus+ Voltage N             |

| 37 | INV-MID_IN_P | Bus- Voltage P             |

| 38 | DCIN_N2      | Bus- Voltage N             |

| 39 | NC           | NC                         |

| 40 | NC           | NC                         |

| 41 | NC           | NC                         |

| 42 | NC           | NC                         |

| 43 | NTC1         | NTC1                       |

| 44 | NTC2         | NTC2                       |

| 45 | NTC3         | NTC3                       |

| 46 | NC           | NC                         |

| 47 | +5VA         | Analog Power               |

| 48 | +5VA         | Analog Power               |

| 49 | AGND         | Analog Power               |

| 50 | AGND         | Analog Power               |

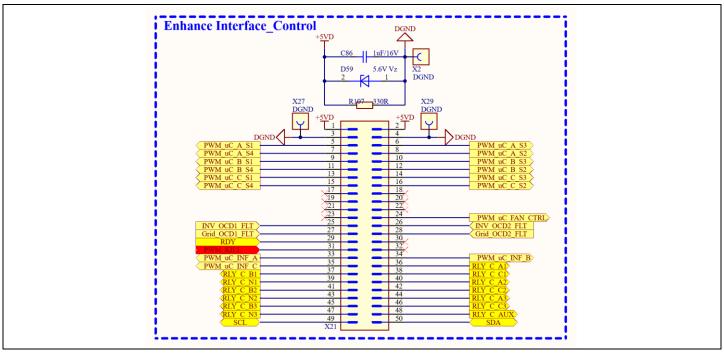

## 2.1.6.3 Enhanced interface-control

Connector X21 contains all the signals related to the PWMs, faults and relay control.

Figure 30 Enhanced interface-control

Table 6 **Enhanced interface-control**

| rable 6         | nnanced interface-control |                |

|-----------------|---------------------------|----------------|

| Basic interface |                           |                |

| Pin             | Signal                    | Description    |

| 1               | +5VD                      | Digtial Power  |

| 2               | +5VD                      | Digtial Power  |

| 3               | DGND                      | Digtial Power  |

| 4               | DGND                      | Digtial Power  |

| 5               | PWM_uC_A_S1               | Phase A T1 PWM |

| 6               | PWM_uC_A_S3               | Phase A T3 PWM |

| 7               | PWM_uC_A_S4               | Phase A T4 PWM |

| 8               | PWM_uC_A_S2               | Phase A T2 PWM |

| 9               | PWM_uC_B_S1               | Phase B T1 PWM |

| 10              | PWM_uC_B_S3               | Phase B T3 PWM |

| 11              | PWM_uC_B_S4               | Phase B T4 PWM |

| 12              | PWM_uC_B_S2               | Phase B T2 PWM |

| 13              | PWM_uC_C_S1               | Phase C T1 PWM |

| 14              | PWM_uC_C_S3               | Phase C T3 PWM |

| 15              | PWM_uC_C_S4               | Phase C T4 PWM |

| 16              | PWM_uC_C_S2               | Phase C T2 PWM |

| 17              | NC                        | NC             |

| 18              | NC                        | NC             |

| 19              | NC                        | NC             |

| 20              | NC                        | NC             |

| 21              | NC                        | NC             |

| 22              | NC                        | NC             |

| 23 | NC              | NC                               |

|----|-----------------|----------------------------------|

| 24 | PWM_uC_FAN_CTRL | NPC2 FAN Control                 |

| 25 | INV_OCD1_FLT    | Inv Current Sensor ODC1 Combine  |

| 26 | INV_OCD1_FLT    | Inv Current Sensor ODC2 Combine  |

| 27 | Grid_OCD1_FLT   | Grid Current Sensor ODC1 Combine |

| 28 | Grid_OCD2_FLT   | Grid Current Sensor ODC2 Combine |

| 29 | RDY             | NC                               |

| 30 | NC              | NC                               |

| 31 | PWM_KILL        | PWM Kill                         |

| 32 | NC              | NC                               |

| 33 | PWM_uC_INF_A    | Phase A Gate Driver Control      |

| 34 | PWM_uC_INF_B    | Phase B Gate Driver Control      |

| 35 | PWM_uC_INF_C    | Phase C Gate Driver Control      |

| 36 | RLY_C_A1        | Grid Phase A Relay Control       |

| 37 | RLY_C_B1        | Grid Phase B Relay Control       |

| 38 | RLY_C_C1        | Grid Phase C Relay Control       |

| 39 | RLY_C_N1        | Grid Phase N Relay Control       |

| 40 | RLY_C_A2        | Bypass Phase A Relay Control     |

| 41 | RLY_C_B2        | Bypass Phase B Relay Control     |

| 42 | RLY_C_C2        | Bypass Phase C Relay Control     |

| 43 | RLY_C_N2        | Bypass Phase N Relay Control     |

| 44 | RLY_C_A3        | Inverter Phase A Relay Control   |

| 45 | RLY_C_B3        | Inverter Phase B Relay Control   |

| 46 | RLY_C_C3        | Inverter Phase C Relay Control   |

| 47 | RLY_C_N3        | Inverter Phase N Relay Control   |

| 48 | RLY_C_AUX       | Pre-Charge Rlay Control          |

| 49 | I2C2_SCL        | Gate Driver Config (If needed)   |

| 50 | I2C2_SDA        | Gate Driver Config (If needed)   |

#### **Isolation coordination** 2.7

The 10 kW NPC2 inverter reference design follows a hot-side control structure where all the measurements and the gate-drive power supply offer functional isolation. Two microcontrollers are used then on the board where one is responsible for the control of the converter. A digital isolator is then implemented and a second microcontroller that the user can deal with safely is used for communication. IEC 62109-1 was used for clearance and creepage requirements.

#### **Testing** 3

The testing of the 10 kW NPC2 inverter reference design was done using the XMC7200-based power control board reference design REF-CLBXMC7PEC that can be purchased separately. It was operated in open loop and tested using a resistive load. The filter board of the converter is not optimized to be used with AC electronic loads, the user needs to stick to resistive loads while using the 10 kW NPC2 kit.

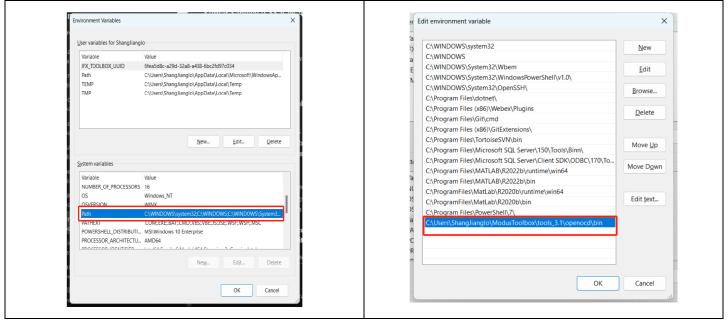

#### 3.1 Flashing the firmware

### Steps to flash the firmware:

- 1. Connect 24 V to the control board

- 2. Add three jumper headers like shown in figure 31

- 3. Connect the debug port of the control board to PC using a USB cable

Figure 31 **REF-CLBXMC7PEC debug configuration**

- Install ModusToolbox™ software

- 5. Add windows system path variable as shown below:

Figure 32 Adding environment variable

- 6. Start the command prompt on your PC and type 'openocd' to verify that the previous steps were made correctly

- 7. Type the following using the address of the location where the firmware is located on your PC:

openocd -s ../scripts -f interface/kitprog3.cfg -f target/cat1c.cfg -c "program C:/Users/AN/Desktop/Firmware/app\_combined.hex verify exit"

**Note:** The user needs to change this path (C:/Users/AN/Desktop/Firmware/app\_combined.hex verify exit) to their own

```

## Actic cou col cortex. little catic cou unknown

1 catic cou cell cortex. little catic cou unknown

2 catic cou cell cortex. little catic cou unknown

2 catic cou cell cortex. little catic cou unknown

3 stitle catic cou cell unknown

4 stitle catic cou unknown

5 c'. Ulyers. Shang, lang (whodus foolbox (tools, 3.1 Nooenocd/bin> openocd -s . ./scripts -f interface/kitprog3.cfg -f target/c

atic. cfg -c 'program C:/MTB. Nooekopace/Gazetle_Base/Nuild/gazetle_get_start.hex verify exit*

Upen un-thip Uebugger v1.2 unknows, sub. July (12025-08-16-09128)

Licensed under GNU GPL v2

For bugg http://popend.org/doc/doxygan/bugs.html

Info: auto-scletting first available session transport "swd". To override use 'transport select <transport>'. adapter sest delay. 25

adapter sest delay. 25

** Auto-acquire enabled, use 'set EMBRE. ACQUIRE 0* to disable

Confo: using CRIST-ORD2 interface sith VID:PID=0x08bt:0xf155, serial=13280EB5931F1408

Info: CRIST-DAP: SNO supported

Info: CRIST-DAP: SNO province commands supported

Info: KRIST-DAP: SNO provinc

```

Figure 33 Flashing the firmware

```

irmwane is out of date, please update to the latest version (2.50.1401)

loader tool which can be found in the following folder

pn/Tools/ModusToolboxProgtools-1.0/fw-loader

\ShangJianglo\ModusToolbox\tools_3.1\openocd\bin>|

```

Figure 34 Flashing the firmware

- Remove the jumpers present on the control board

- Disconnect the external 24V power supply

- 10. Connect the USB cable to the commissioning port instead of the debug port

#### 3.2 Control

The firmware allows the user to operate the NPC2 in open loop using SPWM scheme. The firmware also allows the user to change the modulation index.

#### 3.3 **GUI**

#### **Establishing communication** 3.3.1

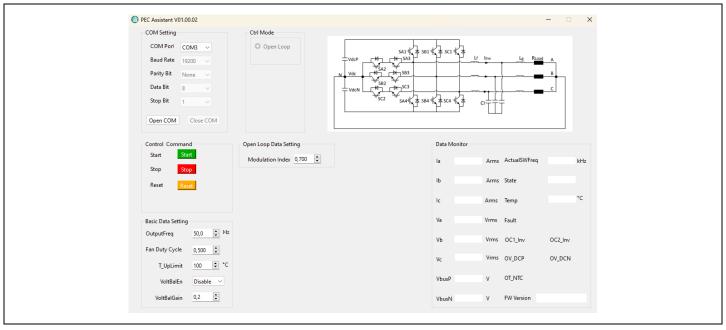

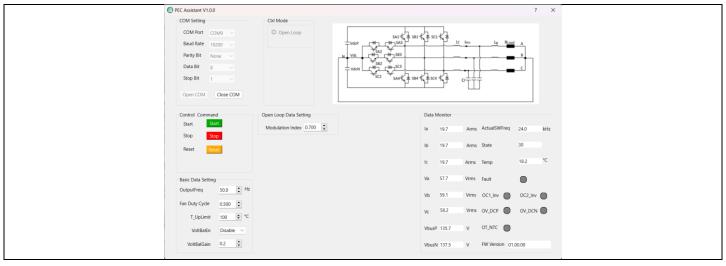

The GUI can be seen in figure 35:

Figure 35 **GUI**

## Steps to establish connection between PC and control board:

1. Make sure that the NPC2 board and the control board are connected as shown in the upcoming Bench setup section

The signal cables from the power board provide the control board with power, no external power supply is needed to be connected to the control board

2. Connect an external 24V to the power board of the NPC2

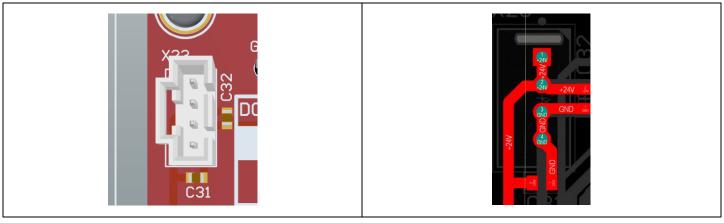

Figure 36 24V connector

3. Open the GUI and log in and choose normal mode, the password is 123456

Figure 37 Logging in

- 4. In the COM port setting in the GUI, choose the COM port the control board is connected to, the user can check that in the device manager

- 5. If everything is set correctly the right section (Measurement section) will start showing values

- 6. Once the bench setup is set, the user can press start to start evaluating the hardware

Figure 38 **GUI after successful connection**

#### 3.3.2 **GUI parameters**

#### Table 7 **GUI parameters**

| Pin                     | Signal                                                          | Range         |

|-------------------------|-----------------------------------------------------------------|---------------|

| Open COM                | Establish communication between the GUI and the microcontroller |               |

| Start                   | Start the inverter                                              |               |

| Stop                    | Stop the inverter                                               |               |

| Reset                   | Reset faults                                                    |               |

| Output frequency        | Adjust the output frequency between (40Hz and 65 Hz)            | 40 Hz – 65 Hz |

| Fan Duty Cycle          | Adjust the duty cycle of the fans mounted on the heatsink       | 0 – 1         |

| T_Upl Limit             | Set temperature protection threshold                            | 0 – 200       |

| VoltBalEn               | Enable the voltage balancing function for the DC-link           | 0 or 1        |

| VoltBalGain             | Set the DC link voltage balance control gain                    | 0 – 20        |

| <b>Modulation Index</b> | Set the modulation index for open-loop operation                | 0 – 1         |

| l <sub>a</sub>          | Phase a measured current                                        |               |

| l <sub>b</sub>          | Phase b measured current                                        |               |

| I <sub>c</sub>          | Phase c measured current                                        |               |

| $V_a$                   | Not implemented (Future development)                            |               |

| $V_b$                   | Not implemented (Future development)                            |               |

| $V_c$                   | Not implemented (Future development)                            |               |

| OC1_Inv                 | Hardware over current protection                                |               |

| OC1_Inv                 | Software overcurrent protection                                 |               |

| OV_DCP                  | DC bus positive over voltage protection                         |               |

| OV_DCN                  | DC bus negative over voltage protection                         |               |

| VbusP                   | Measured voltage on the upper DC-link                           |               |

| VbusN                   | Measured voltage on the lower DC-link                           |               |

#### 3.4 Open-loop test results

#### 3.4.1 **Bench setup**

The inverter is operated in open-loop, caution must be taken in order not to accidently operate the inverter outside the voltages, currents and frequencies specified. The inverter was tested only for the specifications shown in table 2 with a resistive load. In case the user decides to operate outside these specifications, performance is not guaranteed. The firmware gives the user the possibility of using a DC-link voltage balancing function, the user needs to increase the DC-link voltage gradually, monitor it and decide to use it in case it is needed.

### The following equipment are needed to start testing:

- 10 kW NPC2 kit

- REF-CLBXMC7PEC kit with the NPC2 firmware

- GUI

- Resistive load: 3-phase star connected (Neutral is connected to DC-link mid-point)

- DC power source

Figure 39 **Test setup**

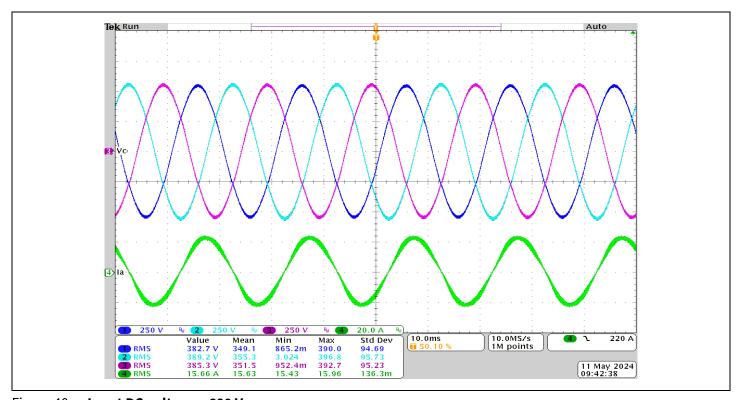

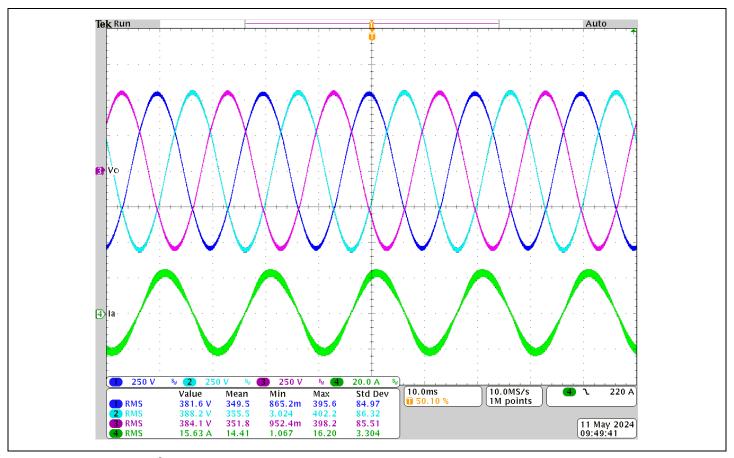

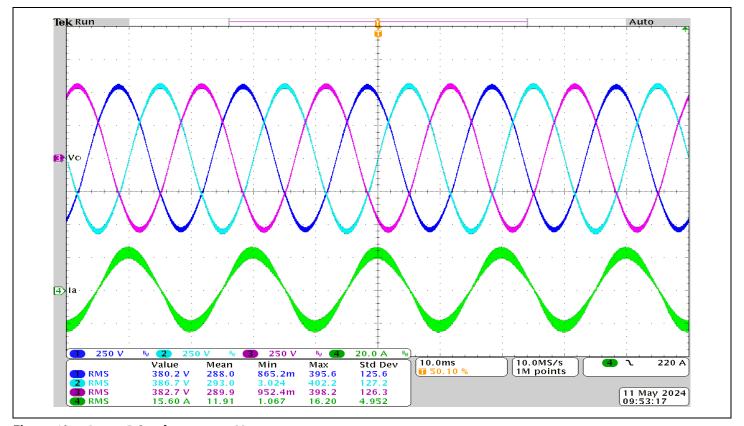

#### 3.4.2 Output AC voltage against different DC input voltages

The design was tested at 3 input DC voltages 680V, 750V and 850V. The output line to line rms voltage was kept at around 380 V at a power of 10 kW.

## Table 8 DC input voltage range

| Input voltage | 680,750 and 850 V <sub>dc</sub>                           |  |

|---------------|-----------------------------------------------------------|--|

| PWM           | SPWM, 24 kHz                                              |  |

| Output power  | 10 kW, V <sub>out</sub> =380 V <sub>I-I rms</sub> / 50 Hz |  |

### Table 9 Test data

| MI     | Input<br>voltage                                                                                     | Input<br>Power | Output Voltage<br>(V <sub>l-l rms</sub> ) |                | Output Current (A <sub>rms</sub> ) |                |                | Waveform       |           |

|--------|------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------|----------------|------------------------------------|----------------|----------------|----------------|-----------|

|        | (V <sub>dc</sub> )                                                                                   | (kW)           | <b>V</b> a                                | V <sub>b</sub> | <b>V</b> <sub>c</sub>              | l <sub>a</sub> | l <sub>b</sub> | l <sub>c</sub> |           |

| 0.95   | 680                                                                                                  | 10.89          | 382.7                                     | 389.2          | 385.3                              | 15.66          | 15.60          | 15.30          | Figure 36 |

| 0.87   | 750                                                                                                  | 10.85          | 381.6                                     | 388.2          | 384.1                              | 15.62          | 15.70          | 15.40          | Figure 37 |

| 0.77   | 850                                                                                                  | 10.79          | 380.2                                     | 386.7          | 382.7                              | 15.61          | 15.50          | 15.20          | Figure 38 |

| Legend | CH1: V <sub>I-I ab</sub> , CH2: V <sub>I-I bc</sub> , CH3: V <sub>I-I ca</sub> , CH4: I <sub>a</sub> |                |                                           |                |                                    |                |                |                |           |

Figure 40 Input DC voltage = 680 V

Figure 41 Input DC voltage = 750 V

Figure 42 Input DC voltage = 850 V

# 3.4.3 Auxiliary power supply output voltage against input DC-link voltage variation

Condition: A 24V power supply is connected externally, the 24V, 5V and 3.3V rails are then observed.

Table 10 Auxiliary power supply measurements

| DC BUS | 3.3V  | 5V   | 24V   |

|--------|-------|------|-------|

| (V)    | (V)   | (V)  | (V)   |

| 680    | 3.310 | 4.90 | 24.20 |

| 750    | 3.310 | 4.90 | 24.20 |

| 850    | 3.310 | 4.90 | 24.20 |

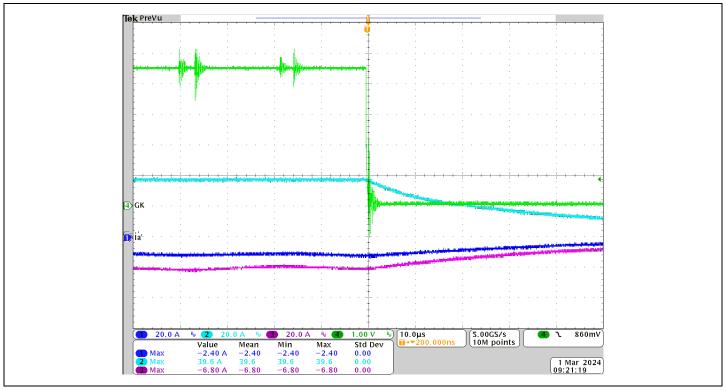

## 3.4.4 Over current protection

The output current is increased until the over current protection reacts. OCD trips when the peak current is 39.6A.

Legend: CH1: Iout-pha, CH2: Iout-phb, CH3: Iout-phc, CH4: GK

Figure 43 **Over current protection**

# 3.4.5 Efficiency measurement

## Table 1 Power semiconductors efficiency measurement

| Specification        | Efficiency measurement using Zimmer LMG 670 power analyzer                      |            |  |  |  |

|----------------------|---------------------------------------------------------------------------------|------------|--|--|--|

| Candition            | M=0.9, V <sub>phase</sub> =220 V, Loading = 10,20,30,50,75 and 100%             |            |  |  |  |

| Condition            | Measurements are taken before the LCL filter board (Power semiconductor losses) |            |  |  |  |

| Operation Efficiency |                                                                                 | Efficiency |  |  |  |

| 10% load             |                                                                                 | 97.8%      |  |  |  |

| 20% load             |                                                                                 | 98.3%      |  |  |  |

| 30% load             |                                                                                 | 98.4%      |  |  |  |

| 50% load             |                                                                                 | 98.5%      |  |  |  |

| 75% load             |                                                                                 | 98.5%      |  |  |  |

| 100% load            |                                                                                 | 98.4%      |  |  |  |

### **Board layout** 4

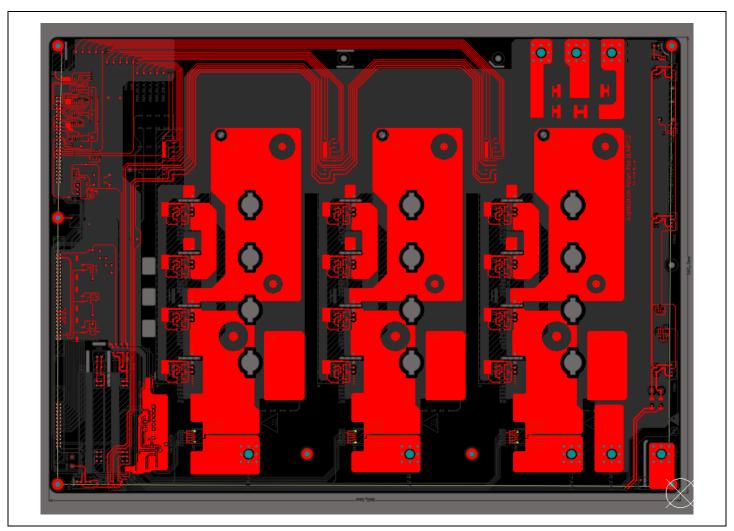

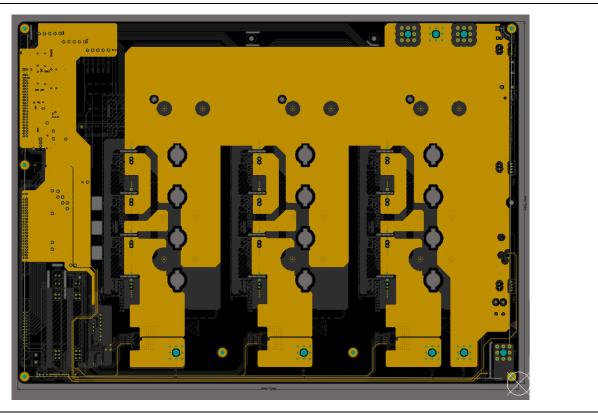

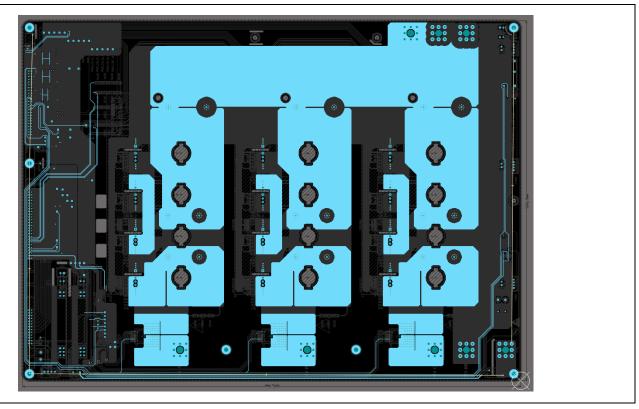

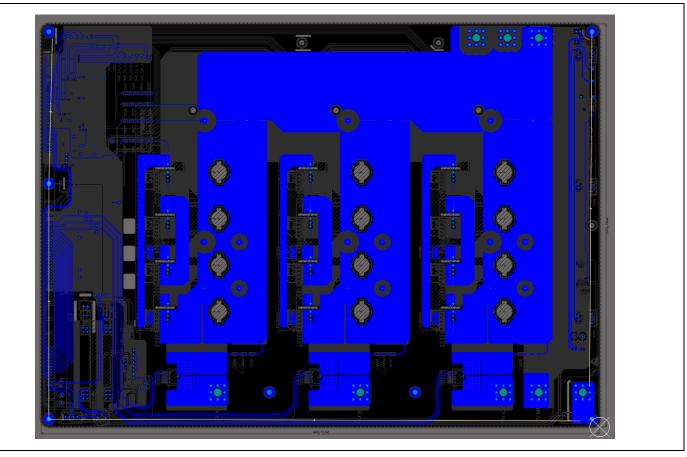

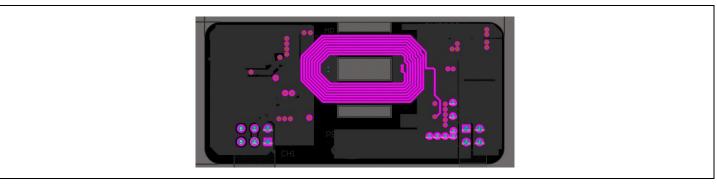

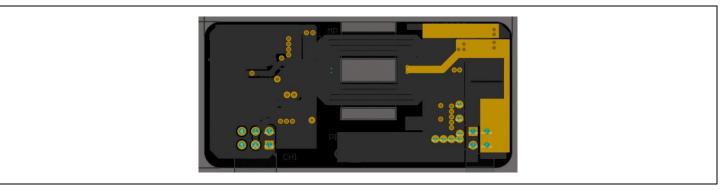

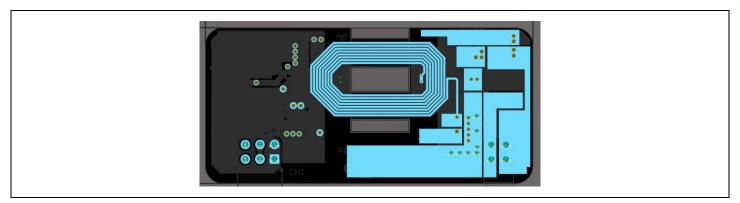

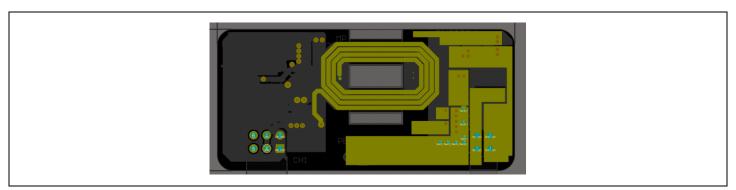

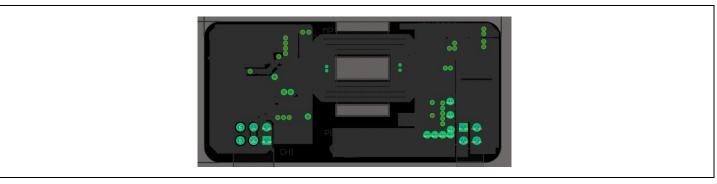

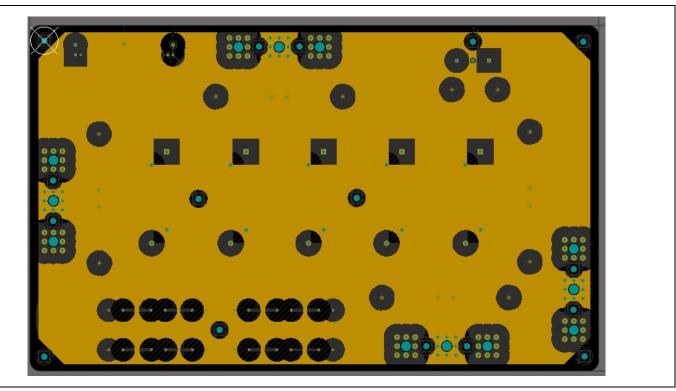

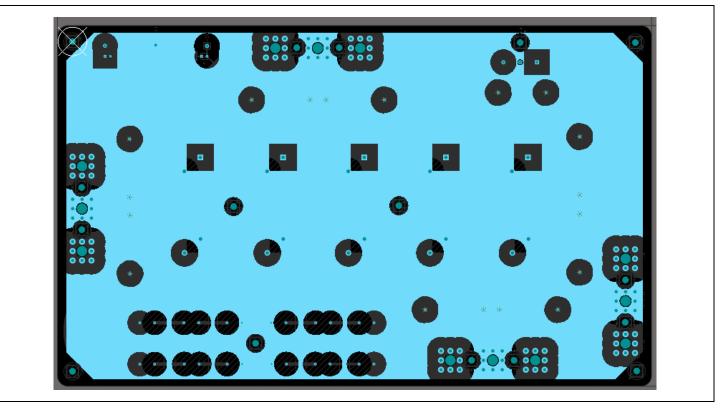

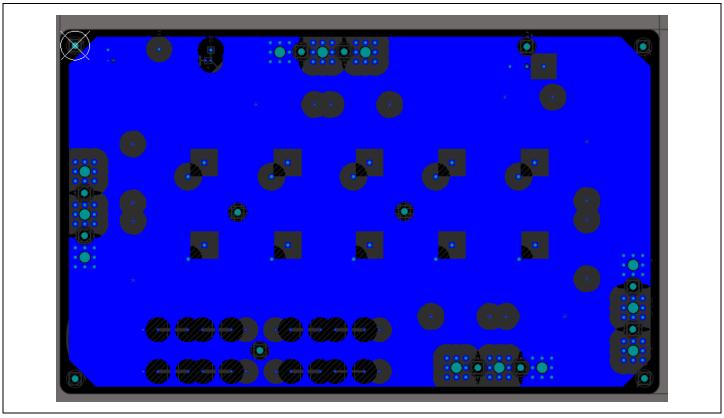

#### 4.1 **REF-10KW3LNPC2**

Table 2 **Mechanical data**

| Dimensions       | 260mm x 360mm |

|------------------|---------------|

| No. of layers    | 4             |

| Copper thickness | 140 μm        |

| Weight           | 8.5 kg        |

Figure 44 Layer 1

Figure 45 Layer 2

Figure 46 Layer 3

Figure 47 Layer 4

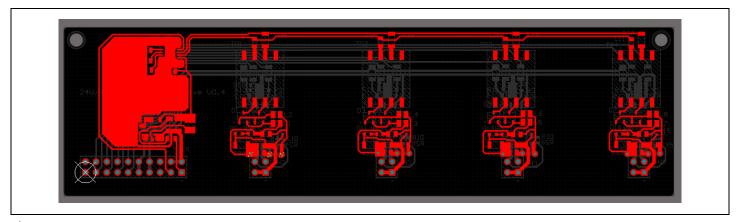

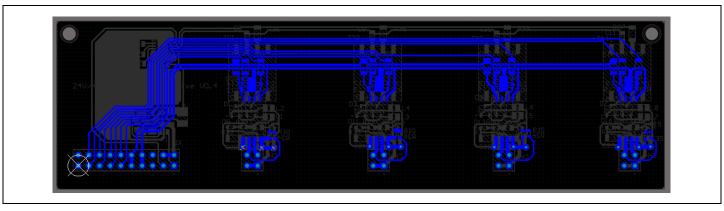

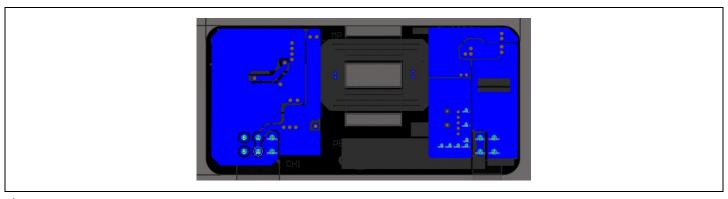

#### 4.2 ISODRV-3240C4P15N05-1

#### Table 3 **Mechanical data**

| Dimensions       | 145mm x 40mm |

|------------------|--------------|

| No. of layers    | 2            |

| Copper thickness | 35 μm        |

Figure 48 Layer 1

# 10 kW 3-level NPC2 inverter reference design REF-10KW3LNPC2

Figure 49 Layer 2

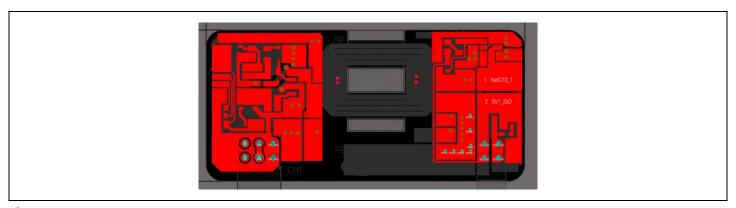

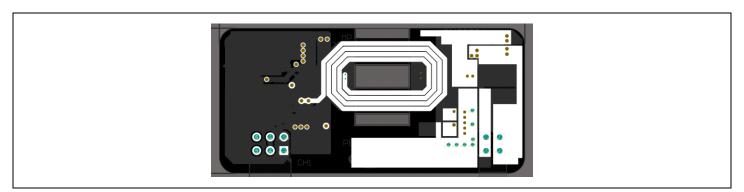

## 4.3 PB-APS-24V-5V ISO

Table 4 Mechanical data

| Dimensions       | 57.1mm x 27.1mm |

|------------------|-----------------|

| No. of layers    | 8               |

| Copper thickness | 105 μm          |

Figure 50 Layer 1

Figure 51 Layer 2

Figure 52 Layer 3

Figure 53 Layer 4

Figure 54 Layer 5

Figure 55 Layer 6

## 10 kW 3-level NPC2 inverter reference design REF-10KW3LNPC2

Figure 56 Layer 7

Figure 57 Layer 8

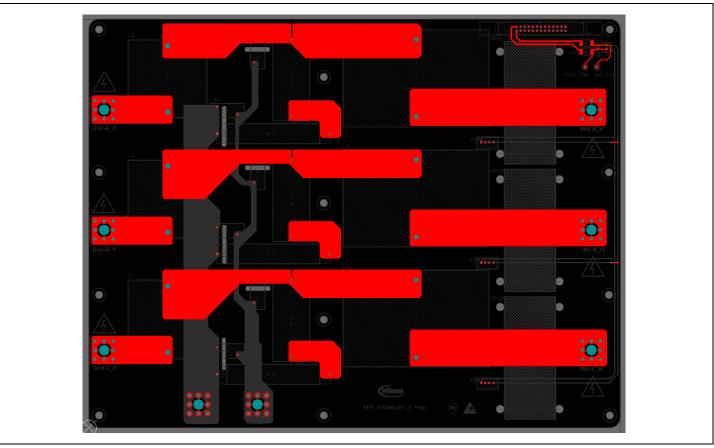

#### 4.4 **REF-10KW3LNPC2-Filter**

Table 5 **Mechanical data**

| Dimensions       | 260mm x 200mm |

|------------------|---------------|

| No. of layers    | 2             |

| Copper thickness | 70 μm         |

| Weight           | 3 kg          |

Figure 58 Layer 1

Figure 59 Layer 2

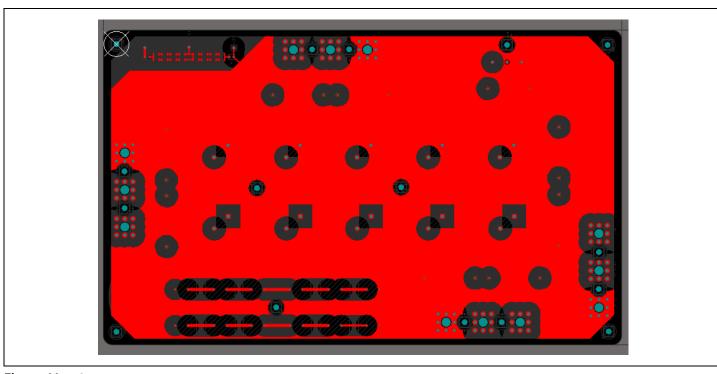

#### 4.5 **PB-CAPTANK-1.1KV**

Table 6 **Mechanical data**

| Dimensions       | 280mm x 170mm |

|------------------|---------------|

| No. of layers    | 4             |

| Copper thickness | 35 μm         |

| Weight           | 1.7 kg        |

Figure 60 Layer 1

Figure 61 Layer 2

Figure 62 Layer 3

Figure 63 Layer 4

## 10 kW 3-level NPC2 inverter reference design REF-10KW3LNPC2

### Bill of key materials 5

Table 7 BoM

| Part                   | Description                                                                                                                  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------|

| <u>IKZA40N120CH7</u>   | 1200 V, 40 A IGBT with anti-parallel diode in TO-247-4 package                                                               |

| IKZA40N65EH7           | 650 V, 40 A IGBT with anti-parallel diode in TO247-4 package                                                                 |

| 1ED3240MC12H           | 10 A, 5.7 kV (rms) single-channel isolated gate driver with two-level slew-<br>rate control, UL 1577 & VDE 0884-11 certified |

| TLI4971-A120T5-U-E0001 | High precision coreless current sensor for industrial applications                                                           |

| 2EP130R                | Full bridge transformer driver                                                                                               |

| <u>IRS27952</u>        | Half Bridge High Voltage Controller IC                                                                                       |

| <u>IRF7351</u>         | 60V Dual N-Channel HEXFET Power MOSFET in a SO-8 package                                                                     |

| TLE42744GS V33         | 3.3V LDO                                                                                                                     |

# 10 kW 3-level NPC2 inverter reference design REF-10KW3LNPC2

# **Revision history**

| Document version | Date of release | Description of changes |

|------------------|-----------------|------------------------|

| V.1.0            | 2024-08-07      | Initial release        |

|                  |                 |                        |

|                  |                 |                        |

Edition 2024-08-07

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2024 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference UG-2024-09 For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

## WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

### Trademarks