# **Package Thermal Datasheet**

PG-VQFN-48-31

### About this document

This document aims at providing information about the thermal characteristics of the Infineon package PG-VQFN-48-31, used for Infineon Embedded Power ICs (Grade-1). The document contains details regarding dimensions, package outline, products involved, and a detailed overview of the thermal resistance characteristics of the package.

### Intended audience

This document is intended for customers who would like to have information of the thermal characteristics of the package used, and the products making use of it.

### Disclaimer

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

## **Table of Contents**

| About this      | s document                                                                                         | 1  |

|-----------------|----------------------------------------------------------------------------------------------------|----|

| Table of C      | ontents                                                                                            | 2  |

| 1               | Package Dimensions                                                                                 |    |

| 2               | List of Embedded Power Products in PG-VQFN-48-31                                                   |    |

| 3               | Thermal Resistance Definition                                                                      | 6  |

| 3.1             | Package only                                                                                       | 7  |

| 3.1.1           | Junction-to-case thermal resistance (R <sub>th-Jc</sub> )                                          | 7  |

| 3.2             | With PCB and housing                                                                               | 7  |

| 3.2.1           | Junction-to-ambient thermal resistance (R <sub>th-JA 2s2p</sub> )                                  |    |

| 3.2.2           | Junction-to-ambient thermal resistance (Rth-JA 150p)/footprint only                                | 7  |

| 3.2.3           | Junction-to-ambient thermal resistance (R <sub>th-JA 1s0p</sub> )/1000mm <sup>2</sup> cooling area | 8  |

| 3.2.4           | Junction-to-housing thermal resistance (R <sub>th-JH1</sub> )                                      | 8  |

| 3.2.5           | Junction-to-housing thermal resistance (R <sub>th-JH2</sub> )                                      | 8  |

| 4               | Thermal Characteristics                                                                            |    |

| 4.1             | Thermal Impedance                                                                                  | 9  |

| 4.2             | Temperature Distributions                                                                          | 10 |

| 4.3             | Impact of thermal vias                                                                             |    |

| Glossary        |                                                                                                    | 12 |

| <b>Revision</b> | listory                                                                                            | 13 |

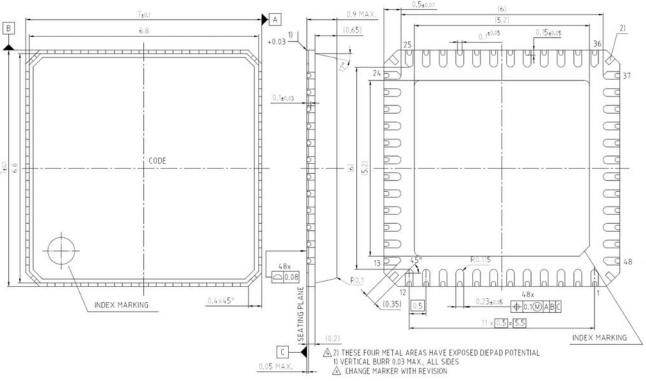

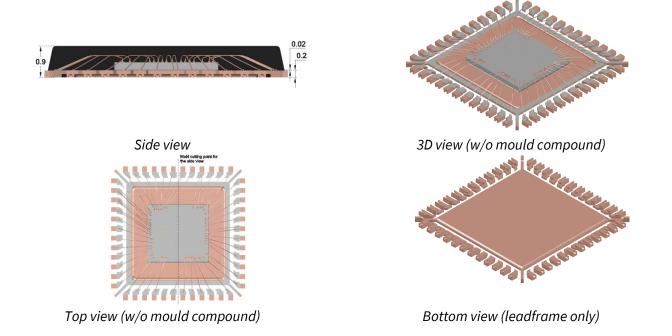

Figure 1: Package outline drawing for PG-VQFN-48-31 with dimensions

# 2 List of Embedded Power Products in PG-VQFN-48-31

### Relay Driver IC with Integrated Arm<sup>®</sup> Cortex<sup>®</sup>-M0

| Product name | Flash<br>[KB] | Freq<br>[MHz] | RAM<br>[KB] | EEPROM in<br>Flash incl.<br>[KB] | High-side<br>switch | High voltage<br>monitor input | Interface |

|--------------|---------------|---------------|-------------|----------------------------------|---------------------|-------------------------------|-----------|

| TLE9842QX    | 36            | 25            | 2           | 4                                | 1                   | 4                             | PWM + LIN |

| TLE9842-2QX  | 40            | 40            | 2           | 4                                | 2                   | 5                             | PWM + LIN |

| TLE9843QX    | 48            | 25            | 4           | 4                                | 1                   | 4                             | PWM + LIN |

| TLE9843-2QX  | 52            | 40            | 4           | 4                                | 2                   | 5                             | PWM + LIN |

| TLE9844QX    | 64            | 25            | 4           | 4                                | 1                   | 4                             | PWM + LIN |

| TLE9844-2QX  | 64            | 40            | 4           | 4                                | 2                   | 5                             | PWM + LIN |

### Half-Bridge Driver IC with Integrated Arm<sup>®</sup> Cortex<sup>®</sup>-M0

| Product name | Flash<br>[KB] | Freq<br>[MHz] | RAM<br>[KB] | EEPROM in<br>Flash incl.<br>[KB] | High-<br>side<br>switch | High<br>voltage<br>monitor<br>input | PN<br>MOS<br>driver | Low-<br>side<br>MOSFET<br>drivers | High-side<br>MOSFET<br>drivers | Interface |

|--------------|---------------|---------------|-------------|----------------------------------|-------------------------|-------------------------------------|---------------------|-----------------------------------|--------------------------------|-----------|

| TLE9845QX    | 48            | 40            | 4           | 4                                | 2                       | 5                                   | YES                 | -                                 | -                              | PWM + LIN |

| TLE9850QX    | 48            | 40            | 4           | 4                                | 1                       | 4                                   | NO                  | 1                                 | 1                              | PWM + LIN |

### H-Bridge Driver IC with Integrated Arm<sup>®</sup> Cortex<sup>®</sup> M0

| Product<br>name | Flash<br>[KB] | Freq<br>[MHz] | RAM<br>[KB] | EEPROM<br>in Flash<br>incl. [KB] | High-<br>side<br>switch | High<br>voltage<br>monitor<br>input | Low-<br>side<br>MOSFET<br>drivers | High-side<br>MOSFET<br>drivers | Interface |

|-----------------|---------------|---------------|-------------|----------------------------------|-------------------------|-------------------------------------|-----------------------------------|--------------------------------|-----------|

| TLE9853QX       | 48            | 40            | 4           | 4                                | 1                       | 4                                   | 2                                 | 2                              | PWM + LIN |

| TLE9854QX       | 64            | 40            | 4           | 4                                | 1                       | 4                                   | 2                                 | 2                              | PWM + LIN |

| TLE9855QX       | 96            | 40            | 4           | 4                                | 1                       | 4                                   | 2                                 | 2                              | PWM + LIN |

| TLE9852QX       | 48            | 40            | 4           | 4                                | 1                       | 4                                   | 2                                 | 2                              | PWM + LIN |

### H-Bridge Driver with Integrated Arm® Cortex®-M3

| Product name | Flash<br>[KB] | Freq<br>[MHz] | RAM<br>[KB] | EEPROM in<br>Flash incl.<br>[KB] | OP-<br>AMP | SD-<br>ADC | Low-side<br>MOSFET<br>drivers | High-side<br>MOSFET<br>drivers | Interface |

|--------------|---------------|---------------|-------------|----------------------------------|------------|------------|-------------------------------|--------------------------------|-----------|

| TLE9861QXA20 | 36            | 24            | 3           | 4                                | YES        | -          | 2                             | 2                              | PWM       |

| TLE9862QXA40 | 256           | 40            | 8           | 4                                | YES        | -          | 2                             | 2                              | PWM + LIN |

| TLE9867QXA20 | 64            | 24            | 6           | 4                                | YES        | -          | 2                             | 2                              | PWM + LIN |

| TLE9867QXA40 | 64            | 40            | 6           | 4                                | YES        | -          | 2                             | 2                              | PWM + LIN |

| TLE9868QXB20 | 128           | 20            | 4           | 4                                | YES        | YES        | 2                             | 2                              | PWM + LIN |

| TLE9869QXA20 | 128           | 24            | 6           | 4                                | YES        | -          | 2                             | 2                              | PWM + LIN |

### 3-Phase Bridge Driver with Integrated Arm® Cortex®-M3

| Product name   | Flash<br>[KB] | Freq<br>[MHz] | RAM<br>[KB] | EEPROM<br>in Flash<br>incl. [KB] | OP-<br>AMP | SD-<br>ADC | Low-side<br>MOSFET<br>drivers | High-side<br>MOSFET<br>drivers | Interface |

|----------------|---------------|---------------|-------------|----------------------------------|------------|------------|-------------------------------|--------------------------------|-----------|

| TLE9871QXA20   | 36            | 24            | 3           | 4                                | YES        | -          | 3                             | 3                              | PWM       |

| TLE9872QXA40   | 256           | 40            | 8           | 4                                | YES        | -          | 3                             | 3                              | PWM + LIN |

| TLE9872-2QXA40 | 256           | 40            | 8           | 4                                | YES        | YES        | 3                             | 3                              | PWM + LIN |

| TLE9877QXA20   | 64            | 24            | 6           | 4                                | YES        | -          | 3                             | 3                              | PWM + LIN |

| TLE9877QXA40   | 64            | 40            | 6           | 4                                | YES        | -          | 3                             | 3                              | PWM + LIN |

| TLE9879QXA20   | 128           | 24            | 6           | 4                                | YES        | -          | 3                             | 3                              | PWM + LIN |

| TLE9879QXA40   | 128           | 40            | 6           | 4                                | YES        | -          | 3                             | 3                              | PWM + LIN |

| TLE9879-2QXA40 | 128           | 40            | 6           | 4                                | YES        | YES        | 3                             | 3                              | PWM + LIN |

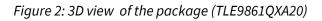

# **3** Thermal Resistance Definition

Package thermal resistance is the measure of a package's heat dissipation capability from a die's active surface (junction) to a specified reference point (case, pin, ambient, etc.). The value of thermal resistance depends on many factors, such as ambient temperature, PCB board used and much more. This chapter describes in details boundary conditions we use in the definition of various thermal resistances.

We divide thermal resistance into two groups: junction-to-case thermal resistance (package only) and junction-to-ambient thermal resistance (with PCB and housing). Below table shows the overview.

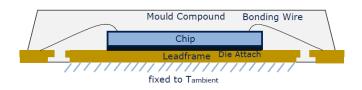

Figure 3: Boundary conditions for thermal resistance definition for package only (left column) and with PCB and housing (right column)

## 3.1 Package only

## 3.1.1 Junction-to-case thermal resistance (R<sub>th-Jc</sub>)

• The backside of the exposed pads is fixed to Tambient

• The other side of the package has an adiabatic boundary condition

## 3.2 With PCB and housing

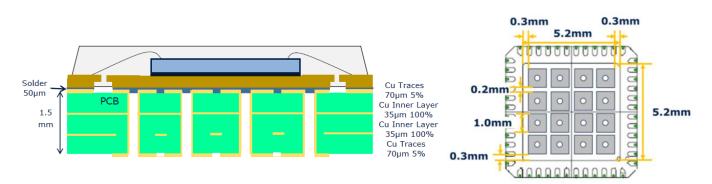

### **3.2.1** Junction-to-ambient thermal resistance (R<sub>th-JA 2s2p</sub>)

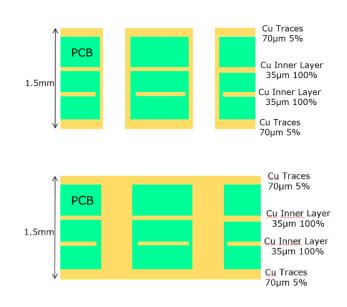

- Only JEDEC (Joint Electron Device Engineering Council) board is used for thermal assessment. PCB construction is according to JEDEC standards 2s2p, with thermal vias placed under exposed pad as much as possible.

- PCB size 74\*116\*1.5 mm

- Number of thermal vias 16. Thermal vias are connected to only one Cu inner layer

- Natural Convection

Figure 4: R<sub>th-JA 2s2p</sub> schematic and top view of JEDEC thermal vias.

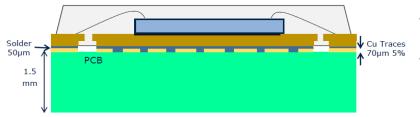

## 3.2.2 Junction-to-ambient thermal resistance (R<sub>th-JA 1sop</sub>)/footprint only

- PCB construction is according to JEDEC standards 1s0p, without thermal vias

- Natural Convection

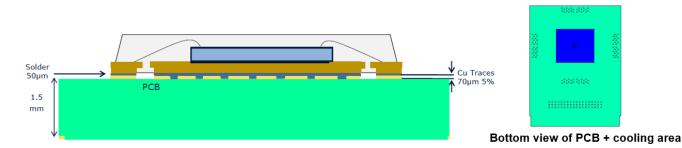

# 3.2.3 Junction-to-ambient thermal resistance (R<sub>th-JA 1s0p</sub>)/1000mm<sup>2</sup> cooling area

- PCB construction is according to JEDEC 1s0p, without thermal vias

- standards 300mm<sup>2</sup> (or 600mm<sup>2</sup> or 1000mm<sup>2</sup>) cooling Cu is connected to the exposed pad on the first PCB layer

- Natural Convection

*Figure 5: R*<sub>th-JA 1s0p</sub> with 1000mm<sup>2</sup> Cu cooling area schematic and bottom view of PCB and cooling area.

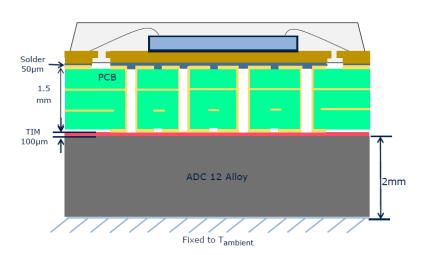

### 3.2.4 Junction-to-housing thermal resistance (R<sub>th-JH1</sub>)

- The backside of the housing is fixed to T<sub>ambient</sub>

- PCB construction is according to JEDEC standards 2s2p, with thermal vias (same as R<sub>th-JA 2s2p</sub>)

- TIM (100µm, 0,7W/mK, X and Y size is double of the package size)

- Housing: 2mm thick, X and Y the same as JEDEC 2s2p board, 92W/mK (alloy name: ADC12)

## 3.2.5 Junction-to-housing thermal resistance (R<sub>th-JH2</sub>)

- The backside of the housing has natural convection

- PCB construction is according to JEDEC standards 2s2p, with thermal vias (same as R<sub>th-JA2s2p</sub>)

- TIM (100µm, 0,7W/mK, X and Y size is double of the package size)

- Housing: 2mm thick, X and Y the same as JEDEC 2s2p board, 92W/mK (alloy name: ADC12)

## 4 Thermal Characteristics

### 4.1 Thermal Impedance

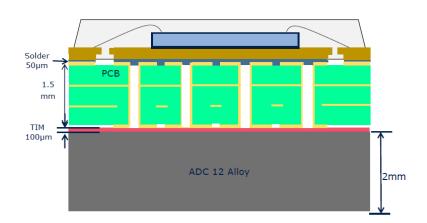

To emphasis the impact of housing, Figure 6 shows the schematic once again. And in Figure 7, thermal impedance for TLE984x families (left) and for TLE986x/7x families (right) are presented. Please refer to chapter 3 to know the concrete boundary conditions in the definition of each thermal resistance.

Figure 6: Plastic and metal housing schematics

*Figure 7: Thermal impedance for TLE984x (top left), for TLE986x/7x (top right) and for TLE985x families (lbottom)*

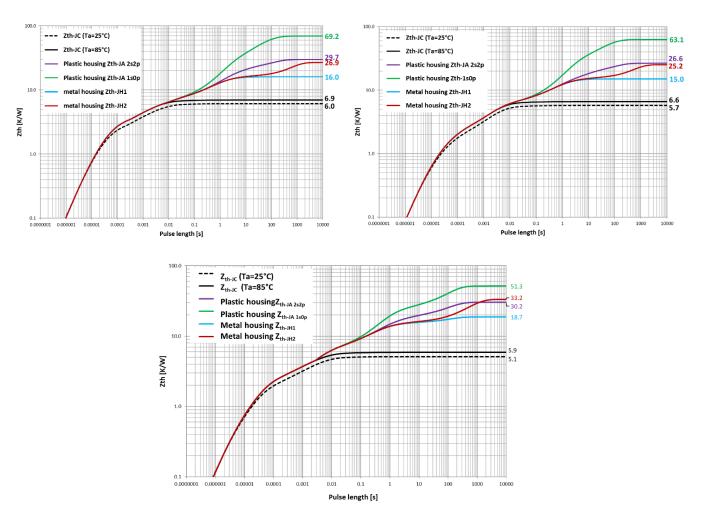

### 4.2 Temperature Distributions

The temperature distribution in steady state for the setup with metal housing with natural convection at back side as defined in  $R_{th-JH2}$  (see section 3.2.5), is shown below for TLE986x/7x families. All temperatures are in Kelvin. TLE984x families have the similar results.

*Figure 8: Temperature distribution at steady state for the setup with metal housing and natural convection at the back - top view (left) and side view (right).*

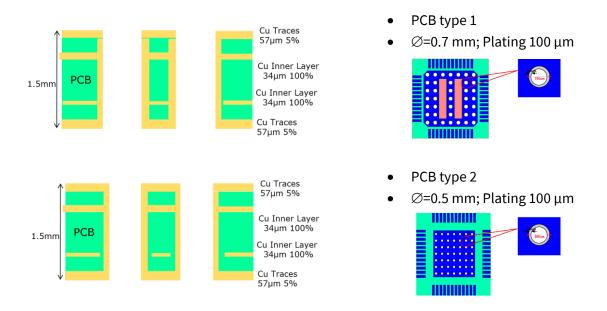

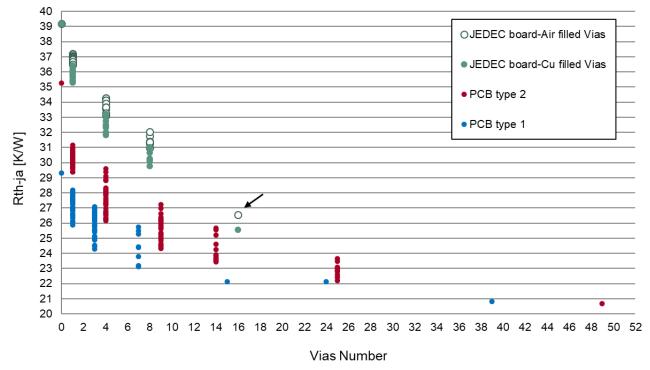

## 4.3 Impact of thermal vias

Thermal vias offer thermal short paths within PCB to imporve heat transfer from device to ambient. Besides JEDEC 2s2p board with air-filled and Cu-filled thermal vias, we extended our study on another 2 PCB, noted as PCB type 1 and PCB type 2. The cross section pictures in Figure 9 shows the differences in all set up. The size of PCBs are fixed at 74\*116\*1.5 mm as in JEDEC standard.

- JEDEC board-Air in vias

- Ø=0.3 mm; Plating 25 μm

- JEDEC board-Cu in vias

- $\emptyset$ =0.3 mm; Plating 25  $\mu$ m

Figure 9: Cross section information of PCB investigated and their thermal vias

Figure 10 is the calculated results of junction to ambient thermal resistance (R<sub>th-JA</sub>) for different PCB types. Obviously the more number of vias, the lower Rth-JA. Cu-filled vias are slightly better than air-filled vias for JEDEC board. When increasing thermal via diameters and thicker plating wall within the vias, Rth-JA is also improved. Therefore PCB type 1 gives the lowest Rth-JA.

In Chapter 4, all the thermal impedances of our products are calculated with the maximum number of vias in JEDEC board, where an arrow is pointing to on this chart.

# Glossary

| R <sub>th</sub> | Thermal Resistance                                                                                                                                                                                                                                                          |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $T_{ambient}$   | Ambient Temperature                                                                                                                                                                                                                                                         |

| JEDEC           | Joint Electron Device Engineering Council                                                                                                                                                                                                                                   |

| PCB             | Printed Circuit Board                                                                                                                                                                                                                                                       |

| 2s2p            | JEDEC standard two internal copper planes embedded in the circuit board and the trace layer on<br>the top surface of the PCB, 's' refers to the signal layers on both outside surfaces of the board and<br>'p' refers to two power planes in the board (voltage and ground) |

| 1s0p            | JEDEC standard no internal copper planes embedded in the circuit board and the trace layer on the top surface of the PCB                                                                                                                                                    |

| ADC             | Aluminium Alloy Die Casting                                                                                                                                                                                                                                                 |

| ТІМ             | Thermal Interface Material                                                                                                                                                                                                                                                  |

# **Revision History**

### Major changes since the last revision

| Page or Reference | Description of change                               |

|-------------------|-----------------------------------------------------|

| Revision 3.0      | 2020-11-04 – Additonal products included (TLE985x)  |

| Revision 2.0      | 2019-09-20 – Additional products included (TLE984x) |

| Revision 1.0      | 2019-05-16 – Initial Release                        |

|                   |                                                     |

### **Trademarks of Infineon Technologies AG**

AURIX<sup>™</sup>, C166<sup>™</sup>, CanPAK<sup>™</sup>, CIPOS<sup>™</sup>, CoolGaN<sup>™</sup>, CoolMOS<sup>™</sup>, CoolSET<sup>™</sup>, CoolSiC<sup>™</sup>, CORECONTROL<sup>™</sup>, CROSSAVE<sup>™</sup>, DAVE<sup>™</sup>, DI-POL<sup>™</sup>, DrBlade<sup>™</sup>, EasyPIM<sup>™</sup>, EconoBRIDGE<sup>™</sup>, EconoDUAL<sup>™</sup>, EconoPACK<sup>™</sup>, EconoPIM<sup>™</sup>, EiceDRIVER<sup>™</sup>, eupec<sup>™</sup>, FCOS<sup>™</sup>, HITFET<sup>™</sup>, HybridPACK<sup>™</sup>, Infineon<sup>™</sup>, ISOFACE<sup>™</sup>, IsoPACK<sup>™</sup>, i-Wafer<sup>™</sup>, MIPAQ<sup>™</sup>, ModSTACK<sup>™</sup>, my-d<sup>™</sup>, NovalithIC<sup>™</sup>, OmniTune<sup>™</sup>, OPTIGA<sup>™</sup>, OptiMOS<sup>™</sup>, ORIGA<sup>™</sup>, POWERCODE<sup>™</sup>, PRIMARION<sup>™</sup>, PrimePACK<sup>™</sup>, PrimeSTACK<sup>™</sup>, PROFET<sup>™</sup>, PRO-SIL<sup>™</sup>, RASIC<sup>™</sup>, REAL3<sup>™</sup>, ReverSave<sup>™</sup>, SatRIC<sup>™</sup>, SIEGET<sup>™</sup>, SIPMOS<sup>™</sup>, SmartLEWIS<sup>™</sup>, SOLID FLASH<sup>™</sup>, SPOC<sup>™</sup>, TEMPFET<sup>™</sup>, thinQ!<sup>™</sup>, TRENCHSTOP<sup>™</sup>, TriCore<sup>™</sup>.

Trademarks updated August 2015

### **Other Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

### Edition 2020-11-18

Published by

**Infineon Technologies AG**

81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

Document reference AppNote NumberZ8F65867540

### **IMPORTANT NOTICE**

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of noninfringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contair dangerous substances. For information on the types in question please contact your nearest Infineor Technologies office.

Except as otherwise explicitly approved by Infineor Technologies in a written document signed by authorized representatives of Infineor Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof car reasonably be expected to result in personal injury.