# PSoC<sup>®</sup> Creator™ 2.1 Migration Guide

## Introduction

This document discusses the known issues that may be encountered when migrating designs from PSoC Creator 1.0 (Beta, Production or Service Pack releases) or 2.0 to version 2.1.

**Note** It does not cover the specifics of migrating from ES-marked (engineering sample) PSoC 5 devices to production parts. That process is described in document 001-74087, *Migrating to PSoC*<sup>®</sup> 5 *Production Devices*. The document is located online at: http://www.cypress.com/go/creator\_migration.

In addition to new components and features, PSoC Creator 2.1 includes tool updates and new component revisions for both PSoC 5 and PSoC 3 devices. Cypress strongly recommends that you update the software and migrate your designs to the latest component revisions.

However, some changes to the software may impact your existing designs, requiring some care when moving to the new tool and updating components. Note that in most cases, the requested updates are a result of improved behavior in newer components and better error checking in the tool.

The key migration issues discussed in the document are:

- Handling Obsolete Devices

- Updating Bootloader Projects

- Component Changes

- Impact of Timing-Driven Placement

# **Handling Obsolete Devices**

As explained in the PSoC Creator 2.1 release notes, support for PSoC 3 ES2 devices has been removed and all ES2-marked part numbers have been made obsolete. This preproduction silicon has not been available for sampling for many months and kit owners should upgrade their hardware (for free) through the kit exchange program. Please use <a href="http://www.cypress.com/go/psoc3kitupgrade">http://www.cypress.com/go/psoc3kitupgrade</a> to apply for a new kit or module on-line.

In addition, the previous product release, PSoC Creator 2.0, also made a small number of PSoC 3 and PSoC 5 part numbers obsolete (because they were never sampled).

### **Migrating From Obsolete Devices**

If you have a project using one of these obsolete devices, you will be prompted to change it when opening the project in PSoC Creator 2.1. In all cases, the tool will suggest an appropriate, functional superset and pin-compatible device to use.

- Start by opening the design in PSoC Creator 2.1.

Note The tool will automatically create a backup copy of the original project.

- 2. If your old design contains a device that is not available, a dialog will display prompting you to select a replacement device.

3. Click **OK** to open the project with the suggested device, or click **Device Selector** to select a different device.

# **Updating Bootloader Projects**

In PSoC Creator 2.1 the bootloader system was reorganized to provide more configuration options and reduce the overall footprint of bootloading designs. In previous releases, bootloading was implemented as part of the cy\_boot component (this is a required component that is automatically and invisibly instantiated in all designs).

The bootloader system is now provided as two independent Bootloader and Bootloadable components that are available in the Component Catalog. The bootloader system configuration options are moved from the Design-Wide Resources (DWR) file of the PSoC Creator into the corresponding component customizers (parameter editor dialogs).

The functionality previously provided by the cy\_boot component version 2.xx and earlier has been moved into two new components: Bootloader and Bootloadable. Bootloader and Bootloadable projects that use cy\_boot v3.0 or above are required to include the corresponding component in the TopDesign schematic.

### **Legacy Bootloading in PSoC Creator 2.1**

It is possible to continue using the legacy bootloading method in PSoC Creator 2.1.Existing designs will continue to build and execute correctly in PSoC Creator 2.1, but the cy\_boot component must not be updated to v3.0 or above. With the exception of cy\_boot, other components used in the design can be updated to the latest available versions (with some caveats). Note that, when cy\_boot versions prior to v3.0 are used in the design, PSoC Creator continues to present the legacy DWR options for Bootloader and Bootloadable projects. If cy\_boot v3.0 or above is used, then those options are hidden and the configuration must be done through the component Configure dialogs.

However, using the legacy bootloading method is not recommended as a long-term solution. Some of the latest component versions shipped with the PSoC Creator 2.1 require cy\_boot version 3.0 or above to operate. Also, future component releases will increasingly rely on newer versions of cy\_boot. As a result of this, continuing with the legacy system and old cy\_boot versions will constrain you to use old versions of other components, which can become a problem when new features and defect fixes are released.

# **Updating to PSoC Creator 2.1 Bootloading**

A better choice is to migrate your design to use cy\_boot v3.0 or above, as well as to include the appropriate Bootloader or Bootloadable component in your TopDesign schematic. This allows you to make changes to your bootloading setup, reduces risk of component incompatibility with cy\_boot, and enables the reduced footprint and new features of the new bootloading architecture.

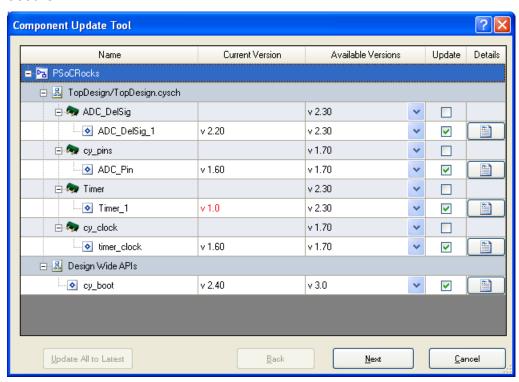

1. Use the Component Update Tool (available from the Project menu) to update to the latest version of cy\_boot (and, preferably, all other components).

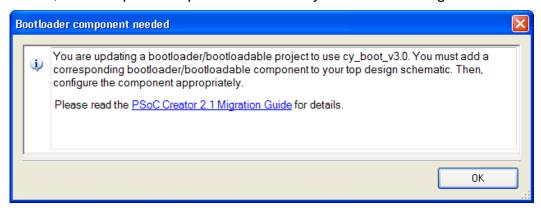

Note that when you update a Bootloader or Bootloadable project to cy\_boot v3.0 or above, the Component Update Tool warns you with a message similar to the following:

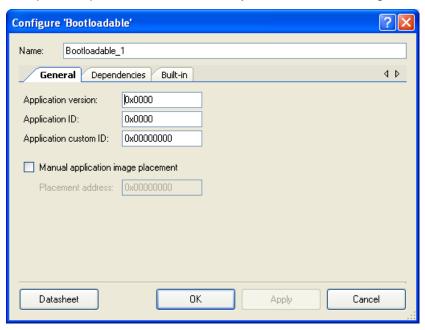

2. For Bootloadable projects, add a Bootloadable component to the design. Edit the component parameters to match your old bootloading settings.

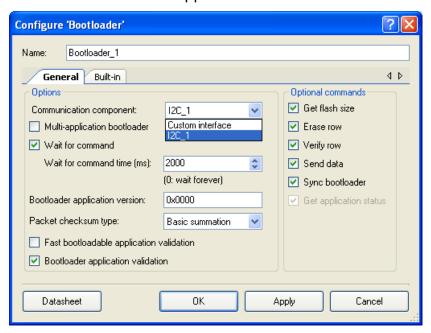

3. For Bootloader and Multi-Application Bootloader projects, add a Bootloader component to the design. Edit the component parameters to match your old bootloading settings. Be sure to check the Multi-Application Bootloader check box for projects of that type.

# **Bootloader Version Compatibility**

The new architecture ensures that Bootloadable projects remain fully compatible with older bootloaders. If you have deployed bootloading systems that use v2.xx of cy\_boot, Bootloadable projects built with the new component and cy\_boot v3.0 or above will correctly load. There is no requirement to build new Bootloadable projects on old versions of the tool or to re-flash deployed Bootloader devices.

If you are implementing a new bootloading system, Cypress recommends using the new architecture for both bootloader and bootloadable projects.

# **Component Changes**

Many components have new versions and changes that impact migration. We recommend using the Component Update Tool to update projects to the latest component versions.

### **Updating Components**

When you open a project that was last saved in an older version of PSoC Creator in the new software you will be prompted to update components to the latest version. This is optional but recommended.

1. Use the Component Update Tool (available from the **Project** menu) to choose the latest, production-ready versions of all components.

It is recommended that all components are updated together and an "Update All to Latest" button is provided to ensure the newest versions are selected for update.

Note that particularly old components, or those with known problems when used on the target device, are shown in red (error condition) or amber (warning condition). Clearly, it is strongly recommended that the project be updated to newer components when this occurs.

Be aware that major version changes (e.g., from v1.xx to v2.xx) are not guaranteed to be backward compatible. So, review the component change logs carefully (these are located at the end of the component datasheets).

2. Rebuild the design and test.

# **Obsolete Old Component Versions**

Many components in PSoC Creator 2.1 pre-date even beta versions of v1.0 of the tool. These components are not recommended for use in production designs and have all been superseded by newer, better implementations. In order to reduce the risk of them being used inadvertently, and to reduce the overall size of the PSoC Creator distribution, they are to be made obsolete and removed from the tool.

In this release, these components have been marked as obsolete and, if used in a schematic, will generate a warning to update to a newer component. In the next release of PSoC Creator, these components will be completely omitted from the distribution.

Use the Component Update Tool to migrate to newer versions of these components.

| Component       | Version( | s) to be O | bsolete |       |       |       |

|-----------------|----------|------------|---------|-------|-------|-------|

| ADC_DelSig      | v1.0     | v1.10      | v1.20   | v1.21 |       |       |

| AMux            | v1.0     | v1.10      |         |       |       |       |

| AMuxSeq         | v1.10    |            |         |       |       |       |

| BoostConv       | v1.0     |            |         |       |       |       |

| CAN             | v0.5     | v1.10      | v1.20   |       |       |       |

| CapSense        | v0.5     | v1.10      | v1.20   | v1.30 |       |       |

| CharLCD         | v0.2     | v1.10      | v1.20   |       |       |       |

| Comp            | v1.0     |            |         |       |       |       |

| Counter         | v1.0     | v1.10      |         |       |       |       |

| CRC             | v1.10    |            |         |       |       |       |

| cy_boot         | v1.0     | v1.10      | v1.20   |       |       |       |

| DieTemp         | v1.0     |            |         |       |       |       |

| EEPROM          | v0.0     | v1.10      |         |       |       |       |

| EZI2C           | v1.0     | v1.10      |         |       |       |       |

| FanController   | v1.20    |            |         |       |       |       |

| Filter          | v1.10    |            |         |       |       |       |

| I2C             | v1.0     | v1.10      |         |       |       |       |

| IDAC8           | v1.0     | v1.10      |         |       |       |       |

| Mixer           | v1.0     | v1.10      |         |       |       |       |

| PGA             | v1.0     |            |         |       |       |       |

| PGA_Inv         | v1.0     |            |         |       |       |       |

| PrISM           | v1.10    |            |         |       |       |       |

| PRS             | v0.5     | v1.10      | v1.20   |       |       |       |

| PWM             | v1.0     |            |         |       |       |       |

| QuadDec         | v1.10    |            |         |       |       |       |

| RTC             | v0.5     | v1.10      |         |       |       |       |

| SegLCD          | v1.0     | v1.10      | v1.20   | v1.30 | v1.50 | v1.60 |

| SGPIO_Initiator | v1.20    |            |         |       |       |       |

| SGPIO_Target    | v1.30    |            |         |       |       |       |

| ShiftReg        | v1.10    |            |         |       |       |       |

| SleepTimer      | v1.0     | v1.50      |         |       |       |       |

| SPI_Master      | v1.0     | v1.10      |         |       |       |       |

| Component        | Version( | (s) to be O | bsolete |       |

|------------------|----------|-------------|---------|-------|

| SPI_Slave        | v1.0     | v1.10       |         |       |

| StaticSegLCD     | v1.10    | v1.20       |         |       |

| TIA              | v0.5     |             |         |       |

| Timer            | v1.0     | v1.10       |         |       |

| UART             | v1.0     | v1.10       | v1.20   |       |

| USBFS            | v0.2     | v1.10       | v1.20   | v1.30 |

| VDAC8            | v1.0     | v1.10       |         |       |

| VoltageSequencer | v1.50    |             |         |       |

# **Changes to Existing Components**

The following are some of the high-level impacts of various component changes in this release. Refer to each individual component datasheet for specific changes made as needed.

#### cy boot v3.10

As discussed previously, the bootloader functionality was removed and is now available in the Bootloader and Bootloadable components.

In addition, the following APIs were removed for PSoC 5 devices (that do not support the functionality).

- CyXTAL\_ReadStatus()

- CyXTAL\_EnableErrStatus()

- CyXTAL\_DisableErrStatus()

- CyXTAL\_EnableFaultRecovery()

- CyXTAL\_DisableFaultRecovery()

# ADC\_DelSig v2.30

Two functions were updated in this release such that they became more complex and are now flagged by the Keil PK51 (8051) compiler for reentrancy checking. The following warning from the linker indicates a reentrancy problem in the application.

#### WARNING: L15: MULTIPLE CALL TO FUNCTION

The following functions should be added to the project .cyre file if the tool issues the above warning(s).

- ADC\_SetDSMRef0Reg()

- ADC\_Ext\_CP\_Clk\_SetDividerRegister()

#### **EEPROM**

The EEPROM component now supports byte-write, and all APIs have been updated to improve performance. Note that, to achieve the speed optimization, the device temperature is no longer checked on every write operation. It is now the application's responsibility to verify the temperature (and re-calibrate the EEPROM component) as needed.

#### VRef v1.60

The IgnoreSleep parameter, which was supposed to enable the component to remain active while the device was in low power modes, was removed. The on-board voltage references on the devices do not, in fact, support that functionality. No change to component behavior is expected as a result. Using older versions is safe because the tool simply ignore the parameter.

#### Fan Controller v2.10 and Voltage Sequencer v1.50

These components were in the Concept tab of the Component Catalog and, as a result of completing Cypress characterization and testing, have been relocated to the main Cypress tab.

#### SGPIO\_Initiator v1.20 and SGPIO\_Target v1.30

The SGPIO components have been made obsolete and are no longer supported. They will be removed from the next release of PSoC Creator. Please contact Technical Support for help with applications that need SGPIO functionality.

#### Net Join (all versions)

This component is still included in the distribution and is safe to use in designs. However, it uses a very large symbol that was not conducive to neat schematics. It is not possible to reduce the size of the symbol without breaking connections in existing designs. So, this component is now hidden from the Component Catalog by default, and a new Net Tie component has been introduced. The Net Tie is functionally equivalent to the Net Join but uses a far smaller, neater symbol.

### Analog Constraint (all versions)

The Analog Resource Constraint component allows you to define the route of the analog signal to which it is connected. It is an advanced feature that is not needed for most designs. It has been found to be difficult to use because it can be applied to both nets and muxes. When the component is connected to a net of wires and muxes it is not visually clear which resource is actually constrained.

The functionality is now split into two new components: the Analog Net Constraint and the Analog Mux Constraint. The Analog Net Constraint limits analog routing of a signal to a specific routing resource. The Analog Mux Constraint limits analog routing of a switchable mux connection to a specific routing resource. Continued use of the old component is not recommended.

# **Impact of Timing-Driven Placement**

Timing-driven placement (TDP) is a back-end feature to reduce warnings from the static timing analyzer (STA). By examining both the clocking requirements of components and the presence of connections between them, TDP seeks to allocate components to UDB resources that are least likely to generate timing violations. It builds on the timing-driven routing (TDR) feature introduced in the PSoC Creator 2.0 release to recognize timing problems and adjust placement to avoid them.

A side-effect of the updated placement algorithm is more thorough checking of clocking relationships. This can lead to new STA warnings in existing designs that previously met timing. In particular, synchronized clocks are no longer allowed to run at more than half of the MASTER\_CLK frequency, with the following error being the result.

Clock Error: (A clock marked as "Sync" cannot be faster than half the frequency of the clock synchronizing it.)

The only resolution to this problem is to modify the clock frequencies sufficiently to obey 2x frequency rule.

# **Document History**

**Document Title: PSoC® Creator™ 2.1 Migration Guide**

Document Number: 001-79640

| Revision | Submission Date | Description of Change                                                                                                                                                         |

|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | June 6, 2012    | New document. Initial release for PSoC Creator 2.1.                                                                                                                           |

| *A       | June 19, 2012   | Changed text to indicate SGPIO_Initiator v1.20 and SGPIO_Target v1.30 components are no longer supported.  Updated the screen capture when updating to cy_boot_v3.0 or above. |

| *B       | June 29, 2012   | Corrected typo.                                                                                                                                                               |

© Cypress Semiconductor Corporation, 2012. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

PSoC® and CapSense® are registered trademarks, and PSoC Creator™, Programmable System-on-Chip™, and SmartSense™ are trademarks of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are property of the respective corporations.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 001-79640, Rev. \*B