## **OPTIGA™** Authenticate Family

## Description

This is a basic OPTIGA<sup>™</sup> Authenticate On short data sheet that provides basic information for getting started to design of OPTIGA<sup>™</sup> Authenticate On.

#### Features

#### Authentication

- 163-bit Elliptic Curve Cryptography (ECC) Engine

- 193-bit OPTIGA Digital Certificate (ODC)

- Message Authentication Code (MAC) Function for the User Data Authentication

- MAC based Host Authentication Feature for SLE956681 Only

- Customizable Kill Features

- Unique Chip ID 96-bit

- Ultra low-power operation at max 500uA

#### Non-Volatile Memory

- 2Kbit NVM size

- Lockable User NVM memory

- 32-bit page granularity

- 2 Lifespan Indicators

#### **Communication Interface**

- SWI I/O interface

#### Package

- Package PG-TSNP-6-16

#### ESD

- JESD22-A114 ESD HBM 2KV Standard

- JESD22-C101 ESD CDM 500V Standard

#### Software

- Host Side library

## **Table of contents**

| Desc | ription                                  | 1  |

|------|------------------------------------------|----|

| Feat | ures                                     | 1  |

| Tabl | e of contents                            | 2  |

| 1    | Overview                                 |    |

| 1.1  | Product Description                      | 3  |

| 1.2  | Functional Overview                      | 3  |

| 1.3  | Typical Application                      | 3  |

| 2    | Signals Description                      | 5  |

| 3    | Packing Specification                    | 8  |

| 3.1  | Package Marking                          |    |

| 3.2  | Emboss Carrier Tape                      |    |

| 4    | Electrical Characteristics               | 12 |

| 4.1  | Absolute Maximum Ratings                 |    |

| 4.2  | Operating Conditions                     |    |

| 4.3  | SWI I/O Characteristics                  |    |

| 4.4  | SWI Timing Characteristics               |    |

| 4.5  | Random Number Generation Time            | 15 |

| 4.6  | Authentication Response Computation Time | 15 |

| 4.7  | NVM Characteristics                      | 15 |

| Revi | sion history                             | 16 |

## 1 Overview

## **1.1 Product Description**

Infineon Technologies' novel OPTIGA<sup>™</sup> Authenticate On Authentication chip offers a robust cryptographic solution that assists OEMs and system manufacturers to ensure the authenticity and safety of their original products, and protection of their investments against unauthorized after-market replacements. It leverages Infineon's market leading security know-how into the battery and accessory authentication markets. With its innovative asymmetric cryptography approach, it significantly reduces system cost whilst making a leap in security.

## 1.2 Functional Overview

OPTIGA<sup>™</sup> Authenticate On is designed to be used as a companion authentication device. This authentication device resides away from the host system such that the host system is able to check if it is communicating with an authenticated original device.

OPTIGA<sup>™</sup> Authenticate On supports a configurable SWI interface to communicate with the Host controller. It is designed to be compatible to MIPI BIF dataword. The configuration of the interface link for the OPTIGA<sup>™</sup> Authenticate On can be configured in the application board.

## **1.3** Typical Application

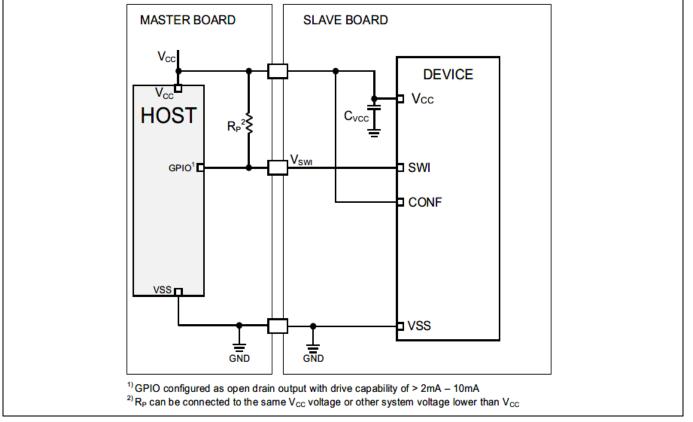

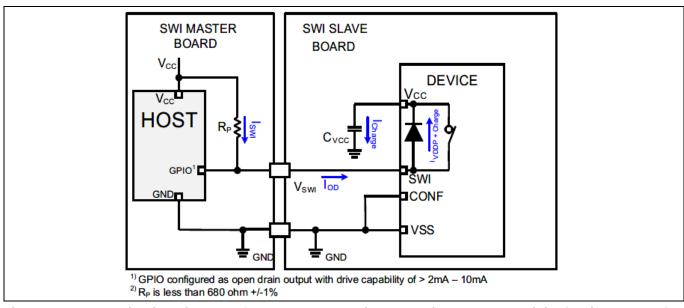

OPTIGA<sup>™</sup> Authenticate On can be integrated to any system with very low hardware requirement. In a typical setup, only a pull-up resistor, R<sub>P</sub>, is required for an open-drain GPIO. OPTIGA<sup>™</sup> Authenticate On provides a combination of secure authentication function and user read/write storage space via a single serial interface (SWI). SWI is able to perform bidirectional communication on multiple devices on the bus without extra hardware. Communication on the SWI is half-duplex transmission in which master and slave can transmit and received commands only one at a time. In SWI architecture, SWI master initiates and controls all the SWI operations. The SWI bus operates in a command and response sequence. An additional feature of SWI interface is the ability of interrupt-based processing which allows for concurrent processing.

Below figures show an example of a Host system connection to an OPTIGA<sup>™</sup> Authenticate On device in direct and indirect powered SWI configurations.

#### **OPTIGA<sup>™</sup>** Authenticate Family

#### Overview

neon

Application Diagram of OPTIGA™ Authenticate On with SWI connectivity (Indirect Power)

**OPTIGA™** Authenticate Family

**Signals Description**

## 2 Signals Description

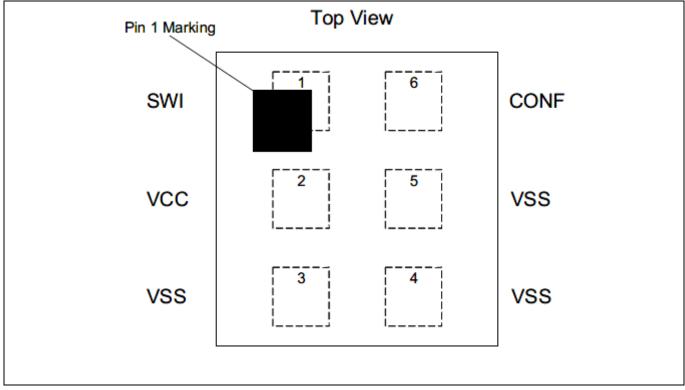

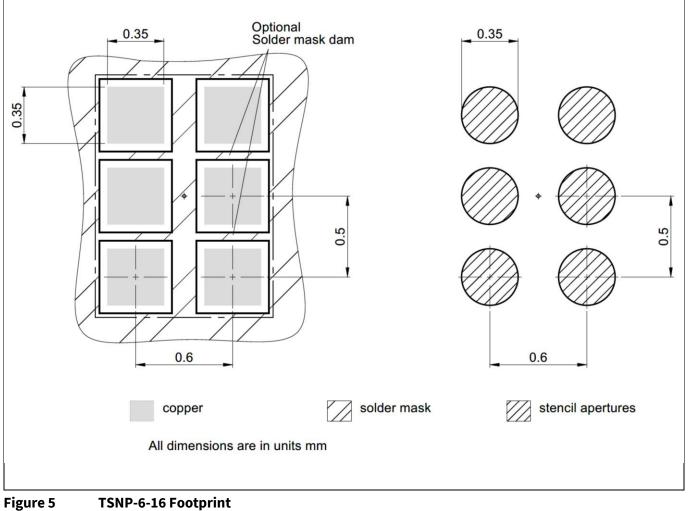

OPTIGA<sup>™</sup> Authenticate On comes with PG-TSNP-6-16 package.

#### Figure 3 Pin configuration of OPTIGA<sup>™</sup> Authenticate On

#### Table 1I/O Signals

| Pin No. | Name | Pin Type | Buffer Type | Function                                         |

|---------|------|----------|-------------|--------------------------------------------------|

| 1       | SWI  | I/O      | OD          | SWI                                              |

| 6       | CONF | AI       | Z           | Must be connected to VSS for indirect power mode |

|         |      |          |             | Must be connected to VCC for direct power mode   |

#### Table 2 Power Supply

| Pin No. | Name | Pin Type | Buffer Type | Function                        |

|---------|------|----------|-------------|---------------------------------|

| 2       | VCC  | PWR      | -           | Positive Power Input for device |

#### Table 3Ground Pins

| Pin No. | Name | Pin Type | Buffer Type | Function            |

|---------|------|----------|-------------|---------------------|

| 3,4,5   | VSS  | PWR      | -           | GND Pin             |

|         |      |          |             | This is the         |

|         |      |          |             | common ground       |

|         |      |          |             | of the IC. Pin 4 is |

#### **OPTIGA™** Authenticate Family

**Signals Description**

| Pin No. | Name | Pin Type | Buffer Type | Function        |

|---------|------|----------|-------------|-----------------|

|         |      |          |             | the main ground |

|         |      |          |             | of the package  |

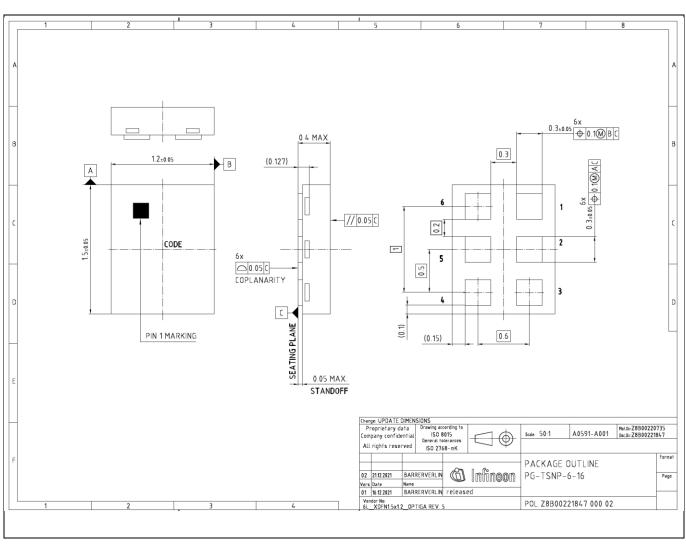

#### Table 4 PG-TSNP-6-16 Package Dimensions

| Parameter | Symbol |      | Values |      |    | Note or Test         |

|-----------|--------|------|--------|------|----|----------------------|

|           |        | Min  | Тур    | Max  |    | Condition            |

| A         |        | 1.45 | 1.50   | 1.55 | mm | Package Width        |

| В         |        | 1.15 | 1.20   | 1.25 | mm | Package Length       |

|           |        | 0.35 | 0.38   | 0.40 | mm | Package Height       |

| AC        |        | 0.25 | 0.30   | 0.35 | mm | Solder Pad Width     |

| BC        |        | 0.25 | 0.30   | 0.35 | mm | Solder Pad Length    |

|           |        |      | 0.60   |      | mm | Solder Pad Pitch - X |

|           |        |      | 0.50   |      | mm | Solder Pad Pitch - Y |

## **OPTIGA™** Authenticate Family

#### **Signals Description**

**OPTIGA™** Authenticate Family

Packing Specification

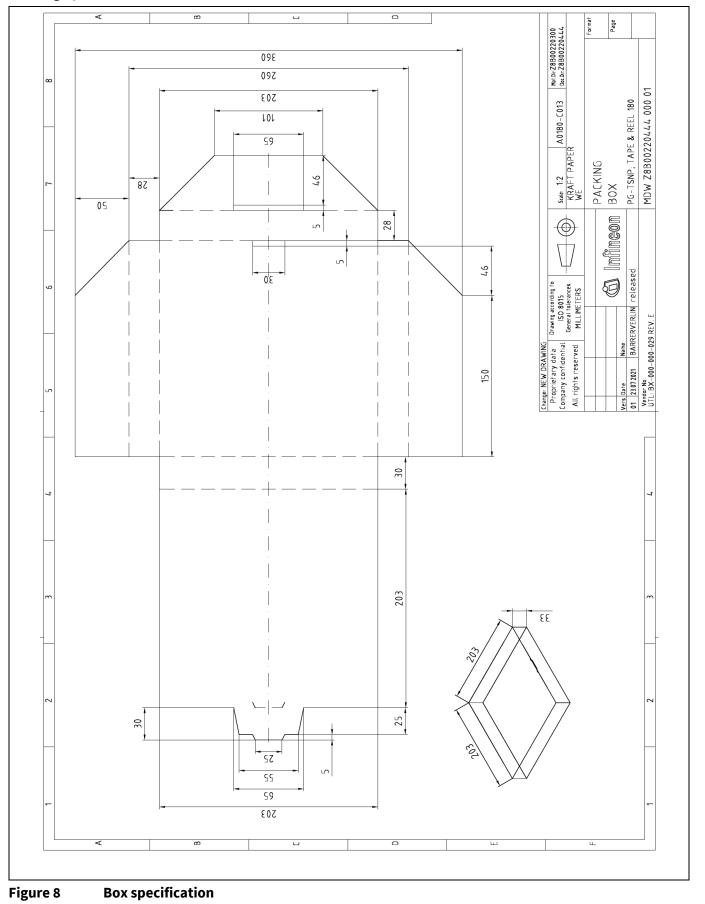

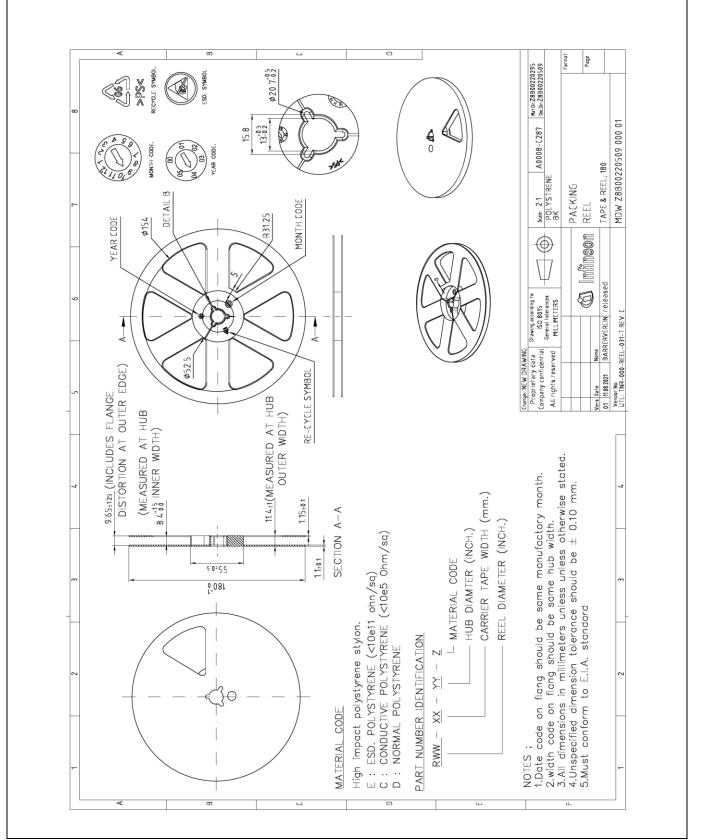

3 Packing Specification

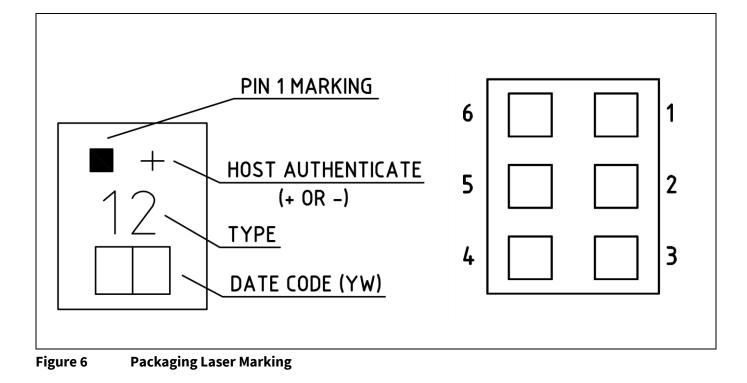

## 3.1 Package Marking

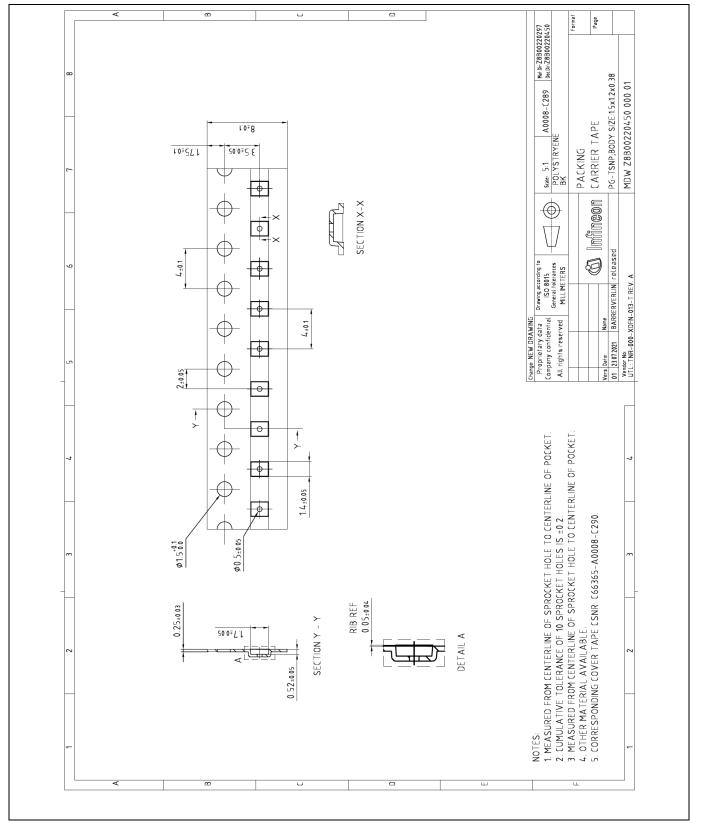

## 3.2 Emboss Carrier Tape

Each box contains a single reel with 5000 pices of device. Reel diameter is 180 mm.

OPTIGA<sup>™</sup> Authenticate On Short Data Sheet OPTIGA<sup>™</sup> Authenticate Family

# infineon

#### **Packing Specification**

**OPTIGA™** Authenticate Family

## infineon

#### **Packing Specification**

### **OPTIGA<sup>™</sup>** Authenticate On Short Data Sheet OPTIGA<sup>™</sup> Authenticate Family

Packing Specification

Infineon

## 4 Electrical Characteristics

## 4.1 Absolute Maximum Ratings

Stresses above the maximum values listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods (over 24 hours) may affect device reliability. Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

#### Table 5 Absolute Maximum Ratings

| Parameter           | Symbol            | Values |      |       | 11   | Note / Test Condition           |

|---------------------|-------------------|--------|------|-------|------|---------------------------------|

| Parameter           | Symbol            | Min.   | Тур. | Max.  | Unit | Note / Test Condition           |

| VCC Supply Voltage  | $V_{\sf cc}$      | -0.3   | -    | 4.6   | V    |                                 |

| SWI Voltage         | $V_{SWI}$         | -0.3   | -    | 4.6   | V    |                                 |

| ESD robustness HBM  | $V_{\rm esd,hbm}$ | 2000   |      |       | V    | According to<br>EIA/JESD22-A114 |

| ESD robustness CDM  | $V_{\rm esd,cdm}$ | 500    |      |       | V    | According to<br>EIA/JESD22-C101 |

| Latch up            | I <sub>LU</sub>   | 100    |      |       | mA   | According to EIA/<br>JESD78     |

| Storage Temperature | $T_{\rm store}$   | -55.0  |      | 150.0 | °C   |                                 |

OPTIGA<sup>™</sup> Authenticate Family Electrical Characteristics

## 4.2 **Operating Conditions**

Within the operational range, the IC operates as explained product description. Typical Values:  $V_{\rm CC}$  = 1.8V,  $T_{\rm AMB}$ =25 °C

#### Table 6 Operating Conditions

| Daramatar                                                     | Symbol                   |        | Values |      | Unit | Note / Test Condition                                                                                      |  |

|---------------------------------------------------------------|--------------------------|--------|--------|------|------|------------------------------------------------------------------------------------------------------------|--|

| Parameter                                                     | Symbol                   | Min.   | Тур.   | Max. | Unit | Note / Test Condition                                                                                      |  |

| VCC Supply Voltage Range                                      | V <sub>cc</sub>          | 1.24   |        | 3.63 | V    | Measurement is at the<br>V <sub>cc</sub> pin. Ramp up of<br>V <sub>cc</sub> shall be slower<br>than 1 μSec |  |

| SWI Voltage Range                                             | $V_{SWI}$                | -0.3   |        | 3.63 | V    |                                                                                                            |  |

| Current Consumption, Active Idle<br>Mode                      | $I_{ m VCC,Active-Idle}$ |        | 150    | 200  | μΑ   | Idle Function Mode<br>Averaged over 1 Sec                                                                  |  |

| Current Consumption, Active<br>Mode, Authentication Operation | $I_{ m VCC,Active-ECC}$  |        | 325    | 500  | μΑ   | Averaged over<br>Authentication                                                                            |  |

| Current Consumption, Power-<br>Down Mode                      | $I_{ m VCC,PD}$          |        | 1.0    |      | μΑ   | SWI is set at 0V<br>Maximum Value<br>condition is set at V <sub>cc</sub> =<br>3.60V @ 85 Deg C             |  |

| Ambient Temperature                                           | $T_{ m AMB}$             | -40    |        | 85   | °C   |                                                                                                            |  |

| Power Down Low Time                                           | <i>t<sub>PDL</sub></i>   | 2000.0 |        |      | μs   |                                                                                                            |  |

| Power Up Delay                                                | $t_{PUD}$                |        |        | 8.0  | ms   |                                                                                                            |  |

| Soft Reset Delay                                              | t <sub>SRD</sub>         |        |        | 1.0  | ms   |                                                                                                            |  |

## 4.3 SWI I/O Characteristics

#### Table 7SWI I/O Characterisitics

| De verse et e v         | Gunahal                               | Values |      |      | 11   | Note / Test Condition                                         |

|-------------------------|---------------------------------------|--------|------|------|------|---------------------------------------------------------------|

| Parameter               | Symbol                                | Min.   | Тур. | Max. | Unit | Note / Test Condition                                         |

| SWI Input High Voltage  | $V_{ m SWI,IH}$                       | 1.2    |      |      | V    |                                                               |

| SWI Input Low Voltage   | $V_{\scriptscriptstyle { m SWI,IL}}$  |        |      | 0.8  | V    |                                                               |

| SWI Output High Voltage | $V_{\scriptscriptstyle { m SWI,OH}}$  | 1.30   |      |      | V    | No remote powering,<br>measured at 1.0 μA.<br>For Master Only |

| SWI Output Low Voltage  | $V_{\scriptscriptstyle {\sf SWI,OL}}$ |        |      | 0.1  | V    | Measured at 1 mA                                              |

| SWI Bus Load            | $C_{\rm SWI,L}$                       |        |      | 250  | рF   |                                                               |

4.4 SWI Timing Characteristics

#### Table 8 SWI Timing Characteristics

| Devementer                       | Cumb al                |        | Values         |       | 11mit                       | Note / Test Condition                                |  |

|----------------------------------|------------------------|--------|----------------|-------|-----------------------------|------------------------------------------------------|--|

| Parameter                        | Symbol                 | Min.   | Min. Typ. Max. |       | Unit                        | Note / Test Condition                                |  |

| Basic Timing Parameters          |                        |        |                |       |                             |                                                      |  |

| Time Base                        | t <sub>swi</sub>       | 1.0    |                | 153   | μs                          |                                                      |  |

| Bus Frequency                    | $f_{SWI}$              | 3.268  |                | 500.0 | kHz                         | 50% Zero, 50% One                                    |  |

| Peak Data Rate                   |                        |        |                | 500   | kBits/s                     |                                                      |  |

| Bus Rise Time                    | tr                     |        |                | 200   | ns                          |                                                      |  |

| Bus Fall Time                    | t <sub>f</sub>         |        |                | 200   | ns                          |                                                      |  |

| Transmit Timing Parameters       | 5                      |        |                |       |                             |                                                      |  |

| Duration for 0 <sub>B</sub>      | t <sub>TO</sub>        | 0.75   |                | 1.25  | t <sub>swi</sub>            |                                                      |  |

| Duration for $1_B$               | <i>t</i> <sub>T1</sub> | 2.75   |                | 3.25  | t <sub>swi</sub>            |                                                      |  |

| Duration for STOP                | t <sub>TS</sub>        | 6.00   |                |       | $\mathbf{t}_{\mathrm{SWI}}$ |                                                      |  |

| <b>Receive Timing Parameters</b> | L                      |        |                |       |                             | · · · · · · · · · · · · · · · · · · ·                |  |

| Duration for 0 <sub>B</sub>      | t <sub>RO</sub>        | 0.6    |                | 1.4   | t <sub>swi</sub>            |                                                      |  |

| Duration for $1_{B}$             | t <sub>R1</sub>        | 2.6    |                | 3.4   | t <sub>swi</sub>            |                                                      |  |

| Duration for STOP                | t <sub>RS</sub>        | 4.5    |                |       | t <sub>swi</sub>            |                                                      |  |

| Interrupt Timing Parameter       | 5                      |        |                |       |                             |                                                      |  |

| Interrupt Arming Time            | t <sub>ARM</sub>       | 4.75   |                |       | $\mathbf{t}_{\mathrm{SWI}}$ |                                                      |  |

| Interrupt Active Time            | t <sub>INT</sub>       | 0.75   | 1              | 1.25  | t <sub>swi</sub>            | Drive period for all<br>Slaves                       |  |

| Interrupt Trailing Time          | t <sub>TRAIL</sub>     |        |                | 3.25  | t <sub>swi</sub>            | Drive period for all<br>Slaves                       |  |

| Bus Time-Out Parameters          |                        |        |                |       |                             |                                                      |  |

| Bus Time-Out Period              | t <sub>TOUT</sub>      |        |                | 90.0  | t <sub>swi</sub>            | Time Base, t <sub>swi</sub> equal or less than 9 μs. |  |

| Bus Time-Out Period              | t <sub>TOUT</sub>      |        |                | 10.0  | t <sub>swi</sub>            | Time Base, t <sub>swi</sub> above<br>9 μs.           |  |

| Power and Reset Control Tin      | ning Parameters        |        |                |       |                             |                                                      |  |

| Communication Low Time           | t <sub>PDL</sub>       | 2000.0 |                |       | μs                          |                                                      |  |

### 4.5 Random Number Generation Time

#### Table 9 Random Number Generation Time

| Parameter                     | Symbol           | values |      | Values |      | Note / Test Condition |

|-------------------------------|------------------|--------|------|--------|------|-----------------------|

| Parameter                     | Min.             |        | Тур. | Max.   | Unit | Note / Test condition |

| Random Number Generation Time | T <sub>RNG</sub> |        | 50.0 | 60.0   | μs   |                       |

## 4.6 Authentication Response Computation Time

#### Table 10 Authentication Response Computation Time

| Daramatar                             | Symbol                   |      | Values |      | Unit | Note / Test Condition |

|---------------------------------------|--------------------------|------|--------|------|------|-----------------------|

| Parameter                             | Symbol                   | Min. | Тур.   | Max. | Unit | Note / Test Condition |

| Response Computation Time<br>ECCS-163 | $T^{I)}_{_{ m ECCS163}}$ |      | 83     | 100  | ms   |                       |

Min. value here refers to the host needing to wait at least max (T<sub>ECCS163</sub>) before accessing the device for the response value. Max value here is optional (theorically, the host can wait as long as it requires before reading back the response value) but this is provided for the host opting to time-out the readback process as a sign for abnormal activity.

## 4.7 NVM Characteristics

#### Table 11NVM Characterisitics

| Deveneter            | Symphol             | Values |      |         | 11    | Note / Test Condition |

|----------------------|---------------------|--------|------|---------|-------|-----------------------|

| Parameter            | Symbol              | Min.   | Тур. | Max.    | Unit  | Note / Test Condition |

| NVM Endurance        | N <sub>CYC</sub>    |        |      | 500,000 | Cycle | 25 °C                 |

| NVM Retention        | T <sub>retent</sub> |        |      | 10      | years | 25 °C                 |

| NVM Programming Time | t <sub>PROG</sub>   |        | 4.59 | 5.1     | ms    | 25 °C                 |

## **Revision history**

| Document<br>version | Date of release | Description of changes                                                |  |

|---------------------|-----------------|-----------------------------------------------------------------------|--|

| 0.1                 | 2021-01-27      | Initial Version.                                                      |  |

| 0.2                 | 2021-10-01      | Fixed minor typo.                                                     |  |

| 0.3                 | 2022-05-06      | Added Char data and diagrams                                          |  |

| 0.4                 | 2022-05-12      | Editorial changes                                                     |  |

| 0.5                 | 2022-12-20      | Added TSNP Solder mask                                                |  |

| 0.6                 | 2023-10-18      | Rename Product Brief to Short datasheet and remove restricted marking |  |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2023-10-18

Published by

**Infineon Technologies AG**

81726 Munich, Germany

© 2023 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

**Document reference**

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contair dangerous substances. For information on the types in question please contact your nearest Infineor Technologies office.

Except as otherwise explicitly approved by Infineor Technologies in a written document signed by authorized representatives of Infineor Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof car reasonably be expected to result in personal injury.