# 2x200W Class D Amplifier, with Analog Inputs and Integrated $49.2m\Omega$ $R_{\text{DS}(\text{ON})}$ Output Stage

#### **Features**

- Integrated output stage with 49.2m $\Omega$  of Typ.  $R_{DS(ON)}$

- $2 \times 200 \text{W P}_{\text{OUT}}$  in stereo mode (8 $\Omega$ , THD=10%)

- $2 \times 190 \text{W P}_{\text{OUT}}$  in stereo mode  $(4\Omega, \text{THD}=10\%)$

- 1 x 400W P<sub>OUT</sub> in mono mode (16Ω, THD=10%)

- 1 x 360W P<sub>OUT</sub> in mono mode (8Ω, THD=10%)

- Supports both single and split supplies

- Split supply operational range: ±30 ±60V

- Single supply Operational range: +60 +120V

- 95% full load efficiency into 8Ω

- >70% idle mode efficiency

- Open-drain flag indicators for clipping and Fault conditions

- Multiple configuration: single-ended, BTL & PSE (Parallel Single Ended)

- Programmable power up delay timer (CSD)

- o Click and pop free startup and shutdown

- Integrated protection: OCP, OTP & UVLO

- Pin to pin compatible to MA53x2 family

- Available in QFN 7m x7m 42 pin

### **Applications**

- Multi-channel home theatre

- Studio monitor

- Active speaker

- Subwoofer

- Marine amplifiers

- Aftermarket car audio

- · General-purpose audio power amplifier

PG-IQFN-42

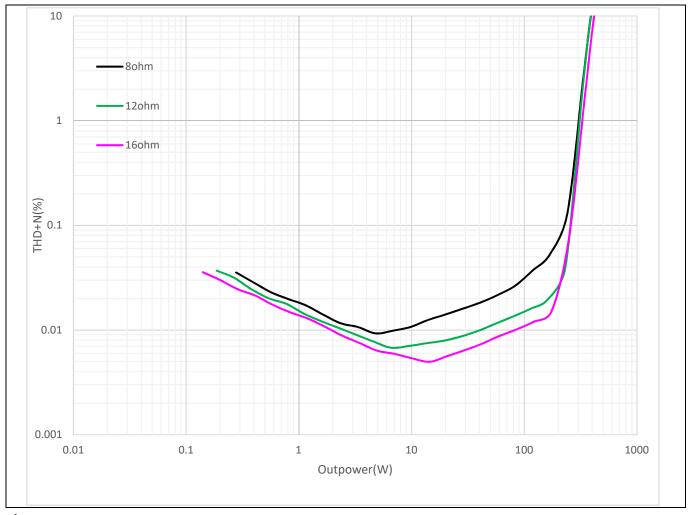

**Total Harmonic Distortion**

#### **Product validation**

Qualified for standard applications according to the relevant tests of J-STD-020 and JESD47.

| Product type | Package           |  |  |  |

|--------------|-------------------|--|--|--|

| MA5342MS     | 7x7mm PG- IQFN-42 |  |  |  |

### **Description**

The MA5342MS provides output power that is equivalent to or greater than monolithic alternatives, while occupying 50% less space and requiring little or no heatsink. This is achieved through the integration of a 2channel PWM controller, a high voltage gate driver, and 4 low RDS(ON) MOSFETs in a multi-chip module (MCM) solution. Similar to its predecessor, the IR43x2M, the MA5342MS includes standard Class D protection features that ensure reliable operation across various environmental conditions. With its small 7x7 mm PG-IQFN-42 package, the MA5342MS represents a powerful upgrade over the IR43x2M and other monolithic alternatives, delivering high power density and the benefits of heatsink-less operation.

| Topology                            | Half-bridge / Full bridge                 |

|-------------------------------------|-------------------------------------------|

| MA5342MS Output power (Half-        | *200W at $8\Omega$ / 400 W at $16\Omega$  |

| bridge,THD+N=10%)                   | *190W at $6\Omega$ / 380 W at $12\Omega$  |

|                                     | *190W at 4 $\Omega$ / 380 W at 8 $\Omega$ |

| *Residual noise (8Ω, AES-17, IHF-A) | *220 μVrms                                |

| *THD+N (1kHz, 75W, 8Ω, AES-17)      | *0.01 %                                   |

<sup>\*</sup> Typical application

## **Table of contents**

| Featı  | ıres                                           | 1  |

|--------|------------------------------------------------|----|

| Appli  | cations                                        | 1  |

| Prod   | uct validation                                 | 1  |

| Desci  | ription                                        | 7  |

|        | of contents                                    |    |

| 1 abic |                                                |    |

| _      | Qualification information                      |    |

| 2      | Device Comparison Table                        |    |

| 3      | Pin Configuration                              |    |

| 3.1    | Lead assignments                               |    |

| 3.2    | Lead definitions                               |    |

| 4      | Specifications                                 |    |

| 4.1    | Absolute maximum ratings                       |    |

| 4.2    | Recommended operating conditions               |    |

| 4.3    | Electrical characteristics                     |    |

| 4.4    | Audio characteristics (SE)                     |    |

| 4.5    | Audio characteristics (BTL)                    |    |

| 4.6    | Audio characteristics (PSE)                    |    |

| 4.6.1  | Power vs. THD+N                                |    |

| 4.6.2  | Frequency vs. THD+N                            |    |

| 4.6.3  | Frequency response                             |    |

| 4.6.4  | Noise floor                                    |    |

| 4.6.5  | Efficiency                                     |    |

| 4.7    | Typical Audio characteristics (BTL)            |    |

| 4.7.1  | Power vs. THD+N                                |    |

| 4.7.2  | Frequency vs. THD+N                            |    |

| 4.7.3  | Frequency response                             |    |

| 4.7.4  | Noise floor                                    |    |

| 4.8    | Typical Audio characteristics (PSE)            |    |

| 4.8.1  | Power vs. THD+N                                |    |

| 4.8.2  | Frequency vs. THD+N                            |    |

| 4.8.3  | Frequency response                             |    |

| 4.8.4  | Noise floor                                    |    |

| 5      | Thermal information                            |    |

| 5.1    | Maximum Wrms duration thermal information      |    |

| 5.2    | Heatsink information                           |    |

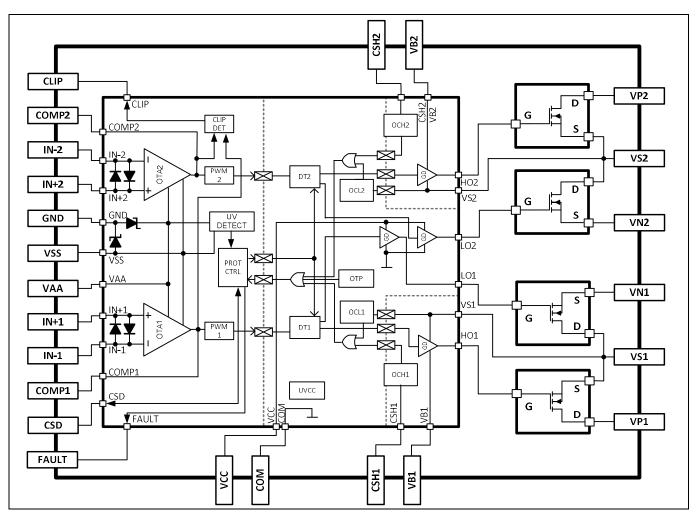

| 6      | Functional block diagram                       | 33 |

| 7      | Typical Implementation                         | 34 |

| 8      | Input / Output pin equivalent circuit diagrams | 37 |

| 9      | PWM Modulator Design                           | 38 |

| 9.1    | Input Section                                  |    |

| 9.2    | Control Loop Design                            | 39 |

| 9.3    | PWM Frequency                                  | 39 |

| 9.4    | Clock Synchronization                          | 40 |

| 9.5    | Click Noise Elimination                        | 41 |

| 9.6    | Differential Input                             | 42 |

| 10 Op  | perational Mode                                       | 43 |

|--------|-------------------------------------------------------|----|

| 10.1   | Self-oscillation Start-up Condition                   | 43 |

| 11 Pr  | otections                                             | 44 |

| 11.1.1 | Self-Reset Protection                                 |    |

| 11.1.2 | Designing Ct                                          | 45 |

| 11.1.3 | Shutdown Input                                        | 46 |

| 11.1.4 | Latched Protection                                    | 47 |

| 11.1.5 | Interfacing with System Controller                    | 47 |

| 11.2   | Over Current Protection (OCP)                         |    |

| 11.3   | Over Temperature Protection (OTP)                     | 49 |

| 11.4   | Under Voltage Protection (UVP)                        | 49 |

| 12 Sta | atus Output                                           | 50 |

| 12.1   | Fault Output                                          |    |

| 12.2   | CLIP Output                                           | 51 |

| 13 Po  | ower Supply Design                                    | 52 |

| 13.1   | Supplying VAA and VSS                                 |    |

| 13.2   | Supplying VCC and VB                                  | 52 |

| 13.2.1 | Choosing Vs Diode                                     | 53 |

| 13.2.2 | Choosing Bootstrap Diode                              | 53 |

| 13.2.3 | Charging V <sub>BS</sub> Prior to Start               | 54 |

| 13.3   | Power Supply Sequence                                 | 55 |

| 14 Pa  | ockage details                                        | 56 |

|        | pard mounting, part marking, and ordering information |    |

|        | · ··· · · · · · · · · · · · · · · · ·                 |    |

## **1** Qualification Information

| Qualification Level (1)  Moisture Sensitivity Level (MSL) (3) |                   | Standard (2)                                                                                |  |  |  |

|---------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------|--|--|--|

|                                                               |                   | Qualified for standard applications according to the relevant tests of J-STD-020 and JESD47 |  |  |  |

|                                                               |                   | MSL3                                                                                        |  |  |  |

|                                                               |                   | (per IPC/JEDEC J-STD-020)                                                                   |  |  |  |

| ESD                                                           | Charge Device     | Class C2a                                                                                   |  |  |  |

|                                                               | Model             | (per JEDEC standard JS-002)                                                                 |  |  |  |

|                                                               | <b>Human Body</b> | Class 1B                                                                                    |  |  |  |

|                                                               | Model             | (per JEDEC standard JS-001)                                                                 |  |  |  |

| IC Latch-Up Test                                              |                   | Class I, Level A                                                                            |  |  |  |

|                                                               |                   | (per JESD78)                                                                                |  |  |  |

| RoHS Compli                                                   | iant              | Yes                                                                                         |  |  |  |

#### Note:

- 1. Qualification standards can be found at Infineon's web site <a href="http://www.infineon.com/">http://www.infineon.com/</a>

- 2. Higher qualification ratings may be available should the user have such requirements. Please contact your Infineon Technologies sales representative for further information.

- 3. Higher MSL ratings may be available for the specific package types listed here. Please contact your Infineon Technologies sales representative for further information.

#### **Device Comparison Table** 2

#### Table 1

| Device Name | Description                                                                   |

|-------------|-------------------------------------------------------------------------------|

| MA5342MS    | 200W x 2 (8Ω) channel integrated analog input Class D audio Amplifier         |

| MA5302MS    | 200W x 2 (2Ω) channel integrated analog input Class D audio Amplifier         |

| MA5332MS    | 200W x 2 (4Ω) channel integrated analog input Class D audio Amplifier         |

| IR4302M     | 130W x 2 (4Ω) channel integrated analog input Class D audio Amplifier         |

| IR4322M     | 100W x 2 (2Ωchannel integrated analog input Class D audio Amplifier           |

| IR4301M     | 160W x 1 (4 Ω) single-channel integrated analog input Class D audio Amplifier |

| IR4321M     | 135W x 1 (2 Ω) single-channel integrated analog input Class D audio Amplifier |

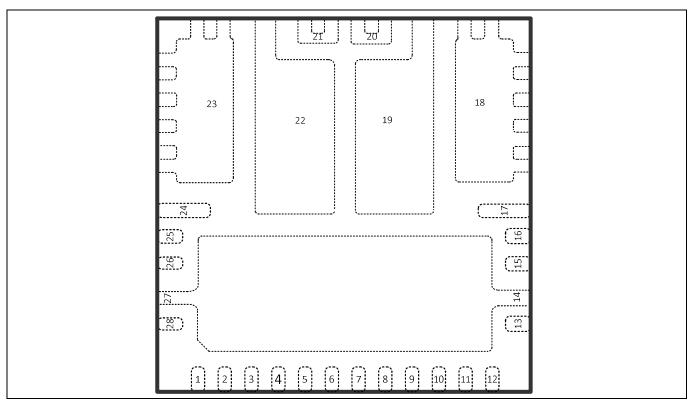

## **3** Pin Configuration

## 3.1 Lead assignments

Figure 1 Lead assignments (top view)

## 3.2 Lead definitions

| Pin# | Symbol | Description                                                                                |

|------|--------|--------------------------------------------------------------------------------------------|

| 1    | CLIP   | Clipping detection output, open drain, referenced to GND                                   |

| 2    | COMP2  | CH2 PWM comparator input                                                                   |

| 3    | IN-2   | CH2 Analog inverting input                                                                 |

| 4    | IN+2   | CH2 Analog non-inverting input                                                             |

| 5    | GND    | GND for internal shunt zener diodes to VAA and VSS, a reference to FAULT and CLIP outputs. |

| 6    | VSS    | Floating input negative supply                                                             |

| 7    | VAA    | Floating input positive supply                                                             |

| 8    | IN+1   | CH1 Analog non-inverting input                                                             |

| 9    | IN-1   | CH1 Analog inverting input                                                                 |

| 10   | COMP1  | CH1 PWM comparator input                                                                   |

| 11   | CSD    | Shutdown timing capacitor / shutdown input                                                 |

| 12   | FAULT  | Fault reporting output, open drain, referenced to GND                                      |

| 13   | VCC    | Low side supply                                                                            |

| 14   | СОМ    | Low side supply return, internally connected to pin 27                                     |

| 15   | CSH1   | CH1 High side over current sensing input, referenced to VS1                                |

| 16 | VB1  | CH1 High side floating supply                               |

|----|------|-------------------------------------------------------------|

| 17 | VS1  | CH1 PWM output, internally connected to pin 19              |

| 18 | VP1  | CH1 Positive power supply                                   |

| 19 | VS1  | CH1 PWM output                                              |

| 20 | VN1  | CH1 Negative power supply, connect to COM externally        |

| 21 | VN2  | CH2 Negative power supply, connect to COM externally        |

| 22 | VS2  | CH2 PWM output, internally connected to pin 24              |

| 23 | VP2  | CH2 Positive power supply                                   |

| 24 | VS2  | CH2 PWM output                                              |

| 25 | VB2  | CH2 High side floating supply                               |

| 26 | CSH2 | CH2 High side over current sensing input, referenced to VS2 |

| 27 | СОМ  | Low side supply return, internally connected to pin 14      |

| 28 | NC   |                                                             |

#### **Specifications** 4

#### **Absolute Maximum Ratings** 4.1

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM=VN1=VN2; all currents are defined positive into any lead. The Thermal Resistance and Power Dissipation ratings are measured under board mounted and still air conditions.

| Symbol                | Definition                                                                                                 | Min                           | Max                  | Units |

|-----------------------|------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------|-------|

| V <sub>Pn</sub>       | Positive power supply rail voltage, n=1-2                                                                  | -                             | 150                  |       |

| V <sub>Bn</sub>       | High side floating supply voltage                                                                          | -0.3                          | 165                  |       |

| V <sub>Sn</sub>       | High side floating supply voltage <sup>(2)</sup> , n=1-2                                                   | V <sub>Bn</sub> -15           | V <sub>Bn</sub> +0.3 |       |

| V <sub>CSHn</sub>     | CSH pin input voltage, n=1-2                                                                               | V <sub>Sn</sub> -0.3          | V <sub>Bn</sub> +0.3 |       |

| V <sub>cc</sub>       | Low side supply voltage <sup>(2)</sup>                                                                     | -0.3                          | 15                   |       |

| V <sub>AA</sub>       | Floating input positive supply voltage <sup>(2)</sup>                                                      | -0.3                          | 160                  |       |

| V <sub>SS</sub>       | Floating input negative supply voltage <sup>(2)</sup>                                                      | -1<br>(See I <sub>SSZ</sub> ) | GND +0.3             |       |

| V <sub>IN+n</sub>     | Floating input supply ground voltage , n=1-2                                                               | V <sub>SS</sub> -0.3          | V <sub>AA</sub> +0.3 |       |

| I <sub>INn</sub>      | Input current between IN- and IN+ pins <sup>(1)</sup> , n=1-2                                              | -                             | ±3                   | mA    |

| $V_{CSD}$             | CSD pin input voltage                                                                                      | V <sub>SS</sub> -0.3          | V <sub>AA</sub> +0.3 |       |

| $V_{COMPn}$           | COMP pin input voltage, n=1-2                                                                              | V <sub>SS</sub> -0.3          | V <sub>AA</sub> +0.3 | V     |

| $V_{\text{CLIP}}$     | CLIP pin input voltage                                                                                     | GND -0.3                      | V <sub>AA</sub> +0.3 |       |

| I <sub>CLIP</sub>     | CLIP pin sinking current                                                                                   | -                             | 5                    | mA    |

| $V_{FAULT}$           | FAULT pin input voltage                                                                                    | GND -0.3                      | V <sub>AA</sub> +0.3 | V     |

| I <sub>FAULT</sub>    | FAULT pin sinking current                                                                                  | -                             | 5                    |       |

| I <sub>AAZ</sub>      | Floating input supply zener clamp current <sup>(2)</sup>                                                   | -                             | 20                   |       |

| I <sub>SSZ</sub>      | Floating input negative supply zener clamp current <sup>(2)</sup>                                          | -                             | 20                   | mA    |

| I <sub>ccz</sub>      | Low side supply zener clamp current <sup>(2)</sup>                                                         | -                             | 20                   |       |

| I <sub>BSZn</sub>     | Floating supply zener clamp current <sup>(2)</sup> , n=1-2                                                 | -                             | 20                   |       |

| dV <sub>Sn</sub> /dt  | Allowable Vs voltage slew rate, n=1-2                                                                      | -                             | 50                   | V/ns  |

| dV <sub>SS</sub> /dt  | Allowable Vss voltage slew rate <sup>(3)</sup>                                                             | -                             | 50                   | V/ms  |

| Id <sub>@ 25°C</sub>  | Continuous output current, from VPn to VSn, VSn to VNn, $V_{CC}=10V$ , $V_{Bn}-V_{Sn}=10V$                 | -                             | 12                   |       |

| Id <sub>@ 100°C</sub> | Continuous output current, from VPn to VSn, VSn to VNn, $V_{CC}$ =10V, $V_{Bn}$ - $V_{Sn}$ =10V            | -                             | 7.8                  | A     |

| I <sub>DM</sub>       | Pulsed output current, from VPn to VSn, VSn to VNn, $V_{cc}$ =10V, $V_{Bn}$ - $V_{Sn}$ =10V <sup>(5)</sup> | -                             | 48                   |       |

| Pd                    | Power dissipation <sup>(4)</sup> @ $T_c$ = 25°C                                                            | -                             | 21                   | W     |

| Rth <sub>JC</sub>     | Thermal resistance, junction to case <sup>(4)</sup>                                                        | -                             | 5                    | °C/W  |

| TJ                    | Junction temperature                                                                                       | -                             | 150                  | °C    |

| Ts             | Storage Temperature                      | -55 | 150 |

|----------------|------------------------------------------|-----|-----|

| T <sub>L</sub> | Lead temperature (Soldering, 10 seconds) | -   | 300 |

#### Note:

- 1. IN- and IN+ contain clamping diodes between the two pins.

- 2. V<sub>AA</sub> -V<sub>SS</sub>, Vcc-COM and VBn-VSn contain internal shunt zener diodes. Note that the voltage ratings of these can be limited by the clamping current.

- 3. For the rising and falling edges of step signal of 10V. Vss=15V to 100V.

- 4. Per MOSFET.

- 5. Repetitive rating, pulse width limited by maximum junction temperature.

#### 4.2 Recommended Operating Conditions

For proper operation, the device should be used within the recommended conditions below. The Vss and Vsn offset ratings are tested with supplies biased at COM=VN1=VN2,  $V_{AA}$ - $V_{SS}$ =9.6V,  $V_{CC}$ =12V and  $V_{Bn}$ - $V_{Sn}$ =12V. All voltage parameters are absolute voltages referenced to COM; all currents are defined positive into any lead.

| Symbol            | Definition                                               |                   | Min                   | Max                   | Units |

|-------------------|----------------------------------------------------------|-------------------|-----------------------|-----------------------|-------|

| V                 | Positive power supply voltage, n=1-2, without heatsink   | -                 | 98                    |                       |       |

| V <sub>Pn</sub>   | Positive power supply voltage, n=1-2, with heatsink      | MA5342MS          | -                     | 120                   |       |

| $V_{Bn}$          | High side floating supply absolute voltage, n=1-2        |                   | V <sub>Sn</sub> +10   | V <sub>Sn</sub> +14   | □ V   |

| $V_{Sn}$          | High side floating supply offset voltage, n=1-2          | MA5342MS          | (6)                   | 80                    |       |

| V <sub>AA</sub>   | Floating input positive supply voltage <sup>(7)</sup>    | •                 | V <sub>SS</sub> +9.0  | V <sub>SS</sub> + 9.8 |       |

| $V_{SS}$          | Floating input negative supply voltage <sup>(7)</sup>    | MA5342MS          | 0                     | 150                   |       |

| I <sub>AAZ</sub>  | Floating input supply zener clamp current <sup>(7)</sup> |                   |                       | 15                    |       |

| I <sub>SSZ</sub>  | Floating input negative supply zener clamp currer        | nt <sup>(7)</sup> | 1                     | 15                    | mA    |

| $V_{cc}$          | Low side fixed supply voltage                            |                   | 10                    | 15                    |       |

| $V_{IC}$          | IN- and IN+ pins common mode input voltage               |                   | V <sub>SS</sub> + 2   | V <sub>AA</sub> - 2   | V     |

| $V_{\text{IN-n}}$ | Inverting input voltage, n=1-2                           |                   | V <sub>IN+</sub> -0.5 | V <sub>IN+</sub> +0.5 |       |

| $V_{\text{CSD}}$  | CSD pin input voltage                                    |                   | V <sub>SS</sub>       | V <sub>AA</sub>       |       |

| $V_{COMPn}$       | COMP pin input voltage, n=1-2                            |                   |                       | V <sub>AA</sub>       |       |

| $C_{COMPn}$       | COMP pin phase compensation capacitor to GND , n=1-2     |                   |                       | -                     | nF    |

| V <sub>CSHn</sub> | CSH pin input voltage, n=1-2                             |                   |                       | $V_{Bn}$              | V     |

| f <sub>SW</sub>   | Switching frequency                                      |                   |                       | 500                   | kHz   |

| TJ                | Junction temperature <sup>(8)</sup>                      |                   |                       | 85                    | °C    |

#### Note:

- 6. Logic operational for Vs equal to -5V to +150V. Logic state held for Vs equal to -5V to  $-V_{BS}$ .

- 7. GND input voltage is limited by I<sub>AAZ</sub> and I<sub>SSZ</sub>.

- 8. Long term average temperature. The device is operational up to  $T_{J_{-}IC}$  100 °C.

#### 4.3 Electrical Characteristics

Unless otherwise specified, the following apply:

- V<sub>CC</sub>,V<sub>BS</sub>= 12 V

- $\bullet \quad V_{SS} = V_{S1} = V_{S2} = V_{N1} = V_{N2} = COM = 0V$

- V<sub>AA</sub>=9.6V

- T<sub>A</sub>=25°C

Table 2

Electrical characteristics

| Symbol                    | Definition                                                | Min  | Тур  | Max  | Units | Test conditions                              |

|---------------------------|-----------------------------------------------------------|------|------|------|-------|----------------------------------------------|

| Low-side s                | upply                                                     |      |      |      |       |                                              |

| UV <sub>CC+</sub>         | Vcc supply UVLO positive threshold                        | 8.4  | 8.9  | 9.4  | V     |                                              |

| UV <sub>cc-</sub>         | Vcc supply UVLO negative threshold                        | 8.2  | 8.7  | 9.2  | V     |                                              |

| $UV_{CCHYS}$              | UV <sub>cc</sub> hysteresis                               | -    | 0.2  | -    | V     |                                              |

| I <sub>QCC</sub>          | Low side quiescent current                                | -    | -    | 3    | mA    |                                              |

| I <sub>cc</sub>           | Low side supply current                                   | -    | 10   | -    | mA    | f=400kHz                                     |

| V <sub>CLAMPL</sub> n     | Low side zener diode clamp<br>voltage, n=1-2              | 14.7 | 15.3 | 16.2 | V     | I <sub>cc</sub> =5mA                         |

| High-side f               | loating supply                                            |      |      |      |       |                                              |

| $UV_{BS+n}$               | High side well UVLO positive threshold, n=1-2             | 8.0  | 8.5  | 9.0  | V     |                                              |

| UV <sub>BS-n</sub>        | High side well UVLO negative threshold, n=1-2             | 7.8  | 8.3  | 8.8  | V     |                                              |

| UV <sub>BSHYSn</sub>      | UV <sub>BS</sub> hysteresis, n=1-2                        | -    | 0.2  | -    | V     |                                              |

| $I_{QBSn}$                | High side quiescent current, n=1-2                        | -    | -    | 2.4  | mA    |                                              |

| I <sub>QBSn_OFF-CSH</sub> | High side quiescent current,<br>with CSH pin open n=1-2   | 350  | 500  | 650  | uA    |                                              |

| V <sub>CLAMPHn</sub>      | High side zener diode clamp<br>voltage, n=1-2             | 14.7 | 15.3 | 16.2 | V     | I <sub>BS</sub> =5mA                         |

| Floating in               | put supply                                                |      |      | •    | •     |                                              |

| UV <sub>AA+</sub>         | VA+, VA- floating supply UVLO positive threshold from Vss | 8.2  | 8.7  | 9.2  | V     | V <sub>SS</sub> =0V, GND pin floating        |

| UV <sub>AA-</sub>         | VA+, VA- floating supply UVLO negative threshold from Vss | 7.7  | 8.2  | 8.7  | V     | V <sub>SS</sub> =0V, GND pin floating        |

| UV <sub>AAHYS</sub>       | UV <sub>AA</sub> hysteresis                               | -    | 0.5  | -    | V     | V <sub>SS</sub> =0V, GND pin floating        |

| I <sub>QAA0</sub>         | Floating Input positive quiescent supply current          | -    | 1.5  | 3    | mA    | $V_{AA}$ =9.6V, $V_{SS}$ =0V, $V_{CSD}$ =VSS |

| I <sub>QAA1</sub>         | Floating Input positive quiescent supply current          | -    | 4    | 6    | mA    | $V_{AA}$ =9.6V, $V_{SS}$ =0V, $V_{CSD}$ =VAA |

| I <sub>QAA2</sub>                   | Floating Input positive quiescent supply current                                                                                                 | -      | 5                                      | 7.5  | mA    | $V_{AA}$ =9.6V, $V_{SS}$ =0V, $V_{CSD}$ =GND                         |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------|------|-------|----------------------------------------------------------------------|

| I <sub>LKM</sub>                    | Floating input side to Low side leakage current                                                                                                  | -      | -                                      | 50   | μΑ    | V <sub>AA</sub> =V <sub>SS</sub> =V <sub>GND</sub> =<br>100V         |

| V <sub>CLAMPM</sub> +               | V <sub>AA</sub> floating supply zener diode<br>clamp voltage, positive, with<br>respect to GND                                                   | 4.9    | 5.1                                    | 5.4  | V     | $I_{AA}$ =5mA,<br>$I_{SS}$ =5mA,<br>$V_{GND}$ =0V,<br>$V_{CSD}$ =VSS |

| V <sub>CLAMPM</sub> -               | V <sub>SS</sub> floating supply zener diode<br>clamp voltage, negative, with<br>respect to GND                                                   | -5.4   | -5.1                                   | -4.9 | V     | $I_{AA}$ =5mA,<br>$I_{SS}$ =5mA,<br>$V_{GND}$ =0V,<br>$V_{CSD}$ =VSS |

| Audio inp                           | ut (V <sub>GND</sub> =0, V <sub>AA</sub> =4.8V, V <sub>SS</sub> =-4.8V)                                                                          |        |                                        |      |       |                                                                      |

| $V_{OSn}$                           | Input offset voltage, n=1-2                                                                                                                      | -18    | 0                                      | 18   | mV    |                                                                      |

| I <sub>BINn</sub>                   | Input bias current, n=1-2                                                                                                                        | -      | -                                      | 40   | nA    |                                                                      |

| GBWn                                | Small signal bandwidth in OTA, n=1-2                                                                                                             | -      | 9                                      | -    | MHz   | C <sub>COMP</sub> =2nF, Rf=0                                         |

| $g_{mn}$                            | OTA transconductance, n=1-2                                                                                                                      | -      | 10                                     | -    | mS    | V <sub>IN+</sub> =0V, V <sub>IN-</sub><br>=10mV                      |

| G <sub>Vn</sub>                     | OTA gain, n=1-2                                                                                                                                  | 50     | -                                      | -    | dB    |                                                                      |

| V <sub>Nrmsn</sub>                  | CHn OTA noise voltage, n=1-2                                                                                                                     | -      | 200                                    | 330  | mVrms |                                                                      |

| PWM                                 |                                                                                                                                                  |        |                                        |      |       | _                                                                    |

| Vth <sub>PWM</sub>                  | PWM comparator threshold in COMP                                                                                                                 | -      | (V <sub>AA</sub> - V <sub>SS</sub> )/2 | -    | V     |                                                                      |

| f <sub>OTAn</sub>                   | COMP pin star-up local oscillation frequency, n=1-2                                                                                              | 0.7    | 1.0                                    | 1.5  | MHz   | V <sub>CSD</sub> =GND                                                |

| Ton_n                               | COMP to VS rising edge propagation delay, n=1-2                                                                                                  | -      | 370                                    | -    | ns    |                                                                      |

| Toff_n                              | COMP to VS trailing edge propagation delay, n=1-2                                                                                                | -      | 320                                    | -    | ns    |                                                                      |

| DTn                                 | Deadtime: Low-side turn-off to High-side turn-on ( $DT_{\text{LO-HO}}$ ) & High-side turn-off to Low-side turn-on ( $DT_{\text{HO-LO}}$ ), n=1-2 | -      | 50                                     | -    | ns    | VP=30V,<br>VN=-30V,                                                  |

|                                     | OSFET (FET1, FET2, FET3, FET4) (MA5 unless otherwise specified                                                                                   | 342MS) |                                        |      |       |                                                                      |

| V <sub>(BR)DSS</sub> <sup>(8)</sup> | Drain-to-Source breakdown voltage                                                                                                                | 150    | -                                      | -    | V     | $V_{GS}$ =0 $V$ , $I_D$ =1 $mA$                                      |

| R <sub>DS(ON)</sub>                 | FET on resistance                                                                                                                                | -      | 49.2                                   | 61.6 | mΩ    | I <sub>D</sub> =3.3A, V <sub>GS</sub> =10V                           |

| Qg                                  | Total gate charge                                                                                                                                | -      | 7.2                                    | 9.36 | nC    | V <sub>GS</sub> =10V                                                 |

| I <sub>LK0</sub>                    | VP leakage current, VS=VN                                                                                                                        | -      | -                                      | 20   | μΑ    | $V_P=150V^{(8)},$ $V_{CSD}=VSS$                                      |

| Protection           |                                                                                        |                      |                      |                      |    |                           |

|----------------------|----------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|----|---------------------------|

| I <sub>OCPn</sub>    | Over current detection Positive threshold, n=1-2 <sup>(8)</sup>                        | -                    | 30                   | -                    | А  |                           |

| I <sub>OCNn</sub>    | Over current detection Negative threshold, n=1-2 <sup>(9)</sup>                        | -                    | -30                  | -                    | А  |                           |

| Vth1                 | CSD pin shutdown release threshold                                                     | 0.62xV <sub>AA</sub> | 0.70xV <sub>AA</sub> | 0.78xV <sub>AA</sub> | V  |                           |

| Vth2                 | CSD pin self-reset threshold                                                           | 0.26xV <sub>AA</sub> | 0.30xV <sub>AA</sub> | 0.34xV <sub>AA</sub> | V  |                           |

| I <sub>CSD+</sub>    | CSD pin discharge current                                                              | 70                   | 100                  | 130                  | μΑ | $V_{CSD} = V_{SS} + 4.8V$ |

| I <sub>CSD-</sub>    | CSD pin charge current                                                                 | 70                   | 100                  | 130                  | μΑ | $V_{CSD} = V_{SS} + 4.8V$ |

| t <sub>SDn</sub>     | Shutdown propagation delay from V <sub>S</sub> < Vth1 to Shutdown, n=1-2               | -                    | -                    | 250                  | ns | COMP = V <sub>SS</sub>    |

| t <sub>OCPn</sub>    | CHn propagation delay time from I <sub>on</sub> > I <sub>OCPn</sub> to Shutdown, n=1-2 | -                    | -                    | 500                  | ns | COMP = V <sub>SS</sub>    |

| t <sub>OCNn</sub>    | CHn propagation delay time from I <sub>on</sub> < I <sub>OCNn</sub> to Shutdown, n=1-2 | -                    | -                    | 500                  | ns | COMP = V <sub>SS</sub>    |

| Vth+ <sub>CLIP</sub> | Clip detection positive threshold in COMP                                              | 0.85xV <sub>AA</sub> | 0.90xV <sub>AA</sub> | 0.95xV <sub>AA</sub> | V  |                           |

| Vth- <sub>CLIP</sub> | Clip detection negative threshold in COMP                                              | 0.05xV <sub>AA</sub> | 0.10xV <sub>AA</sub> | 0.15xV <sub>AA</sub> | V  |                           |

| t <sub>CLIP</sub>    | Clipping detection propagation delay                                                   | -                    | 40                   | -                    | ns |                           |

| t <sub>CLIPmin</sub> | Clipping detection minimum output duration                                             | -                    | 3                    | -                    | us |                           |

| T <sub>SD</sub>      | Over-temperature shutdown threshold in controller IC                                   | 100                  | -                    | -                    | °C |                           |

| $T_{SDHYS}$          | Over-temperature shutdown threshold hysteresis                                         | -                    | 7                    | -                    | °C |                           |

#### **Audio Characteristics (SE)** 4.4

#### Table 3

| Parameter                                   | Test conditions                                                | Тур | Unit |

|---------------------------------------------|----------------------------------------------------------------|-----|------|

| Po Power output per channel <sup>(10)</sup> | RL= $8\Omega$ , $10\%$ THD+N, $V_{bus} = \pm 52.2 \text{ V}$   | 210 | W    |

|                                             | RL= $6\Omega$ , $10\%$ THD+N, $V_{bus} = \pm 44 \text{ V}$     | 190 |      |

|                                             | RL= $4\Omega$ , $10\%$ THD+N, $V_{bus}$ = $\pm 36.4$ V         | 190 |      |

|                                             |                                                                |     |      |

|                                             | RL= $8\Omega$ , 1%THD+N, $V_{bus}$ = $\pm$ 52.2 V              | 160 |      |

|                                             | RL= $6\Omega$ , 1%THD+N, $V_{bus} = \pm 44 \text{ V}$          | 150 |      |

|                                             | RL= $4\Omega$ , 1%THD+N, $V_{bus} = \pm 36.4 \text{ V}$        | 150 |      |

|                                             |                                                                |     |      |

| Residual noise(AES-17, IHF-A, typical)      | EVAL_MA5342MS_200Wx2 , $V_{bus}$ = $\pm$ 52.2 V ,RL= $8\Omega$ | 220 | uV   |

| Idling supply current                       | $V_{\text{bus}} = \pm 52.2 \text{ V}$ ,RL= $8\Omega$           | 25  | mA   |

|                                             |                                                                | -35 |      |

## Integrated Class D Amplifier

| Parameter                  | Test conditions                                                      | Тур | Unit |

|----------------------------|----------------------------------------------------------------------|-----|------|

| Efficiency <sup>(11)</sup> | EVAL_MA5342MS_200Wx2 , $V_{bus} = \pm 52.2 \text{ V}$ ,RL= $8\Omega$ | 95  | %    |

#### Note:

- 9.  $V_p$  changes over temperature at a rate of 50mV/K compared to Tj=25°C.

- 10. Over-current protection threshold measured under Tj=25°C condition.

- 11. Tested with heatsink (digikey part number: V8818V)

- 12. Class D stage only

## 4.5 Audio Characteristics (BTL)

#### Table 4

| Parameter                                  | Test conditions                                                         | Тур | Unit |

|--------------------------------------------|-------------------------------------------------------------------------|-----|------|

| Po Power output per channel <sup>(9)</sup> | $RL= 16\Omega, 10\%THD+N, V_{bus} = \pm 52.2 V$                         | 420 | W    |

|                                            | $RL= 12\Omega, 10\%THD+N, V_{bus} = \pm 44 V$                           | 380 |      |

|                                            | RL= $8\Omega$ , $10\%$ THD+N, $V_{bus} = \pm 36.4 \text{ V}$            | 380 |      |

|                                            |                                                                         |     |      |

|                                            | RL= $16\Omega$ , $1\%$ THD+N, $V_{bus} = \pm 52.2 \text{ V}$            | 320 |      |

|                                            | RL= $12\Omega$ , $1\%$ THD+N, $V_{bus} = \pm 44 \text{ V}$              | 300 |      |

|                                            | RL= $8\Omega$ , 1%THD+N, $V_{bus} = \pm 36.4V$                          | 300 |      |

|                                            |                                                                         |     |      |

| Residual noise(AES-17, IHF-A, typical)     | EVAL_MA5342MS_200Wx2 , $V_{bus} = \pm 52.2 \text{ V}$ , $RL = 16\Omega$ | 330 | uV   |

| Idling supply current                      | $V_{\text{bus}} = \pm 52.2 \text{ V}, \text{RL} = 16\Omega$             | 25  | mA   |

|                                            |                                                                         | -35 |      |

| Efficiency <sup>(10)</sup>                 | EVAL_MA5342MS_200Wx2 , $V_{bus} = \pm 52.2 \text{ V}$ , RL= $16\Omega$  | 95  | %    |

## 4.6 Audio Characteristics (PSE)

#### Table 5

| Parameter                                  | Test conditions                                                         | Тур | Unit |

|--------------------------------------------|-------------------------------------------------------------------------|-----|------|

| Po Power output per channel <sup>(9)</sup> | RL= $4\Omega$ , 10%THD+N, $V_{bus} = \pm 52.2 \text{ V}$                | 420 | W    |

|                                            | $R_L = 4\Omega$ , 1%THD+N, $V_{bus} = \pm 52.2 \text{ V}$               | 320 |      |

| Residual noise(AES-17, IHF-A, typical)     | EVAL_MA5342MS_200Wx2 , $V_{bus} = \pm 52.2V$ , $RL = 4\Omega$           | 220 | uV   |

| Idling supply current                      | EVAL_MA5342MS_200Wx2 , $V_{bus} = \pm 52.2 \text{ V}$ , $R_L = 4\Omega$ | 25  | mA   |

|                                            |                                                                         | -35 |      |

| Efficiency <sup>(10)</sup>                 | EVAL_MA5342MS_200Wx2, $V_{bus} = \pm 52.2 \text{ V}$ , $Rl = 4\Omega$   | 95  | %    |

## **Typical Audio Characteristics (SE)**

Test conditions:

All Measurements taken at Sine wave frequency= 1 kHz, AES17+ AUX-0025measurementfilters.

$V_{bus}$  = ± 52.2 V, Load impedance = 8  $\Omega$ ,  $F_{PWM}$  = 400 kHz

$V_{bus} = \pm 44 \text{ V}$ , Load impedance = 6  $\Omega$ ,  $F_{PWM} = 400 \text{ kHz}$

$V_{\text{bus}}$  = ± 36.4 V, Load impedance = 4  $\Omega,\,F_{\text{PWM}}$  = 400 kHz

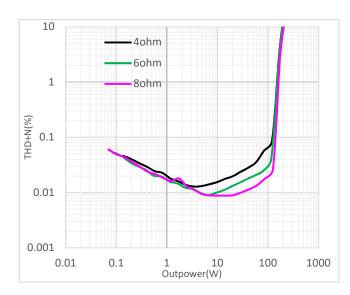

#### 4.6.1 Power vs. THD+N

Figure 2 Power vs. THD+N

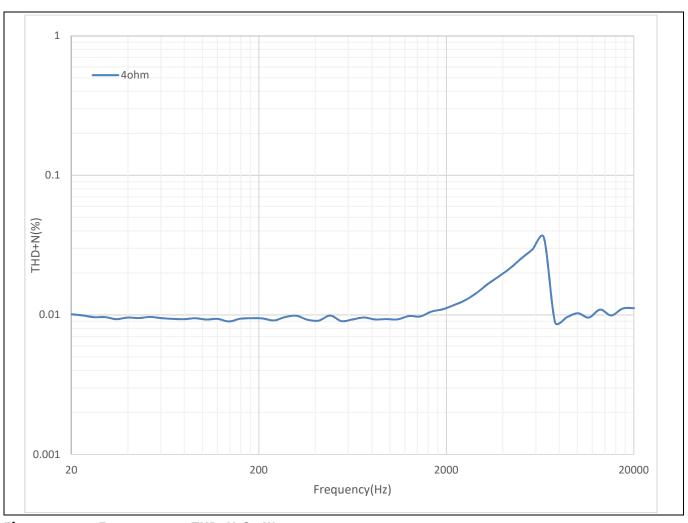

## 4.6.2 Frequency vs. THD+N

Figure 3 Frequency vs. THD+N @1W

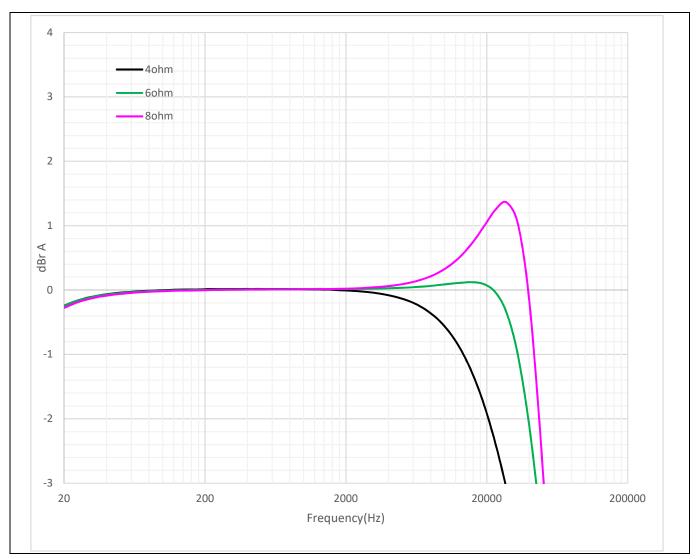

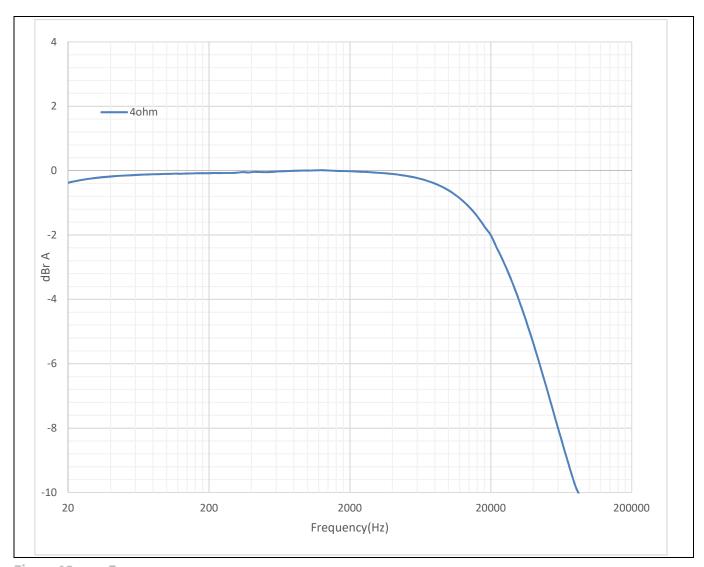

## 4.6.3 Frequency Response

Test conditions:

Output power = 1 W, fixed LPF 33uH+0.22uF

Figure 4 Frequency response

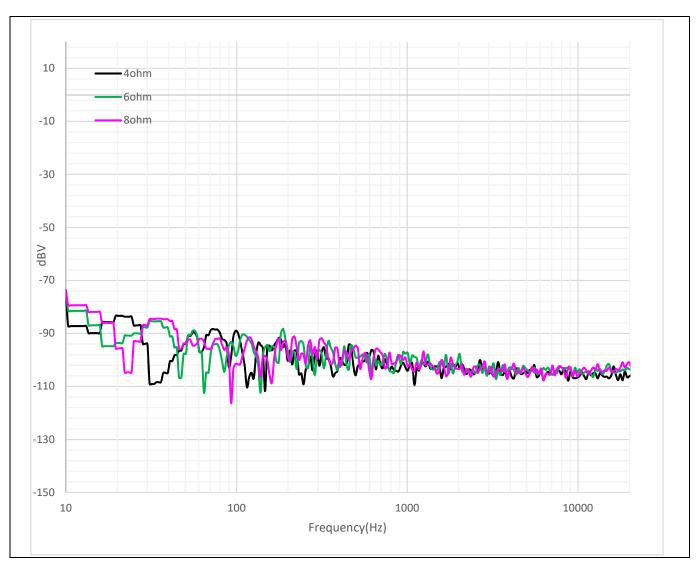

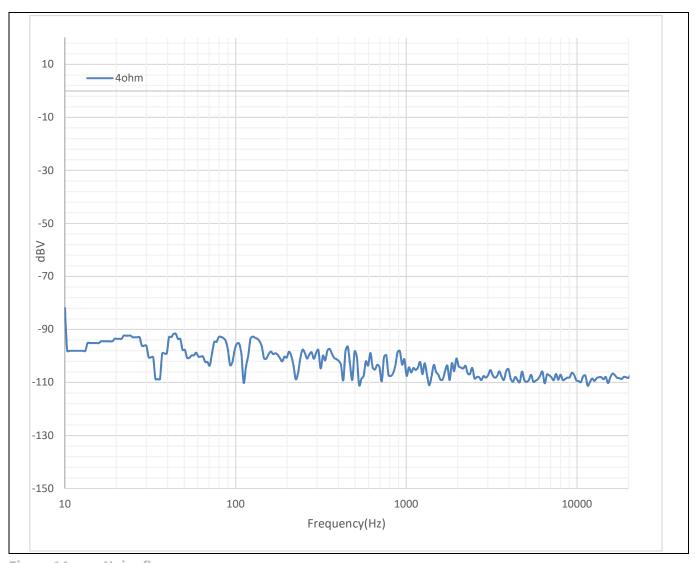

#### 4.6.4 Noise Floor

### No input signal

Figure 5 Noise floor

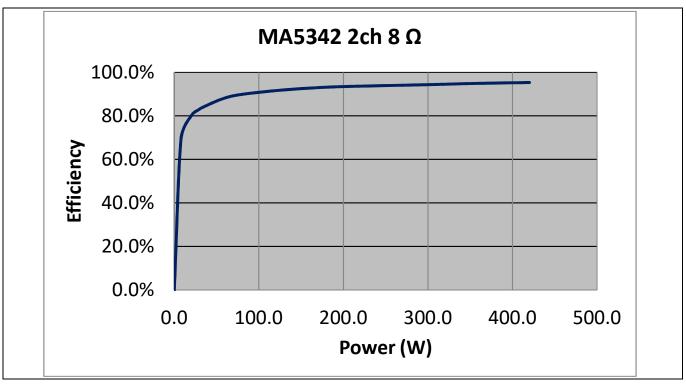

## 4.6.5 Efficiency

Figure 6 Efficiency 8  $\Omega$  load

## 4.7 Typical Audio Characteristics (BTL)

Test conditions:

All Measurements taken at Sine wave frequency= 1 kHz, AES17+ AUX-0025 measurement filters.

$V_{bus}$  = ± 52.2 V, Load impedance = 16  $\Omega$ ,  $F_{PWM}$  = 400 kHz

$V_{bus}$  = ± 44 V, Load impedance = 12  $\Omega$ ,  $F_{PWM}$  = 400 kHz

$V_{bus}$  = ± 36.4 V, Load impedance = 8  $\Omega$ ,  $F_{PWM}$  = 400 kHz

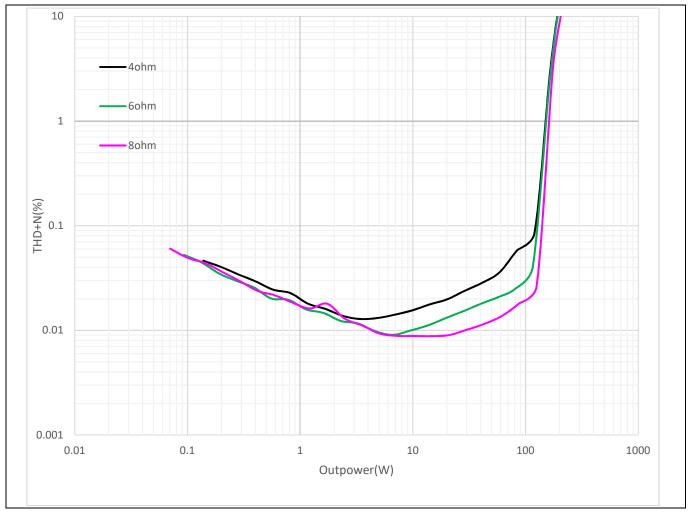

#### 4.7.1 Power vs. THD+N

Figure 7 Power vs. THD+N

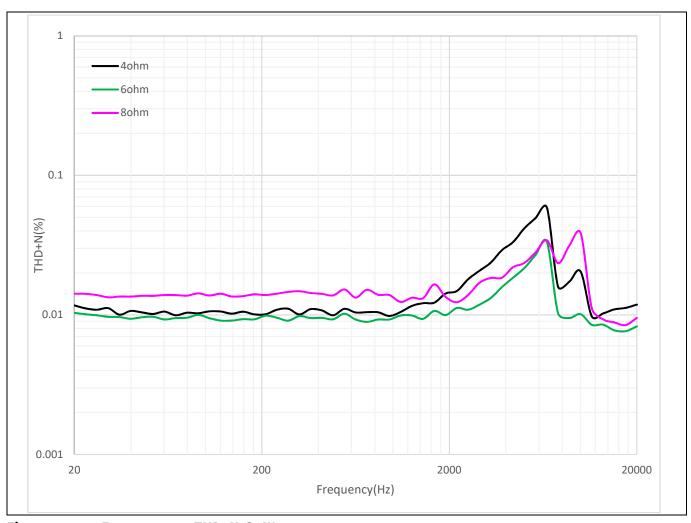

## 4.7.2 Frequency vs. THD+N

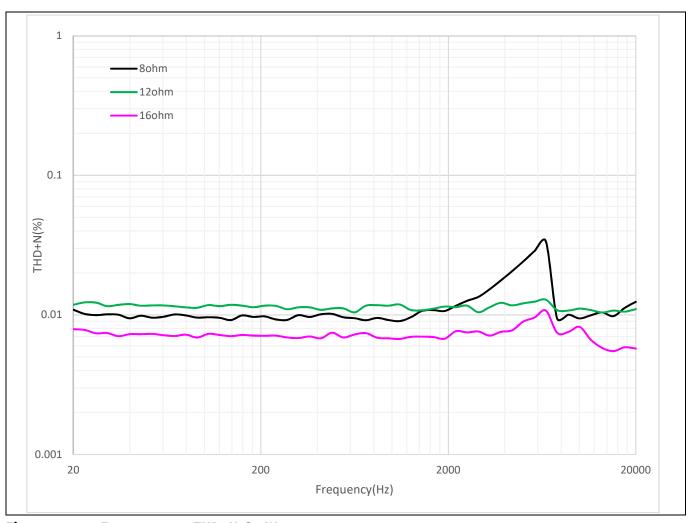

Figure 8 Frequency vs. THD+N @ 1W

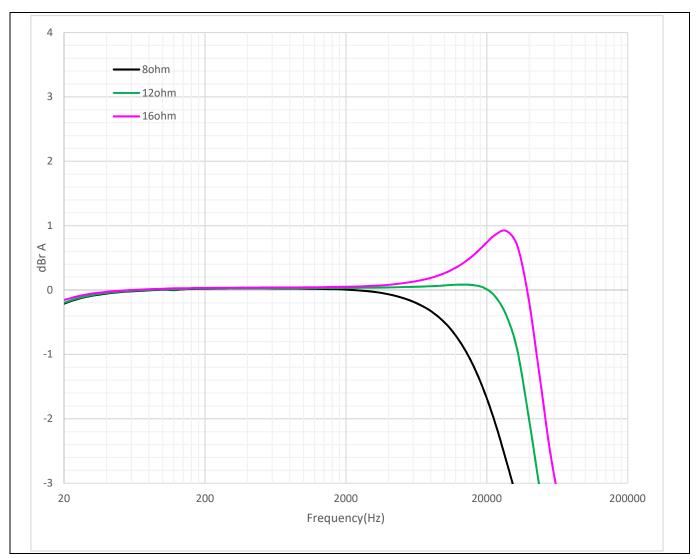

## 4.7.3 Frequency Response

Test conditions:

Output power = 1 W, fixed LPF 33uH+0.22uF

Figure 9 Frequency response

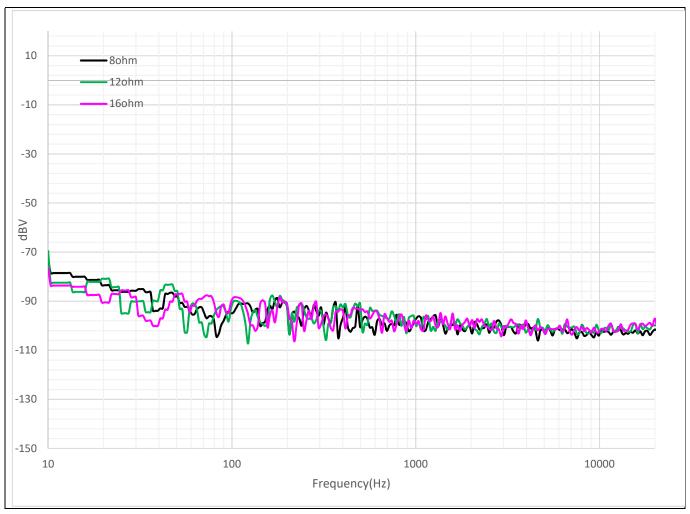

#### 4.7.4 Noise Floor

Test conditions:

No input signal

Figure 10 Noise floor

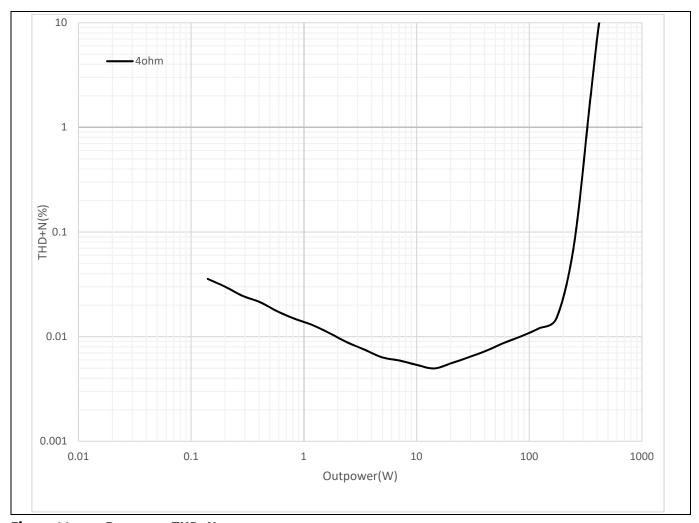

## **4.8** Typical Audio Characteristics (PSE)

Test conditions:

All Measurements taken at Sine wave frequency= 1 kHz, AES17+ AUX-0025measurement filters.

$V_{bus}$  = ±52.2 V, Load impedance = 4  $\Omega$ ,  $F_{PWM}$  = 400 kHz

#### 4.8.1 Power vs. THD+N

Figure 11 Power vs. THD+N

## 4.8.2 Frequency vs. THD+N

Figure 12 Frequency vs. THD+N @ 1W

## 4.8.3 Frequency Response

Test conditions:

Output power = 1 W, fixed LPF 33uH+0.22uF

Figure 13 Frequency response

#### 4.8.4 Noise Floor

Test conditions:

No input signal

Figure 14 Noise floor

## 5 Thermal Information

MA5342MS benefits from a unique co-packaging technique and superior MOSFET technology, resulting in best-in-class thermal performance and peak power duration. It is capable of delivering 100W x 2 at  $8\Omega$  even without requiring a heatsink

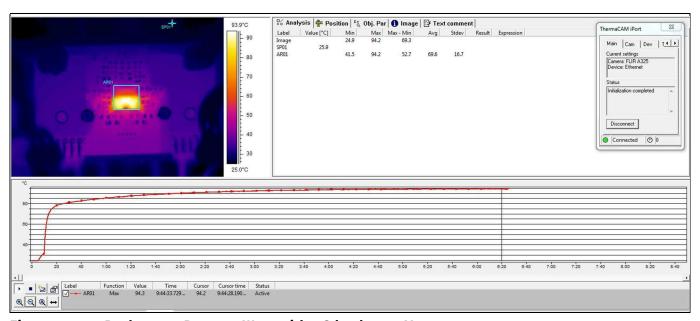

#### 5.1 Maximum Wrms Duration Thermal Information

#### Test conditions:

All Measurements are taken at Sinewave frequency= 1 kHz, AES17+ AUX-0025 measurement filters. Input signal = 1 kHz,  $F_{PWM} = 400 \text{ kHz}$ .

Tests are based on EVAL\_MA5342MS\_200Wx2 board when both channels are driven

Table 6 Peak power with heatsink

| Load (Ω) | ±V <sub>bus</sub> (V) | 10 percent THD+N power (W) | Duration                               |

|----------|-----------------------|----------------------------|----------------------------------------|

| 8        | 52.2                  | 210                        | More than 1 minute no thermal shutdown |

| 6        | 44                    | 190                        |                                        |

| 4        | 36.4                  | 190                        |                                        |

|          |                       |                            |                                        |

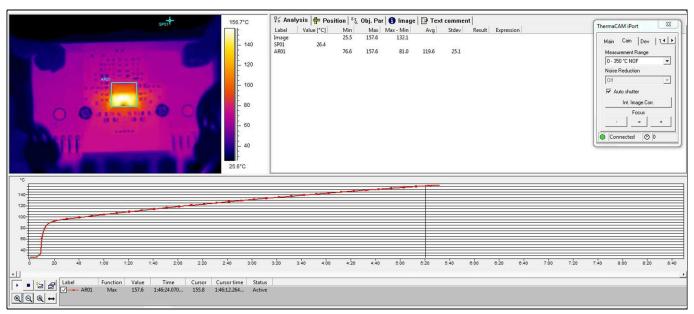

Figure 15 Peak power  $P_{out} = 210W \times 2$  with  $8 \Omega \log \pm 52.2 V$

Note: Maximum temperature 94°C at 6 minutes.

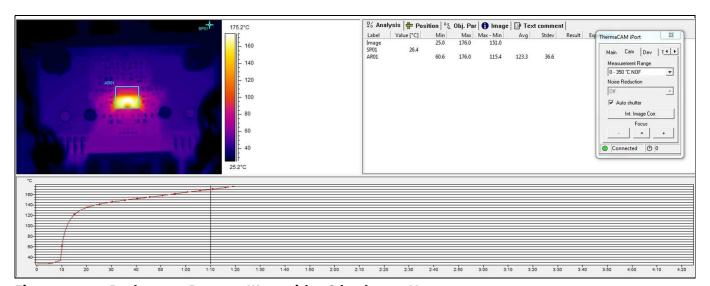

Figure 16 Peak power  $P_{out} = 190W \times 2$  with  $6 \Omega \log \pm 44 V$

Note: Maximum temperature 157°C at 5.5 minutes.

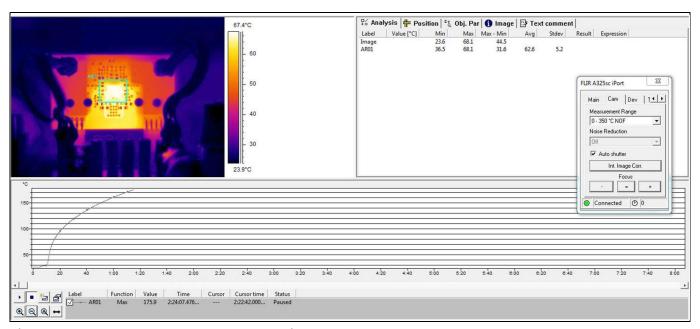

Figure 17 Peak power  $P_{out} = 190W \times 2$  with  $4 \Omega \log \pm 36.4 V$

Note: Maximum temperature 175°C at 1.33 minutes.

Table 7 Peak power without heatsink

| Load (Ω) | ±V <sub>bus</sub> (V) | 10 percent THD+N power<br>(W) | Duration                               |

|----------|-----------------------|-------------------------------|----------------------------------------|

| 8        | 44                    | 144                           | More than 1 minute no thermal shutdown |

| 4        | 24.5                  | 85                            |                                        |

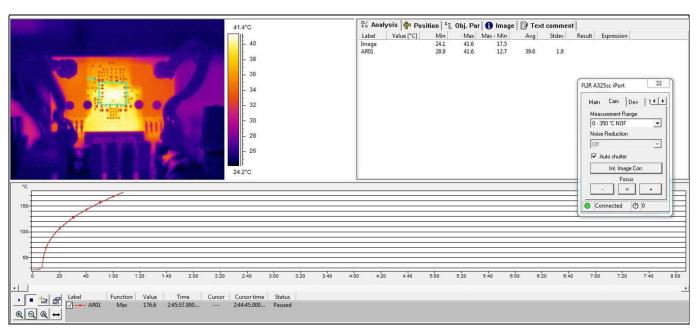

Figure 18 Peak power  $P_{out} = 144W \times 2$  with 8  $\Omega$  load  $\pm 44 \text{ V}$

Note: Maximum temperature 175°C at 1 minute.

Figure 19 Peak power  $P_{out}$  = 85W x 2 with 4  $\Omega$  load ±24.5 V

Note: Maximum temperature 175°C at 1 minute.

## Table 8 1/8 power test with heatsink

| Load (Ω) | ±V <sub>bus</sub> (V) | Max. T-case (°C) | 1/8 power (W) | Duration (minutes) |

|----------|-----------------------|------------------|---------------|--------------------|

| 8        | 52.1                  | 88.5             | 21            | 30                 |

| 6        | 44                    | 84.5             | 18.6          | 30                 |

| 4        | 36.4                  | 86.8             | 18.5          | 30                 |

|          |                       |                  |               |                    |

#### Table 9 1/8 power test without heatsink

| Load (Ω) | ±V <sub>bus</sub> (V) | Max. T-case (°C) | 1/8 power (W) | Duration (minutes) |

|----------|-----------------------|------------------|---------------|--------------------|

| 4        | 44                    | 83.7             | 10.8          | 30                 |

| 2        | 24.5                  | 83               | 9.3           | 30                 |

## 5.2 Heatsink Information

Heatsink: V8818V

Thermal pad: BER161-ND

Figure 20 Heatsink installation

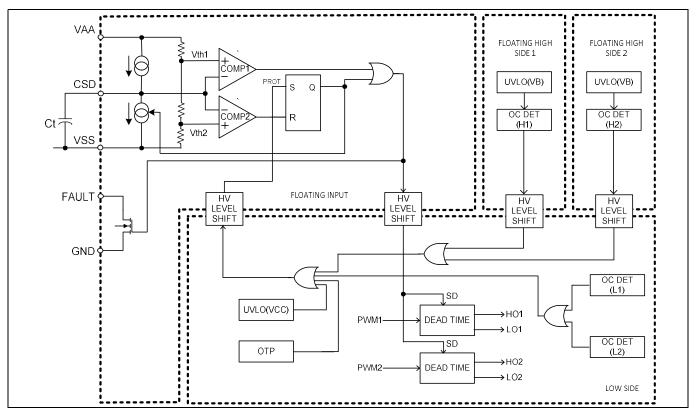

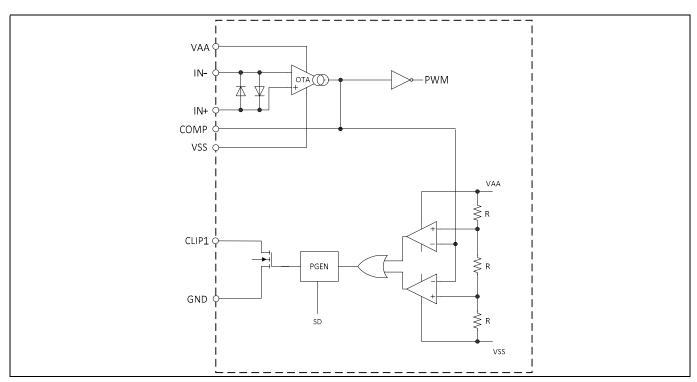

## 6 Functional Block Diagram

Figure 21 Block diagram

## 7 Typical Implementation

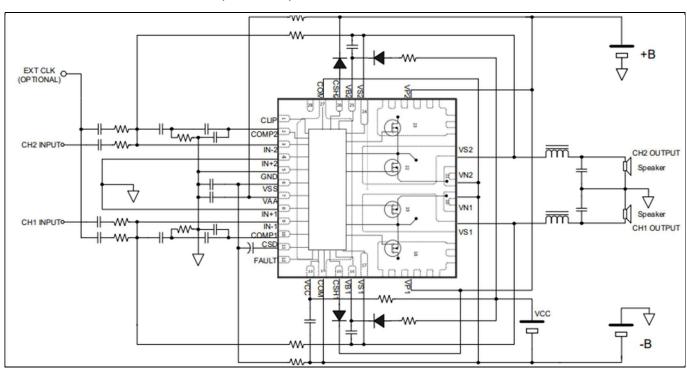

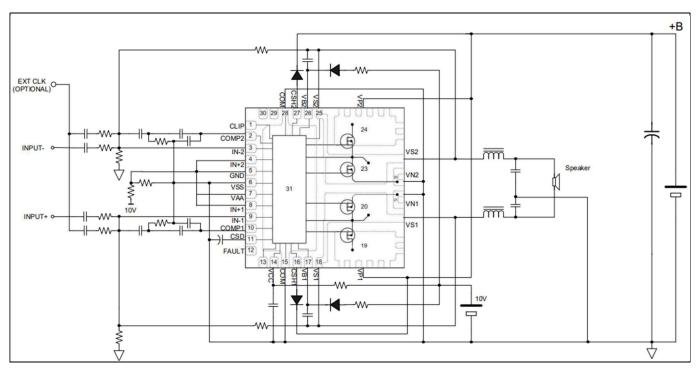

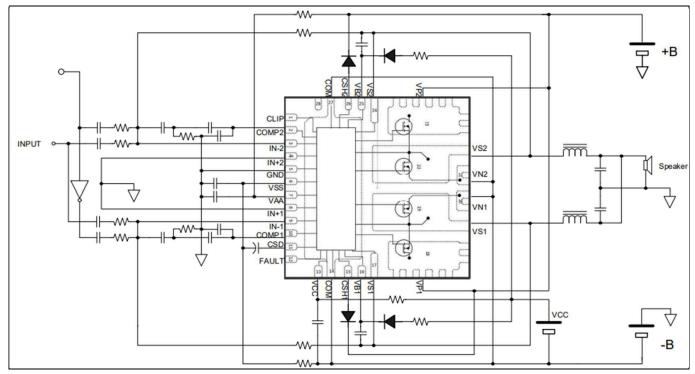

The MA5342MS can be designed as single-ended BTL or PSE output, using a single or split power supply. Here are examples of typical configurations.

A configuration for single-ended input with split power supply sets the base example. The front end section refers to GND which is common to speaker output GND.

Figure 22 Inverting amplifier with Split Power Supply

Figure 23 Differential amplifier with Split Power Supply

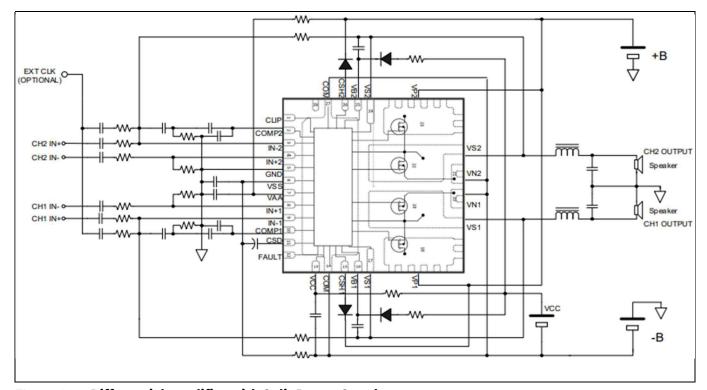

The single-supply configuration uses a virtual GND which sits in the middle of the power supply rail. The frontend section of the amplifier refers to the virtual GND as a reference. This method uses differential input to receive an input signal from a different voltage potential. It is recommended to allow input capacitors to fully settle to steady-state values before releasing the CSD pin to start PWM oscillation. The load current and inductor ripple current flow through the bus splitting capacitor.

**Typical Application Circuit with Single Power Supply** Figure 24

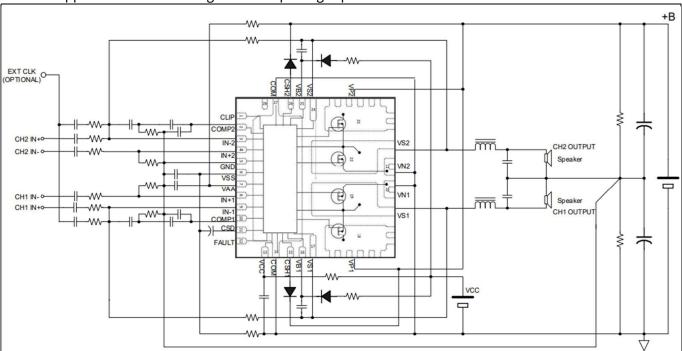

Balanced Tied Load (BTL) output takes two output legs for speaker output. It doubles output power with double load impedance. Any load current does not flow through supply dividing capacitor; therefore BTL configuration is free from GND fluctuations. Also, the bus splitting capacitor can be much smaller. Higher output power and absence of GND fluctuation make BTL suitable for subwoofer applications.

Typical Bridged Tied Load (BTL) Output Application with Split Power Supply Figure 25

Figure 26 Typical Bridged Tied Load (BTL) Output Application with Single Power Supply

Parallel Single Ended (PSE) output parallels two channels' output legs for one speaker output. It doubles output current and makes it easier to drive a low impedance load. Higher output current with lower bus voltage makes PSE suitable for subwoofer applications.

Figure 27 PSE amplifier with Split Power Supply

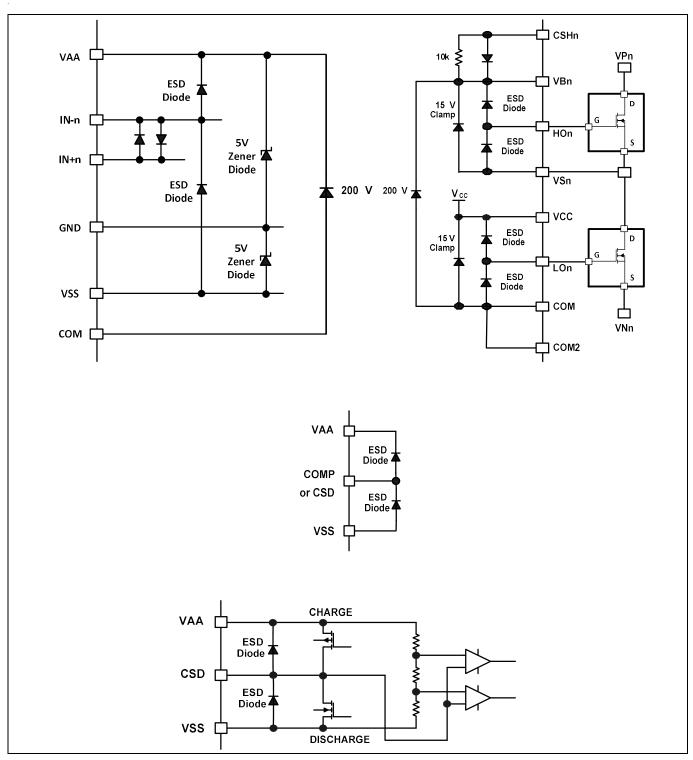

# 8 Input / Output pin equivalent circuit diagrams

Figure 28 Input/output pin equivalent circuit diagrams

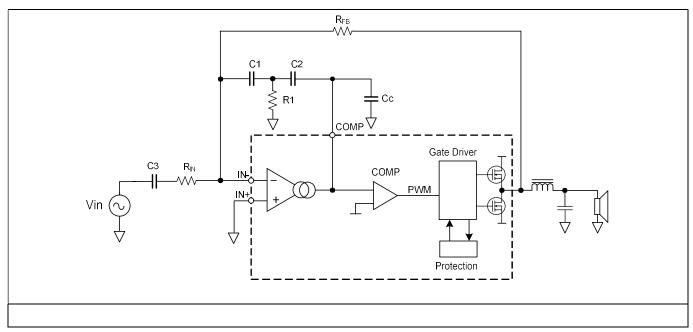

#### 9 **PWM Modulator Design**

The open-access front-end configuration of MA5342MS enables many ways to implement a PWM modulator. This section explains how PWM modulation works based on an example of a self-oscillating PWM modulator in a typical application.

Figure 29 **MA5342MS Typical Control Loop Design**

#### 9.1 **Input Section**

The audio input stage of MA5342MS forms an inverting error amplifier. The voltage gain of the amplifier, G<sub>V</sub>, is determined by the ratio between input resistor R<sub>IN</sub> and feedback resistor R<sub>FB</sub>.

$$G_V = \frac{R_{FB}}{R_{IN}}$$

Since the feedback resistor R<sub>FB</sub> is part of an integrator time constant, which determines switching frequency, changing the overall voltage gain by R<sub>IN</sub> is simpler and therefore recommended. Note that the input impedance of the amplifier is equal to the input resistor R<sub>IN</sub>.

A DC blocking capacitor C3 should be connected in series with R<sub>IN</sub> to minimize the DC offset voltage on the output. Due to potential distortion, a ceramic capacitor is not recommended. Minimizing the DC offset is essential to minimize the audible noise during power-ON and -OFF.

The connection of the non-inverting input IN+ is a reference for the error amplifier, and thus is crucial for audio performance. Connect IN+ to the signal reference ground in the system, which has the same potential as the negative terminal of the speaker output.

#### 9.2 **Control Loop Design**

The MA5342MS allows the user to choose from numerous methods of PWM modulator implementations. In this section, all the explanations are based on a typical application circuit of a self-oscillating

#### 9.3 **PWM Frequency**

Choosing the switching frequency entails making a trade-off between many aspects. At lower switching frequency, conduction losses in the MOSFET stage increases due to higher inductor ripple current. The output carrier leakage in the speaker output increases. At higher switching frequency, the efficiency degrades due to higher switching losses. Higher switching frequency supports wider audio bandwidth. The inductor ripple decreases yet core loss might increase. For these reasons, 400kHz is chosen for a typical design example.

Self-oscillating frequency has little influence from the bus voltage and input resistance RIN. Note that the nature of a self-oscillating PWM is for the switching frequency to decrease as PWM modulation deviates from idling.

Table 6 summarizes suggested values of components for a given target self-oscillating frequency. The front-end operational transconductance amplifier (OTA) output has limited voltage and current compliances. This set of component values ensures that OTA operates within its linear region for optimal THD+N performance. In case the target frequency is somewhere in between the frequencies listed in Table 6, simply adjust the frequency by tweaking R1.

Table 10 **External Component Values vs. Self-Oscillation Frequency**

| Target Self-Oscillation |            |           |

|-------------------------|------------|-----------|

| Frequency (kHz)         | C1=C2 (nF) | R1 (ohms) |

| 500                     | 2.2        | 200       |

| 450                     | 2.2        | 165       |

| 400                     | 2.2        | 141       |

| 350                     | 2.2        | 124       |

| 300                     | 2.2        | 115       |

| 250                     | 2.2        | 102       |

| 200                     | 4.7        | 41.2      |

| 150                     | 10         | 20.0      |

| 100                     | 10         | 14.0      |

| 70                      | 22         | 4.42      |

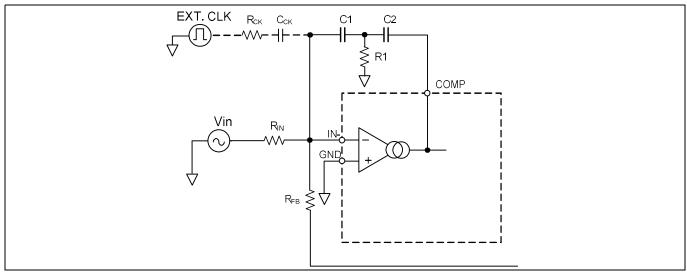

### 9.4 Clock Synchronization

In the PWM control loop design example, the self-oscillating frequency can be set and synchronized to an external clock. Through a set of resistors and a capacitor, the external clock injects periodic pulsating charges into the integrator, forcing oscillation to lock up to the external clock frequency. A typical setup with 5 Vp-p 50% duty clock signal uses  $R_{CK}$ =22 k $\Omega$  and  $C_{CK}$ =100 pF in Figure 30. To maximize audio performance, the self-running frequency without clock injection should be 20 to 30% higher than the external clock frequency.

Figure 30 External Clock Synchronization

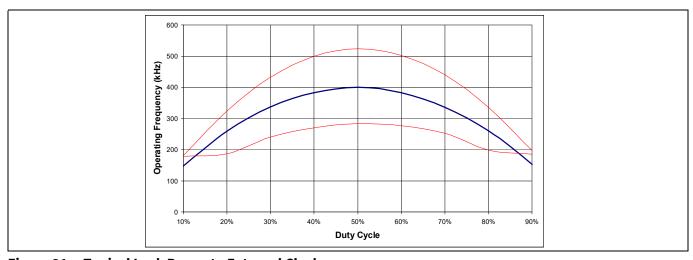

Figure 31 shows how a self-oscillating frequency locks up to an external clock frequency. A design of a 400 kHz self-oscillating frequency synchronizes to an external clock whose frequency is within the red border lines.

Figure 31 Typical Lock Range to External Clock

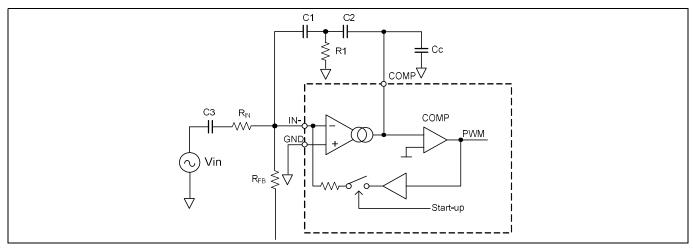

#### 9.5 Click Noise Elimination

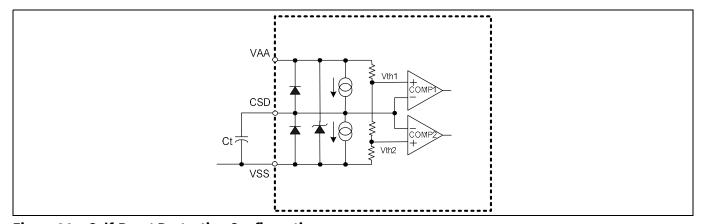

The MA5342MS has a unique feature that minimizes power-ON and -OFF audible click noise. When CSD is in between Vth1 and Vth2 during start-up, an internal closed loop around the OTA enables an oscillation that generates voltages at COMP and IN-, bringing them to steady-state values. It runs at around 1 MHz, independent from the switching oscillation.

Figure 32 Audible Click Noise Elimination

As a result, all capacitive components connected to COMP and IN- pins, such as C1, C2, C3 and Cc in Figure 32, are pre-charged to their steady-state values during the start-up sequence. This allows instant settling of closed-loop PWM operation.

To utilize the click noise reduction function, the following conditions must be met.

- 1. CSD pin has slow enough ramp up from Vth1 to Vth2 such that the voltages in the capacitors can settle to their target values.

- 2. High-side bootstrap power supply needs to be charged up prior to starting oscillation.

- 3. Audio input has to be zero.

- 4. For internal local loop to override external feedback during the startup period, DC offset at speaker output prior to shutdown release has to satisfy the following condition.

$$DCoffset < 30 \,\mu A \cdot R_{FB}$$

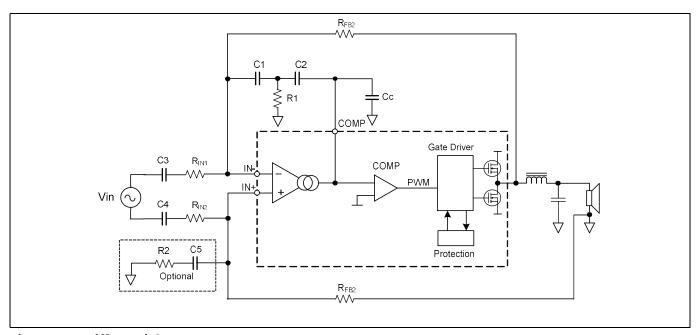

## 9.6 Differential Input

Figure 33 shows an example of a differential input configuration. This design is useful in a single supply configuration. Use  $R_{IN1}=R_{IN2}$ ,  $R_{FB1}=R_{FB2}$ , C3=C4.

Voltage gain is given by a ratio between R<sub>IN</sub> and R<sub>FB</sub>.

$$G_{V} = \frac{R_{FB}}{R_{IN}}$$

Figure 33 Differential Input

Although component values in the feedback network are balanced between inverting and non-inverting inputs, the integration capacitor path in the non-inverting input creates unbalance at high frequencies, causing slightly higher distortion compared to an unbalanced input configuration. To improve the THD degradations, place optional RC network R2=R1 and C5=C1.

## 10 Operational Mode

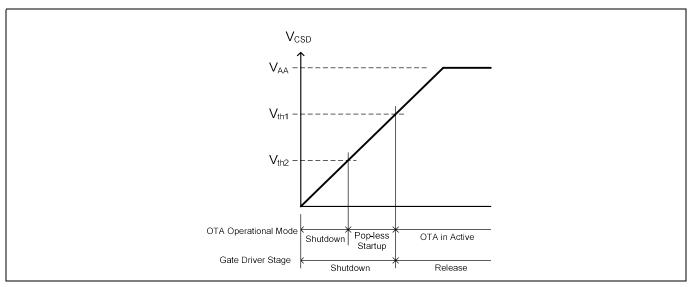

The CSD pin determines the operational mode of the MA5342MS as shown in Figure 34. The OTA has three operational modes: shutdown, pop-less startup and normal operation; while the gate driver section has two modes: shutdown and normal operation.

When  $V_{CSD} < Vth2$ , the IC is in shutdown mode and the input OTA is cut off. When Vth2<  $V_{CSD} < Vth1$ , the output MOSFETs are still in shutdown mode. The OTA is activated and starts local oscillation for pop-less start-up which pre-biases all the capacitive components in the error amplifier. When  $V_{CSD} > Vth1$ , the MA5342MS enters normal operation mode and PWM operation starts.

Figure 34 V<sub>CSD</sub> and Operational Mode

### 10.1 Self-oscillation Start-up Condition

The MA5342MS requires the following conditions in order for pop-less startup to work properly.

- All the control power supplies, VAA, VSS, VCC and VBS are above the under-voltage lockout thresholds.

- CSD pin voltage is over Vth1 threshold.

- $|i_{IN}| < |i_{FB}|$

Where

$$i_{{\scriptscriptstyle I}{\scriptscriptstyle N}}=\frac{V_{{\scriptscriptstyle I}{\scriptscriptstyle N}}}{R_{{\scriptscriptstyle I}{\scriptscriptstyle N}}}$$

,  $i_{{\scriptscriptstyle F}{\scriptscriptstyle B}}\!=\!\frac{V_{{\scriptscriptstyle +}{\scriptscriptstyle B}}}{R_{{\scriptscriptstyle F}{\scriptscriptstyle B}}}.$

- The duration CSD voltage transitioning from Vth2 to Vth1 is long enough to pre-charge input and integration capacitors around OTA section.

## 11 Protections

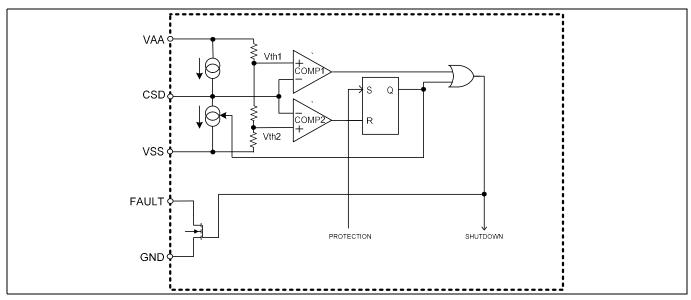

Figure 35 Protection Functional Block Diagram (MA5342MS)

The internal protection control block dictates the operational modes, normal or shutdown, using the input of the CSD pin. In shutdown mode, the controller IC turns off internal power MOSFETs.

The CSD pin provides five functions.

- 1. Power up delay timer

- 2. Self-reset timer

- 3. Shutdown input

- 4. Latched protection configuration

- 5. Shutdown status output (host I/F)

The CSD pin cannot be paralleled with another MA5342MS directly.

The operating statuses of the protection features are shown in Table 2.

Table 11 Events and Actions of CSD and FAULT

| Event              | CSD     | FAULT                          |

|--------------------|---------|--------------------------------|

| UVCC, rising edge  | Recycle | L until CSD>Vth1               |

| UVCC, falling edge | n/a     | n/a                            |

| UVAA, rising edge  | n/a     | L at VAA <uvaa< td=""></uvaa<> |

| UVAA, falling edge | n/a     | L at VAA <uvaa< td=""></uvaa<> |

| UVBS, rising edge  | n/a     | n/a                            |

| UVBS, falling edge | n/a     | n/a                            |

|                                | Keep recycling until OCP  |                           |

|--------------------------------|---------------------------|---------------------------|

| <b>Over Current Protection</b> | is reset                  | Held L until OCP is reset |

| DC Protection                  | Held L until DCP is reset | Held L until DCP is reset |

| Clip Detection                 | n/a                       | n/a                       |

|                                | Keep recycling until OTP  |                           |

| OTP1-3 Inputs                  | is reset                  | Held L until OTP is reset |

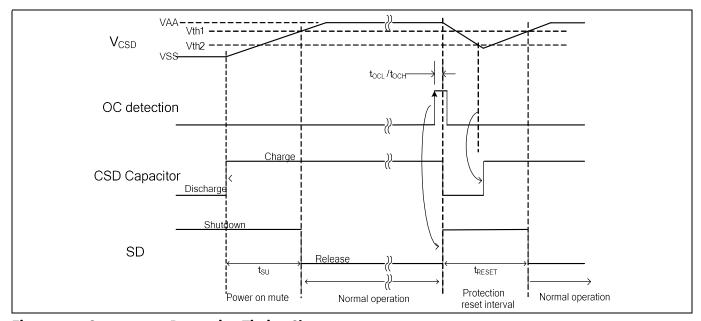

#### 11.1.1 Self-Reset Protection

Attaching a capacitor between CSD and V<sub>ss</sub> configures the MA5342MS self-reset protection mode.

Upon an OCP event, the CSD pin discharges the external capacitor voltage  $V_{CSD}$  down to the lower threshold  $V_{th2}$  to reset the internal shutdown latch. Then, the CSD pin begins to charge the external capacitor, Ct, in an attempt to resume operation. Once the voltage of the CSD pin rises above the upper threshold,  $V_{th1}$ , the IC resumes normal operation.

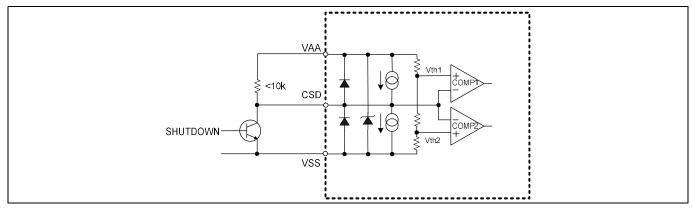

Figure 36 Self-Reset Protection Configuration

## 11.1.2 Designing Ct

The external timing capacitor, Ct, programs self-reset timings:  $t_{RESET}$  and  $t_{SU}$ .

- trest is the time that elapses from when the IC enters the shutdown mode to the time when the IC resumes operation. trest should be long enough to avoid over heating the MOSFETs from the repetitive sequence of shutting down and resuming operation during over-current conditions. In most applications, the minimum recommended time for trest is 0.1 seconds.

- t<sub>SU</sub> is the time between powering up the IC in shutdown mode to the moment the IC releases shutdown to begin normal operation.

The Ct determines t<sub>RESET</sub> and t<sub>SU</sub> as following equations:

<sup>\*</sup>CSD recycle: CSD pin voltage discharges down to Vth2 and charges back to VAA, if CSD pin is configured as self reset protection.

# Integrated Class D Amplifier

$$t_{\textit{RESET}} = \frac{Ct \cdot V_{\textit{AA}}}{1.1 \cdot I_{\textit{CSD}}} \quad [s]$$

$$t_{SU} = \frac{Ct \cdot V_{AA}}{0.7 \cdot I_{CSD}} \quad [s]$$

where I<sub>CSD</sub>: the charge/discharge current at the CSD pin

V<sub>AA</sub>: the floating input supply voltage with respect to V<sub>SS.</sub>

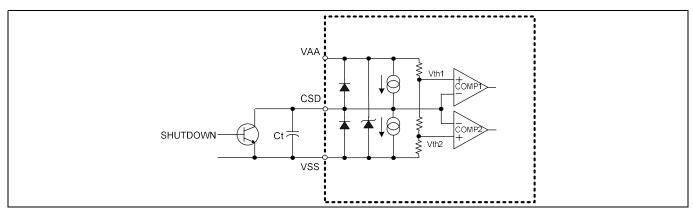

## 11.1.3 Shutdown Input

During normal operation, pulling the CSD pin below the upper threshold Vth1 forces the IC into shutdown mode. Figure 37 shows how to add an external discharging path to shutdown the PWM.

Figure 37 Shutdown Input

#### 11.1.4 Latched Protection

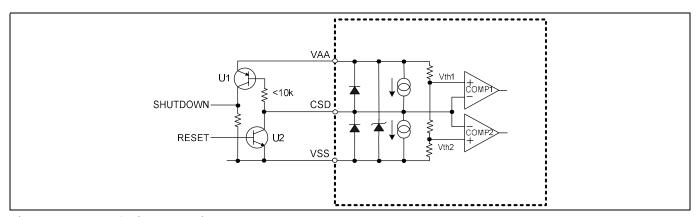

Connecting CSD to  $V_{AA}$  through a 10 k $\Omega$  or less resistor configures latched protection mode. The internal shutdown latch stays in shutdown mode after the overcurrent is detected. An external reset switch brings CSD below the lower threshold Vth2 for a minimum of 200 ns and resets the latch. At first power-up, a reset signal to the CSD pin is required to release the IC from shutdown mode.

Figure 38 Latched Protection with Reset Input

#### 11.1.5 Interfacing with System Controller

The MA5342MS can communicate with an external system controller through a simple interfacing circuit shown in Figure 39. A generic PNP transistor, U1, detects the sink current at the CSD pin during protection event and outputs a shutdown flag signal to an external system controller. Another generic NPN transistor, U2, can then reset the internal protection logic by pulling the CSD voltage below the lower threshold Vth2. After the first power-up sequence, a reset signal to the CSD pin is required to release the IC from shutdown mode.

Figure 39 Interfacing CSD with System Controller

### 11.2 Over Current Protection (OCP)

The MA5342MS features over current protection to protect the internal power MOSFETs during abnormal load conditions. The control logic diagrams are in Figure 40. As soon as either the high-side or low-side current sensing block detects over current, the following sequence will occur.

- 1. The shutdown latch flips its logic states from normal operational mode to shutdown mode.

- 2. Low-side and high-side MOSFETs go into an off state condition.

- 3. The CSD pin starts discharging the external capacitor Ct.

- 4. When voltage across Ct falls below the lower threshold Vth2, COMP2 resets the shutdown latch to normal mode.

- 5. The CSD pin starts charging the external capacitor Ct.

- 6. When  $V_{CSD}$  goes above the upper threshold Vth1, the logic on COMP1 toggles and the IC resumes operation.

Figure 40 summarizes the above. As long as the over current condition exists, the IC will repeat the over current protection sequence at a repetitive rate set by the CSD capacitor.

Figure 40 Overcurrent Protection Timing Chart

### 11.3 Over Temperature Protection (OTP)

If the junction temperature  $T_J$  of the controller IC exceeds the on-chip thermal shutdown threshold,  $T_{SD}$ , the on-chip over temperature protection shuts down the PWM.

### 11.4 Under Voltage Protection (UVP)

In order to prevent a partial on-state of the internal MOSFET, under-voltage protection monitors the low side and high side gate bias supplies, VCC and VB. When VCC is below UVLO, both high and low side MOSFETs are turned off. When the high side supply  $V_{BS}$  is below the UVLO threshold, the high side output is disabled, while the low side works normally.

# 12 Status Output

### 12.1 Fault Output

FAULT output is an open drain output referenced to GND to report whether the MA5342MS is in shutdown mode or in normal operating mode. If the FAULT pin is open, the MA5342MS is in normal operation mode, i.e. the output MOSFETs are active. The following conditions trigger shutdown internally and pulls the FAULT pin down to GND.

- Over Current Protection

- Over Temperature Protection

- Shutdown mode from CSD pin voltage

Figure 41 Fault Output

### 12.2 CLIP Output

When the output of the amplifier loses track of an expected target value, the amplifier enters into clipping condition.

The CLIP detection block monitors the COMP pin voltage with a window comparator. The CLIP pin is pulled to GND when a clipping condition is detected. The detection thresholds in the COMP pin are at 10% and 90% of VAA-VSS. The CLIP outputs are disabled in shutdown mode.

Figure 42 CLIP Detection

## 13 Power Supply Design

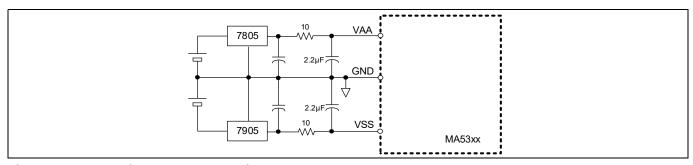

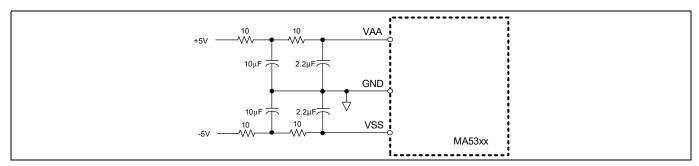

#### 13.1 Supplying VAA and VSS

VAA and VSS are supply voltages to the front-end of the analog section, hence are noise sensitive. For best audio performance, use regulated power supplies for VAA and VSS.

Figure 43 Supplying VAA and VSS with External Voltage Regulators

When switched-mode regulators are used as supply voltages for VAA and VSS, place a two-stage R-C noise filter in the supply lines as shown in Figure 44.

Figure 44 Supplying VAA and VSS from Switched Mode Power Supply

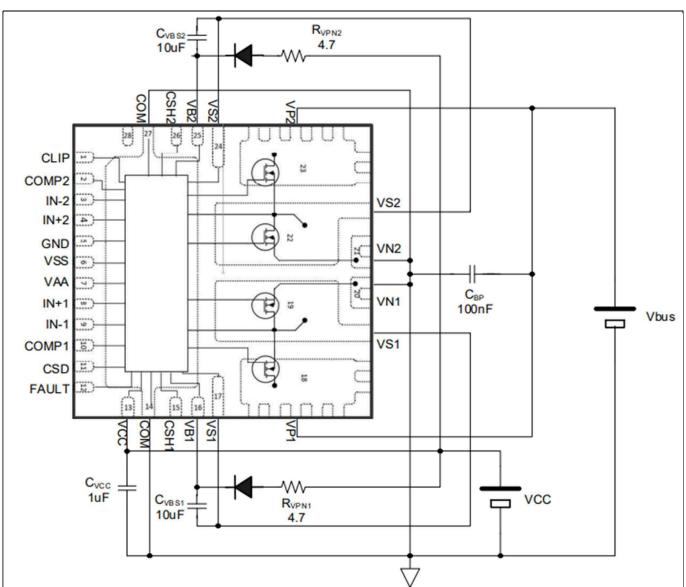

### 13.2 Supplying VCC and VB

Figure 45 shows the recommended power supply configuration for gate driver power supplies. The gate driver stage has three power supply inputs:

- 1. VCC-COM: low side gate drive supply

- 2. VB1-VS1: CH1 high side gate drive supply

- 3. VB2-VS2: CH2 high side gate drive supply

The low-side power supply, VCC, feeds the internal gate drive logic and low side gate driver. In order to protect VCC from switching noise generated by the VS node, it is recommended to insert a few ohms of  $R_{VBS}$  in the bootstrap charging path.

The high-side driver requires a floating supply VBn referenced to the respective switching node VSn where the source of the output MOSFET is connected. A charge pump method (floating bootstrap power supply) eliminates the need for a floating power supply and thus is used in the typical application circuit. The floating bootstrap power supply charges the bootstrap capacitor C<sub>BS</sub> from the low-side power supply VCC during the low-side MOSFET ON period. When the high-side MOSFET is ON, the diode cuts off and floats the VBS supply. C<sub>BS</sub> retains its VB supply voltage for the rest of the high-side ON duration.

Recommend to have minimum 20% design margin for Ivcc.

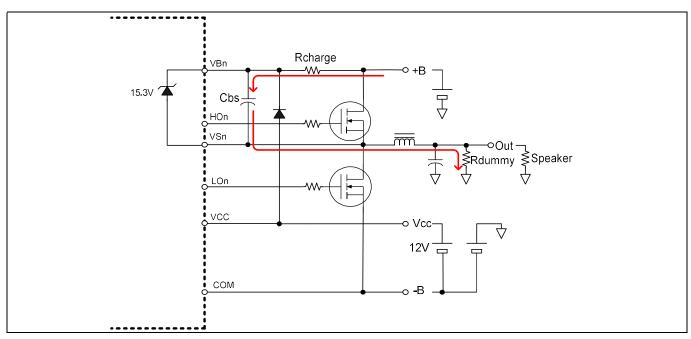

Figure 45 Recommended Power Supply Configurations for Output Stage

### 13.2.1 Choosing Vs Diode

To prevent excessive negative spiking across low side MOSFET during output short circuit event, add  $D1_{vs}$  and  $D2_{vs}$  across VS1-VN1 and VS2-VN2. Diode type Schottky 200V/1A is recommended.

## 13.2.2 Choosing Bootstrap Diode

Use a bootstrap charging diode with voltage rating of 1.5 x the maximum bus voltage. In order to charge the bootstrap capacitor in a very short low-side ON period with a high PWM modulation ratio, a fast recovery diode type with trr of <50ns and Ct of <10pF at 0V is recommended.

### 13.2.3 Charging V<sub>BS</sub> Prior to Start

For proper start-up, pre-charging the bootstrap supply  $V_{BS}$  prior to PWM start-up is necessary for self-oscillating PWM modulator topologies. A charging resistor,  $R_{CHARGE}$ , inserted between the positive supply bus and  $V_{B}$ , charges  $C_{BS}$  prior to switching start as shown in Figure 46. The minimum resistance of  $R_{CHARGE}$  is limited by the maximum PWM modulation index of the system. When the high-side MOSFET is on,  $R_{CHARGE}$  drains the bootstrap power supply together with the quiescent current,  $I_{QBS}$ , so it reduces the holding time, resulting in maximum continuous high-side on time.

The maximum resistance of R<sub>CHARGE</sub> is limited by the current charge capability of the resistor during startup.

Pre-charging current flows into the speaker load. In order to startup without the load connected, a dummy load  $R_{dummy}$  in parallel with the speaker output provides a pre-charging current path.

Figure 46 Bootstrap Supply Pre-Charging

### 13.3 Power Supply Sequence

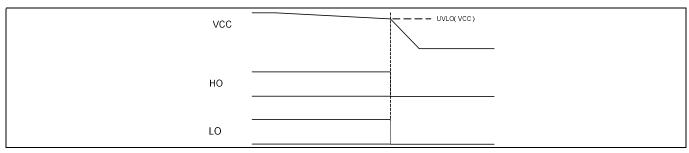

The protection control block in the MA5342MS monitors the status of  $V_{AA}$  and  $V_{CC}$  to ensure that both voltage supplies are above their respective UVLO (under voltage lockout) thresholds before starting normal operation. If either  $V_{AA}$  or  $V_{CC}$  is below the under voltage threshold, the output MOSFETs are disabled in shutdown mode until both  $V_{AA}$  and  $V_{CC}$  rise above their voltage thresholds. As soon as  $V_{AA}$  or  $V_{CC}$  falls below its UVLO threshold, protection logic in the MA5342MS turns off high-side and low-side.

Figure 47 MA5342MS UVLO Timing Chart

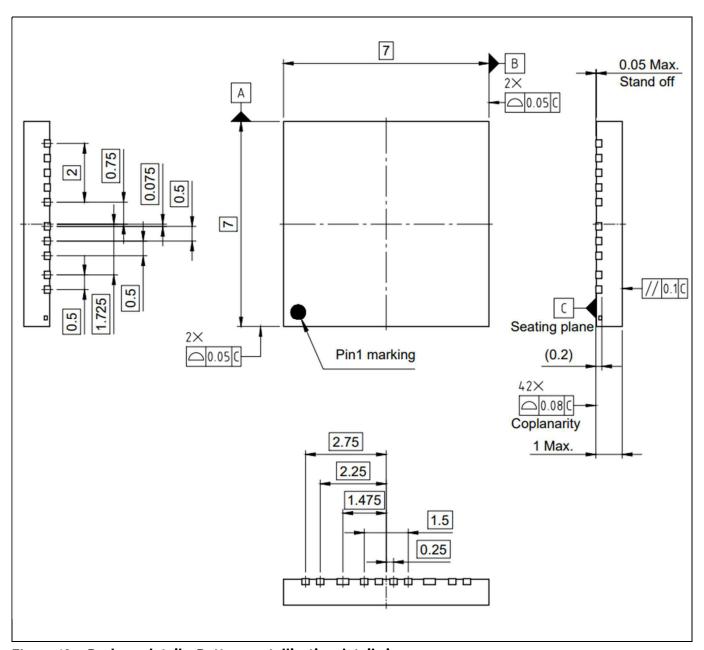

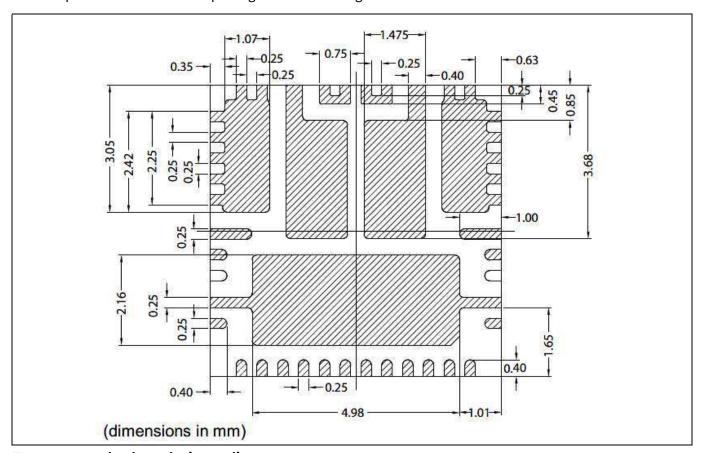

#### **Package details** 14

Figure 48 Package details; Bottom metallization detail view

All dimensions are in units mm

The drawing is in compliance with ISO 128-30, Projection Method 1 [ Drawing according to ISO 8015, general tolerances ISO 2768-mK

Figure 49 **Dimension table**

All dimensions are in units mm The drawing is in compliance with ISO 128-30, Projection Method 1 [ Drawing according to ISO 8015, general tolerances ISO 2768-mK

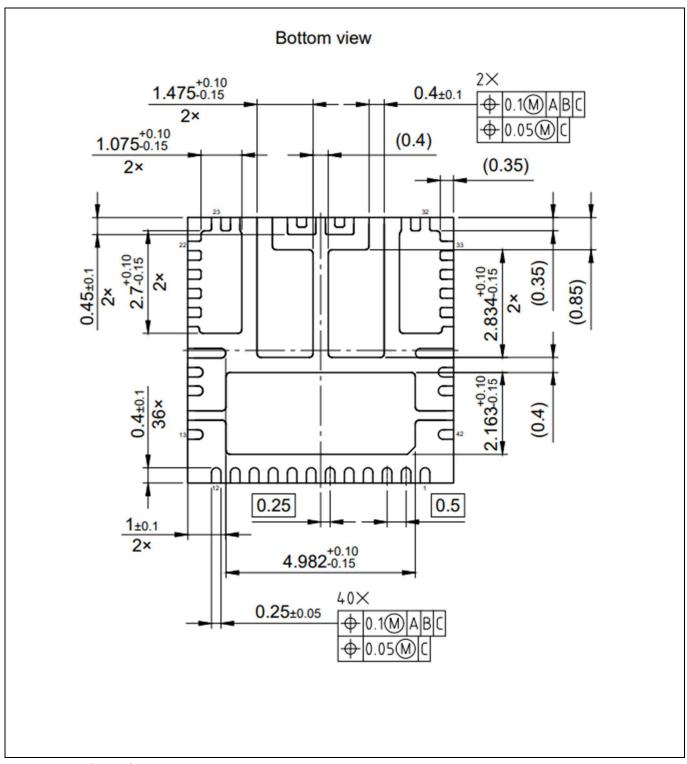

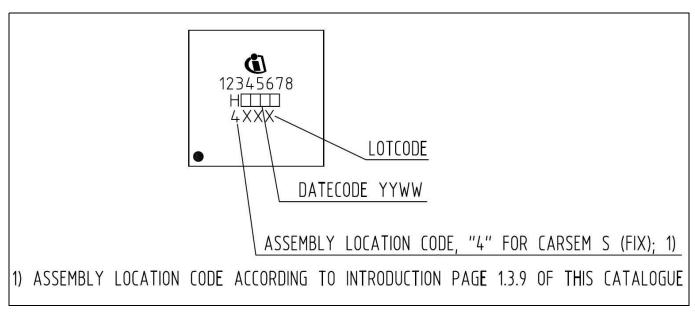

#### Board mounting, part marking, and ordering information **15**

Reliability of products in the PQFN package is subject to the board mounting process. The Soldering process is critical. Refer to Application Note AN-1170 Audio IC Board Mounting Application Note for specific footprint design and soldering methods.

#### **Device outline**

Figure 50 shows the outline for these devices. The relative pad positions are controlled to an accuracy of ±0.050mm. For full dimensions and tolerances of each device, and to find out its size and outline, refer to the relevant product data sheet and package outline drawing.

42-lead 7x7 device outline Figure 50

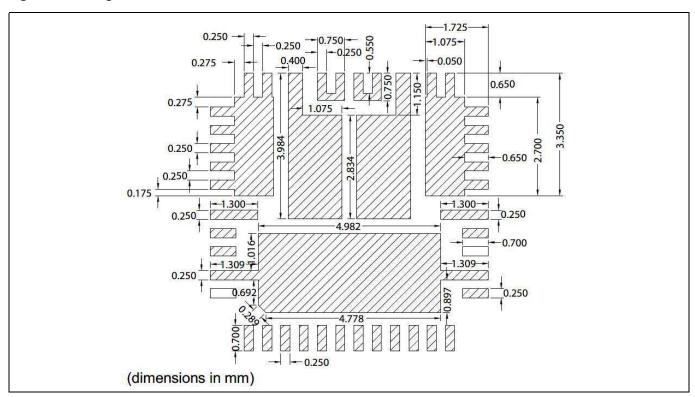

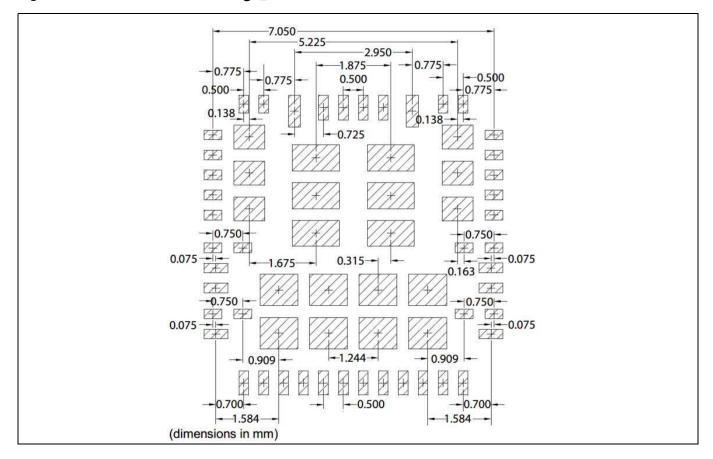

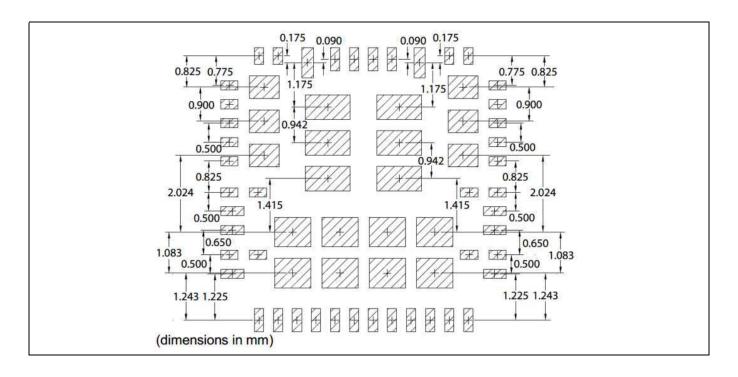

#### **Substrate/PCB layout**

Evaluations have shown that the best overall performance is achieved using the substrate/PCB layout shown in Figure 51 and Figure 52

Figure 51 42-lead 7x7 substrate /PCB layout\_1

Figure 52 42-lead 7x7 substrate /PCB layout\_2

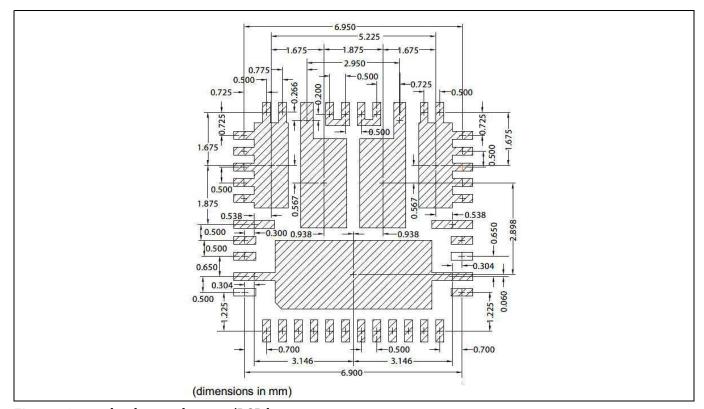

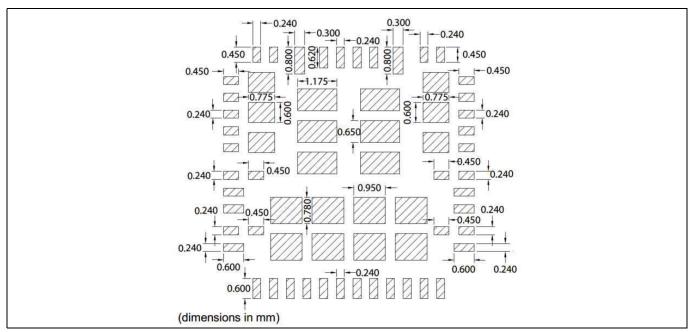

#### **Stencil Design**

Evaluations have shown that the best overall performance is achieved using the stencil design shown in Figure 53-55.

Figure 53 42-lead 7x7 stencil design\_1

Figure 54 42-lead 7x7 stencil design\_2

Figure 55 42-lead 7x7 stencil design\_3

Note:

This design is for a stencil thickness of 0.127mm (0.005"). The reduction should be adjusted for stencils of other thicknesses. All soldering conditions are necessary to ensure reliability. More details please refer to Application Note AN-1170 Audio Power Quad Flat No-Lead (PQFN) Board Mounting Application

#### **Part marking**

Figure 56 Part marking

## **Ordering information**

| Dage next number | Dackage type | Standard pack |          | Complete new number  |

|------------------|--------------|---------------|----------|----------------------|

| Base part number | Package type | Form          | Quantity | Complete part number |

| MA5342MS         | PQFN42 7x7mm | Tape and Reel | 3000     | MA5342MS             |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2022-02-07

Published by

Infineon Technologies AG 81726 Munich, Germany

© 2023 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

**Document reference**

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.