6A Single-input Voltage, Synchronous Buck Regulator with PMBus Interface DCDC Converter

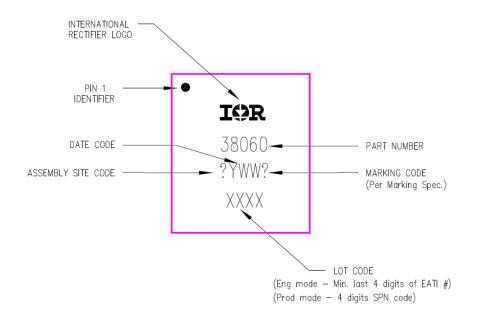

Digital Sup*IR*Buck IR38060

## FEATURES

- Internal LDO allows single 16V operation

- Output Voltage Range: 0.5V to 0.875\*PVin

- 0.5% accurate Reference Voltage

- Programmable Switching Frequency up to 1.5MHz using Rt/Sync pin or PMBus

- Internal Soft-Start with Pre-Bias Start-up

- Enable input with Voltage Monitoring Capability

- Remote Sense Amplifier with True Differential Voltage Sensing

- Fast mode I2C and 400 kHz PMBus interface

- Sequencing and tracking capable

- Selectable analog mode or digital mode

- 66 PMBus commands for configuration, control, fault protection and telemetry.

- Thermally compensated current limit with configurable overcurrent responses

- Optional light load efficiency mode

- External synchronization with Smooth Clocking

- Dedicated output voltage sensing protection which remains active even when Enable is low.

- Integrated MOSFETs and Bootstrap diode

- Operating junction temp: -40°C<Tj<125°C

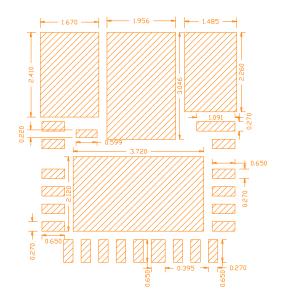

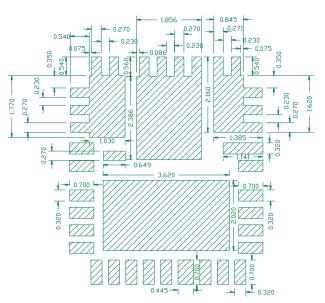

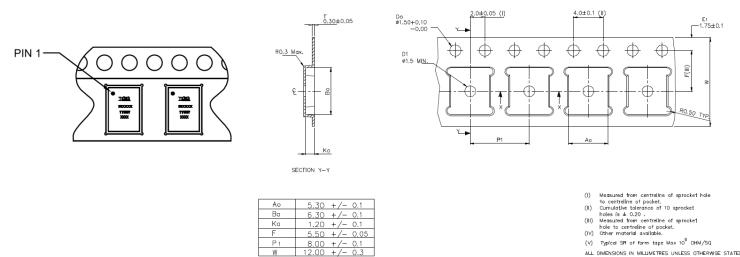

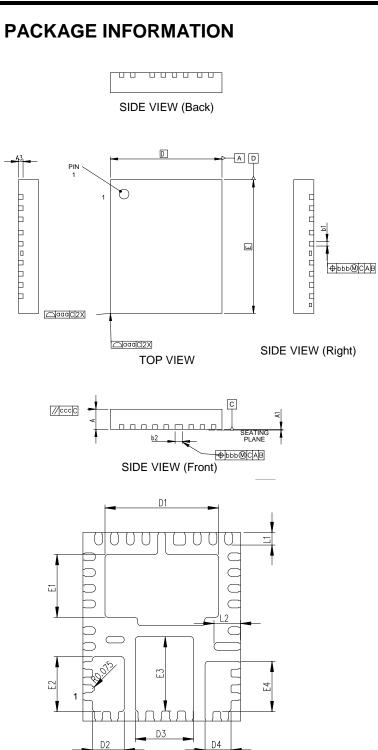

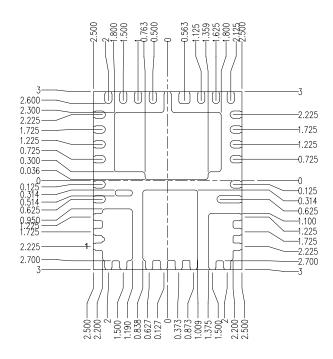

- Small Size 5mmx6mm PQFN

- Pb-Free (RoHS Compliant)

## DESCRIPTION

The IR38060 PMBus SupIRBuck<sup>™</sup> is an easy-to-use, fully integrated and highly efficient DC/DC regulator with I2C/PMBus interface. The onboard PWM controller and MOSFETs make IR38060 a space-efficient solution, providing accurate power delivery for low output voltage and high current applications.

The IR38060 can be comprehensively configured via PMBus and the configuration stored in internal memory. In addition, PMBus commands allow run-time control, fault status and telemetry.

The IR38060 can also operate as a standard analog regulator without any programming and can provide current and temperature telemetry in an analog format.

## **APPLICATIONS**

Server Applications Netcomm applications Embedded telecom Systems Distributed Point Of Load Architectures

## **ORDERING INFORMATION**

| Base    | Package  | Standa | ard Pack | Orderable Part  | Application Description                     |

|---------|----------|--------|----------|-----------------|---------------------------------------------|

| Part    | Туре     | Form   | Quantity | Number          | Application Description                     |

|         |          | Tape   |          | IR38060MTRPBF   | Standard part, 0.5Vout                      |

|         |          | &      |          | IR38060MBC01TRP | Broadcom SAS34xx, SAS35xx, SAS36xx, SAS37xx |

|         | QFN      | Reel   | 4000     | IR38060MGM09TRP | 0.9Vout, 607kHz pre-configured              |

| IR38060 | 5x6 mm   |        | 4000     | IR38060MGM10TRP | 1.0Vout, 607kHz pre-configured              |

|         | 520 1111 |        |          | IR38060MGM12TRP | 1.2Vout, 607kHz pre-configured              |

|         |          |        |          | IR38060MGM18TRP | 1.8Vout, 607kHz pre-configured              |

|         |          |        | 250      | 111-4188PBF     | Standard part, 0.5Vout for Distributors     |

89

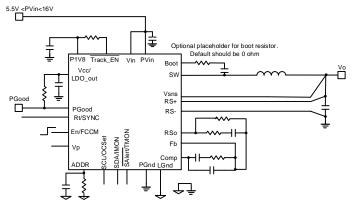

**BASIC APPLICATION**

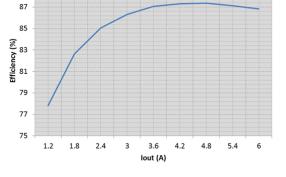

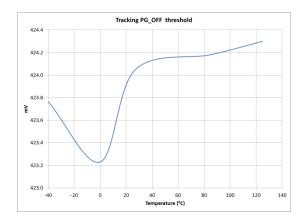

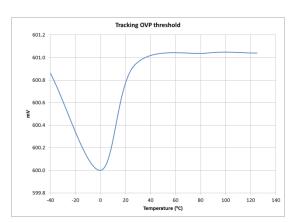

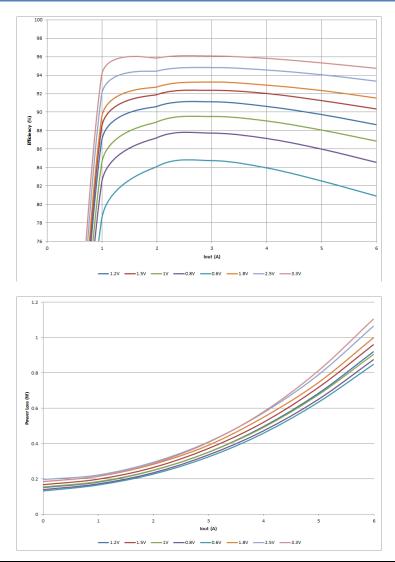

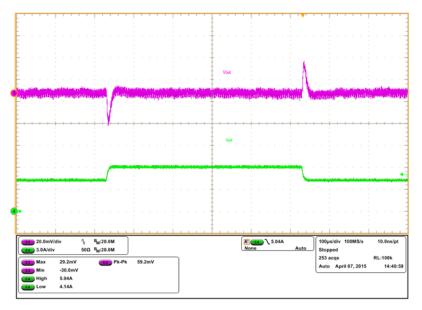

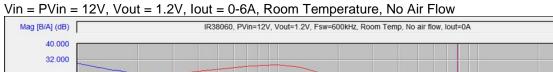

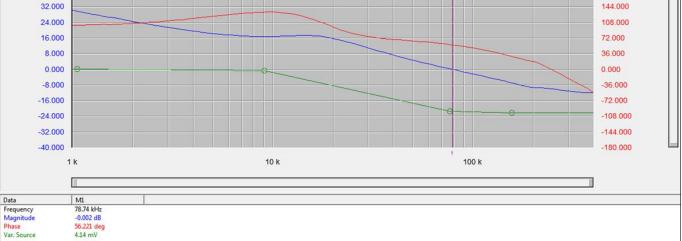

Figure 2: Performance Curve

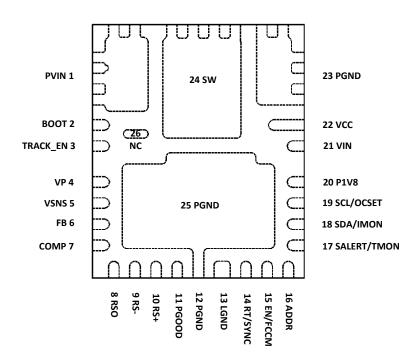

## **PINOUT DIAGRAM**

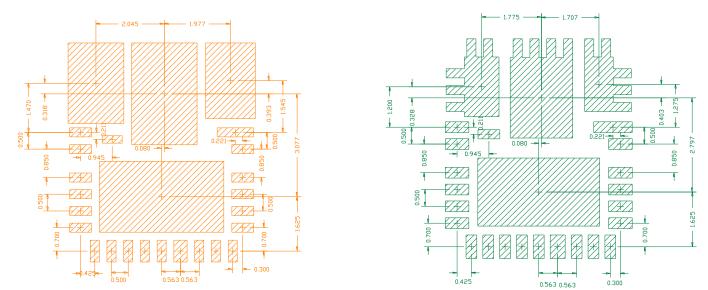

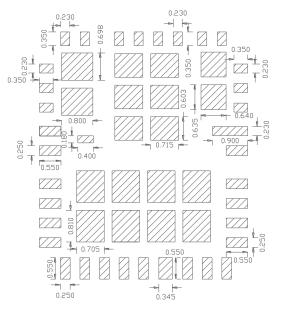

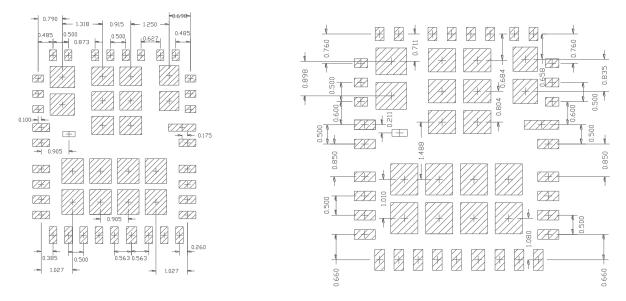

Figure 3: IR38060 package (Top View) 5mm x 6mm PQFN

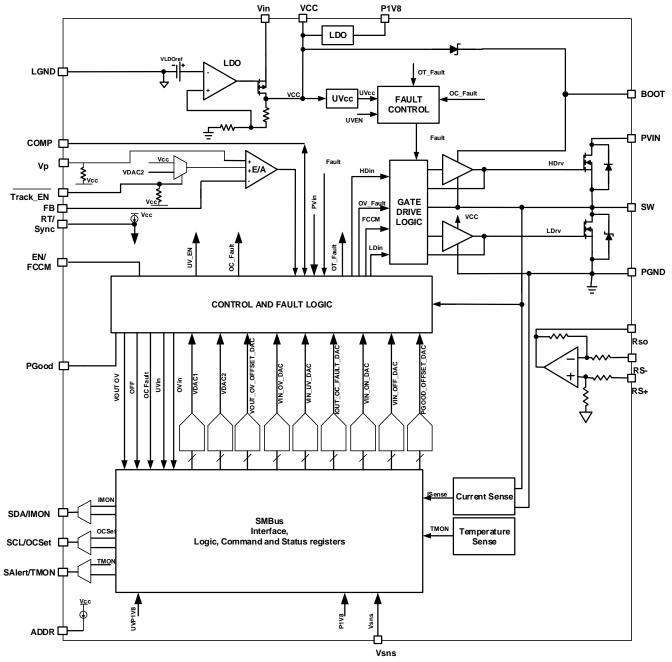

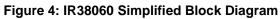

## **BLOCK DIAGRAM**

## **PIN DESCRIPTIONS**

| PIN #        | PIN NAME   | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | PVIN       | Input voltage for power stage. Bypass capacitors between PVin and PGND should<br>be connected very close to this pin and PGND. Typical applications use 4 X22 uF<br>input capacitors and a low ESR, low ESL 0.1uF decoupling capacitor in a<br>0603/0402 case size. A 3.3nF capacitor may also be used in parallel with these<br>input capacitors to reduce ringing on the Sw node.                     |

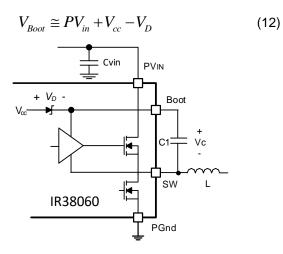

| 2            | Boot       | Supply voltage for high side driver. A 0.1uF capacitor should be connected between the Boot pin and the Sw node. It is recommended to provide a placement for a 0 ohm resistor in series with the capacitor. For applications in which PVin>12V, the value of the series resistor should be chosen to be 1 ohm.                                                                                         |

| 3            | Track_En * | Pull low to enable tracking function. For normal, non-tracking operation, connect a 100 kOhm resistor from this pin to P1V8. An alternative to using 100kohm to P1V8 is to connect a 750 kohm resistor from Track_En# to LGND when the Track_En# pin is not used for a tracking function. One of these two options must be used to disable tracking functionality. The 100kOhm is the preferred method. |

| 4            | Vp         | Used for sequencing and tracking applications. Leave open if not used.                                                                                                                                                                                                                                                                                                                                  |

| 5            | Vsns       | Sense pin for OVP and PGood                                                                                                                                                                                                                                                                                                                                                                             |

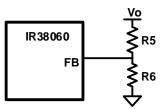

| 6            | FB         | Inverting input to the error amplifier. This pin is connected directly to the output of the regulator or to the output of the remote sense amplifier, via resistor divider to set the output voltage and provide feedback to the error amplifier.                                                                                                                                                       |

| 7            | COMP       | Output of error amplifier. An external resistor and capacitor network is typically connected from this pin to FB to provide loop compensation.                                                                                                                                                                                                                                                          |

| 8            | RSo        | Remote Sense Amplifier Output                                                                                                                                                                                                                                                                                                                                                                           |

| 9            | RS-        | Remote Sense Amplifier input. Connect to ground at the load.                                                                                                                                                                                                                                                                                                                                            |

| 10           | RS+        | Remote Sense Amplifier input. Connect to output at the load.                                                                                                                                                                                                                                                                                                                                            |

| 11           | PGood      | Po Power Good status pin. Output is open drain. Connect a pull up resistor from this pin to VCC. If the power good voltage before VCC UVLO needs to be limited to < 500 mV, use a 49.9K pullup, otherwise a 4.99K pullup will suffice.                                                                                                                                                                  |

| 12,23,<br>25 | PGND       | Power ground. This pin should be connected to the system's power ground plane.<br>Bypass capacitors between PVin and PGND should be connected very close to the<br>PVIN pin (pin 1) and this pin.                                                                                                                                                                                                       |

| 13           | LGND       | Signal ground for internal reference and control circuitry.                                                                                                                                                                                                                                                                                                                                             |

| 14           | RT/Sync    | In analog mode, use an external resistor from this pin to GND to set the switching frequency. The resistor should be placed very close to the pin. This pin can also be used for external synchronization. In digital mode this pin is typically left floating however a 15K resistor from this pin to GND may be used instead of floating the pin.                                                     |

| 15           | EN/FCCM    | Enable pin to turn on and off the IC. In analog mode, also serves as a mode pin, forcing the converter to operate in CCM when pulled to<3.1V.                                                                                                                                                                                                                                                           |

| 16           | ADDR       | A resistor should be connected from this pin to LGnd to set the PMBus address<br>offset for the device. It is recommended to provide a placement for a capacitor in<br>parallel with the offset resistor. If communication is not needed, as in analog mode,<br>this pin should be left floating.                                                                                                       |

| PIN # | PIN NAME        | PIN DESCRIPTION                                                                                                                                                                                                                                                                              |

|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17    | SALERT<br>/TMON | SMBus Alērt line; open drain SMBALERT# pin. This should be pulled up to 3.3V-<br>5V with a 1K-5K resistor; this pin provides a voltage proportional to the junction<br>temperature if digital communication is not needed, as in analog mode.                                                |

| 18    | SDA/IMON        | SMBus data serial input/output line; This should be pulled up to 3.3V-5V with a 1K-<br>5K resistor; this pin provides a voltage proportional to the output current if digital<br>communication is not needed, as in analog mode.                                                             |

| 19    | SCL/OCSet       | SMBus clock line; This should be pulled up to $3.3V-5V$ with a 1K-5K resistor. This pin is used to set OC thresholds if digital communication is not needed, as in analog mode. In analog mode recommend $4.7K\Omega$ for the pull-up to VCC or pull down to GND when setting the OCP value. |

| 20    | P1V8            | This is the supply for the digital circuits; bypass with a minimum 2.2uF capacitor to PGnd. A 10uF capacitor is recommended.                                                                                                                                                                 |

| 21    | Vin             | Input Voltage for LDO.                                                                                                                                                                                                                                                                       |

| 22    | VCC             | Bias Voltage for IC and driver section, output of LDO. Add 10 uF bypass cap from this pin to PGnd.                                                                                                                                                                                           |

| 24    | SW              | Switch node. This pin is connected to the output inductor.                                                                                                                                                                                                                                   |

| 26    | NC              | NC                                                                                                                                                                                                                                                                                           |

\*Design has simulated the Track\_En# input threshold test for a 750K over:

- the temperature range of -40 to 150degC,

- Vcc of 4.5V to 5.5V

- Over all corners of silicon

## **ABSOLUTE MAXIMUM RATINGS**

Stresses beyond these listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications are not implied.

| PVin, Vin                                             | -0.3V to 25V                                |

|-------------------------------------------------------|---------------------------------------------|

| VCC                                                   | -0.3V to 6V                                 |

| P1V8                                                  | -0.3V to 2 V                                |

| SW                                                    | -0.3V to 25V (DC), -4V to 25V (AC, 100ns)   |

| BOOT                                                  | -0.3V to 31V                                |

| PGD, other Input/output pins                          | -0.3V to 6V (Note 1)                        |

| BOOT to SW                                            | -0.3V to 6V (DC), -0.3V to 6.5V (AC, 100ns) |

| PGND to GND, RS- to GND                               | -0.3V to + 0.3V                             |

| THERMAL INFORMATION                                   |                                             |

| Junction to Ambient Thermal Resistance $\Theta_{JA}$  | 30°C/W                                      |

| Junction to PCB Thermal Resistance O <sub>J-PCB</sub> | 2°C/W                                       |

| Storage Temperature Range                             | -55°C to 150°C                              |

| Junction Temperature Range                            | -40°C to 150°C                              |

(Voltages referenced to GND unless otherwise specified)

Note 1: Must not exceed 6V.

## **ELECTRICAL SPECIFICATIONS**

## **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL     | DEFINITION                     | MIN | MAX                    | UNITS |

|------------|--------------------------------|-----|------------------------|-------|

| PVin       | Input Bus Voltage              | 1.2 | 16*                    | V     |

| Vin        | LDO supply voltage             | 5.5 | 16                     |       |

| VCC        | LDO output/Bias supply voltage | 4.5 | 5.5                    |       |

| Boot to SW | High Side driver gate voltage  | 4.5 | 5.5                    |       |

| Vo         | Output Voltage                 | 0.5 | 0.875*PV <sub>in</sub> |       |

| lo         | Output Current                 | 0   | 6                      | А     |

| Fs         | Switching Frequency            | 225 | 1650                   | kHz   |

| TJ         | Junction Temperature           | -40 | 125                    | °C    |

\* SW Node must not exceed 25V

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, these specification apply over,  $1.5V < PVin < 16V, 4.5V < Vcc < 5.5, 0^{\circ}C < T_{\rm J} < 125^{\circ}C.$

Typical values are specified at  $T_A = 25^{\circ}C$ .

| PARAMETER                                                                                                                                                             | SYMBOL            | CONDITIONS                                               | MIN   | ТҮР | МАХ   | UNIT |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------|-------|-----|-------|------|--|--|

| MOSFET Rds(on)                                                                                                                                                        |                   |                                                          |       |     |       |      |  |  |

| Top Switch                                                                                                                                                            | Rds(on)_Top       | $V_{Boot} - V_{SW} = 5V, I_D = 6A, Tj$<br>= 25°C         | 14    | 21  | 27    | mΩ   |  |  |

| Bottom Switch                                                                                                                                                         | Rds(on)_Bot       | Vcc =5V, I <sub>D</sub> = 6A, Tj = 25°C                  | 6     | 9   | 12    |      |  |  |

| Reference Voltage                                                                                                                                                     | Reference Voltage |                                                          |       |     |       |      |  |  |

|                                                                                                                                                                       |                   | 1.25V <v<sub>FB&lt;2.555V<br/>VOUT_SCALE_LOOP=1;</v<sub> | -1    |     | +1    | %    |  |  |

| Accuracy<br>0ºC <tj<85ºc< td=""><td></td><td>0.75V<v<sub>FB&lt;1.25V<br/>VOUT_SCALE_LOOP=1;</v<sub></td><td>-0.75</td><td></td><td>+0.75</td><td></td></tj<85ºc<>     |                   | 0.75V <v<sub>FB&lt;1.25V<br/>VOUT_SCALE_LOOP=1;</v<sub>  | -0.75 |     | +0.75 |      |  |  |

|                                                                                                                                                                       |                   | 0.45V <v<sub>FB&lt;0.75V<br/>VOUT_SCALE_LOOP=1;</v<sub>  | -0.5  |     | +0.5  | %    |  |  |

| Accuracy<br>-40ºC <tj<125ºc< td=""><td></td><td>1.25V<v<sub>FB&lt;2.555V<br/>VOUT_SCALE_LOOP=1;</v<sub></td><td>-1.6</td><td></td><td>+1.6</td><td>%</td></tj<125ºc<> |                   | 1.25V <v<sub>FB&lt;2.555V<br/>VOUT_SCALE_LOOP=1;</v<sub> | -1.6  |     | +1.6  | %    |  |  |

| PARAMETER                                                  | SYMBOL            | CONDITIONS                                                       | MIN  | ТҮР    | МАХ  | UNIT |

|------------------------------------------------------------|-------------------|------------------------------------------------------------------|------|--------|------|------|

|                                                            |                   | 0.75V <v<sub>FB&lt;1.25V<br/>VOUT_SCALE_LOOP=1;</v<sub>          | -1.0 |        | +1.0 | %    |

|                                                            |                   | 0.45V <v<sub>FB&lt;0.75V<br/>VOUT_SCALE_LOOP=1;</v<sub>          | -2.0 |        | +2.0 | %    |

| Supply                                                     |                   |                                                                  |      |        |      |      |

| PVin range (using<br>external Vcc=5.1V)                    |                   |                                                                  |      | 1.2-16 |      | V    |

| Vin range (using                                           |                   | Fsw=600kHz                                                       |      | 5.3-16 |      | v    |

| internal LDO)                                              |                   | Fsw=1.5MHz                                                       |      | 5.5-16 |      | v    |

| Vin range (when<br>Vin=Vcc)                                |                   |                                                                  | 4.5  | 5.1    | 5.5  | V    |

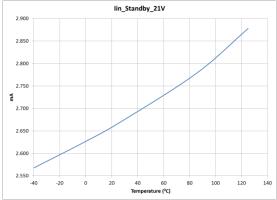

| V <sub>in</sub> Supply Current<br>(Standby) (internal Vcc) | lin(Standby)      | Enable low, No Switching,<br>Vin=16V, low power mode<br>enabled  |      | 2.7    | 4    | mA   |

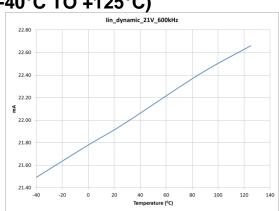

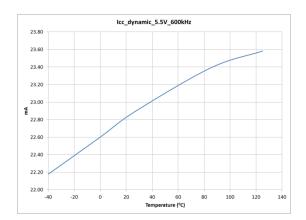

| V <sub>in</sub> Supply Current<br>(Dyn)(internal Vcc)      | lin(Dyn)          | Enable high, Fs = 600kHz,<br>Vin=16V                             |      | 22     | 30   | mA   |

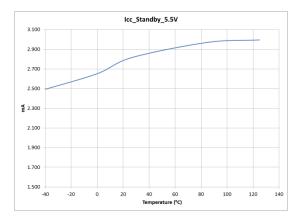

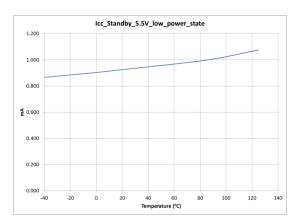

| VCC Supply Current<br>(Standby)(external Vcc)              | Icc(Standby)      | Enable low, No Switching,<br>Vcc=5.5V, low power mode<br>enabled |      | 2.7    | 5    | mA   |

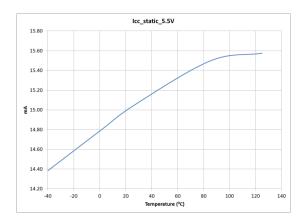

| VCC Supply Current<br>(Dyn)(external Vcc)                  | Icc(Dyn)          | Enable high, Fs = 600kHz,<br>Vcc=5.5V                            |      | 22     | 40   | mA   |

| Under Voltage Lockout                                      |                   |                                                                  |      |        |      |      |

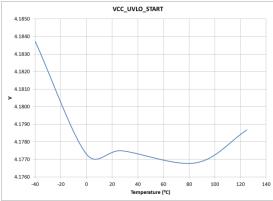

| VCC – Start –<br>Threshold                                 | VCC_UVLO_Start    | VCC Rising Trip Level                                            | 4.0  | 4.2    | 4.4  | V    |

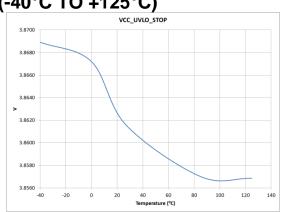

| VCC – Stop –<br>Threshold                                  | VCC_UVLO_Stop     | VCC Falling Trip Level                                           | 3.7  | 3.9    | 4.1  | V    |

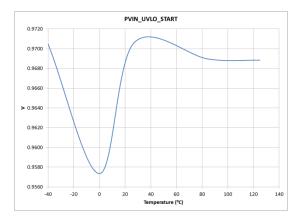

| PVin-Start-Threshold                                       | PVin_UVLO_Start   | PVin Rising Trip Level                                           | 0.85 | 0.95   | 1.05 | V    |

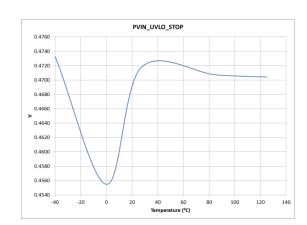

| PVin-Stop-Threshold                                        | PVin_UVLO_Stop    | PVin Falling Trip Level                                          | 0.35 | 0.45   | 0.55 |      |

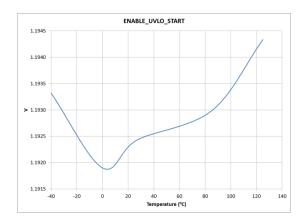

| Enable – Start –<br>Threshold                              | Enable_UVLO_Start | Supply ramping up                                                | 1.14 | 1.2    | 1.36 |      |

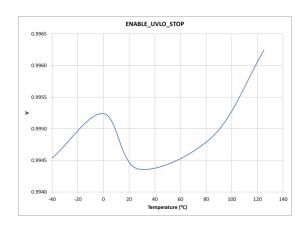

| Enable – Stop –<br>Threshold                               | Enable_UVLO_Stop  | Supply ramping down                                              | 0.9  | 1.0    | 1.06 | V    |

| Enable leakage current                                     | len               | Enable=5.5V                                                      |      |        | 1    | uA   |

| Oscillator                                                 |                   |                                                                  |      |        |      |      |

| Rt current (analog mode only)                              |                   | Rt pin voltage < 1.1V                                            | 98   | 100    | 102  | uA   |

| Frequency Range                                            | Fs                | Rt=1.54K                                                         | 360  | 400    | 440  |      |

|                                                            |                   | Rt=3.83K                                                         | 540  | 600    | 660  | kHz  |

|                                                            |                   | Rt=11.8K                                                         | 1350 | 1500   | 1650 |      |

| Min Pulse Width                                            | Dmin (ctrl)       | Note 2                                                           |      | 35     | 50   | ns   |

| Fixed Off Time                                             |                   | Note 2 Fs=1.5MHz                                                 |      | 100    | 150  | ns   |

| PARAMETER                  | SYMBOL       | CONDITIONS                                                                                                                       | MIN  | ТҮР  | МАХ   | UNIT |

|----------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------|

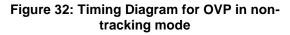

| Max Duty Cycle             | Dmax         | Fs=400kHz                                                                                                                        | 86.5 | 87.5 | 88.5  | %    |

| Sync Frequency Range       |              | Note 2                                                                                                                           | 225  |      | 1650  | kHz  |

| Sync Pulse Duration        |              |                                                                                                                                  | 100  | 200  |       | ns   |

| Sync Level Threshold       | High         |                                                                                                                                  | 2.1  |      |       |      |

|                            | Low          |                                                                                                                                  |      |      | 1     | V    |

| Error Amplifier            |              |                                                                                                                                  |      |      |       |      |

| Input Offset Voltage       | Vos_Vp       | VFb - Vp, Vp = 0.5V                                                                                                              | -1.5 |      | +1.5  | %    |

| Input Bias Current         | IFb(E/A)     |                                                                                                                                  | -0.5 |      | +0.5  | μA   |

| Input Bias Current         | IVp(E/A)     |                                                                                                                                  | 0    |      | 7     | μA   |

| Sink Current               | lsink(E/A)   |                                                                                                                                  | 0.6  | 1.1  | 1.8   | mA   |

| Source Current             | Isource(E/A) |                                                                                                                                  | 8    | 13   | 25    | mA   |

| Slew Rate                  | SR           | Note 2                                                                                                                           | 7    | 12   | 20    | V/µs |

| Maximum Voltage            | Vmax(E/A)    |                                                                                                                                  | 2.8  | 3.9  | 4.3   | V    |

| Minimum Voltage            | Vmin(E/A)    |                                                                                                                                  |      |      | 100   | mV   |

| Common Mode Voltage        | Vcm_Vp       | Note 2                                                                                                                           | 0    |      | 2.555 | V    |

| Remote Sense Differential  | Amplifier    |                                                                                                                                  |      |      |       |      |

| <b>0</b> ″                 | or           | 0.5V <rs+<2.555v, 4kω="" load<br="">27ºC<tj<85ºc< td=""><td>-1.6</td><td>0</td><td>1.6</td><td>m)/</td></tj<85ºc<></rs+<2.555v,> | -1.6 | 0    | 1.6   | m)/  |

| Offset Voltage             | Offset_RS    | 0.5V <rs+<2.555v, 4kω="" load<br="">-40ºC<tj<125ºc< td=""><td>-3</td><td></td><td>3</td><td>mV</td></tj<125ºc<></rs+<2.555v,>    | -3   |      | 3     | mV   |

| Source Current             | Isource_RS   | V_RSO=1.5V, V_RSP=4V                                                                                                             | 11   |      | 16    | mA   |

| Sink Current               | lsink_RS     |                                                                                                                                  | 0.4  | 1    | 2     | mA   |

| Slew Rate                  | Slew_RS      | Note 2, C <sub>load</sub> = 100pF                                                                                                | 2    | 4    | 8     | V/µs |

| RS+ input impedance        | Rin_RS+      |                                                                                                                                  | 36   | 55   | 74    | Kohm |

| RS- input impedance        | Rin_RS-      | Note 2                                                                                                                           | 36   | 55   | 74    | Kohm |

| Maximum Voltage            | Vmax_RS      | V(VCC) – V(RS+)                                                                                                                  | 0.5  | 1    | 1.5   | V    |

| Minimum Voltage            | Min_RS       |                                                                                                                                  |      | 4    | 20    | mV   |

| Bootstrap Diode            |              |                                                                                                                                  |      |      |       |      |

| Forward Voltage            |              | I(Boot) = 40mA                                                                                                                   | 150  | 300  | 450   | mV   |

| Switch Node                | •            |                                                                                                                                  |      |      | · .   |      |

| SW Leakage Current         | lsw          | SW = 0V, Enable = 0V                                                                                                             |      |      | 1     |      |

|                            | lsw_En       | SW=0; Enable= 2V                                                                                                                 |      | 18   |       | μA   |

| Internal Regulator (VCC/LI | DO)          |                                                                                                                                  |      | •    | · ·   |      |

| Output Voltage             | VCC          | Vin(min) = 5.5V, Io=0mA,<br>Cload = 10uF                                                                                         | 4.8  | 5.15 | 5.4   |      |

|                            |              | Vin(min) = 5.5V, Io=70mA,<br>Cload = 10uF                                                                                        | 4.5  | 4.99 | 5.2   | V    |

9

| PARAMETER                                 | SYMBOL                 | CONDITIONS                                                              | MIN   | ТҮР  | МАХ   | UNIT   |

|-------------------------------------------|------------------------|-------------------------------------------------------------------------|-------|------|-------|--------|

| VCC dropout                               | VCC_drop               | Io=0-70mA, Cload = 10uF,<br>Vin=5.1V                                    |       |      | 0.7   | V      |

| Short Circuit Current                     | Ishort                 |                                                                         |       | 110  |       | mA     |

| Internal Regulator (P1V8)                 |                        |                                                                         |       |      |       |        |

| Output Voltage                            | P1V8                   | Vin(min) = 4.5V, lo = 0-<br>10mA, Cload = 2.2uF                         | 1.795 | 1.83 | 1.905 | V      |

| 1.8V Short Circuit Current                | lshort_P1V8            |                                                                         | 12    | 20   | 35    | mA     |

| 1.8V UVLO Start                           | P1V8_UVLO_Start        | 1.8V Rising Trip Level                                                  | 1.66  | 1.72 | 1.78  | V      |

| 1.8V UVLO Stop                            | P1V8_UVLO_Stop         | 1.8V Falling Trip Level                                                 | 1.59  | 1.63 | 1.68  | V      |

| Adaptive On time Mode                     |                        |                                                                         |       |      |       |        |

| AOT Threshold                             | High                   | En/Fccm                                                                 | 3.8   | 3.9  | 4.1   |        |

|                                           | Low                    | -                                                                       | 3.1   | 3.6  | 3.8   | V      |

| Zero-crossing comparator threshold        | ZC_Vth                 |                                                                         | -4    | -1   | 2     | mV     |

| Zero-crossing comparator delay            | ZC_Tdly                |                                                                         |       | 8/Fs |       | S      |

|                                           |                        | FAULTS                                                                  |       |      |       |        |

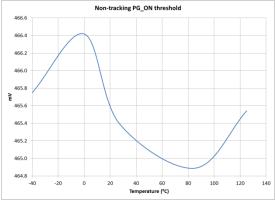

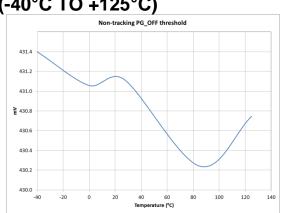

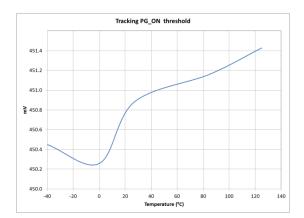

| Power Good                                |                        |                                                                         |       |      |       |        |

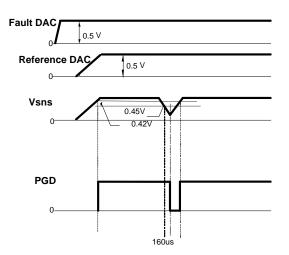

| Power Good High threshold                 | Power_Good_High        | Vsns rising,<br>VOUT_SCALE_LOOP=1,<br>Track_EN floating,<br>VDAC1=0.5V  |       | 91   |       | %VDAC1 |

|                                           |                        | Vsns rising,<br>VOUT_SCALE_LOOP=1,<br>Track_EN low, Vp=0.5V             |       | 90   |       | %Vp    |

| Power Good Low<br>Threshold               | Power_Good_Low         | Vsns falling,<br>VOUT_SCALE_LOOP=1,<br>Track_EN floating,<br>VDAC1=0.5V |       | 86   |       | %VDAC1 |

|                                           |                        | Vsns falling,<br>VOUT_SCALE_LOOP=1,<br>Track_EN low, Vp=0.5V            |       | 84.5 |       | %Vp    |

| Power Good High<br>Threshold Rising Delay | TPDLY                  | Vsns rising, Vsns ><br>Power_Good_High                                  |       | 0    |       | Ms     |

| Power Good Low<br>Threshold Falling delay | VPG_low_Dly            | Vsns falling, Vsns <<br>Power_Good_Low                                  | 150   | 175  | 200   | Us     |

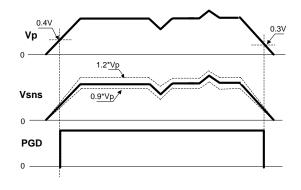

| Tracker Comparator<br>Upper Threshold     | VPG(tracker_<br>upper) | Vp Rising,<br>VOUT_SCALE_LOOP=1,<br>Track_EN low, Vsns=Vp               | 0.38  | 0.4  | 0.42  | V      |

| Tracker Comparator<br>Lower Threshold     | VPG(tracker_<br>lower) | Vp Falling,<br>VOUT_SCALE_LOOP=1,<br>Track_EN low, Vsns=Vp              | 0.28  | 0.3  | 0.32  | V      |

| PGood Voltage Low                         | PG (voltage)           | IPGood = -5mA                                                           |       |      | 0.5   | V      |

| PARAMETER                                | SYMBOL                  | CONDITIONS                                                                                              | MIN | ТҮР      | МАХ | UNIT           |

|------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------|-----|----------|-----|----------------|

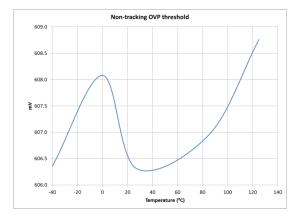

| Over Voltage Protection (                | OVP)                    |                                                                                                         |     | <b>I</b> |     |                |

| OVP Trip Threshold                       | OVP (trip)              | Vsns rising,<br>VOUT_SCALE_LOOP=1,<br>Track_EN floating,<br>VDAC1=0.5V                                  | 115 | 121      | 125 | %VDAC1         |

|                                          |                         | Vsns rising,<br>VOUT_SCALE_LOOP=1,<br>Track_EN low, Vp=0.5V                                             | 115 | 120      | 125 | %Vp            |

| OVP comparator<br>Hysteresis             | OVP (hyst)              | Vsns falling,<br>VOUT_SCALE_LOOP=1,<br>Track_EN floating,<br>VDAC1=0.5V                                 | 2.5 | 4.5      | 5.8 | %OVP<br>(trip) |

|                                          |                         | Vsns falling,<br>VOUT_SCALE_LOOP=1,<br>Track_EN low, Vp=0.5V                                            | 2.5 | 4.5      | 5.8 | %OVP<br>(trip) |

| OVP Fault Prop Delay                     | OVP (delay)             | Vsns rising, Vsns-<br>OVP(trip)>200 mV                                                                  |     | 200      |     | Ns             |

| <b>Over-Current Protection</b>           |                         |                                                                                                         |     |          |     |                |

| OC Trip Current                          | Itrip                   | Analog mode: OCSet pulled<br>high to VCC via resistor.<br>VCC = 5.05V, Tj=25°C                          | 8.1 | 9        | 9.9 | A              |

|                                          |                         | Analog mode: OCSet left<br>floating.<br>VCC = 5.05V, Tj=25°C                                            | 5.4 | 6        | 6.7 | A              |

|                                          |                         | Analog mode: OCSet pulled<br>low to GND via resistor.<br>VCC = $5.05V$ , T <sub>j</sub> = $25^{\circ}C$ | 2.4 | 3        | 3.6 | A              |

| OCset Current<br>Temperature coefficient | OCSET(temp)             | -40°C to 125°C, VCC=5.2V,<br>Note 2                                                                     |     | 4500     |     | ppm/°C         |

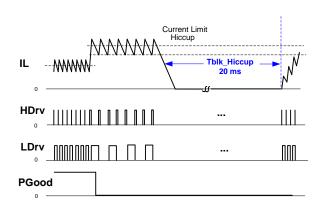

| Hiccup blanking time                     | Tblk_Hiccup             | Note 2                                                                                                  |     | 20       |     | Ms             |

| Thermal Shutdown                         |                         |                                                                                                         |     |          |     |                |

| Thermal Shutdown                         |                         | Note 2                                                                                                  |     | 145      |     | °C             |

| Hysteresis                               |                         | Note 2                                                                                                  |     | 25       |     | °C             |

| Input Over-Voltage Protection            |                         |                                                                                                         |     |          |     |                |

| PVin overvoltage<br>threshold            | PVinov                  |                                                                                                         | 22  | 23.7     | 25  | V              |

| PVin overvoltage<br>Hysteresis           | PVin <sub>ov hyst</sub> |                                                                                                         |     | 2.4      |     | V              |

|                                          | M                       | ONITORING AND REPORTING                                                                                 |     |          |     |                |

| Bus Speed                                |                         |                                                                                                         |     | 100      | 400 | kHz            |

| lout & Vout filter                       |                         |                                                                                                         |     | 78       |     | Hz             |

| lout & Vout Update rate                  |                         |                                                                                                         |     | 31.25    |     | kHz            |

| PARAMETER                              | SYMBOL            | CONDITIONS                                                                                            | MIN | ТҮР    | МАХ | UNIT |

|----------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|-----|--------|-----|------|

| Vin & Temperature filter               |                   |                                                                                                       |     | 78     |     | Hz   |

| Vin & Temperature update rate          |                   |                                                                                                       |     | 31.25  |     | kHz  |

| Output Voltage Reporting               |                   |                                                                                                       |     |        |     |      |

| Resolution                             | N <sub>Vout</sub> | Note 2                                                                                                |     | 1/256  |     | V    |

| Lowest reported Vout                   | Vomon_low         | Vsns=0V                                                                                               |     | 0      |     | V    |

| Highest reported Vout                  | Vomon_high        | VOUT_SCALE_LOOP=1,<br>Vsns=3.3V                                                                       |     | 3.3    |     | V    |

|                                        |                   | VOUT_SCALE_LOOP=0.5,<br>Vsns=3.3V                                                                     |     | 6.6    |     | V    |

|                                        |                   | VOUT_SCALE_LOOP=0.25,<br>Vsns=3.3V                                                                    |     | 13.2   |     | V    |

|                                        |                   | VOUT_SCALE_LOOP=0.125<br>, Vsns=3.3V                                                                  |     | 26.4   |     | V    |

| Vout reporting accuracy                |                   | 0ºC to 85ºC, 4.5V <vcc<5.5v,<br>1V<vsns≤ 1.5v<br="">VOUT_SCALE_LOOP=1</vsns≤></vcc<5.5v,<br>          |     | +/-0.6 |     |      |

|                                        |                   | 0°C to 85°C, 4.5V <vcc<5.5v,<br>Vsns&gt; 1.5V<br/>VOUT_SCALE_LOOP=1</vcc<5.5v,<br>                    |     | +/-1   |     | %    |

|                                        |                   | 0°C to 125°C,<br>4.5V <vcc<5.5v, vsns="">0.9V<br/>VOUT_SCALE_LOOP=1</vcc<5.5v,>                       |     | +/-1.5 |     | 70   |

|                                        |                   | 0ºC to 125ºC,<br>4.5V <vcc<5.5v,<br>0.5V<vsns<0.9v<br>VOUT_SCALE_LOOP=1</vsns<0.9v<br></vcc<5.5v,<br> |     | +/-3   |     |      |

| lout Reporting                         |                   |                                                                                                       |     |        |     |      |

| Resolution                             | Nlout             | Note 2                                                                                                |     | 62.5   |     | mA   |

| lout (digital) monitoring<br>Range     | lout_dig          |                                                                                                       | 0   |        | 10  | А    |

| lout_dig Accuracy                      |                   | 0°C to 125°C,<br>4.5V <vcc<5.5v<b>, lout=6A</vcc<5.5v<b>                                              |     | +/-5   |     | %    |

| lmon (analog) voltage                  | lmon              |                                                                                                       | 0.3 |        | 1.1 | V    |

| Imon ( analog) accuracy                |                   | 0°C to 125°C,<br>4.5V <vcc<5.5v, -<br="" lout="6A,">30uA&lt; I_IMON&lt;30uA</vcc<5.5v,>               |     | +/-1   |     | A    |

| Temperature Reporting                  |                   |                                                                                                       |     |        |     |      |

| Resolution                             | N <sub>Tmon</sub> | Note 2                                                                                                |     | 1      |     | °C   |

| Temperature Monitoring (digital) Range | Tmon_dig          |                                                                                                       | -40 |        | 150 | °C   |

| PARAMETER                                                                                                | SYMBOL              | CONDITIONS                                                                                                         | MIN   | ТҮР  | МАХ   | UNIT  |

|----------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Temperature Monitoring<br>(digital) accuracy                                                             |                     | -40°C to 125°C,<br>4.5V <vcc<5.5v, -30ua<<br="">I_TMON&lt;30uA; Guaranteed<br/>by char</vcc<5.5v,>                 | -5    |      | 5     | °C    |

| Analog monitoring range                                                                                  | Tmon                | -40°C to 150°C                                                                                                     | 500   |      | 1100  | mV    |

| Analog Monitoring<br>Accuracy                                                                            |                     | -40°C to 125°C,<br>4.5V <vcc<5.5v, -30ua<<br="">I_TMON&lt;30uA, Note 2</vcc<5.5v,>                                 | -9    |      | 9     | °C    |

| Temperature coefficient                                                                                  |                     |                                                                                                                    |       | 2.27 |       | mV/°C |

| Thermal shutdown<br>hysteresis                                                                           |                     | Note 2                                                                                                             |       | 25   |       | °C    |

| Input Voltage Reporting                                                                                  |                     |                                                                                                                    |       |      |       |       |

| Resolution                                                                                               | Nevin               | Note 2                                                                                                             |       | 1/32 |       | V     |

| Monitoring Range                                                                                         | PMBVinmon           |                                                                                                                    | 0     |      | 16    | V     |

| Monitoring accuracy                                                                                      |                     | 0°C to 85°C, 4.5V <vcc<5.5v,<br>PVin&gt;10V</vcc<5.5v,<br>                                                         | -1.5  |      | 1.5   |       |

|                                                                                                          |                     | -40°C to 125°C,<br>4.5V <vcc<5.5v, pvin="">14V</vcc<5.5v,>                                                         | -1.5  |      | 1.5   | %     |

|                                                                                                          |                     | -40ºC to 125ºC,<br>4.5V <vcc<5.5v,<br>6V<pvin<14v< td=""><td>-3</td><td></td><td>3</td></pvin<14v<></vcc<5.5v,<br> | -3    |      | 3     |       |

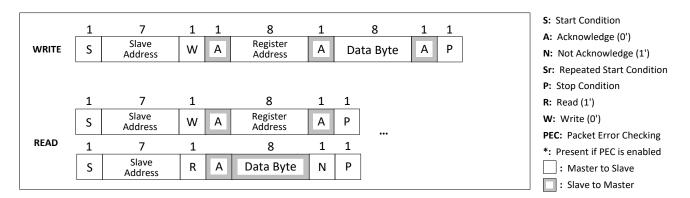

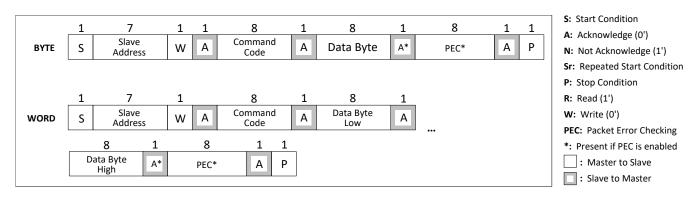

| PMBus Interface Timing Sp                                                                                | pecifications       |                                                                                                                    |       |      |       |       |

| Bus Free time between<br>Start and Stop condition                                                        | TBUF                |                                                                                                                    | 1.3   |      |       | us    |

| Hold time after<br>(Repeated) Start<br>Condition. After this<br>period, the first clock is<br>generated. | Thd:sta             |                                                                                                                    | 0.6   |      |       | us    |

| Repeated start<br>condition setup time                                                                   | T <sub>SU:STA</sub> |                                                                                                                    | 0.6   |      |       | us    |

| Stop condition setup time                                                                                | Tsu:sto             |                                                                                                                    | 0.6   |      |       | us    |

| Data Rising Threshold                                                                                    |                     |                                                                                                                    | 1.339 |      | 1.766 | V     |

| Data Falling Threshold                                                                                   |                     |                                                                                                                    | 1.048 |      | 1.495 | V     |

| Clock Rising Threshold                                                                                   |                     |                                                                                                                    | 1.339 |      | 1.766 | V     |

| Clock Falling Threshold                                                                                  |                     |                                                                                                                    | 1.048 |      | 1.499 | V     |

| Data Hold Time                                                                                           | T <sub>HD:DAT</sub> |                                                                                                                    | 300   |      | 900   | ns    |

| Data Setup Time                                                                                          | T <sub>SU:DAT</sub> |                                                                                                                    | 100   |      |       | ns    |

| Clock low time out                                                                                       | Ттімеоцт            |                                                                                                                    | 25    |      | 35    | ms    |

| Clock low period                                                                                         | TLOW                |                                                                                                                    | 1.3   |      |       | us    |

| PARAMETER         | SYMBOL | CONDITIONS | MIN | ТҮР | МАХ | UNIT |

|-------------------|--------|------------|-----|-----|-----|------|

| Clock High Period | Тнідн  |            | 0.6 |     | 50  | us   |

### Notes

- 2. Guaranteed by design but not tested in production

- 3. Guaranteed by statistical correlation, but not tested in production

14

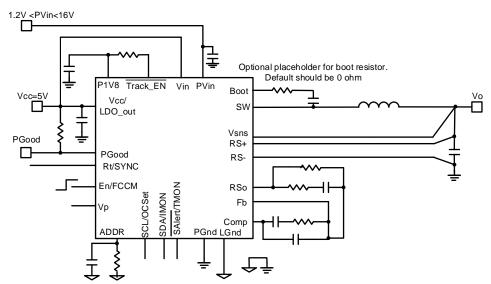

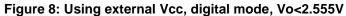

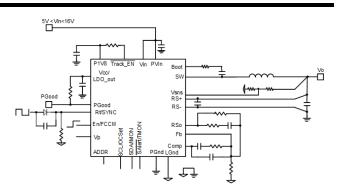

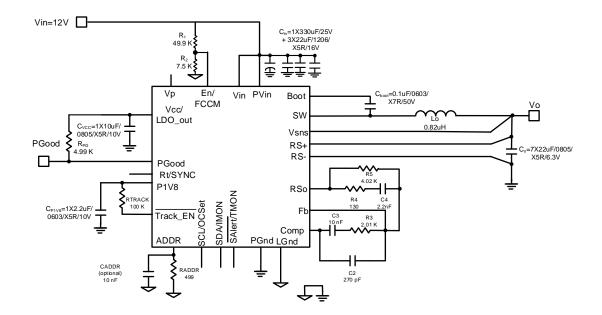

## **TYPICAL APPLICATION DIAGRAMS**

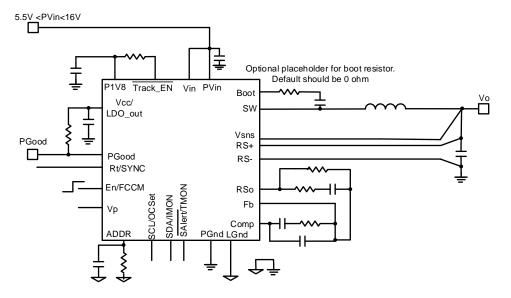

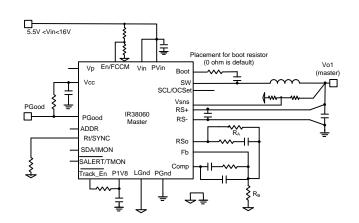

Figure 5: Using the internal LDO, digital mode, Vo < 2.555V

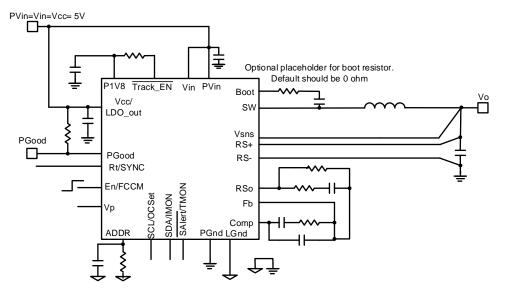

## **TYPICAL APPLICATION DIAGRAMS**

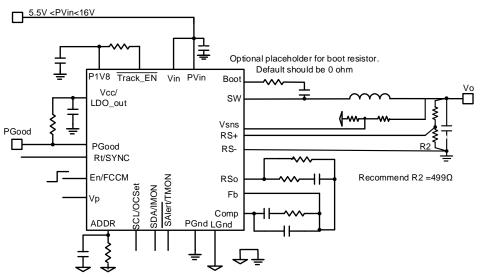

Figure 7: Using the internal LDO, analog mode, Vo<2.555V

## **TYPICAL APPLICATION DIAGRAMS**

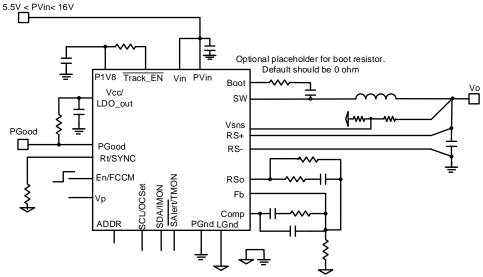

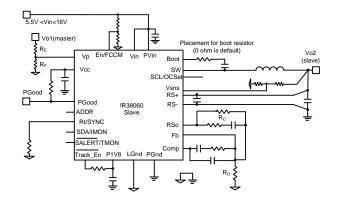

Figure 10: Using the internal LDO, digital mode, tracking mode

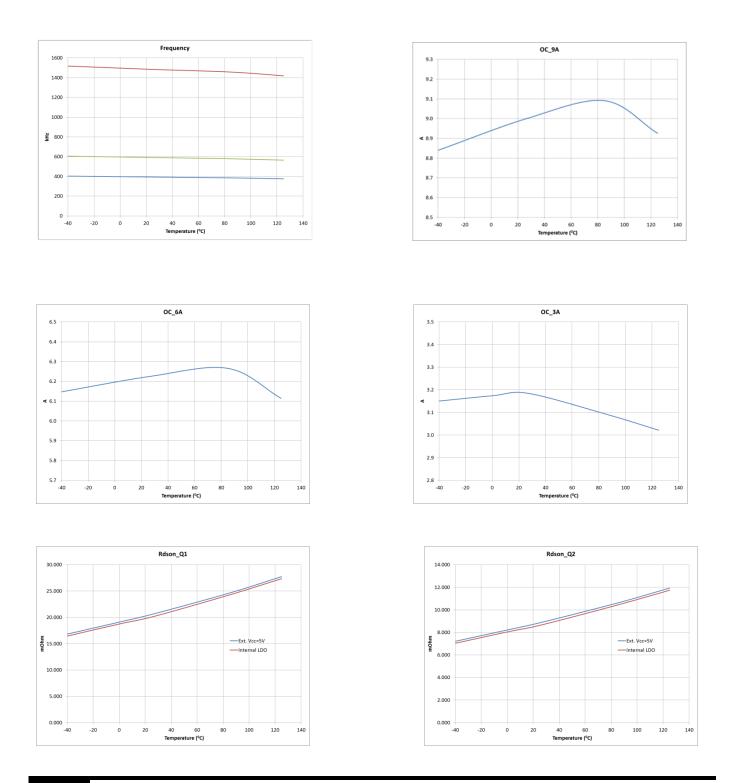

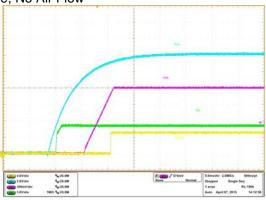

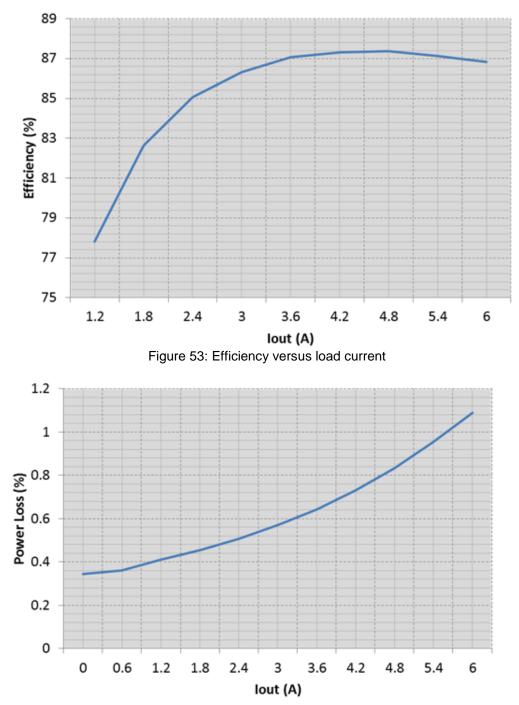

## **TYPICAL EFFICIENCY AND POWER LOSS CURVES**

PVin = Vin = 12V, VCC = Internal LDO, Io=0-6A, Fs= 600kHz, Room Temperature, No Air Flow. Note that the losses of the inductor, input and output capacitors are also considered in the efficiency and power loss curves. The table below shows the indicator used for each of the output voltages in the efficiency measurement.

| VOUT (V) | LOUT (uH) | P/N                 | DCR (mΩ) |

|----------|-----------|---------------------|----------|

| 0.6      | 0.82      | SPM6550T-R82M (TDK) | 4.3      |

| 0.8      | 0.82      | SPM6550T-R82M (TDK) | 4.3      |

| 1        | 0.82      | SPM6550T-R82M (TDK) | 4.3      |

| 1.2      | 1.0       | SPM6550T-1R0M (TDK) | 4.7      |

| 1.5      | 1.0       | SPM6550T-1R0M (TDK) | 4.7      |

| 1.8      | 1.0       | SPM6550T-1ROM (TDK) | 4.7      |

| 2.5      | 2.2       | WE-7443340220 (WE)  | 4.4      |

| 3.3      | 2.2       | WE-7443340220 (WE)  | 4.4      |

| 5        | 2.2       | WE-7443340220 (WE)  | 4.4      |

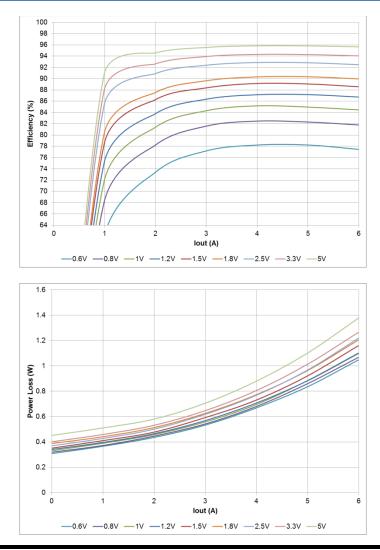

## **TYPICAL EFFICIENCY AND POWER LOSS CURVES**

PVin = Vin = VCC = 5V, Io=0-6A, Fs= 600kHz, Room Temperature, No Air Flow. Note that the losses of the inductor, input and output capacitors are also considered in the efficiency and power loss curves. The table below shows the indicator used for each of the output voltages in the efficiency measurement.

| VOUT (V) | LOUT (uH) | P/N                 | DCR (mΩ) |

|----------|-----------|---------------------|----------|

| 0.6      | 0.82      | SPM6550T-R82M (TDK) | 4.3      |

| 0.8      | 0.82      | SPM6550T-R82M (TDK) | 4.3      |

| 1        | 0.82      | SPM6550T-R82M (TDK) | 4.3      |

| 1.2      | 0.82      | SPM6550T-R82M (TDK) | 4.3      |

| 1.5      | 0.82      | SPM6550T-R82M (TDK) | 4.3      |

| 1.8      | 0.82      | SPM6550T-R82M (TDK) | 4.3      |

| 2.5      | 0.82      | SPM6550T-R82M (TDK) | 4.3      |

| 3.3      | 0.82      | SPM6550T-R82M (TDK) | 4.3      |

## THEORY OF OPERATION

## DESCRIPTION

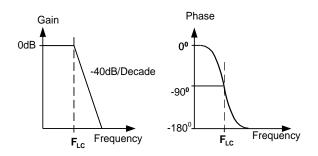

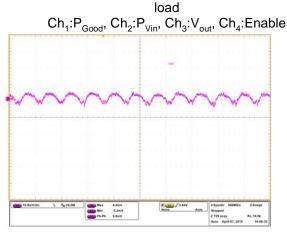

The IR38060 is a 6A synchronous buck regulator with a selectable digital interface and an externally compensated fast, analog, PWM voltage mode control scheme to provide good noise immunity as well as fast dynamic response in a wide variety of applications. At the same time, enabling the digital PMBus interface allows complete configurability of output setting and fault functions, as well as telemetry.

The switching frequency is programmable to 1.5MHz and provides the capability of optimizing the design in terms of size and performance.

IR38060 provides precisely regulated output voltage from 0.5V to 0.875\*PVin programmed via two external resistors or digitally through PMBus commands. The IR38060 operates with an internal bias supply (LDO), typically 5.2V. This allows operation with a single supply. The output of this LDO is brought out at the Vcc pin and may be bypassed to the system power ground with a 10 uF decoupling capacitor. The Vcc pin may also be connected to the Vin pin, and an external Vcc supply between 4.5V and 5.5V may be used, allowing an extended operating bus voltage (PVin) range from 1.2V to 16V.

The device utilizes the on-resistance of the low side MOSFET (synchronous MOSFET) as current sense element. This method enhances the converter's efficiency and reduces cost by eliminating the need for external current sense resistor.

IR38060 includes two low  $R_{ds(on)}$  MOSFETs using IR's HEXFET technology. These are specifically designed for high efficiency applications.

## **DEVICE POWER-UP AND INITIALIZATION**

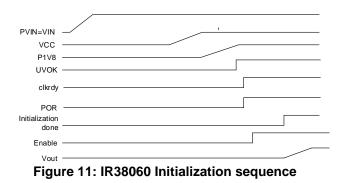

During the power-up sequence, when Vin is brought up, the internal LDO converts it to a regulated 5.2V at Vcc. There is another LDO which further converts this down to 1.8V to supply the internal digital circuitry. An under-voltage lockout circuit monitors the voltage of VCC pin and the P1V8 pin, and holds the Power-on-reset (POR) low until these voltages exceed their thresholds and the internal 48 MHz oscillator is stable. When the device comes out of reset, it initializes a multiple times programmable memory (MTP) load cycle, where the contents of the MTP are loaded into the working registers. Once the registers are loaded from MTP, the designer can use PMBus commands to re-configure the various parameters to suit the specific VR design requirements if desired, irrespective of the status of Enable.

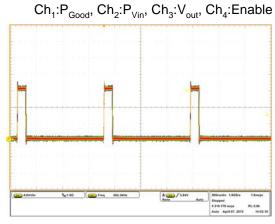

In the default configuration, power conversion is enabled only when the En/FCCM pin voltage exceeds its undervoltage threshold, the PVin bus voltage exceeds its undervoltage threshold, the contents of the MTP have been fully loaded into the working registers and the device address has been read. The initialization sequence is shown in Figure Figure 11.

IR38060 provides additional options to enable the device power conversion through software and these options may be configured to override the default by using the I2C interface or PMBus, if used in digital mode. For further details see UN0060 IR3806x PMBus commandset user note.

## ANALOG AND DIGITAL MODE OPERATION

The IR38060 has 2 7-bit registers that are used to set the base I2C address and base PMBus address of the device, as shown below in Table 1.

# Table 1: Registers used to set device base address

| Register           | Description                                                               |  |  |

|--------------------|---------------------------------------------------------------------------|--|--|

| I2c_address[6:0]   | The chip I2C address. An address of 0 will disable communication          |  |  |

| Pmbus_address[6:0] | The chip PMBus address.<br>An address of 0 will disable<br>communication. |  |  |

In addition, a resistor may be connected between the ADDR and LGND pins to set an offset from the default preconfigured I2C address (0x10)/PMBus address (0x40) in the MTP. Up to 16 different offsets can be set, allowing 16 IR38060 devices with unique addresses in a single system. This offset, and hence, the device address, is read by the internal 10 bit ADC during the initialization sequence. It is recommended that a layout placement be provided for a capacitor in parallel with this offset resistor. On noisier systems, a small capacitance (e.g. 2.2nF) may help the 10 bit ADC read the offset and generate the appropriate address offset.

Table 2 below provides the resistor values needed to set the 16 offsets from the base address.

# Table 2 : Address offset vs. External Resistor(R<sub>ADDR</sub>)

| ADDR Resistor<br>(Ohm) | Address Offset |  |

|------------------------|----------------|--|

| 499                    | +0             |  |

| 1050                   | +1             |  |

| 1540                   | +2             |  |

| 2050                   | +3             |  |

| 2610                   | +4             |  |

| 3240                   | +5             |  |

| 3830                   | +6             |  |

| 4530                   | +7             |  |

| 5230                   | +8             |  |

| 6040                   | +9             |  |

## IR38060

| 6980  | +10 |

|-------|-----|

| 7870  | +11 |

| 8870  | +12 |

| 9760  | +13 |

| 10700 | +14 |

| 11800 | +15 |

|       |     |

The device will then respond to I2C/PMbus commands sent to this address. This mode in which digital communication to and from the device is allowed following the MTP load sequence is referred to as the digital mode of operation. However, if the ADDR pin is left floating, the IR38060 disables digital communication and will not respond to commands sent over the bus. In fact, the 3 pins used for digital communication are dual purpose pins which get reconfigured for analog applications if ADDR is left floating. Hence, in the analog mode, the default configuration parameters loaded in to the working registers from the MTP during the initialization sequence cannot be modified on the fly, and the device can be operated similar to an analog only SupIRBuck such as IR3847.

## **BUS VOLTAGE UVLO**

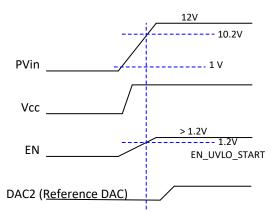

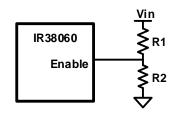

In the analog mode of operation or with the default configuration, if the input to the Enable pin is derived from the bus voltage by a suitably programmed resistive divider, it can be ensured that the IR38060 does not turn on until the bus voltage reaches the desired level as shown in Figure 12. Only after the bus voltage reaches or exceeds this level and voltage at the Enable pin exceeds its threshold (typically 1.2V) IR38060 will be enabled. Therefore, in addition to being a logic input pin to enable the IR38060, the Enable feature, with its precise threshold, also allows the user to override the default 1 V Under-Voltage Lockout for the bus voltage (PVin). This is desirable particularly for high output voltage applications, where we might want the IR38060 to be disabled at least until PVin exceeds the desired output voltage level. Alternatively, the default 1 V PVin UVLO threshold may be reconfigured/overridden using the VIN\_ON and VIN OFF PMBus commands. It should be noted that while the input voltage is also fed to an ADC

through a 21:1 internal resistive divider, the digitized input voltage is used only for the purposes of reporting the input voltage through the READ VIN PMBUs command and has no impact on the bus voltage UVLO, input overvoltage faults and input undervoltage warnings, all of which are implemented by using analog comparators to compare the input voltage to the corresponding thresholds programmed by the PMBus commands VIN ON, VIN OV FAULT LIMIT VIN OFF, and VIN UV WARN\_LIMIT respectively. The bus voltage reading as reported by READ VIN has no effect on the input feedforward function either.

Figure 12: Normal Start up, device turns on when the bus voltage reaches 10.2V

A resistor divider is used at EN pin from PVin to turn on the device at 10.2V.

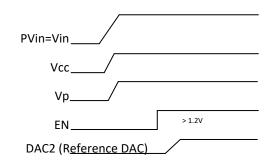

Figure 14: Recommended startup for sequencing operation (ratiometric or simultaneous)

# Figure 15: Recommended startup for memory tracking operation (DDR-VTT)

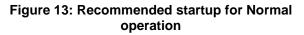

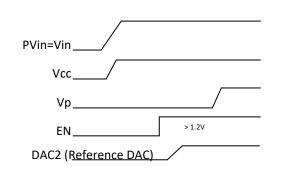

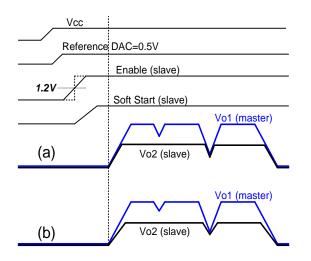

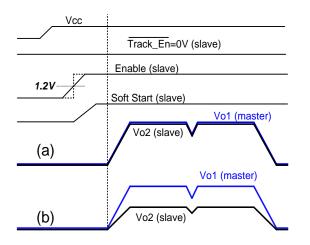

Figure 13 shows the recommended startup sequence for the normal (non-tracking, nonsequencing) operation of IR38060, when Enable is used as logic input. In this operating mode, a 100 kOhm resistor is connected from Track\_En to P1V8. Figure 14 shows the recommended startup sequence for sequenced operation of IR38060 with Enable used as logic input. For this mode of operation also, a 100 kOhm resistor is connected from Track\_En to P1V8. Figure 15 shows the recommended startup sequence for tracking operation of IR38060 with Enable used as logic input. For this mode of operation of IR38060 with Enable used as logic input. For this mode of operation of IR38060 with Enable used as logic input. For this mode of operation, Track\_En should be connected to LGND.

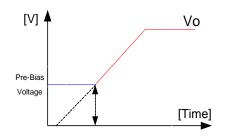

## PRE-BIAS STARTUP

IR38060 is able to start up into pre-charged output, which prevents oscillation and disturbances of the output voltage.

26

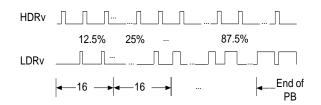

The output starts in asynchronous fashion and keeps the synchronous MOSFET (Sync FET) off until the first gate signal for control MOSFET (Ctrl FET) is generated. Figure 16 shows a typical Pre-Bias condition at start up. The sync FET always starts with a narrow pulse width (12.5% of a switching period) and gradually increases its duty cycle with a step of 12.5%, with 16 cycles at each step, until it reaches the steady state value. Figure 17 shows the series of 16x8 startup pulses.

Figure 16: Pre-Bias startup

Figure 17: Pre-Bias startup pulses

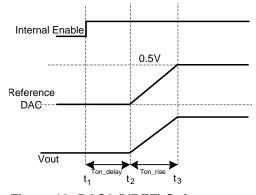

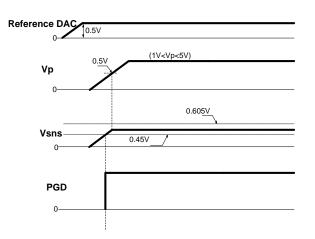

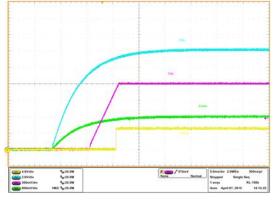

### SOFT-START (REFERENCE DAC RAMP)

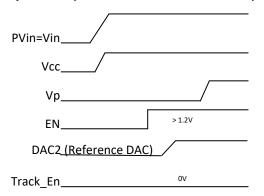

IR38060 has an internal soft starting DAC to control the output voltage rise and to limit the current surge at the start-up. In the default configuration and in analog mode, to ensure correct start-up, the DAC sequence initiates only after power conversion is enabled when the En/FCCM pin voltage exceeds its undervoltage threshold, the PVin bus voltage exceeds its undervoltage threshold and the contents of the MTP have been fully loaded into the working registers. In analog mode and in the default configuration, the reference DAC signal linearly rises to 0.5V in 2 ms. Figure 18 shows the waveforms during soft start In digital mode, the reference DAC soft-start may be delayed from time power conversion is enabled. The range for this

programmable delay is 0ms to 127 ms, and the resolution is 1 ms. Further, the soft start time may be configured from 1ms to 127 ms with 1 ms resolution.

For more details on the PMBus commands TON\_DELAY and TON\_RISE used to program the startup sequence, please see the UN0060 IR3806x PMBus commandset user note.

Note however, that a shorter Ton\_Rise can lead to a slight overshoot on the output voltage during startup. Infineon recommends using a rise time that would limit the soft start rate to <0.4mV/us. Also, it is recommended that the system designer should verify in the actual design that the selected rise time keeps the overshoot within limits acceptable to the system.

Figure 18: DAC2 (VREF) Soft start

During the startup sequence the over-current protection (OCP) and over-voltage protection (OVP) are active to protect the device for any short circuit or over voltage condition.

### **OPERATING FREQUENCY**

In the analog mode, the switching frequency can be programmed between 306kHz - 1500kHz by connecting an external resistor from Rt pin to LGnd. This frequency is set during the initialization sequence, when the 10 bit ADC reads the voltage at the RT pin. It should be noted that after the

initialization sequence is complete, the ADC no longer reads the voltage at the ADC pin, so changing the resistor on the fly after initialization will not affect the switching frequency. Table 3 tabulates the oscillator frequency versus R<sub>t</sub>.

#### Table 3: Switching Frequency (F<sub>s</sub>) vs. External Resistor(*R*t)

| Resistor(R)                         |         |  |  |

|-------------------------------------|---------|--|--|

| R <sub>t</sub><br>Resistor<br>(Ohm) | F₅(kHz) |  |  |

| 499                                 | 306     |  |  |

| 1050                                | 356     |  |  |

| 1540                                | 400     |  |  |

| 2050                                | 444     |  |  |

| 2610                                | 500     |  |  |

| 3240                                | 550     |  |  |

| 3830                                | 600     |  |  |

| 4530                                | 706     |  |  |

| 5230                                | 750     |  |  |

| 6040                                | 800     |  |  |

| 6980                                | 923     |  |  |

| 7870                                | 1000    |  |  |

| 8870                                | 1091    |  |  |

| 9760                                | 1200    |  |  |

| 10700                               | 1333    |  |  |

| 11800                               | 1500    |  |  |

|                                     |         |  |  |

In the digital mode, the default switching frequency is configured to be 607 kHz, and is programmable from 250 kHz to 1500 kHz. The user can override this using the FREQUENCY\_SWITCH PMBus command. In the digital mode of operation no resistor is used or needed on the R<sub>t</sub>/Sync pin. For best telemetry accuracy, it is recommended that the following switching frequencies be avoided: 250 kHz, 300 kHz, 400 kHz, 500 kHz, 600 kHz, 750 kHz, 800 kHz, 1 MHz, 1.2 MHz and 1.5 MHz. Instead, Infineon suggests using the following values 251 kHz, 302 kHz, 403 kHz, 505 kHz, 607 kHz, 762 kHz, 813 kHz, 978 kHz, 1171 kHz and 1454 kHz respectively.

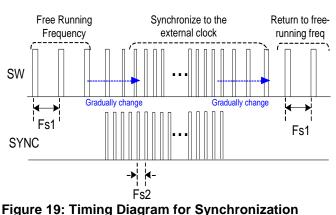

## EXTERNAL SYNCHRONIZATION

IR38060 incorporates an internal phase lock loop (PLL) circuit which enables synchronization of the internal oscillator to an external clock. This function is important to avoid sub-harmonic oscillations due to beat frequency for embedded systems when multiple point-of-load (POL) regulators are used. A multi-function pin, Rt/Sync, is used to connect the external clock. In the analog mode, if the external clock is applied before the initialization sequence is done, the internal ADC cannot read the value of the RT resistor and hence, for proper operation, it is mandatory that the external clock remains applied. If the synchronization clock is then lost after initialization, the IR38060 will treat this as a symptom of a failure in the system and disable power conversion. Therefore, for such applications, where the switching frequency is always determined by an external synchronization clock, the Rt/Sync pin can be connected to the external clock signal solely and no other resistor is needed. If the external clock is applied after the initialization sequence, the IR38060 treats this as an application where the converter switching frequency is allowed to run at free-running frequency the internal if the synchronization clock is lost. Therefore, in analog mode, an external resistor from Rt/Sync pin to LGnd is required to set the free-running frequency. In the digital mode, the resistor is not needed because the free running frequency is set in an internal register.

When an external clock is applied to Rt/Sync pin after the converter runs in steady state with its freerunning frequency, a transition from the free-running frequency to the external clock frequency will happen. This transition is to gradually make the actual switching frequency equal to the external clock frequency, no matter which one is higher. When the external clock signal is removed from Rt/Sync pin, the switching frequency is also changed to free-running gradually.

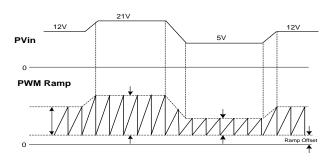

#### Figure 19: Timing Diagram for Synchronization to the external clock (Fs1>Fs2 or Fs1<Fs2)

An internal circuit is used to change the PWM ramp slope according to the clock frequency applied on Rt/Sync pin. Even though the frequency of the external synchronization clock can vary in a wide range, the PLL circuit will make sure that the ramp amplitude is kept constant, requiring no adjustment of the loop compensation. PVin variation also affects the ramp amplitude, which will be discussed separately in Feed-Forward section.

It must be noted here that in analog mode, since the voltage at the Rt/Sync pin is read by the ADC at startup special care must be taken if a low impedance system clock is used for synchronization and is applied before the initialization sequence is done. The circuit shown in **Figure** 20 below shows how this may be done using a diode-capacitor combination. This couples the clock edges to the Rt/Sync pin while not loading the Rt/SYNC pin with the impedance of the synchronization clock, and thus not affecting the Rt voltage read by the ADC at startup.

# Figure 20: Synchronizing a low impedance clock in analog mode

It must be re-iterated that this is not a concern in digital mode and the clock may be directly applied to the Rt/Sync pin.

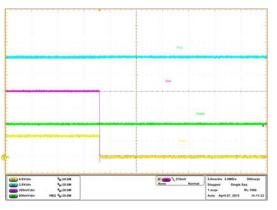

## SHUTDOWN

In the default configuration, IR38060 can be shutdown by pulling the Enable pin below its 1.0V threshold. During shutdown the high side and the low side drivers are turned off. By default, the device exhibits an immediate shutdown with no delay and no soft stop.

Alternatively, in digital mode, the part may be configured to allow shutdown using the OPERATION PMBus command as well.

# CURRENT SENSING, TELEMETRY AND OVER CURRENT PROTECTION

Current sensing for both, telemetry as well as overcurrent protection is done by sensing the voltage across the sync FET RDson. This method enhances the converter's efficiency, reduces cost by eliminating a current sense resistor and any minimizes sensitivity to layout related noise issues. A novel, patented scheme allows reconstruction of the average inductor current from the voltage sensed across the Sync FET Rdson. It should be noted here that it is this reconstructed average inductor current that is digitized by the ADC and used for output current reporting as well as for overcurrent warning, the threshold for which may be set using the IOUT\_OC\_WARN\_LIMIT command.

The current is reported in 1/16A resolution using the READ IOUT PMBus command.

The Over current (OC) fault protection circuit also uses the voltage sensed across the RDS(on) of the Synchronous MOSFET; however, the protection mechanism relies on a fast comparator to compare the sensed signal to the overcurrent threshold and does not depend on the ADC or reported current. In the analog mode of operation, the current limit can be set to one of three possible settings by floating the OCSet pin, or pulling it up to Vcc or pulling it down to PGnd. The current limit scheme in the IR38060 uses an internal temperature compensated current source that has the same temperature coefficient as the R<sub>DS(on)</sub> of the Synchronous MOSFET. As a result, the over-current trip threshold remains almost constant over temperature.

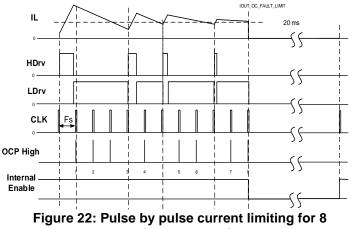

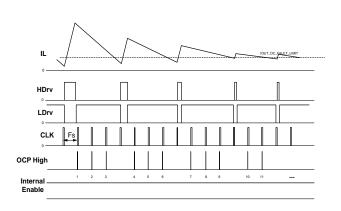

Over Current Protection circuitry senses the inductor current flowing through the Synchronous FET closer to the valley point. The OCP circuit samples this current for 75 ns typically after the rising edge of the PWM set pulse which is an internal signal that has a width of 12.5% of the switching period. The PWM pulse that turns on the high side FET starts at the falling edge of the PWM set pulse. This makes valley current sense more robust as current is sensed close to the bottom of the inductor downward slope where transient and switching noise is low. This helps to prevent false tripping due to noise and transients.

The actual DC output current limit point will be greater than the valley point by an amount equal to approximately half of the peak to peak inductor ripple current. The current limit point will be a function of the inductor value, input voltage, output voltage and the frequency of operation. On equation 1. It imit is the value set when configuring the OCP value. The user should account for the inductor ripple to obtain the actual DC output current limit.

$$I_{OCP} = I_{LIMIT} + \frac{\Delta i}{2} \tag{1}$$

- **I**OCP = DC current limit hiccup point

- = Current Limit Valley Point LIMIT Δi

- = Inductor ripple current

### Figure 21: Timing Diagram for Current Limit Hiccup

In the default configuration and in analog mode, if the overcurrent detection trips the OCP comparator, the IR38060 goes into a hiccup mode after 8 current limit cycles. In order to put the part into hiccup, a total of 8 current limited cycles in needed. If the device sees 6 consecutive cycles without an overcurrent condition it resets the 8 cycle counter. The hiccup is performed by de-asserting the internal Enable signal to the analog and power conversion circuitry and holding it low for 20 ms.

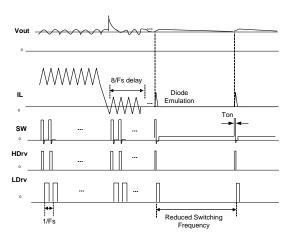

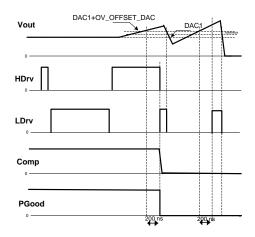

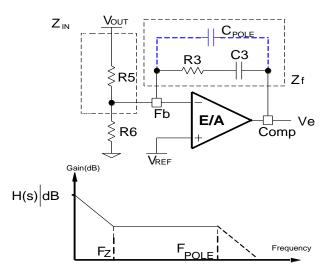

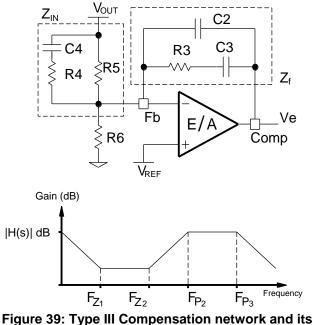

Following this, the OCP signal resets and the converter recovers. After every hiccup cycle, the converter stays in this mode until the overload or short circuit is removed. This behavior is shown in Figure 21.