# Hibernate

XMC<sup>™</sup> microcontrollers September 2016

- 1 Overview

- 2 Key feature: real time clock and retention memory

- Key feature: low power analog comparator

- 4 Key feature: flexible wake-up configuration

- 5 System integration

- 6 Application examples

- 7 Software view

- 1 Overview

- 2 Key feature: real time clock and retention memory

- 3 Key feature: low power analog comparator

- 4 Key feature: flexible wake-up configuration

- 5 System integration

- 6 Application examples

- 7 Software view

#### Hibernate

### **Highlights**

XMC<sup>™</sup>4000 provides a very low power hibernate mode allowing power saving while real time keeping and system context retention in sixteen 32-bit registers, at current consumption below 10 µA.

### **Key feature**

- Real time clock and retention memory

- Low Power Analog Comparator (LPAC)

- Flexible wake-up configuration

### **Customer benefits**

- Real time and context keeping while the rest of the system is powered off

- Support for wake-up on analog event

- Diversity of wake-up trigger options from external and internal sources

- 1 Overview

- Key feature: real time clock and retention memory

- 3 Key feature: low power analog comparator

- 4 Key feature: flexible wake-up configuration

- 5 System integration

- 6 Application examples

- 7 Software view

# Hibernate Real time clock and retention memory

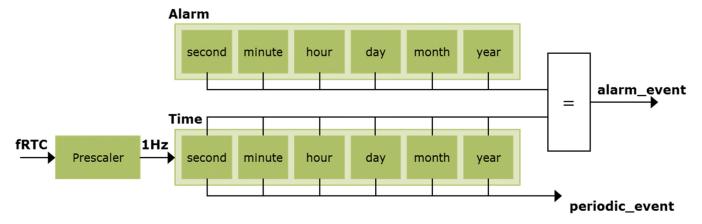

- > RTC features

- Clock and calendar function

- Generation of alarms and periodic events including wake-up events

- Time keeping during system power off

- 16 x 32-bit registers for data storage

- Context storage for wake-up from hibernate

- 1 Overview

- 2 Key feature: real time clock and retention memory

- 3 Key feature: low power analog comparator

- 4 Key feature: flexible wake-up configuration

- 5 System integration

- 6 Application examples

- 7 Software view

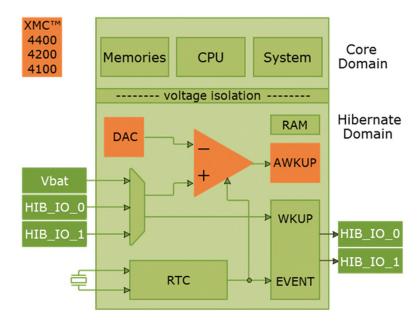

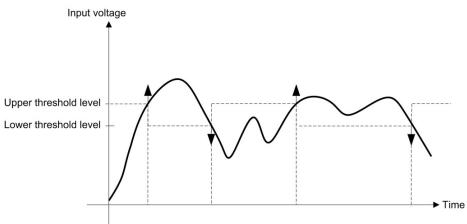

# Hibernate Low power analog comparator (LPAC)

- Supports wake-up from hibernate on analog events

- 3 independent analog input channels: battery supply pin V<sub>BAT</sub>, HIB\_IO\_0, HIB\_IO\_1

- Compare triggered by RTC, digital HIB\_IO event, software or continuous mode

- Upper and lower threshold programmable with 6-bit resolution (64 level)

- 1 Overview

- 2 Key feature: real time clock and retention memory

- 3 Key feature: low power analog comparator

- 4 Key feature: flexible wake-up configuration

- 5 System integration

- 6 Application examples

- 7 Software view

# Hibernate Flexible wake-up configuration

- Wake-up from hibernate on

- Digital input signals at HIB\_IO pins

- RTC events

- Single alarm

- Periodic event

- Low Power Analog Comparator (LPAC) event on the analog input signal

- Analog sensor input

- Threshold crossing on V<sub>BAT</sub> pin

- 1 Overview

- 2 Key feature: real time clock and retention memory

- 3 Key feature: low power analog comparator

- 4 Key feature: flexible wake-up configuration

- 5 System integration

- 6 Application examples

- 7 Software view

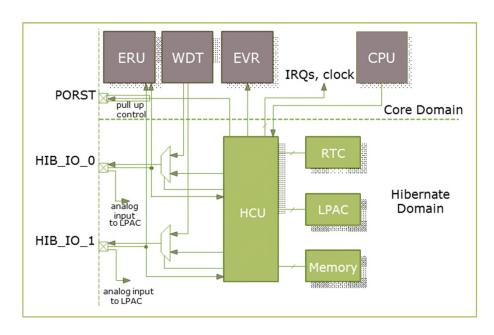

# Hibernate System integration

- Target applications

- Human machine interface

- General purpose

LPAC module is available on XMC<sup>™</sup>4400 and XMC<sup>™</sup>4200 only.

The hibernate domain consists of several functional modules that can be used in hibernate mode and also in active mode.

User software can access hibernate domain registers and memory while in active mode.

- 1 Overview

- 2 Key feature: real time clock and retention memory

- 3 Key feature: low power analog comparator

- 4 Key feature: flexible wake-up configuration

- 5 System integration

- 6 Application examples

- 7 Software view

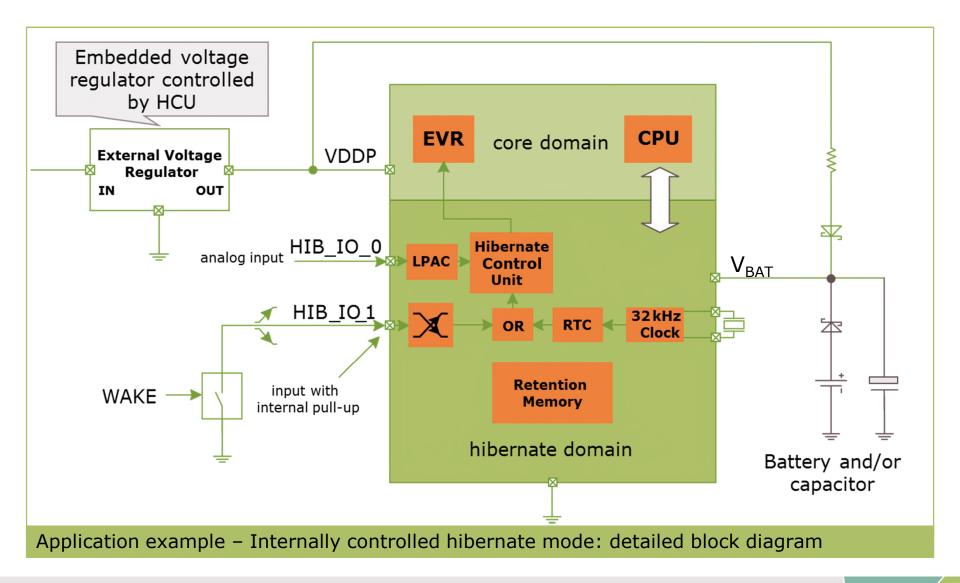

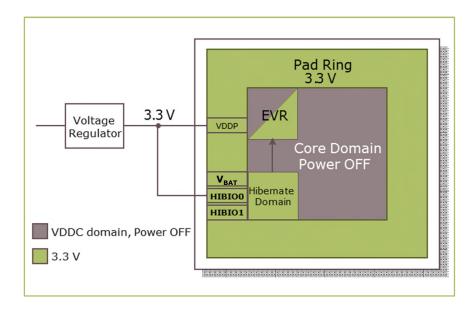

# Application example Internally controlled hibernate mode

### **Overview**

The main chip supply voltage is present during hibernate mode. Embedded voltage regulator (EVR) is controlled by hibernate domain. Core domain of the chip is powered off.

Current consumption of  $\sim$ 25  $\mu$ A can be achieved while RTC is active.

#### In brief

The lowest BoM. Valid supply voltage present while in hibernate mode.

Supported on XMC<sup>™</sup>4400 and XMC<sup>™</sup>4200 only.

# Application example Internally controlled hibernate mode