# GPDMA General Purposes DMA

XMC<sup>™</sup> microcontrollers September 2016

- 1 Overview

- 2 Key feature: multi-block transfers through linked list

- 3 Key feature: scatter or gather transfer mode

- 4 Key feature: software or hardware triggered DMA

- 5 System integration

- 6 Application example

- 1 Overview

- 2 Key feature: multi-block transfers through linked list

- 3 Key feature: scatter or gather transfer mode

- 4 Key feature: software or hardware triggered DMA

- 5 System integration

- 6 Application example

# GPDMA General Purposes DMA

#### **Highlights**

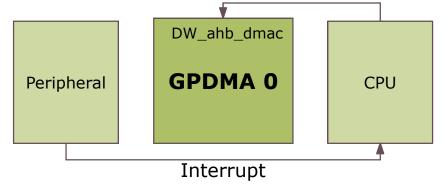

The GPDMA is a highly configurable DMA controller, that allows low latency data transfers between peripherals and memories. Complex data transfers can be done with minimal intervention of the processor, keeping this way the CPU resources free for other operations. DMA line router also provides flexible peripheral connection to different DMA channels.

#### **Key feature**

- Multi-block transfers achieved through linked list

- Scatter or gather transfer mode

- Software or hardware triggered DMA

#### **Customer benefits**

- Can achieve greater flexibility for complex data transfer from source to destination

- Source or destination address increment or decrement and address offset

- Hardware trigger allows integrated system solution with minimal CPU loading

- 1 Overview

- 2 Key feature: multi-block transfers through linked list

- 3 Key feature: scatter or gather transfer mode

- 4 Key feature: software or hardware triggered DMA

- 5 System integration

- 6 Application example

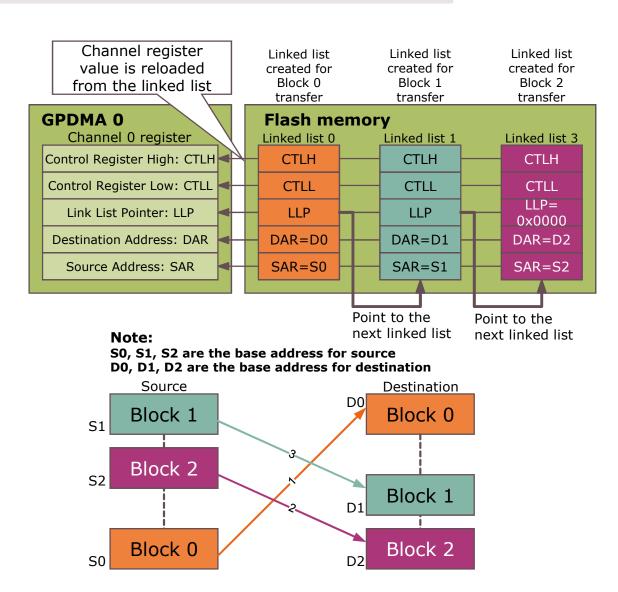

# GPDMA: Multi-block transfers achieved through linked list

- The linked list method offers greater flexibility for source and destination address control during multi block transfer

- The GPDMA reprograms the channel registers prior to the start of each block by fetching the linked list for that block from system memory

- GPDMA block chaining uses a Linked List

Pointer register (LLP) that stores the address in memory of the next linked list item

- 1 Overview

- 2 Key feature: multi-block transfers through linked list

- 3 Key feature: scatter or gather transfer mode

- 4 Key feature: software or hardware triggered DMA

- 5 System integration

- 6 Application example

### GPDMA

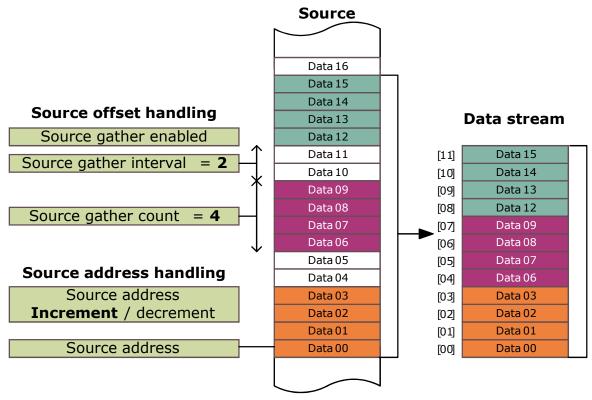

## Scatter or gather transfer mode (1/2)

- To perform a source address offset within a transfer block, we can make use of the gather transfer mode

- The source address is incremented or decremented by a programmed amount (source gather interval) when a gather boundary (source gather count) is reached

#### **GPDMA**

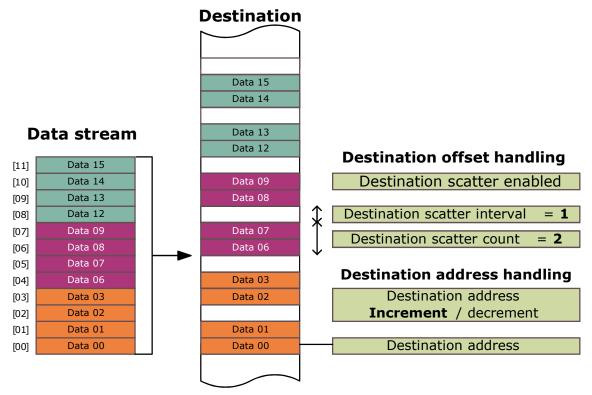

## Scatter or gather transfer mode (2/2)

- To perform a destination address offset within a transfer block, we can make use of the scatter transfer mode

- The destination address is incremented or decremented by a programmed amount (destination scatter interval) when a scatter boundary (destination scatter count) is reached

- 1 Overview

- 2 Key feature: multi-block transfers through linked list

- 3 Key feature: scatter or gather transfer mode

- 4 Key feature: software or hardware triggered DMA

- 5 System integration

- 6 Application example

#### **GPDMA**

#### Software or hardware triggered DMA

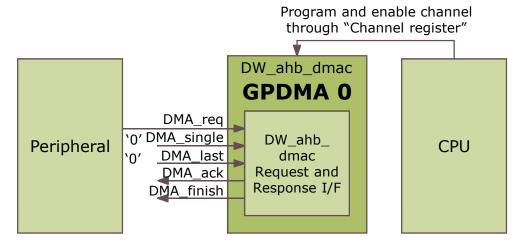

Software controlled transfers or synchronous transfers, when the peripheral requires to perform a DMA transaction triggers an interrupt. The interrupt service routine makes use of the software handshaking registers to initiate and control the DMA transaction acting as flow

controller

Hardware triggered transfers or asynchronous transfers make use of the service request signals of the peripheral to initiate the DMA transaction. DMA acts as flow controller

- 1 Overview

- 2 Key feature: multi-block transfers through linked list

- 3 Key feature: scatter or gather transfer mode

- 4 Key feature: software or hardware triggered DMA

- 5 System integration

- 6 Application example

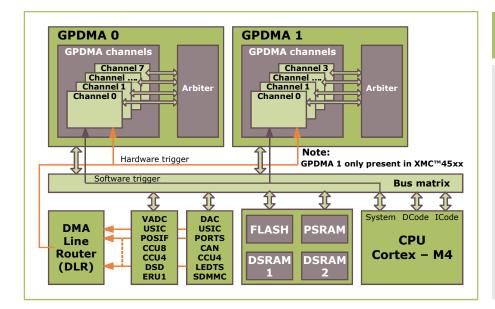

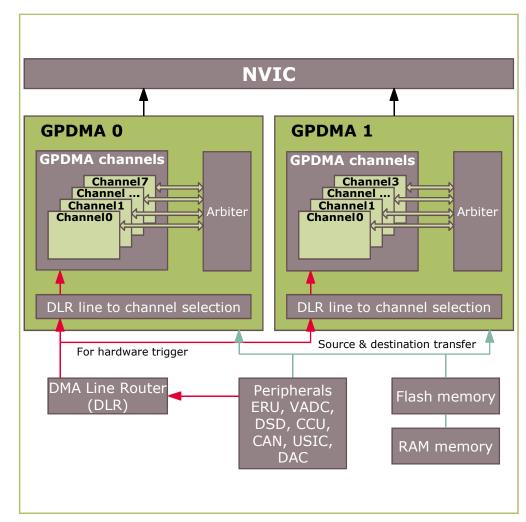

# GPDMA System integration

- The DMA can be triggered by the peripherals through the DMA line router

- DMA transfer is available for memoryto-memory, memory-to-peripheral, peripheral-to-memory, and peripheralto-peripheral

- DMA service can be generated for each channel due to DMA activity:

- Source transaction complete

- Destination transaction complete

- Block transfer complete

- DMA transfer complete

- Error

- 1 Overview

- 2 Key feature: multi-block transfers through linked list

- 3 Key feature: scatter or gather transfer mode

- 4 Key feature: software or hardware triggered DMA

- 5 System integration

- 6 Application example

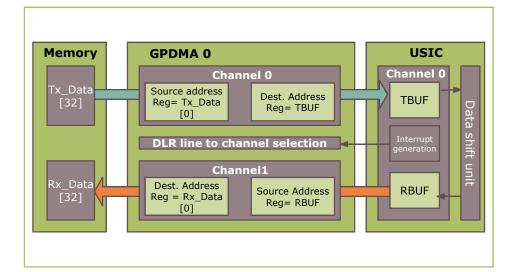

## Application example Integrated solution for data transfer

#### In brief

For communication, there is always a need to rely on software to copy data from memory to a transmit buffer or from a receive buffer to a memory area.

However this software copy process can be replaced by DMA transfer with hardware trigger, hence reducing the CPU loading.

#### **Overview**

#### Memory to peripheral

During transmission, with every byte of data being transmitted by the USIC will actually trigger the DMA to fetch the next byte of data from the memory and move to USIC TBUF.

#### **Peripheral to memory**

For receiving, when the UART had received a data, the DMA is triggered for a data transfer from the USIC RBUF to a designated memory buffer.

#### Support material

# Collaterals and Brochures

- Product Briefs

- Selection Guides

- Application Brochures

- Presentations

- Press Releases, Ads

www.infineon.com/XMC

#### **Technical Material**

- Application Notes

- Technical Articles

- Simulation Models

- Datasheets, MCDS Files

- PCB Design Data

- www.infineon.com/XMC

- Kits and Boards

- DAVETM

- Software and Tool Ecosystem

#### **Videos**

- Technical Videos

- Product InformationVideos

- Infineon Media Center

- XMC Mediathek

#### Contact

- Forums

- Product Support

- Infineon Forums

- Technical Assistance Center (TAC)

#### Disclaimer

The information given in this training materials is given as a hint for the implementation of the Infineon Technologies component only and shall not be regarded as any description or warranty of a certain functionality, condition or quality of the Infineon Technologies component.

Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this training material.

Part of your life. Part of tomorrow.