# IMD111T/IMD112T - iMOTION™ driver for motor control

### Motor controller with integrated high-voltage gate driver

IMD111T/IMD112T

#### **Features**

- Motion Control Engine (MCE) as a ready-to-use control solution for variable speed drives

- Integrated script engine for application control customization

- Integrated drive and system protection features

- Field oriented control (FOC) for permanent magnet synchronous motor (PMSM)

- Flexible space vector PWM for sinusoidal voltage control

- Current sensing via single or leg shunt

- Sensorless operation

- Hall sensor operation using analog or digital Hall

- Integrated analog comparators for over-current protection

- Built-in temperature sensor

- Power factor correction (PFC) control (optional)

- Flexible control input options: UART, Frequency, duty cycle or analog signal

- Certified drive safety functions according to IEC/UL 60730-1 'Class B'

- High voltage three phase gate driver with 600 V blocking voltage

- 15V supply voltage for gate driver

- · Thin-film-SOI-technology with negative transient robustness

- Ultra fast integrated boot strap diodes

- Integrated 5 V voltage regulator for controller supply

- External 5 V output available

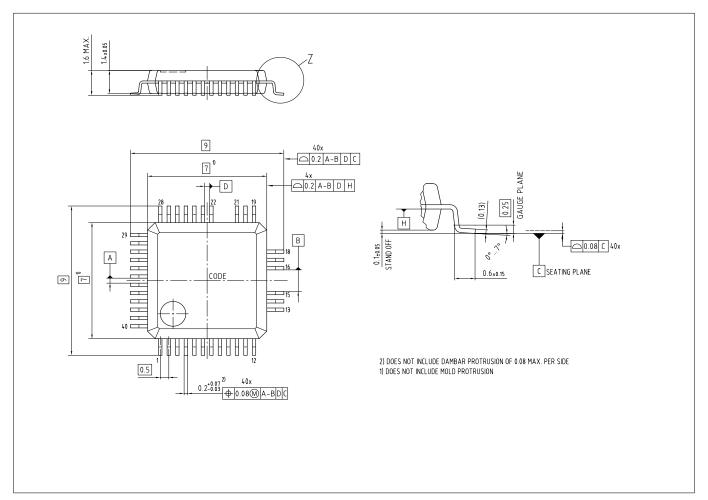

- Small LQFP-40 package with improved clearance & creepage

- Footprint derived from LQFP-48

## **Potential applications**

- Small and major home appliances

- Fans, Pumps, Compressors

- General purpose variable speed drives

### **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

**Description**

## **Description**

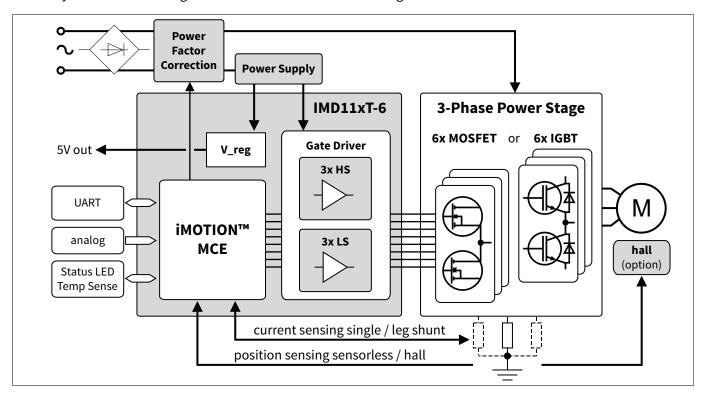

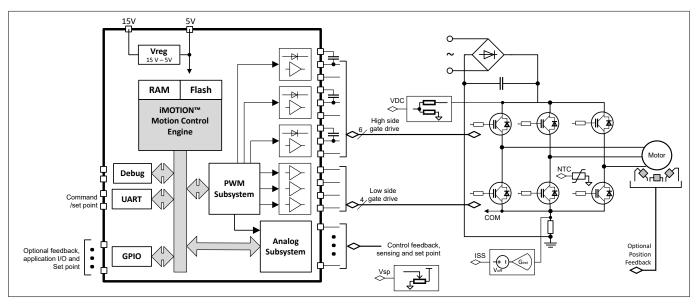

iMOTION™IMD110-6 is a family of highly integrated ICs for the control of variable speed drives. It integrates a motor controller with a high voltage three phase gate driver and a voltage regulator.

The motor controller uses the Motion Control Engine (MCE) to create a ready-to-use solution to perform control of a permanent magnet synchronous motor (PMSM) providing the shortest time to market for any motor system at the lowest system and development cost. The integrated script engine allows to add application flexibility without interfering with the motor and PFC control algorithm.

Figure 1 Application block diagram

#### **Ordering information**

| Product type  | Control function integrated  | Package      |  |  |

|---------------|------------------------------|--------------|--|--|

| IMD111T-6F040 | iMOTION™ Motor control       | PG-LQFP-40-1 |  |  |

| IMD112T-6F040 | iMOTION™ Motor + PFC control | PG-LQFP-40-1 |  |  |

### **Table of contents**

## **Table of contents**

|       | Features                                        | 1  |

|-------|-------------------------------------------------|----|

|       | Potential applications                          | 1  |

|       | Product validation                              | 1  |

|       | Description                                     | 2  |

|       | Table of contents                               | 3  |

| 1     | Block diagram reference                         | 5  |

| 2     | Pin configuration                               | 6  |

| 2.1   | Pin types and pad structure                     |    |

| 2.2   | Pin definitions and functions                   | 7  |

| 2.3   | Pin configuration drawing IMD111T               | 10 |

| 2.4   | Pin configuration drawing IMD112T               |    |

| 3     | Functional description                          | 12 |

| 3.1   | Overview                                        |    |

| 3.2   | Motion Control Engine                           |    |

| 3.3   | Gate Driver                                     |    |

| 3.4   | Low Side Supply (VCC, VSS and COM)              |    |

| 3.5   | High Side Supplies (VB1,2,3 and VS1,2,3)        |    |

| 3.6   | Low and High Side Outputs (LO1,2,3 and HO1,2,3) |    |

| 3.7   | Internal Voltage Regulator                      |    |

| 3.8   | Application diagrams                            |    |

| 4     | Electrical characteristics and parameters       | 16 |

| 4.1   | General parameters                              |    |

| 4.1.1 | Parameter Interpretation                        | 16 |

| 4.1.2 | Absolute maximum ratings                        | 16 |

| 4.1.3 | Pin Reliability in Overload                     | 17 |

| 4.1.4 | Operating Conditions                            | 19 |

| 4.2   | DC characteristics                              | 20 |

| 4.2.1 | Input/Output Characteristics                    | 20 |

| 4.2.2 | Analog to Digital Converter (ADC)               | 22 |

| 4.2.3 | Analog comparator characteristics               | 22 |

| 4.2.4 | Power Supply Current Controller                 | 23 |

| 4.2.5 | Flash Memory Parameters                         | 23 |

| 4.2.6 | Static parameters gate driver                   | 24 |

| 4.2.7 | Static parameters voltage regulator             | 25 |

| 4.3   | AC characteristics                              | 26 |

| 4.3.1 | Testing Waveforms                               | 26 |

| 4.3.2 | Power-Up and Supply Threshold Characteristics   | 26 |

### **Table of contents**

| 4.3.3 | On-Chip Oscillator Characteristics       | 28 |

|-------|------------------------------------------|----|

| 4.3.4 | Dynamic parameters gate driver           | 29 |

| 4.3.5 | Timing diagrams                          | 30 |

| 4.4   | Motor Control Parameters                 | 31 |

| 4.4.1 | PWM Characteristics                      | 31 |

| 4.4.2 | Current Sensing                          | 31 |

| 4.4.3 | Fault Timing                             | 32 |

| 4.5   | Power Factor Correction (PFC) parameters |    |

| 4.5.1 | Boost PFC characteristics                | 33 |

| 4.5.2 | Totem Pole PFC characteristics           | 33 |

| 4.5.3 | PFC Current Sensing                      | 33 |

| 4.5.4 | PFC Fault Timing                         | 33 |

| 4.6   | Device Interfaces                        | 35 |

| 4.6.1 | UART Interface                           | 35 |

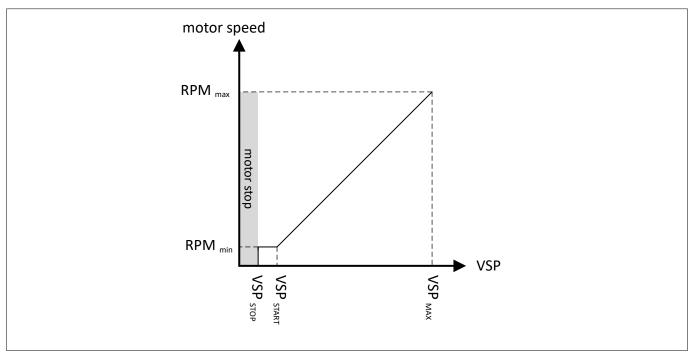

| 4.6.2 | Analog Speed Input                       | 36 |

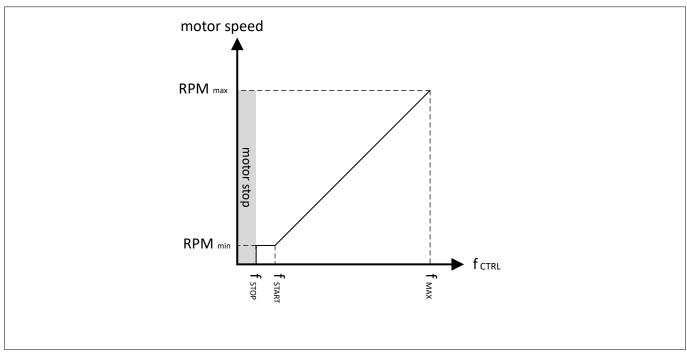

| 4.6.3 | Frequency Input                          | 37 |

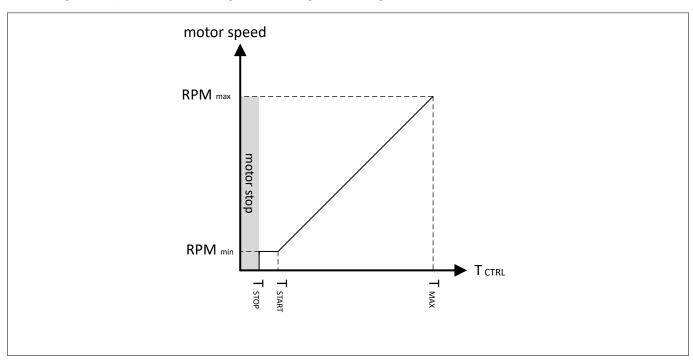

| 4.6.4 | Duty Cycle Input                         | 38 |

| 4.6.5 | Over Temperature Input                   | 39 |

| 4.6.6 | Pulse Output                             | 39 |

| 4.6.7 | LED Output                               | 39 |

| 5     | Device and package specifications        | 40 |

| 5.1   | Quality declaration                      | 40 |

| 5.2   | SBSL and Chip-IDs                        | 40 |

| 5.3   | Thermal considerations                   | 40 |

| 5.4   | Package Outline PG-LQFP-40-1             | 42 |

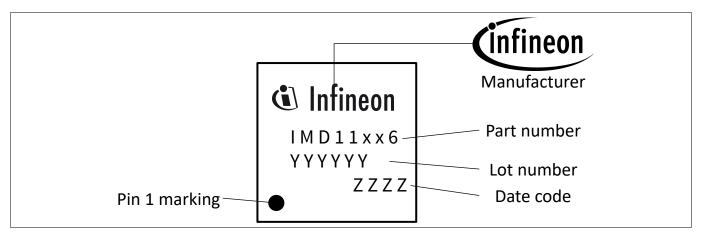

| 5.5   | Part marking information                 | 42 |

|       | Revision history                         | 43 |

|       | Disclaimer                               | 44 |

1 Block diagram reference

#### **Block diagram reference** 1

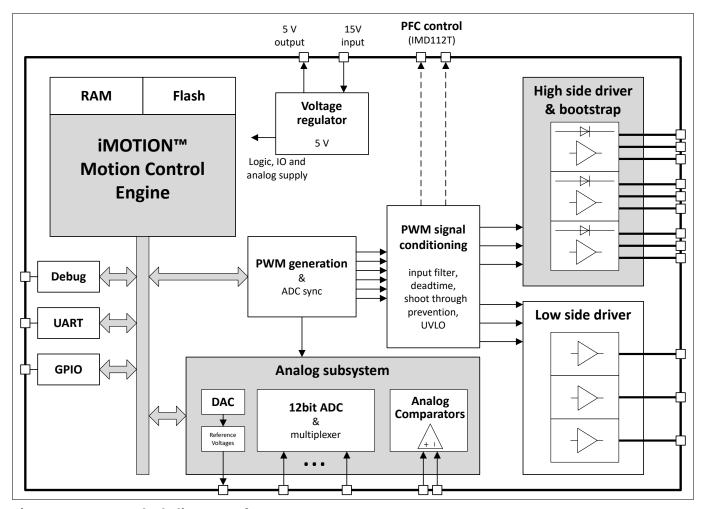

**Block diagram reference** Figure 2

#### 2 Pin configuration

## 2 Pin configuration

### 2.1 Pin types and pad structure

The pin type is specified as follows:

- P power

- I digital input

- O digital output

- IO digital input or output

- AIN analog input

- AO analog output

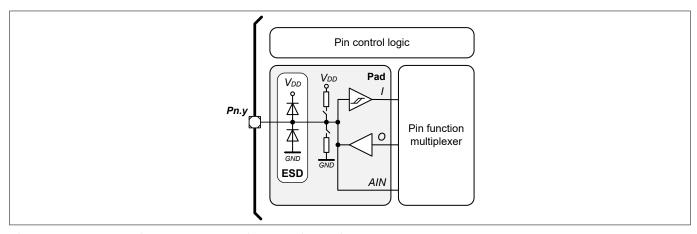

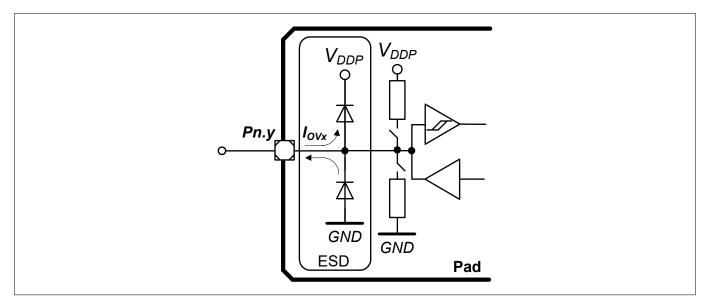

Figure 3 shows the pad structure and pin function control configuration for the input and output pins of the controller integrated.

The pin function, type and pull up/pull down circuit configuration are all controlled by the Motion Control Engine. Digital input, output or analog input signals that are not assigned to MCE functions can be assigned to the script engine. The gate driver outputs are controlled by MCE PWM signals internally connected to the gate driver inputs.

Figure 3 Pin Pad and Function Configuration

The pin function table given below refers to the standard configuration. The pin control or interface functions are defined by the version of software downloaded to the device and may change. Some of the input pins can be configured to have pull up or pull down resistor and some output pins can be configured to push-pull or open drain. This is described in the respective software reference manual.

Pins can serve multiple functions and have to be configured accordingly. Please also refer to the respective pin configuration drawings in this data sheet and the description in the MCE software reference manual.

Pins that do not have any signal assigned are reserved for future use. These pins should be left unconnected and neither be connected to ground nor to the positive supply.

**Note**: All required reference voltages are generated by an internal DAC, therefore the AO pins like IREF, REFU, REFV, and REFW only require a blocking capacitor.

### 2 Pin configuration

### 2.2 Pin definitions and functions

| Table 1 | Pin definitions and functions   |

|---------|---------------------------------|

| Ianic T | Fill delillicions and functions |

| Signal             | Туре   | IMD111T  | IMD112T  | Description                                                                             |  |  |

|--------------------|--------|----------|----------|-----------------------------------------------------------------------------------------|--|--|

| Supply             | '      | ,        | •        |                                                                                         |  |  |

| VCC1               | Power  | 8        | 8        | Control supply voltage input to the voltage regulator                                   |  |  |

| VCC                | Power  | 22       | 22       | Gate drive supply voltage                                                               |  |  |

| VDD                | Power  | 5        | 5        | Digital controller voltage (this 5V LDO output must b blocked with a ceramic capacitor) |  |  |

| VSS                | Power  | 6, 7, 23 | 6, 7, 23 | Ground                                                                                  |  |  |

| Motor contr        | ol     |          |          |                                                                                         |  |  |

| СОМ                | Р      | 9        | 9        | Low side gate driver return                                                             |  |  |

| LO1                | 0      | 12       | 12       | Low side gate driver output - phase 1                                                   |  |  |

| LO2                | 0      | 11       | 11       | Low side gate driver output - phase 2                                                   |  |  |

| LO3                | 0      | 10       | 10       | Low side gate driver output - phase 3                                                   |  |  |

| VS1                | Р      | 19       | 19       | High side gate driver return - phase 1                                                  |  |  |

| H01                | 0      | 20       | 20       | High side gate driver output - phase 1                                                  |  |  |

| VB1                | Р      | 21       | 21       | High side gate driver positive power supply - phase 1                                   |  |  |

| VS2                | Р      | 16       | 16       | High side gate driver return - phase 2                                                  |  |  |

| H02                | 0      | 17       | 17       | High side gate driver output - phase 2                                                  |  |  |

| VB2                | Р      | 18       | 18       | High side gate driver positive power supply - phase 2                                   |  |  |

| VS3                | Р      | 13       | 13       | High side gate driver return - phase 3                                                  |  |  |

| H03                | 0      | 14       | 14       | High side gate driver output - phase 3                                                  |  |  |

| VB3                | Р      | 15       | 15       | High side gate driver positive power supply - phase 3                                   |  |  |

| VDC                | AIN    | 36       | 36       | DC bus sensing input                                                                    |  |  |

| ISS/IU             | AIN    | 40       | 40       | Current sense input single shunt / phase U                                              |  |  |

| IV                 | AIN    | 37       | 37       | Current sense input phase V / analog input                                              |  |  |

| IW                 | AIN    | 33       | 33       | Current sense input phase W / analog input                                              |  |  |

| REFU <sup>1)</sup> | 0      | 39       | 39       | Itrip single shunt/phase U reference DAC output                                         |  |  |

| REFV               | AIN    | 38       | 38       | Itrip phase V reference / analog input                                                  |  |  |

| REFW               | AIN    | 32       | 32       | Itrip phase W reference / analog input                                                  |  |  |

| Hall sensor i      | inputs |          |          |                                                                                         |  |  |

| AHALL1+            | AIN    | 32       | 32       | Analog Hall Element input 1 (+)                                                         |  |  |

| AHALL1-            | AIN    | 33       | 33       | Analog Hall Element input 1 (-)                                                         |  |  |

| AHALL2+            | AIN    | 38       | 38       | Analog Hall Element input 2 (+)                                                         |  |  |

| AHALL2-            | AIN    | 37       | 37       | Analog Hall Element input 2 (-)                                                         |  |  |

| HALL1              | I      | 28       | 28       | Digital Hall sensor input 1                                                             |  |  |

(table continues...)

1.2

This pin must have a filter capacitor connected to ground

## 2 Pin configuration

| Table 1 | continued) Pin definitions and function | nns           |

|---------|-----------------------------------------|---------------|

| Iable I | tontinueu, r in dennitions and idnitiv  | <i>-</i> 1113 |

| Signal Type IMD111T IMD112T |            |    | IMD112T | Description                                        |  |  |  |

|-----------------------------|------------|----|---------|----------------------------------------------------|--|--|--|

| HALL2                       | 1          | 29 | 29      | Digital Hall sensor input 2                        |  |  |  |

| HALL3                       | 1          | 30 | 30      | Digital Hall sensor input 3                        |  |  |  |

| Power factor                | correction |    |         |                                                    |  |  |  |

| PFCG0                       | 0          | -  | 24      | PFC gate drive 0                                   |  |  |  |

| PFCG1                       | 0          | -  | 25      | PFC gate drive 1 (totem-pole PFC only)             |  |  |  |

| IPFC                        | AIN        | -  | 34      | PFC current sensing                                |  |  |  |

| PFCREF                      | AIN        | -  | 3       | PFC Itrip comparator reference input               |  |  |  |

| PFCITRIP                    | AIN        | -  | 4       | PFC Itrip comparator input                         |  |  |  |

| VAC1                        | AIN        | -  | 2       | VAC sense input line 1                             |  |  |  |

| VAC2                        | AIN        | -  | 1       | VAC sense input line 2                             |  |  |  |

| Interface                   |            |    |         |                                                    |  |  |  |

| DUTYFREQ                    | I          | 29 | 29      | Duty/Frequency input                               |  |  |  |

| VSP                         | AIN        | 31 | 31      | Analog speed reference input                       |  |  |  |

| PGOUT                       | 0          | 25 | 25      | Pulse output                                       |  |  |  |

| PARAM                       | AIN        | 34 | -       | Parameter table selection, analog                  |  |  |  |

| NTC                         | AIN        | 35 | 35      | External thermistor input                          |  |  |  |

| DIR                         | I          | 24 | 30      | CW/CCW rotation direction input                    |  |  |  |

| RXD0                        | 1          | 26 | 26      | Serial port 0, device programming, receive input   |  |  |  |

| TXD0                        | 0          | 27 | 27      | Serial port 0, device programming, transmit output |  |  |  |

| RXD1                        | 1          | 1  | -       | Serial port 1, user communication, receive input   |  |  |  |

| TXD1                        | 0          | 2  | -       | Serial port 1, user communication, transmit output |  |  |  |

| Scripting <sup>2)</sup>     |            |    |         |                                                    |  |  |  |

| GPIO1                       | I/O        | 25 | 25      | Digital I/O                                        |  |  |  |

| GPIO2                       | I/O        | 28 | 28      | Digital I/O                                        |  |  |  |

| GPIO3                       | I/O        | 29 | 29      | Digital I/O                                        |  |  |  |

| GPIO4                       | I/O        | 30 | -       | Digital I/O                                        |  |  |  |

| GPIO6                       | I/O        | 24 | 30      | Digital I/O                                        |  |  |  |

| GPI07                       | I/O        | 1  | -       | Digital I/O                                        |  |  |  |

| GPIO8                       | I/O        | 2  | -       | Digital I/O                                        |  |  |  |

| GPIO9                       | I/O        | 3  | -       | Digital I/O                                        |  |  |  |

| GPIO10                      | I/O        | 4  | -       | Digital I/O                                        |  |  |  |

| AIN0                        | AIN        | 31 | 31      | Analog input                                       |  |  |  |

| AIN1                        | AIN        | 32 | 32      | Analog input                                       |  |  |  |

| AIN2                        | AIN        | 33 | 33      | Analog input                                       |  |  |  |

| AIN3                        | AIN        | 34 | -       | Analog input                                       |  |  |  |

(table continues...)

GPIO29 is an internal MCE output connected to the gate driver enable input

## 2 Pin configuration

(continued) Pin definitions and functions Table 1

| Signal | Туре | IMD111T | IMD112T | Description                |  |  |

|--------|------|---------|---------|----------------------------|--|--|

| AIN4   | AIN  | 35      | 35      | Analog input               |  |  |

| AIN7   | AIN  | 38      | 38      | Analog input               |  |  |

| AIN10  | AIN  | 1       | -       | Analog input               |  |  |

| AIN11  | AIN  | 2       | -       | Analog input               |  |  |

| TRIN0  | I    | 25      | 25      | TRIAC control input        |  |  |

| TRIN1  | I    | 34      | -       | TRIAC control input        |  |  |

| TROUT0 | 0    | 4       | -       | TRIAC control output       |  |  |

| TROUT1 | 0    | 30      | 30      | TRIAC control output       |  |  |

| SCL    | 0    | 26      | 26      | I2C interface serial clock |  |  |

| SDA    | I/O  | 27      | 27      | I2C interface serial data  |  |  |

| IR0    | I    | 26      | 26      | IR interface               |  |  |

| IR1    | 1    | 1       | -       | IR interface               |  |  |

| IR2    | I    | 31      | 31      | IR interface               |  |  |

#### 2 Pin configuration

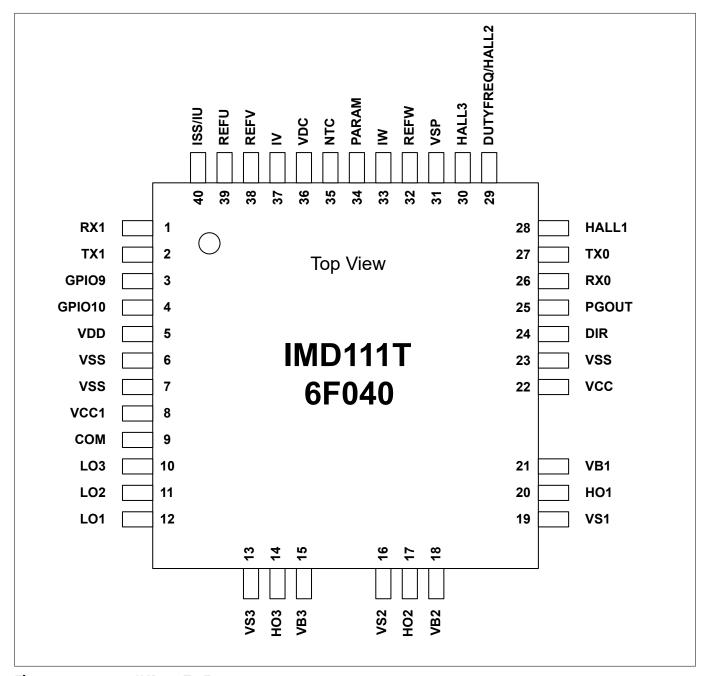

## 2.3 Pin configuration drawing IMD111T

The drawings give the position of the functional pins for the available packages. Only the primary function of the respective pin is shown. Depending on the version of the Motion Control Engine (MCE) used pins might provide additional functionality which is given in the respective pin configuration tables.

Figure 4 IMD111T-6F040

Pins that do not have any signal assigned are reserved for future use. Unused pins should be left unconnected and neither be connected to ground nor to the positive supply.

#### 2 Pin configuration

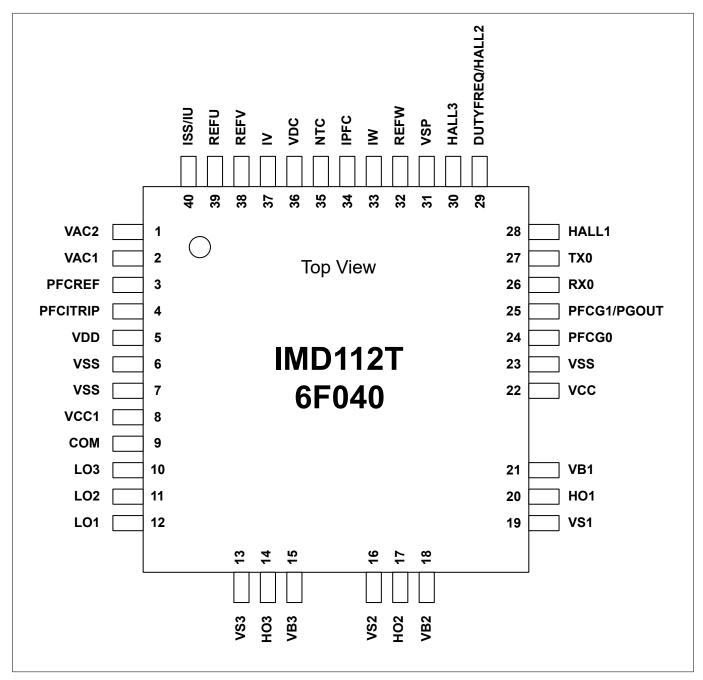

## 2.4 Pin configuration drawing IMD112T

The drawings give the position of the functional pins for the available packages. Only the primary function of the respective pin is shown. Depending on the version of the Motion Control Engine (MCE) used pins might provide additional functionality which is given in the respective pin configuration tables.

Figure 5 IMD112T-6F040

Pins that do not have any signal assigned are reserved for future use. Unused pins should be left unconnected and neither be connected to ground nor to the positive supply.

#### 3 Functional description

## 3 Functional description

#### 3.1 Overview

The IMD111T/IMD112T integrates a controller, a high-voltage three-phase gate driver and a voltage regulator in a single package. The controller PWM outputs are internally connected to the gate driver inputs. Two controller digital pins are also connected to the gate driver enable input and fault output of the gate driver.

The integrated voltage regulator generates the controller 5V supply and can share the same 15V supply rail as the gate driver.

The package PG-LQFP-40-1 is footprint compatible to an industry standard LQFP-48 with pins removed for improved clearance and creepage.

### 3.2 Motion Control Engine

iMOTION™ IMD111T/IMD112T use the latest generation of the Motion Control Engine (MCE). The MCE is a ready-to-use solution for variable speed drives and contains all control functions to perform closed loop control of a three phase motor. Optionally, control of a power factor correction (PFC) is provided running in parallel to the motor.

Multiple configurable protections like over- and under-voltage, over current or rotor lock are integrated protecting the power stage as well as the motor itself.

iMOTION™ IMD111T/IMD112T supports the use in applications requiring functional safety according to IEC/UL 60730-1 ('Class B')

Using the MCE does not require any software development. Instead the MCE is configured for the concrete power stage configuration and motor type using PC based tools. Following parameter creation the behavior of the motor control loop can be monitored and fine tuned in real time. The respective tools are available for download from the iMOTION™ web pages.

For improved application flexibility the MCE contains a scripting engine running user scripts in the background task. Writing, downloading and monitoring scripts is supported by the above mentioned tools.

The MCE is driven by an internal temperature compensated oscillator that supports peripheral operation at 96 MHz and data processing at 48 MHz.

This data sheet provides all electrical, mechanical, thermal and quality parameters of the IMD111T/IMD112T. A more detailed description of the features and functionality of the MCE can be found in the respective reference manual. The MCE software images are made available for download from the Infineon web site. A special secure boot algorithm assures that these MCE software images can only be installed onto the matching hardware derivative, i.e. the product variant for which the software has been tested for.

#### 3 Functional description

#### 3.3 **Gate Driver**

The integrated gate driver provides three high side and three low side drivers to control power devices like MOS-transistors or IGBTs in 3-phase systems such as variable speed drives. The gate drivers are based on SOItechnology which provides excellent ruggedness to transient voltages. The devices do not have parasitic thyristor structures so parasitic latch-up does not occur for any temperature or voltage condition.

The six independent drivers are controlled from the MCE PWM generator though internal connections. The device includes an under-voltage detection unit that monitors the driver voltage supplies. An under-voltage condition causes the driver to shut off all six switches. The error signal provided by the driver is internally connected to the MCE controller GK input pin to trip the MCE PWM generator. The gate driver enable input EN is internally connected to the MCE which allows the SW to manage the device power up sequencing.

The typical output currents can be up to 165 mA for pull-up and 375 mA for pull down. The MCE PWM generator introduces a deadtime between the high and low side signals but the gate driver introduces a fail safe 310 ns minimum dead time. The monolithic integrated bootstrap diode structures between pins VCC and VBx can be used to create the power supply for the high side circuits.

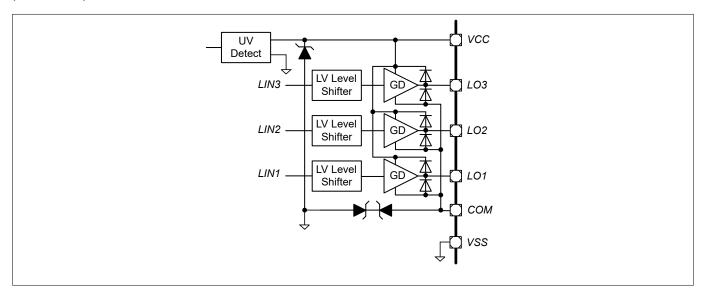

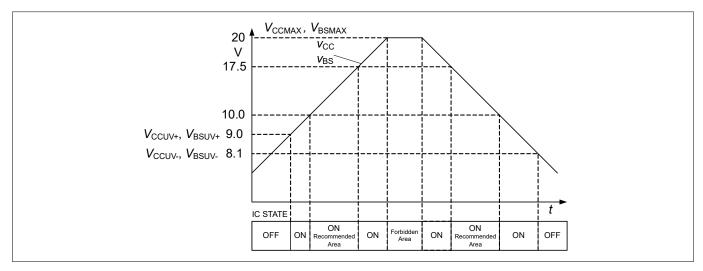

#### 3.4 Low Side Supply (VCC, VSS and COM)

In the figure below, VCC is the low side supply for the gate driver which powers both the input logic and the low side output power stage. The under-voltage detection circuit Input logic is referenced to VSS ground. Output power stage is referenced to COM ground. COM ground is floating respect to VSS ground with a maximum range of operation of +/-5.7 V. A back-to-back zener structure protects grounds from noise spikes.

The under-voltage circuit enables the device to operate when the VCC supply voltage is higher than V<sub>CCUV+</sub> . The IC shuts down all the gate drivers power outputs, when the VCC supply voltage is below V<sub>CCUV</sub>. This prevents the external power switches from critically low gate voltage levels during on-state and therefore from excessive power dissipation.

**Low Side Driver circuit** Figure 6

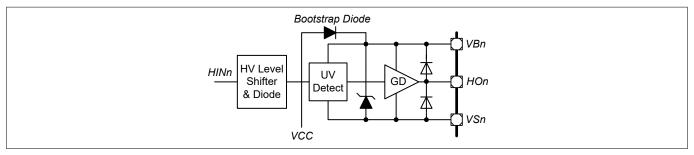

#### 3.5 High Side Supplies (VB1,2,3 and VS1,2,3)

Figure 7 shows the high side gate driver output circuit. VB to VS is the supply voltage supply for the high side gate driver. Each of the three high side circuits can float with respect to VSS following the external high side power device emitter/source voltage. The floating driver stage can be supplied by bootstrap topology using the internal diode connected between VB and VCC.

The device operating area as a function of the supply voltage is given in the Timing diagrams section under AC characteristics.

#### 3 Functional description

Figure 7 High Side Driver circuit

### 3.6 Low and High Side Outputs (LO1,2,3 and HO1,2,3)

Low side and high side power outputs are specifically designed for pulse operation such as gate drive of IGBT and MOSFET devices. Low side outputs (i.e. LO1,2,3) are state triggered by the respective inputs, while high side outputs (i.e. HO1,2,3) are edge triggered by the respective inputs. In particular, after an under voltage condition of the VBS supply, a new turn-on signal (edge) is necessary to activate the respective high side output, while after a under voltage condition of the VCC supply, the low side outputs switch to the state of their respective inputs.

## 3.7 Internal Voltage Regulator

The IMD111T/IMD112T contains a linear voltage regulator that can be used to generate the controller supply voltage from the gate driver supply. The regulator can also supply external components like sensors. The maximum current capability must be respected.

In order to maintain the stability of the control loop the regulator output requires an output capacitor CQ of at least 3.3  $\mu$ F with a maximum permissible ESR of 2  $\Omega$ . It is recommended to use a multi layer ceramic capacitor for CQ with a nominal capacitance of 4.7  $\mu$ F. Aluminum electrolytic as well as tantalum capacitors do not cover the required ESR range over the full operating temperature range. At the input of the regulator an input capacitor is necessary for compensating line influences (100 nF ceramic capacitor recommended). A resistor of approx. 1  $\Omega$  in series with CI can dampen oscillations that could occur due to the input inductivity and the input capacitor. If the regulator is sourced via long input lines of several meters it is recommended to place an additional electrolytic capacitor  $\geq$  47  $\mu$ F at the input.

In case the integrated controller is supplied from an external source, the internal regulator can be disabled by connecting the respective input to ground.

### **3 Functional description**

## 3.8 Application diagrams

Figure 8 Application diagram single shunt

4 Electrical characteristics and parameters

## 4 Electrical characteristics and parameters

### 4.1 General parameters

### 4.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the IMD111T/IMD112T and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

#### CC

Such parameters indicate **C**ontroller **C**haracteristics, which are distinctive feature of the IMD111T/IMD112T and must be regarded for a system design.

#### SR

Such parameters indicate **S**ystem **R**equirements, which must be provided by the application system in which the IMD111T/IMD112T is designed in.

## 4.1.2 Absolute maximum ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Table 2 Absolute maximum ratings

| Parameter                                                               | Symbol              | V    | Values               |    | Note or Test Condition         |

|-------------------------------------------------------------------------|---------------------|------|----------------------|----|--------------------------------|

|                                                                         |                     | Min. | Max.                 |    |                                |

| Ambient temperature                                                     | T <sub>A</sub> SR   | -40  | 105                  | °C |                                |

| Junction temperature                                                    | $T_{J}SR$           | -40  | 115                  | °C | Digital controller             |

|                                                                         |                     | -40  | 125                  | °C | Gate driver, power transistors |

| Storage temperature                                                     | T <sub>ST</sub> SR  | -40  | 125                  | °C |                                |

| Lead temperature (soldering, 30 seconds)                                | T <sub>L</sub> SR   |      | 260                  | °C |                                |

| Control supply voltage                                                  | V <sub>CC1</sub> SR | -42  | 45                   | V  |                                |

| Digital Controller voltage                                              | V <sub>DD</sub> SR  | -0.3 | 6                    | V  |                                |

| Controller digital and analog pin voltage                               | V <sub>ID</sub> SR  | -0.3 | V <sub>DD</sub> +0.3 | V  |                                |

| Input current on any controller pin during overload condition           | I <sub>IN</sub> SR  | -10  | 10                   | mA |                                |

| Absolute sum of all controller input currents during overload condition | $\Sigma I_{IN}$ SR  | -50  | 50                   | mA |                                |

(table continues...)

#### 4 Electrical characteristics and parameters

Table 2 (continued) Absolute maximum ratings

| Parameter                                                                       | Symbol                 | Values                                |                        | Unit | Note or Test Condition                                                     |  |

|---------------------------------------------------------------------------------|------------------------|---------------------------------------|------------------------|------|----------------------------------------------------------------------------|--|

|                                                                                 |                        | Min.                                  | Max.                   |      |                                                                            |  |

| High side return offset voltage <sup>3)</sup>                                   | V <sub>S</sub> SR      | V <sub>CC</sub> -V <sub>BS</sub> -6   | 600                    | V    | Voltage on high side<br>gate driver return pins<br>relative to the COM pin |  |

| High side return offset voltage (t <sub>p</sub> < 500 ns, <sup>3)</sup> )       | V <sub>S</sub> SR      | V <sub>CC</sub> -V <sub>BS</sub> - 50 |                        | V    |                                                                            |  |

| High side supply offset voltage <sup>3)</sup>                                   | V <sub>B</sub> SR      | V <sub>CC</sub> – 6                   | 620                    | V    | Voltage on high side<br>gate driver supply pins<br>relative to the COM pin |  |

| High side supply offset voltage $(t_p < 500 \text{ ns}, \frac{3}{})$            | V <sub>B</sub> SR      | V <sub>CC</sub> – 50                  |                        | V    |                                                                            |  |

| High side floating supply voltage $(V_B \text{ vs. } V_S)$ (internally clamped) | V <sub>BS</sub> SR     | -1                                    | 20                     | V    |                                                                            |  |

| High side output voltage ( $V_{HO}$ vs. $V_{S}$ )                               | V <sub>HO</sub> SR     | -0.5                                  | V <sub>B</sub> + 0.5   | V    |                                                                            |  |

| Gate drive low side supply voltage (internally clamped)                         | V <sub>CC</sub> SR     | -1                                    | 20                     | V    |                                                                            |  |

| Low side supply voltage ( $_{VCC}$ vs. $V_{COM}$ )                              | V <sub>CCCOM</sub> SR  | -0.5                                  | 25                     | V    |                                                                            |  |

| Gate driver ground                                                              | V <sub>COM</sub> SR    | -5.7                                  | 5.7                    | V    | relative to V <sub>SS</sub>                                                |  |

| Low side output voltage ( $V_{LO}$ vs. $V_{COM}$ )                              | V <sub>LO</sub> SR     | -0.5                                  | V <sub>COM</sub> + 0.5 | V    |                                                                            |  |

| Offset voltage slew rate <sup>4)</sup>                                          | dV <sub>S</sub> /dt CC | _                                     | 50                     | V/ns |                                                                            |  |

**Note**: Characterized, not tested at manufacturing.

**Note**: Voltages referenced to  $V_{SS}$  if not stated otherwise

## 4.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

The table below defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels  $(V_{DD})$

- temperature

In case V<sub>CC</sub> > V<sub>B</sub> there is an additional power dissipation in the internal bootstrap diode between pins VCC and VBx. Insensitivity of bridge output to negative transient voltage up to -50V is not subject to production test - verified by design / characterization.

Not subject of production test, verified by characterization

#### 4 Electrical characteristics and parameters

If a pin current is outside of the Operating Conditions but within the overload conditions, then the parameters of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

**Note**: An overload condition on one or more pins does not require a reset.

**Note**: A series resistor at the pin to limit the current to the maximum permitted overload current is sufficient

to handle failure situations like short to battery.

Table 3 Overload Parameters

| Parameter                                                    | Symbol Values       |      |      | Unit | Note or Test Condition |  |

|--------------------------------------------------------------|---------------------|------|------|------|------------------------|--|

|                                                              |                     | Min. | Тур. | Max. |                        |  |

| Input current on analog port pins during overload condition  | I <sub>OVA</sub> SR | -3   | _    | 3    | mA                     |  |

| Input current on any port pin during overload condition      | I <sub>OV</sub> SR  | -5   | -    | 5    | mA                     |  |

| Absolute sum of all input currents during overload condition | I <sub>OVS</sub> SR | -    | _    | 25   | mA                     |  |

Figure 9 shows the path of the input currents during overload via the ESD protection structures. The diodes against  $V_{\rm DD}$  and ground are a simplified representation of these ESD protection structures.

Figure 9 Input Overload Current via ESD structures

Table 4 and Table 5 list input voltages that can be reached under overload conditions. Note that the absolute maximum input voltages as defined in the Absolute maximum ratings must not be exceeded during overload.

### 4 Electrical characteristics and parameters

Table 4 PN-Junction Characterisitics for positive Overload

| Pad Type                | I <sub>OV</sub> = 5 mA                                |

|-------------------------|-------------------------------------------------------|

| Standard, High-current, | $V_{\rm IN} = V_{\rm DD} + (0.3 \dots 0.5) \text{ V}$ |

| AN/DIG_IN               | $V_{AIN} = V_{DD} + 0.5 \text{ V}$                    |

|                         | $V_{AREF} = V_{DD} + 0.5 \text{ V}$                   |

### Table 5 PN-Junction Characterisitics for negative Overload

| Pad Type                | I <sub>OV</sub> = 5 mA                        |

|-------------------------|-----------------------------------------------|

| Standard, High-current, | $V_{IN} = V_{SS} - (0.3 \dots 0.5) \text{ V}$ |

| AN/DIG_IN               | $V_{AIN} = V_{SS} - 0.5 \text{ V}$            |

|                         | $V_{AREF} = V_{SS} - 0.5 V$                   |

## 4.1.4 Operating Conditions

The following operating conditions must not be exceeded in order to ensure correct operation and reliability of the IMD111T/IMD112T. All parameters specified in the following tables refer to these operating conditions, unless noted otherwise.

Table 6Recommended Operating Conditions

| Parameter                                        | Symbol                 |                    | Values |                     | Unit | Note or Test Condition              |

|--------------------------------------------------|------------------------|--------------------|--------|---------------------|------|-------------------------------------|

|                                                  |                        | Min.               | Тур.   | Max.                |      |                                     |

| Ambient Temperature                              | T <sub>A</sub> SR      | -40                | _      | 105                 | °C   |                                     |

| Junction temperature                             | T <sub>J</sub> SR      | -40                | _      | 115                 | °C   |                                     |

| Positive DC Bus Input Voltage                    | V <sub>DCP</sub> SR    | 12                 | -      | 400                 | V    |                                     |

| Gate Driver High Side Floating<br>Supply Voltage | V <sub>B1,2,3</sub> SR | V <sub>S</sub> + 5 | -      | V <sub>S</sub> + 18 | V    |                                     |

| Gate Driver Low Side Supply<br>Voltage           | V <sub>CC</sub> SR     | 12                 | -      | 16.5                | V    |                                     |

| Digital supply voltage <sup>5)</sup>             | V <sub>DD</sub> SR     | 3.0                | 3.3    | 5.5                 | V    | Internal voltage regulator disabled |

| Voltage regulator input voltage                  | V <sub>CC1</sub> SR    | 5.5                | -      | 20                  | V    |                                     |

All supply pins must be driven with the same voltage.

### 4 Electrical characteristics and parameters

### 4.2 DC characteristics

### 4.2.1 Input/Output Characteristics

The table below provides the characteristics of the input/output pins of the controller.

**Note**: These parameters are not subject to production test, but verified by design and/or characterization.

**Note**: Unless otherwise stated, input DC and AC characteristics, including peripheral timings, assume that

the input pads operate with the standard hysteresis.

Table 7 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                                     | Symbol            |    | Limit Valu             | es                     | Unit | Test Conditions                                                                      |

|-------------------------------------------------------------------------------|-------------------|----|------------------------|------------------------|------|--------------------------------------------------------------------------------------|

|                                                                               |                   |    | Min.                   | Max.                   |      |                                                                                      |

| Input low voltage on port pins<br>(Standard Hysteresis)                       | V <sub>ILPS</sub> | SR | -                      | 0.19 × V <sub>DD</sub> | V    | CMOS Mode                                                                            |

| Input high voltage on port pins<br>(Standard Hysteresis)                      | V <sub>IHPS</sub> | SR | 0.7 × V <sub>DD</sub>  | _                      | V    | CMOS Mode                                                                            |

| Input low voltage on port pins<br>(Large Hysteresis, scripting pins<br>only)  | V <sub>ILPL</sub> | SR | -                      | 0.08 × V <sub>DD</sub> | V    | CMOS Mode                                                                            |

| Input high voltage on port pins<br>(Large Hysteresis, scripting pins<br>only) | V <sub>IHPL</sub> | SR | 0.85 × V <sub>DD</sub> | -                      | V    | CMOS Mode                                                                            |

| Output low voltage on port pins                                               | V <sub>OLP</sub>  | CC | -                      | 1.0                    | V    | I <sub>OL</sub> = 11 mA ( V)<br>I <sub>OL</sub> = 7 mA (3.3 V)                       |

|                                                                               |                   |    | -                      | 0.4                    | V    | $I_{OL} = 5 \text{ mA } (5 \text{ V})$<br>$I_{OL} = 3.5 \text{ mA } (3.3 \text{ V})$ |

| Output high voltage on port pins                                              | V <sub>OHP</sub>  | CC | V <sub>DD</sub> - 1.0  | _                      | V    | $I_{OH} = -10 \text{ mA (5 V)}$<br>$I_{OH} = -7 \text{ mA (3.3 V)}$                  |

|                                                                               |                   |    | V <sub>DD</sub> - 0.4  | _                      | V    | $I_{OH}$ = -4.5 mA (5 V)<br>$I_{OH}$ = -2.5 mA (3.3 V)                               |

| Rise/fall time on standard pad                                                | $t_{R}, t_{F}$    | CC | -                      | 12                     | ns   | 50 pF @ 5 V                                                                          |

|                                                                               |                   |    | -                      | 15                     | ns   | 50 pF @ 3.3 V.                                                                       |

| Pin capacitance<br>(digital inputs/outputs)                                   | C <sub>IO</sub>   | CC | -                      | 10                     | pF   |                                                                                      |

| Pull-up/-down resistor on port<br>pins<br>(if enabled in software)            | R <sub>PUP</sub>  | CC | 20                     | 50                     | kΩ   | $V_{IN} = V_{SS}$                                                                    |

(table continues...)

### **4** Electrical characteristics and parameters

### Table 7 (continued) Input/Output Characteristics (Operating Conditions apply)

| Parameter                                               | Symbol                                | Symbol |      | Limit Values |    | <b>Test Conditions</b>                       |

|---------------------------------------------------------|---------------------------------------|--------|------|--------------|----|----------------------------------------------|

|                                                         |                                       |        | Min. | Max.         |    |                                              |

| Input leakage current <sup>6)</sup>                     | I <sub>OZP</sub>                      | CC     | -1   | 1            | μΑ | $0 < V_{IN} < V_{DD},$<br>$T_A 105^{\circ}C$ |

| Maximum current per pin standard pin                    | I <sub>MP</sub>                       | SR     | -10  | 11           | mA | -                                            |

| Maximum current into $V_{\rm DD}$ / out of $V_{\rm SS}$ | I <sub>MVDD</sub> / I <sub>MVSS</sub> | SR     | -    | 260          | mA |                                              |

An additional error current (I<sub>INJ</sub>) will flow if an overload current flows through an adjacent pin.

#### 4 Electrical characteristics and parameters

### 4.2.2 Analog to Digital Converter (ADC)

The following table shows the Analog to Digital Converter (ADC) characteristics. This specification applies to all analog input including the analog Hall sensor interface input (AHALLx+/AHALLx-, where x=1,2) as given in the pin configuration list.

**Note**: These parameters are not subject to production test, but verified by design and/or characterization.

Table 8 ADC Characteristics (Operating Conditions apply)<sup>7)</sup>

| Parameter                                | Symbol                   |                        | Values | ;                      | Unit  | Note or Test<br>Condition |

|------------------------------------------|--------------------------|------------------------|--------|------------------------|-------|---------------------------|

|                                          |                          | Min.                   | Тур.   | Max.                   |       |                           |

| Supply voltage range                     | $V_{\rm DD}{\rm SR}$     | 3.0                    | _      | 5.5                    | V     |                           |

| Analog input voltage range               | V <sub>AIN</sub> SR      | V <sub>SS</sub> - 0.05 | _      | V <sub>DD</sub> + 0.05 | V     |                           |

| Conversion time                          | t <sub>C12</sub> CC      | _                      | 1.0    | -                      | μs    | Defined by SW             |

| Total capacitance of an analog input     | C <sub>AINT</sub> CC     | _                      | _      | 10                     | pF    |                           |

| Total capacitance of the reference input | C <sub>AREFT</sub>       | _                      | _      | 10                     | pF    |                           |

| Sample time                              | t <sub>sample</sub>      | _                      | 333    | -                      | ns    | Defined by SW             |

| RMS noise                                | EN <sub>RMS</sub><br>CC  | _                      | 1.5    | -                      | LSB12 |                           |

| DNL error                                | EA <sub>DNL</sub> CC     | _                      | ±2.0   | _                      | LSB12 |                           |

| INL error                                | EA <sub>INL</sub> CC     | _                      | ±4.0   | _                      | LSB12 |                           |

| Gain error                               | EA <sub>GAIN</sub><br>CC | _                      | ±0.5   | -                      | %     |                           |

| Offset error                             | EA <sub>OFF</sub> CC     | _                      | ±8.0   | _                      | mV    |                           |

## 4.2.3 Analog comparator characteristics

The table below shows the Analog Comparator characteristics.

**Note**: These parameters are not subject to production test, but verified by design and/or characterization.

Table 9 Analog Comparator Characteristics (Operating Conditions apply)

| Parameter        | Symbol           | Symbol |       |       |                         | Unit | Note or                                              |  |

|------------------|------------------|--------|-------|-------|-------------------------|------|------------------------------------------------------|--|

|                  |                  |        | Min.  | Тур.  | Max.                    |      | <b>Test Conditions</b>                               |  |

| Input Voltage    | $V_{CMP}$        | SR     | -0.05 | -     | V <sub>DDP</sub> + 0.05 | V    | includes common mode and differential input voltages |  |

| Input Offset     | $V_{CMPOFF}$     | СС     | _     | +/-3  | _                       | mV   | High power mode $\Delta V_{\rm CMP}$ < 200 mV        |  |

| Input Hysteresis | V <sub>HYS</sub> | CC     | _     | +/-15 | _                       | mV   | Defined by SW                                        |  |

All parameters are defined for the full supply range if not stated otherwise.

#### 4 Electrical characteristics and parameters

## 4.2.4 Power Supply Current Controller

The total power supply current defined below consists of a leakage and a switching component for the voltage regulator and the controller through the  $V_{CC1}$  pin. The  $V_{CC}$  supply current is listed under the gate driver parameters.

Application relevant values are typically lower than those given in the following tables, and depend on the customer's system operating conditions (e.g. thermal connection or used application configurations).

**Note**: These parameters are not subject to production test, but verified by design and/or characterization.

Table 10 Power supply parameter table;  $V_{CC1} = 15V$

| Parameter                                  | Symbol              |      | Values |      | Unit | Note or Test Condition |

|--------------------------------------------|---------------------|------|--------|------|------|------------------------|

|                                            |                     | Min. | Тур.   | Max. |      |                        |

| Active mode current motor control only     | I <sub>DD1</sub> CC | _    | 12     | 20   | mA   | T <sub>a</sub> = 25°C  |

| Active mode current motor control plus PFC | I <sub>DD2</sub> CC | _    | 16     | 20   | mA   | T <sub>a</sub> = 25°C  |

### 4.2.5 Flash Memory Parameters

**Note**: These parameters are not subject to production test, but verified by design and/or characterization.

Table 11 Flash Memory Parameters

| Parameter           | Symbol               |      | Values |                   | Unit   | Note or Test Condition                          |

|---------------------|----------------------|------|--------|-------------------|--------|-------------------------------------------------|

|                     |                      | Min. | Тур.   | Max.              |        |                                                 |

| Data Retention Time | $t_{RET}CC$          | 10   |        |                   | years  | Max. 100 erase / program cycles                 |

| Erase Cycles        | N <sub>ECYC</sub> CC |      |        | 5*10 <sup>4</sup> | cycles | Sum of page and sector erase cycles a page sees |

| Total Erase Cycles  | N <sub>TECYC</sub>   |      |        | 2*10 <sup>6</sup> | cycles |                                                 |

### 4 Electrical characteristics and parameters

## 4.2.6 Static parameters gate driver

**Note**:  $V_{CC} = V_{BS} = 15V$  unless otherwise specified. All parameters valid for  $T_a = 25$  °C

### Table 12 Static parameter

| Parameter                                                                               | Symbol                                     |      | Values                    |      | Unit | Note or Test Condition                                  |

|-----------------------------------------------------------------------------------------|--------------------------------------------|------|---------------------------|------|------|---------------------------------------------------------|

|                                                                                         |                                            | Min. | Тур.                      | Max. |      |                                                         |

| High level output voltage,<br>LO1,2,3                                                   | V <sub>OH</sub>                            | _    | V <sub>CC</sub> -0.7      |      | V    | I <sub>O</sub> = 20mA                                   |

| High level output voltage,<br>HO1,2,3                                                   |                                            |      | V <sub>B</sub> -0.7       |      | V    | I <sub>O</sub> = 20mA                                   |

| Low level output voltage ,<br>LO1,2,3                                                   | V <sub>OL</sub>                            | _    | V <sub>COM</sub> +<br>0.2 |      | V    | I <sub>O</sub> = -20mA                                  |

| Low level output voltage ,<br>HO1,2,3                                                   | V <sub>OL</sub>                            | _    | V <sub>S</sub> + 0.2      |      | V    | I <sub>O</sub> = -20mA                                  |

| V <sub>CC</sub> and V <sub>BS</sub> supply<br>undervoltage positive going<br>threshold  | V <sub>CCUV</sub> +<br>V <sub>BSUV</sub> + | 8.3  | 9                         | 9.8  | V    | -                                                       |

| V <sub>CC</sub> and V <sub>BS</sub> supply<br>undervoltage negative going<br>threshold  | V <sub>CCUV</sub> -                        | 7.5  | 8.1                       | 8.8  | V    | -                                                       |

| V <sub>CC</sub> and V <sub>BS</sub> supply<br>undervoltage lockout<br>hysteresis        | V <sub>CCUVH</sub><br>V <sub>BSUVH</sub>   | 0.5  | 0.9                       |      | V    | V <sub>S</sub> = 600V                                   |

| High side leakage current<br>betw. VS and VSS                                           | I <sub>LVS+</sub>                          | -    | 1                         | 12.5 | μΑ   | V <sub>S</sub> = 600V                                   |

| High side leakage current<br>betw. VS and VSS <sup>8)</sup>                             | I <sub>LVS+</sub>                          |      | 10                        | _    | μΑ   | $T_J = 125  {}^{\circ}\text{C}, V_S = 600V$             |

| High side leakage current<br>between VSx and VSy (x=1,2,3<br>and y=1,2,3)               | I <sub>LVS</sub> -                         | -    | 10                        | _    | μА   | $T_J = 125  {}^{\circ}\text{C}, V_{Sx} - V_{Sy} = 600V$ |

| Quiescent current V <sub>BS</sub> supply<br>(VB only)                                   | I <sub>QBS</sub>                           | _    | 210                       | 400  | μΑ   | -                                                       |

| Quiescent current V <sub>CC</sub> supply<br>(VCC only)                                  | I <sub>QCC</sub>                           | -    | 0.75                      | 1.5  | mA   |                                                         |

| Mean output current for load capacity charging in range from 3 V (20%) to 6 V (40%)     | I <sub>O+</sub>                            | 120  | 165                       | -    | mA   | C <sub>L</sub> =10 nF                                   |

| Peak output current turn on (single pulse) <sup>8)</sup>                                | I <sub>Opk+</sub>                          | -    | 240                       | _    | mA   | $R_L = 0 \Omega, t_p < 10 \mu s$                        |

| Mean output current for load capacity discharging in range from 12 V (80%) to 9 V (60%) | I <sub>O-</sub>                            | 250  | 375                       | -    | mA   | C <sub>L</sub> =10 nF                                   |

| Peak output current turn off (single pulse) 8)                                          | I <sub>Opk-</sub>                          | -    | 420                       |      | mA   | $R_L = 0 \Omega, t_p < 10 \mu s$                        |

(table continues...)

1.2

Not subject of production test, verified by characterization

### **4** Electrical characteristics and parameters

Table 12 (continued) Static parameter

| Parameter                                          | Symbol Values      |      |      | Unit | Note or Test Condition |                                            |

|----------------------------------------------------|--------------------|------|------|------|------------------------|--------------------------------------------|

|                                                    |                    | Min. | Тур. | Max. |                        |                                            |

| Bootstrap diode forward voltage between VCC and VB | $V_{F,BSD}$        | -    | 1.0  | 1.3  | V                      | I <sub>F</sub> =0.5 mA                     |

| Bootstrap diode forward current between VCC and VB | I <sub>F,BSD</sub> | -    | 50   | -    | mA                     | V <sub>F</sub> =4 V                        |

| Bootstrap diode resistance                         | R <sub>BSD</sub>   | 24   | 40   | 60   | Ω                      | V <sub>F1</sub> =4 V, V <sub>F2</sub> =5 V |

## **4.2.7** Static parameters voltage regulator

Table 13 Static parameters

| Parameter                     | Symbol            |      | Values |      | Unit | Note or Test Condition                                    |

|-------------------------------|-------------------|------|--------|------|------|-----------------------------------------------------------|

|                               |                   | Min. | Тур.   | Max. |      |                                                           |

| Input Voltage                 | V <sub>CC1</sub>  | 5.5  |        | 20   | V    |                                                           |

| Output Voltage                | $V_{\mathrm{Q}}$  | 4.80 | 5.00   | 5.20 | V    | 1 mA ≤ I <sub>Q</sub> ≤ 30 mA                             |

| Output Current Limitation     | $I_{QExt}$        |      |        | 10   | mA   | Total regulator output for external devices               |

| Dropout Voltage <sup>9)</sup> | V <sub>dr</sub>   | -    | 250    | 300  | mV   | I <sub>Q</sub> = 20 mA                                    |

| Output capacitor              | $C_{Q}$           | 3.3  | -      | -    | μF   | ESR≤2Ω at 10 kHz                                          |

| Load Regulation               | $\Delta V_{ m Q}$ | -    | 17     | 50   | mV   | 1 mA < $I_Q$ < 25 mA;<br>$T_j$ = 25°C;                    |

| Line Regulation               | $\Delta V_{ m Q}$ | -    | 10     | 25   | mV   | V <sub>I</sub> = (V <sub>Q,nom</sub> + 0.5 V)<br>to 36 V; |

|                               |                   |      |        |      |      | $I_{Q} = 1 \text{ mA}; T_{j} = 25^{\circ}\text{C}$        |

| Power Supply Ripple Rejection | PSRR              | -    | 60     | -    | dB   | $f_{\rm r} = 100 \text{ kHz};$                            |

|                               |                   |      |        |      |      | $V_{\rm r} = 0.5  \rm Vpp$                                |

1.2

Measured when the output voltage VQ has dropped 100 mV from the nominal value.

#### 4 Electrical characteristics and parameters

### 4.3 AC characteristics

## 4.3.1 Testing Waveforms

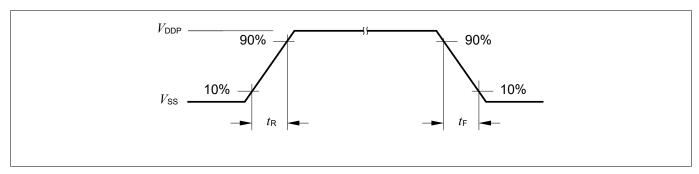

Figure 10 Rise/Fall Time Parameters

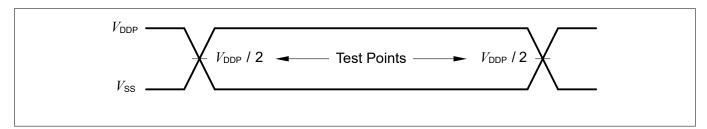

Figure 11 Testing Waveform, Output Delay

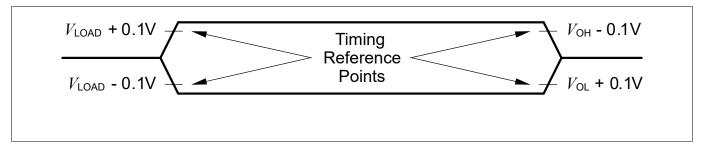

Figure 12 Testing Waveform, Output High Impedance

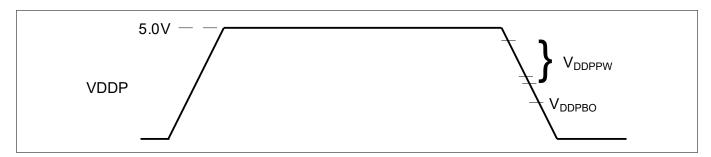

### 4.3.2 Power-Up and Supply Threshold Characteristics

This chapter provides the characteristics of the supply threshold for the controller.

The guard band between the lowest valid operating voltage and the brownout reset threshold provides a margin for noise immunity and hysteresis. The electrical parameters may be violated while  $V_{\rm DD}$  is outside its operating range.

The brownout detection triggers a reset within the defined range. The prewarning detection can be used to trigger an early warning and issue corrective and/or fail-safe actions in case of a critical supply voltage drop.

**Note**: These parameters are not subject to production test, but verified by design and/or characterization.

**Note**: Operating Conditions apply.

### 4 Electrical characteristics and parameters

Table 14 Power-Up and Supply Threshold Parameters

| Parameter                                            | Symbol                                 |                                           | Values |                 | Unit | Note or Test Condition                                              |

|------------------------------------------------------|----------------------------------------|-------------------------------------------|--------|-----------------|------|---------------------------------------------------------------------|

|                                                      |                                        | Min.                                      | Тур.   | Max.            |      |                                                                     |

| V <sub>DD</sub> ramp-up time                         | $t_{RAMPUP}SR$                         | V <sub>DD</sub> /<br>S <sub>VDDrise</sub> | _      | 10 <sup>7</sup> | μs   |                                                                     |

| V <sub>DD</sub> slew rate                            | S <sub>VDDOP</sub> SR                  | 0                                         | _      | 0.1             | V/μs | Slope during normal operation                                       |

|                                                      | S <sub>VDD10</sub> SR                  | 0                                         | -      | 10              | V/µs | Slope during fast transient within +/-10% of V <sub>DD</sub>        |

|                                                      | S <sub>VDDrise</sub> SR                | 0                                         | -      | 10              | V/µs | Slope during power-<br>on or restart after<br>brownout event        |

|                                                      | S <sub>VDDfall</sub> <sup>10)</sup> SR | 0                                         | -      | 0.25            | V/µs | Slope during supply falling out of the +/-10% limits <sup>11)</sup> |

| V <sub>DD</sub> prewarning voltage                   | V <sub>DDPW</sub> CC                   | 2.1                                       | 2.25   | 2.4             | V    | ANAVDEL.VDEL_SELECT<br>= 00 <sub>B</sub>                            |

|                                                      |                                        | 2.85                                      | 3      | 3.15            | V    | ANAVDEL.VDEL_SELECT<br>= 01 <sub>B</sub>                            |

|                                                      |                                        | 4.2                                       | 4.4    | 4.6             | V    | ANAVDEL.VDEL_SELECT<br>= 10 <sub>B</sub>                            |

| V <sub>DD</sub> brownout reset voltage               | $V_{\rm DDBO}$ CC                      | 1.55                                      | 1.62   | 1.75            | V    | calibrated, before user code starts running                         |

| V <sub>DD</sub> voltage to ensure defined pad states | $V_{\rm DDA}$ CC                       | -                                         | 1.0    | -               | V    |                                                                     |

| Start-up time from power-<br>on reset                | t <sub>SSW</sub> CC                    | _                                         | 260    | -               | μs   | Time to the first user code instruction <sup>12)</sup>              |

| Start-up time to PWM on                              | $t_{PWMON}$ CC                         | 5.2                                       | -      | 360             | ms   | Time to PWM enabled                                                 |

Figure 13 Supply Threshold Parameters

<sup>&</sup>lt;sup>10</sup> A capacitor of at least 100 nF has to be added between VDD and VSS to fulfill the requirement as stated for this parameter.

Valid for a 100 nF buffer capacitor connected to supply pin where current from capacitor is forwarded only to the chip. A larger capacitor value has to be chosen if the power source sink a current.

This values does not include the ramp-up time. During startup firmware execution, MCLK is running at 48 MHz and the clocks to peripheral as specified in register CGATSTAT0 are gated.

### 4 Electrical characteristics and parameters

## 4.3.3 On-Chip Oscillator Characteristics

Table 15 provides the characteristics of the 96 MHz digital controlled oscillator DCO1. The DCO1 is used as the time base during normal operation.

**Note**: These parameters are not subject to production test, but verified by design and/or characterization.

Table 15 96 MHz DCO1 Characteristics

| Parameter                                                  | Symbol               | Limit \ | /alues |      | Unit | <b>Test Conditions</b>                                                   |

|------------------------------------------------------------|----------------------|---------|--------|------|------|--------------------------------------------------------------------------|

|                                                            |                      | Min.    | Тур.   | Max. |      |                                                                          |

| Nominal frequency                                          | f <sub>NOM</sub> CC  | -       | 96     | -    | MHz  | under nominal conditions after trimming                                  |

| Accuracy with adjustment algorithm <sup>13)</sup> based on | $\Delta f_{LTTS}$ CC | -0.6    | -      | +0.6 | %    | with respect to $f_{NOM}$ (typ),<br>T <sub>A</sub> from 0°C to 105°C     |

| temperature sensor                                         |                      | -1.9    | -      | +1.0 | %    | with respect to $f_{NOM}$ (typ),<br>T <sub>A</sub> from -25 °C to 105°C  |

|                                                            |                      | -2.6    | -      | +1.3 | %    | with respect to $f_{NOM}(typ)$ ,<br>T <sub>A</sub> from -40° C to 105 °C |

| Accuracy                                                   | $\Delta f_{LT}$ CC   | -1.7    | -      | +3.4 | %    | with respect to $f_{NOM}(typ)$ ,<br>T <sub>A</sub> from 0 ° C to 85 °C   |

|                                                            |                      | -3.9    | -      | +4.0 | %    | with respect to $f_{NOM}(typ)$ ,<br>T <sub>A</sub> from -40° C to 105 °C |

Table 16 provides the characteristics of the 32 kHz digital controlled oscillator used internally as a secondary clock source for the internal watchdog.

Table 16 32 kHz DCO2 Characteristics

| Parameter         | Symbol              | Limit Values |       |      | Unit | <b>Test Conditions</b>                                                   |  |

|-------------------|---------------------|--------------|-------|------|------|--------------------------------------------------------------------------|--|

|                   |                     | Min.         | Тур.  | Max. |      |                                                                          |  |

| Nominal frequency | f <sub>NOM</sub> CC | -            | 32.75 | -    | kHz  | under nominal conditions <sup>14)</sup> after trimming                   |  |

| Accuracy          | $\Delta f_{LT}$ CC  | -1.7         | -     | +3.4 | %    | with respect to $f_{NOM}$ (typ),<br>T <sub>A</sub> from 0 ° C to 85 °C   |  |

|                   |                     | -3.9         | -     | +4.0 | %    | with respect to $f_{NOM}$ (typ),<br>T <sub>A</sub> from -40° C to 105 °C |  |

MCE version newer or equal to V1.03.00, clock adjustment algorithm for improved accuracy enabled

The deviation is relative to the factory trimmed frequency at nominal  $V_{\rm DDC}$  and  $T_{\rm A}$  = + 25°C.

### **4** Electrical characteristics and parameters

## 4.3.4 Dynamic parameters gate driver

$V_{CC} = V_{BS} = 15 \text{ V}$ ,  $V_S = V_{SS} = V_{COM}$  unless otherwise specified. All parameters are valid for  $T_a = 25 \, ^{\circ}\text{C}$ .

Table 17 Dynamic parameters

| Parameter                                                                                   | Symbol            |      | Values |      | Unit | Note or Test Condition |

|---------------------------------------------------------------------------------------------|-------------------|------|--------|------|------|------------------------|

|                                                                                             |                   | Min. | Тур.   | Max. |      |                        |

| Turn-on propagation delay                                                                   | t <sub>on</sub>   | 400  | 530    | 800  | ns   |                        |

| Turn-off propagation delay                                                                  | t <sub>off</sub>  | 400  | 530    | 800  | ns   |                        |

| Turn-on rise time                                                                           | t <sub>r</sub>    | _    | 60     | 100  | ns   | C <sub>L</sub> = 1 nF  |

| Turn-off fall time                                                                          | t <sub>f</sub>    | _    | 26     | 45   | ns   | C <sub>L</sub> = 1 nF  |

| Dead time                                                                                   | DT                | 150  | 310    | _    | ns   |                        |

| Matching delay ON, max(ton)-<br>min(ton), ton are applicable to<br>all 6 driver outputs     | MT <sub>ON</sub>  | _    | 20     | 100  | ns   |                        |

| Matching delay OFF, max(toff)-<br>min(toff), toff are applicable to<br>all 6 driver outputs | MT <sub>OFF</sub> | -    | 40     | 100  | ns   |                        |

| Output pulse width matching. P <sub>win</sub> -P <sub>Wout</sub>                            | PM                | -    | 10     | 100  | ns   |                        |

### **4** Electrical characteristics and parameters

## 4.3.5 Timing diagrams

Figure 14 Operating Areas

### 4 Electrical characteristics and parameters

### 4.4 Motor Control Parameters

The following values are given for reference only. Concrete parameters are defined in the iMOTION™ Motion Control Engine (MCE) software.

### 4.4.1 PWM Characteristics

### Table 18Electrical characteristics

| Parameter                          | r Symbol Values  |      |      |      | Symbol | Values    |  |  | Unit | Note or test |

|------------------------------------|------------------|------|------|------|--------|-----------|--|--|------|--------------|

|                                    |                  | Min. | Тур. | Max. |        | condition |  |  |      |              |

| Motor PWM Frequency <sup>15)</sup> | f <sub>PWM</sub> | 5    | 16   | 40   | kHz    |           |  |  |      |              |

### 4.4.2 Current Sensing

### Table 19 Motor Current Sensing

| Parameter                | Symbol               |                       | Values   | Unit                  | Note or test |                            |

|--------------------------|----------------------|-----------------------|----------|-----------------------|--------------|----------------------------|

|                          |                      | Min.                  | Тур.     | Max.                  |              | condition                  |

| Input range              | I <sub>PWM</sub>     | V <sub>SS</sub> -0.05 | -        | V <sub>DD</sub> +0.05 | V            |                            |

| Configurable analog gain |                      | -                     | 1/3/6/12 | -                     |              |                            |

| Itrip input range        | I <sub>PWMTRIP</sub> | V <sub>SS</sub> -0.05 | -        | V <sub>DD</sub> +0.05 | V            |                            |

| Itrip offset             |                      | -                     | ±8       | -                     | mV           |                            |

| Input capacitance        | C <sub>REF</sub>     | -                     | -        | 10                    | pF           | REFU, REFV, REFW capacitor |

Actual min. and max. limits defined in resp. software version

### 4 Electrical characteristics and parameters

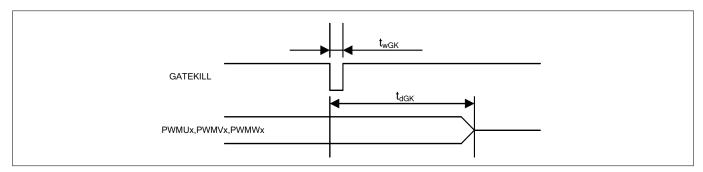

## 4.4.3 Fault Timing

Figure 15 Fault timing

Table 20 Gatekill timing

| Parameter                       | Symbol              | Symbol Values |      |      |    | Note or test                                              |

|---------------------------------|---------------------|---------------|------|------|----|-----------------------------------------------------------|

|                                 |                     | Min.          | Тур. | Max. |    | condition                                                 |

| GK pulse width                  | $t_{wGK}$           | 1             | -    | -    | μs |                                                           |

| GK input to PWM shutoff         | $t_{GK}$            | -             | 1.3  | -    | μs |                                                           |

| Motor Fault reset timing        | t <sub>RESET</sub>  | -             | 1.84 | -    | ms | fault reset<br>command via<br>UART to PWM<br>reactivation |

| MCE digital ITRIP filter window | t <sub>PWMOFF</sub> | 0.075         | 1.0  | 10   | μs | Configurable in software                                  |

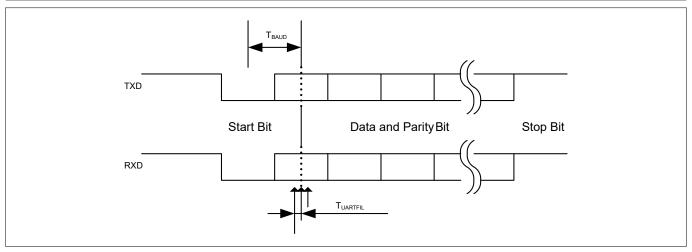

Note: