# CoolGaN<sup>™</sup> Integrated Power Stage (IPS) IGI60F2020A1L

### 200 m $\Omega$ / 600 V GaN half-bridge with fast accurate isolated gate drivers

#### Features

- Two 200 m $\Omega$  GaN switches in half-bridge configuration with dedicated high- and low-side isolated gate drivers

- Source / sink driving current up to 1 / 2 A

- Application-configurable turn-on and turn-off speed

- Fast input-to-output propagation (typ. 47 ns) with extremely small channel-tochannel mismatch

- PWM input signal (switching frequency up to 3 MHz)

- Standard logic input levels compatible with digital controllers

- Wide supply range

- Single gate driver supply voltage possible (typ. 8 V) with fast UVLO recovery

- Low-side open source for current sensing with external shunt resistor •

- Galvanic input-to-output isolation based on robust coreless transformer technology •

- Gate driver with very high common mode transient immunity (CMTI) > 300 V/ns

- Thermally enhanced 8 x 8 mm QFN-28 package

- Product is fully qualified acc. to JEDEC for Industrial Applications

#### Description

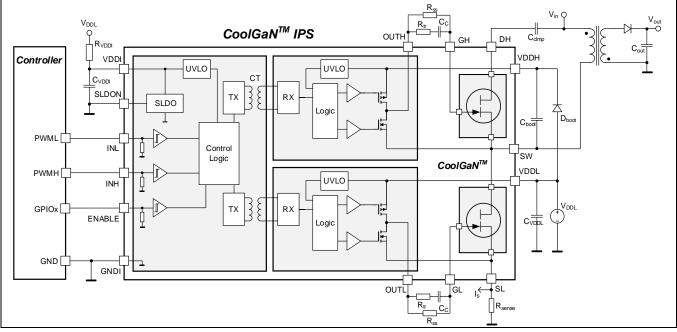

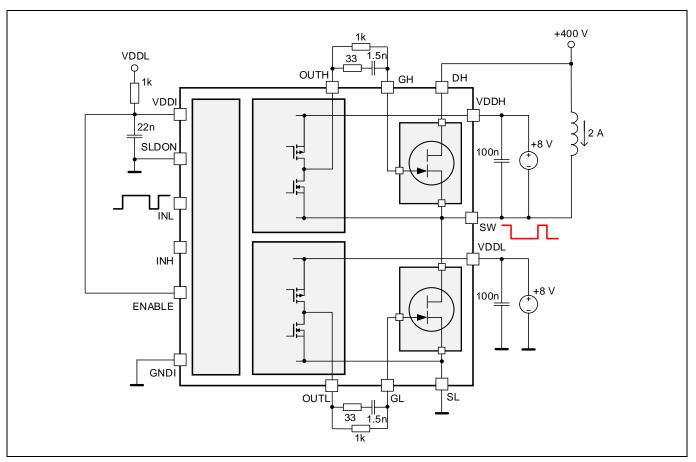

IGI60F2020A1L combines a half-bridge power stage consisting of two 200 mΩ (typ. Rdson) / 600 V enhancementmode CoolGaN<sup>™</sup> HEMTs with dedicated gate drivers in a small 8 x 8 mm QFN-28 package. In the low-to-medium power area (example application in Figure 1) it is thus ideally suited to support the design of high-density AC/DC chargers and adapters utilizing the superior switching behavior of CoolGaN<sup>™</sup> HEMTs.

Infineon's CoolGaN<sup>™</sup> and related power switches provide a very robust gate structure. When driven by a continuous gate current of a few mA in the "on" state, a minimum on-resistance Rdson is always guaranteed.

Figure 1 Typical application circuit (active clamp flyback converter)

Infineon

www.infineon.com

**Final Datasheet**

Due to the GaN-specific low threshold voltage and the fast switching transients, a negative gate drive voltage is required in certain applications to both enable fast turn-off and avoid cross-conduction effects. This can be achieved by the well-known RC interface between driver and switch. A few external SMD resistors and caps enable easy adaptation to different power topologies.

The driver utilizes on-chip coreless transformer technology (CT) to achieve signal level-shifting to the high-side. Further, CT guarantees robustness even for extremely fast switching transients above 300 V/ns.

#### Applications

- Charger and adaptors

- Server, telecom & networking SMPS

- Low power motor drive

- LED lighting

#### **Power Topologies**

- Active clamp flyback or hybrid flyback converters

- LLC or LCC resonant converters

- Single or interleaved synchronous buck or boost converter

- Single phase or multiphase two-level inverters

#### **Product Versions**

#### Table 1 CoolGaN<sup>™</sup> integrated power stage half bridge products overview

| Part Number /<br>Ordering code | OPN                    | Package                   | Typ. R <sub>dson</sub><br>high- / Iow-side | Marking  |

|--------------------------------|------------------------|---------------------------|--------------------------------------------|----------|

| IGI60F1414A1L                  | IGI60F1414A1L<br>AUMA1 | PG-TIQFN-28-1<br>8 x 8 mm | 140 mΩ / 140 mΩ                            | 60F1414A |

| IGI60F2020A1L                  | IGI60F2020A1L<br>AUMA1 | PG-TIQFN-28-1<br>8 x 8 mm | 200 mΩ / 200 mΩ                            | 60F2020A |

| IGI60F2727A1L                  | IGI60F2727A1L<br>AUMA1 | PG-TIQFN-28-1<br>8 x 8 mm | 270 mΩ / 270 mΩ                            | 60F2727A |

| IGI60F5050A1L                  | IGI60F5050A1L<br>AUMA1 | PG-TIQFN-28-1<br>8 x 8 mm | 500 mΩ / 500 mΩ                            | 60F5050A |

## **Table of contents**

| Table | e of contents                           |

|-------|-----------------------------------------|

| 1     | Pin configuration and description       |

| 2     | Functional description                  |

| 2.1   | Block Diagram6                          |

| 2.2   | Power supply7                           |

| 2.2.1 | Driver input supply voltage7            |

| 2.2.2 | Driver output supply voltages7          |

| 2.3   | Input configurations8                   |

| 2.4   | Driver outputs8                         |

| 2.5   | Undervoltage Lockout (UVLO)8            |

| 2.6   | Start-up and active clamping9           |

| 2.7   | CT Communication and Data Transmission9 |

| 2.8   | CoolGaN™ output stage9                  |

| 3     | Characteristics10                       |

| 3.1   | Absolute maximum ratings10              |

| 3.2   | Thermal characteristics11               |

| 3.3   | Recommended operating range11           |

| 3.4   | Electrical characteristics12            |

| 3.5   | Timing diagrams and test circuit17      |

| 4     | Driving CoolGaN™ HEMTs                  |

| 5     | Typical characteristics                 |

| 5.1   | GaN switch characteristics21            |

| 5.2   | Gate driver characteristics             |

| 6     | Application circuit                     |

| 7     | Package information                     |

| 8     | Layout guidelines                       |

| 9     | Appendix32                              |

| 10    | References                              |

| Revis | ion history                             |

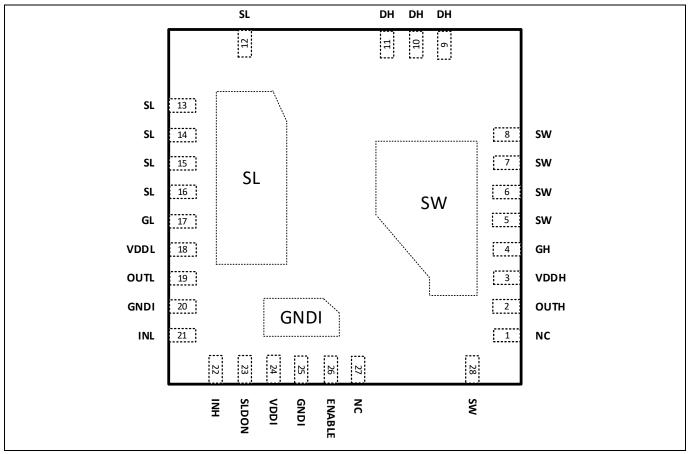

# 1 Pin configuration and description

Figure 2 Pin configuration and exposed pads for QFN-28 8 x 8 mm package, top view (not to scale)

#### Table 2Pin description

| Pin No.   | Symbol | Description                                                   |

|-----------|--------|---------------------------------------------------------------|

| 1         | NC     | Not connected                                                 |

| 2         | OUTH   | Driver output high-side                                       |

| 3         | VDDH   | Supply voltage for high-side driver (typ. 8 V referred to SW) |

| 4         | GH     | Gate connection high-side switch                              |

| 5 – 8, 28 | SW     | Half-bridge output (switching node)                           |

| 9 - 11    | DH     | Drain connection high-side switch                             |

| 12 - 16   | SL     | Source connection low-side switch                             |

| 17        | GL     | Gate connection low-side switch                               |

| 18        | VDDL   | Supply voltage for low-side driver (typ. 8 V referred to SL)  |

| 19        | OUTL   | Driver output low-side                                        |

| 20, 25    | GNDI   | Ground connection of driver input stage                       |

|    | 1      |                                                                                                                                                                          |

|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21 | INL    | Input signal (default state "Low"); controls low-side switch                                                                                                             |

| 22 | INH    | Input signal (default state "Low"); controls high-side switch                                                                                                            |

| 23 | SLDON  | Connected to VDDI (or not connected): VDDI directly supplies driver input circuitry<br>Connected to GNDI: Internal shunt regulator activated to generate VDDI (3.3 V)    |

| 24 | VDDI   | Supply voltage driver input stage (+3.3 V); can be either applied directly or generated by internal SLDO (e.g by connecting VDDI via resistor R <sub>VDDI</sub> to VDDL) |

| 26 | ENABLE | Input signal (default state "Low" - both outputs set to low state); logic "High" required to activate outputs                                                            |

| 27 | NC     | Not connected                                                                                                                                                            |

# 2 Functional description

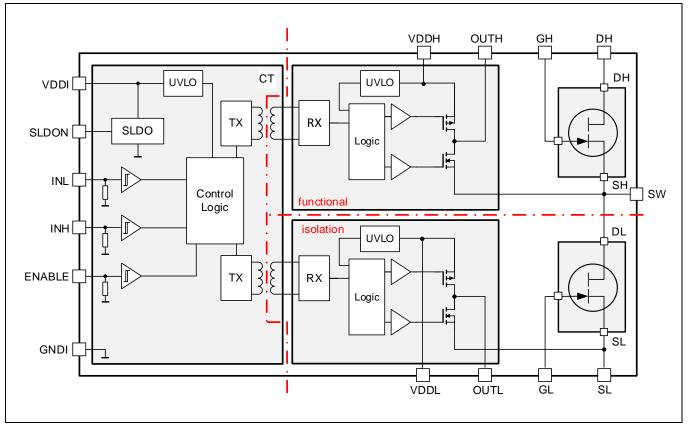

## 2.1 Block Diagram

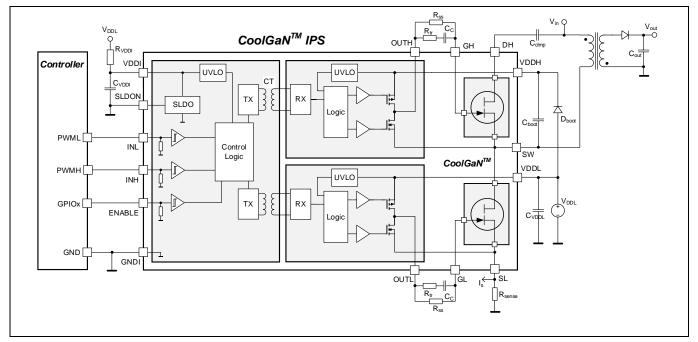

A simplified functional block diagram of the CoolGaN<sup>™</sup> Power Stage is given in **Figure 3**. For the level-shifting function of the input signal to the high-side switch an on-chip coreless transformer (CT) is utilized. For symmetry reasons a CT is also included in the low-side path, resulting in both a galvanic input-to-output and high-to-low-side isolation. In addition, this CT separates the low-side gate driver reference (SL) from GNDI allowing to use a shunt resistor for current sensing as shown in **Figure 1**.

Figure 3 Block Diagram IGI60F2020A1L

### 2.2 Power supply

Basically, the Power Stage requires 3 supply voltages: a ground-related 3.3 V ( $V_{DDI}$ ) for the driver input circuitry, another ground-related 8 V ( $V_{DDL}$ ) for the low-side driver and a floating 8 V ( $V_{DDH}$ ) for the high-side driver. However, in most applications a single 8 V supply is sufficient, as  $V_{DDI}$  and  $V_{DDH}$  can be simply generated from  $V_{DDL}$ . Independent Undervoltage Lockout (UVLO) functions for all supply voltages ensure a defined start-up and robust functionality under all operating conditions.

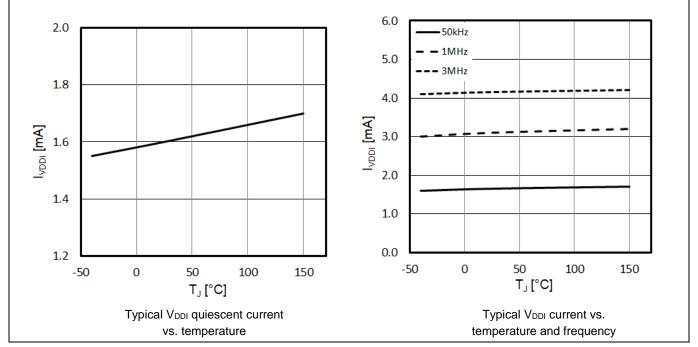

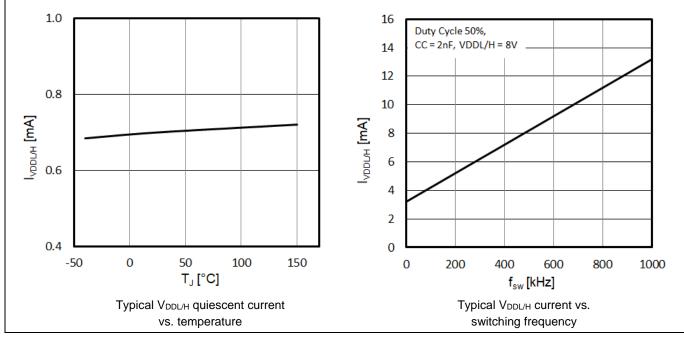

All driver supply currents stay in the few mA range, as described in **Table 9**, resp. However, in particular applications a further power reduction in stand-by mode might be beneficial. Then a complete elimination of the supply currents can be achieved by implementing a simple circuit with a bipolar transistor as a supply switch controlled by the Enable signal.

## 2.2.1 Driver input supply voltage

The driver input die is supplied via  $V_{DDI}$  with a nominal voltage of 3.3 V. The Undervoltage Lockout threshold, defining the minimum  $V_{DDI}$ , is set to typically 2.85 V. Power consumption to some extent depends on switching frequency, as the input signal is converted into a train of repetitive current pulses to drive the CT. Due to the chosen robust encoding scheme the average repetition rate of these pulses and thus the average supply current depends on the switching frequency  $f_{sw}$ . However, for  $f_{sw} < 500$  kHz this effect is very small.

If no separate 3.3 V supply is available, the input side can also be operated with  $V_{DDL}$  (typically 8 V). Then the shunt LDO voltage regulator (SLDO) has to be enabled by connecting pin SLDON (pin#23) to GNDI. The SLDO regulates the current through an external resistor  $R_{VDDI}$  connected between  $V_{DDL}$  and pin VDDI as depicted in **Figure 1** to generate the required voltage drop. For proper operation it has to be ensured that the current through  $R_{VDDI}$  always exceeds the maximum supply current  $I_{VDDI}$  of the input chip; but not too small to casue a high power dissipation and significant impact on the total system efficiency.  $R_{VDDI}$  thus has to fulfil:

$$R_{VDDI} < \frac{V_{DDL,min} - 3.3 V}{I_{VDDI,max}}$$

(1)

A typical choice for  $V_{DDL} = 8$  V would be  $R_{VDDI} = 1$  k $\Omega$ , resulting in sufficient margin between resistor current and maximum operating current. Dynamic current peaks are provided by a blocking cap (10 to 22 nF) between  $V_{DDI}$  and GNDI. Table 3 shows proper  $R_{VDDI}$  values for different supply voltages  $V_{DDL}$ .

Table 3

Proper R<sub>VDDI</sub> values for different V<sub>DDL</sub>

| V <sub>DDL</sub> | R <sub>VDDI</sub>                      | SLDO     |

|------------------|----------------------------------------|----------|

| 3.3 V            | no resistor (connect VDDL to VDDI pin) | Disabled |

| 5.0 V            | 360 Ω                                  | Enabled  |

| 8.0 V            | 1.0 kΩ                                 | Enabled  |

| 12.0 V           | 1.8 kΩ                                 | Enabled  |

## 2.2.2 Driver output supply voltages

Both output dice have to be supplied by a voltage of typically 8 V related to the source of the respective GaN switch. In many applications the floating high-side supply  $V_{DDH}$  can be generated from the ground-related  $V_{DDL}$  by means of bootstrapping (components  $D_{boot}$ ,  $C_{boot}$  and  $R_{boot}$  in **Figure 1**). A ceramic bypass capacitance  $C_{VDDL}$  of typically 100 nF has to be placed close to pin VDDL.

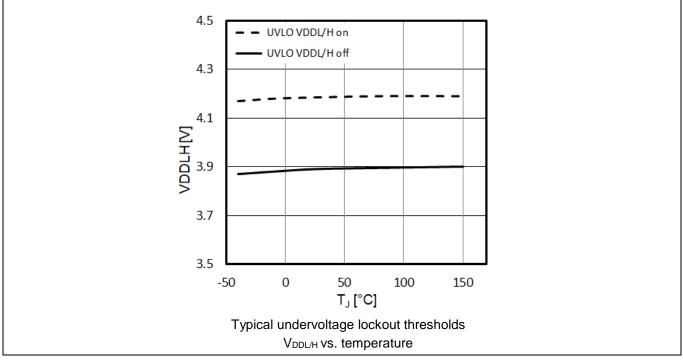

For both driver output stages the minimum operating supply voltage is set by independent undervoltage lockout functions (UVLO<sub>out</sub>).

## 2.3 Input configurations

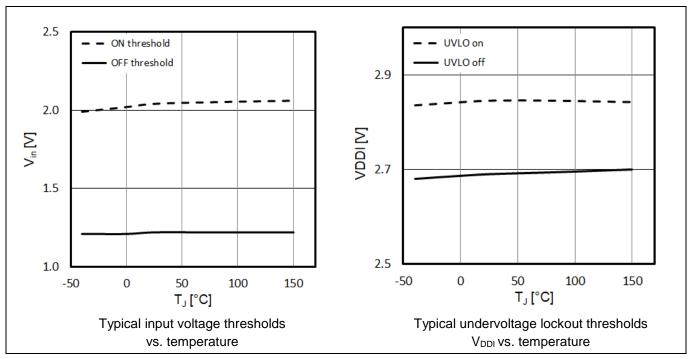

The inputs INL and INH are two independent logic (PWM) channels. The input signal is transferred non-inverted to the corresponding gate driver outputs OUTL and OUTH. All inputs are compatible with LV-TTL threshold levels with a hysteresis of typ. 0.8 V. The hysteresis is independent of the supply voltage VDDI.

The PWM inputs are internally pulled down to a logic low voltage level (GNDI). In case the PWM-controller signals have an undefined state during the power-up sequence, the gate driver outputs are forced to the "off"-state (low). If the Enable input is low, both channel outputs are driven to "low", regardless of the state of INL or INH. Table 4 shows the logic table in normal operation.

## Table 4Logic table (UVLO input inactive, both output side UVLO inactive; normal operation)

|        | Inputs |     | Gate Dri | ve Ouput |

|--------|--------|-----|----------|----------|

| Enable | INL    | INH | OUTL     | OUTH     |

| L      | x      | x   | L        | L        |

| Н      | L      | L   | L        | L        |

| Н      | L      | Н   | L        | н        |

| Н      | Н      | L   | Н        | L        |

| Н      | Н      | Н   | Н        | н        |

## 2.4 Driver outputs

The rail-to-rail gate driver output stage realized with complementary MOS transistors is able to provide a typical 1 A sourcing and 2 A sinking current. This is by far sufficient when driving the GaN HEMTs due to their low gate charge. In addition, the relatively low driver output resistance is beneficial, too. With an R<sub>on</sub> of 3.1  $\Omega$  for the sourcing pMOS and 1.2  $\Omega$  for the sinking nMOS transistor the driver can be considered as nearly ideal. The gate drive parameters can thus be determined easily and accurately by the external components as described in chapter 4. The p-channel sourcing transistor allows real rail-to-rail behavior without suffering from a source follower's voltage drop.

## 2.5 Undervoltage Lockout (UVLO)

The Undervoltage Lockout function ensures that the gate drive outputs can be switched to their high level only, if both input and output supply voltages exceed the corresponding UVLO threshold voltages. Thus it can be guaranteed, that the GaN switches are in "off" state, if the driving voltage is too low for complete and fast switching on, thereby avoiding excessive power dissipation and keeping the switch transistors within their safe operating area (SOA).

The UVLO levels for the output supplies  $V_{DDL}$  and  $V_{DDH}$  are set to a typical "on"-value of 4.2 V (with 0.3 V hysteresis), whereas UVLO<sub>in</sub> for  $V_{DDI}$  is set to 2.85 V with 0.15 V hysteresis. Table 5 shows the logic table in the condition that input or outputs are in UVLO active or inactive condition.

| Inputs |     |     |            |                             |          |      | Gate Drive Ouput |  |  |

|--------|-----|-----|------------|-----------------------------|----------|------|------------------|--|--|

| Enable | INL | INH | UVLO input | UVLO output L UVLO output H |          | OUTL | OUTH             |  |  |

| х      | х   | х   | Active     | х                           | Х        | L    | L                |  |  |

| Н      | х   | L   | Inactive   | Active                      | Inactive | L    | L                |  |  |

| Н      | х   | Н   | Inactive   | Active                      | Inactive | L    | н                |  |  |

| н      | L   | x   | Inactive   | Inactive                    | Active   | L    | L                |  |  |

| н      | Н   | x   | Inactive   | Inactive                    | Active   | Н    | L                |  |  |

#### Table 5Logic table ( dependence on UVLO status)

## 2.6 Start-up and active clamping

Special attention has been paid to cover all possible operating conditions, like start-up or arbitrary supply voltage situations:

- if V<sub>DDI</sub> drops below UVLO<sub>in</sub>, a "switch-to-low" command is sent to both outputs OUTL and OUTH

- for V<sub>DDL</sub> and/or V<sub>DDH</sub> lower than the respective UVLO levels, a new fast active clamping circuit provides a low-impedance path from the gate driver outputs OUTL and OUTH to their respective grounds SL and SW. As soon as the output voltage exceeds a low threshold level (typically below 1 V), the clamp is activated within approximately 20 ns.

As the result, safe operation of the GaN Power Stage can be guaranteed under any circumstances.

## 2.7 CT Communication and Data Transmission

A Coreless Transformer (CT) based communication module is used for PWM signal transfer between input and outputs. A proven high-resolution pulse repetition scheme in the transmitter combined with a watchdog time-out at the receiver side enables recovery from communication fails and ensures safe system shut-down in failure cases.

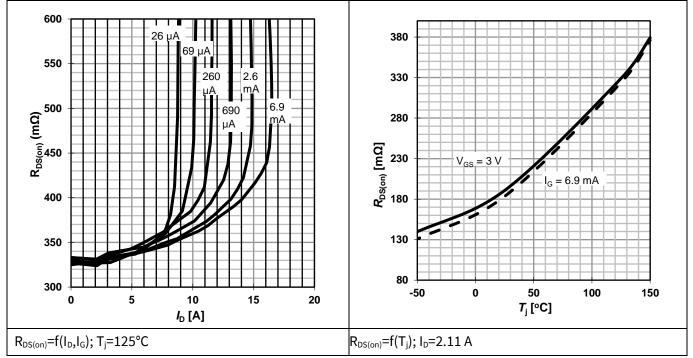

## 2.8 CoolGaN<sup>™</sup> output stage

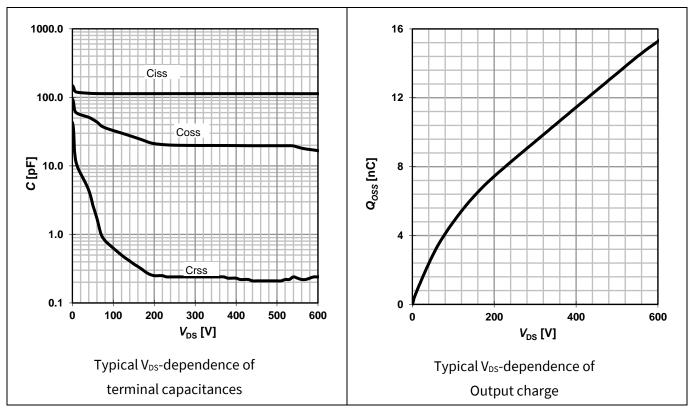

The output stage consists of two CoolGaN<sup>TM</sup> 600V switches in half-bridge configuration. The switches are characterized by a typical R<sub>dson</sub> of 200 m $\Omega$  @ 25 °C. And thanks to the current driving concept, this value increases by a comparably moderate 85 % @ 150 °C. As typical for GaN, gate and output charges are very small (3 and 16 nC, resp.) and there is no reverse recovery charge due to the lack of a physical body diode (for more information please refer to [1]).

# 3 Characteristics

### 3.1 Absolute maximum ratings

The absolute maximum ratings are listed in **Table 6**. Stresses beyond these values may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                           | Symbol                | Va   | alues                    | Unit | Note or Test Conditions                                                 |

|-------------------------------------|-----------------------|------|--------------------------|------|-------------------------------------------------------------------------|

|                                     |                       | Min. | Max.                     |      |                                                                         |

| Voltage between output pins         | VDHSW                 | -    | 600                      | V    |                                                                         |

| DH, SW and SL                       | Vswsl                 | -    | 600                      | V    | $V_{GHSH} = 0 \ V, \ V_{GLSL} = 0 \ V$                                  |

| Drain-to-source voltage pulsed      | V <sub>DS,pulse</sub> | -    | 750 <sup>1</sup>         | V    | $T_J = 25^{\circ}C, V_{GS} \le 0 V,$<br>cumulated stress time $\le 1h$  |

|                                     |                       | -    | 650                      | V    | $T_J = 125^{\circ}C, V_{GS} \le 0 V,$<br>cumulated stress time $\le 1h$ |

| Continuous drain current            | ID                    | -    | 5.0                      | А    | T <sub>Case</sub> = 25°C                                                |

|                                     |                       | -    | 3.7                      | А    | T <sub>Case</sub> = 125°C                                               |

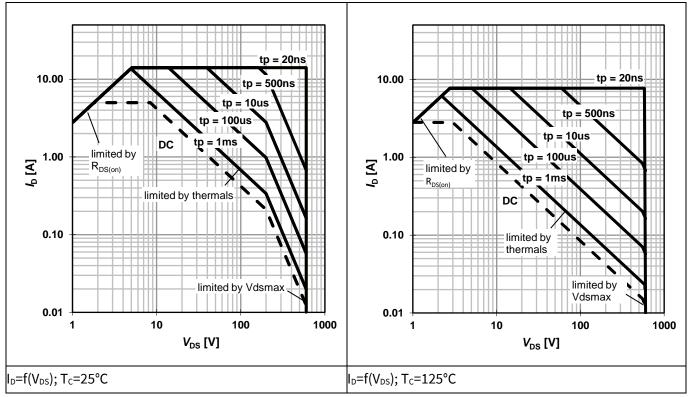

| Pulsed drain current <sup>2</sup>   | I <sub>D,pulse</sub>  | -    | 14.1                     | А    | T <sub>Case</sub> = 25°C (see Figure 13)                                |

|                                     |                       | -    | 7.7 <sup>3</sup>         | А    | T <sub>Case</sub> = 125°C (see Figure 13)                               |

| Supply voltage input chip           | V <sub>DDI</sub>      | -0.3 | 3.7                      | V    | Note <sup>4</sup>                                                       |

| Supply voltage output chips         | V <sub>DDL/H</sub>    | -0.3 | 22                       | V    | with respect to SW/SL                                                   |

| Voltage at pins INL, INH and ENABLE | V <sub>IN</sub>       | -0.3 | 17                       | V    |                                                                         |

| Voltage at pin SLDO                 | V <sub>SLDO</sub>     | -0.3 | V <sub>DDI</sub> + 0.3   | V    |                                                                         |

| Voltage at pins OUTL, OUTH          | V <sub>OUTL/H</sub>   | -0.3 | V <sub>DDL/H</sub> + 0.3 | V    |                                                                         |

| Junction temperature                | TJ                    | - 40 | 150                      | °C   |                                                                         |

| Storage temperature                 | Ts                    | - 55 | 150                      | °C   |                                                                         |

| Soldering temperature               | T <sub>sold</sub>     | -    | 260                      | °C   | reflow/wave soldering <sup>5</sup>                                      |

#### Table 6 Absolute maximum ratings

<sup>&</sup>lt;sup>1</sup> Acc to JEDEC-JEP180

<sup>&</sup>lt;sup>2</sup> Limits derived from product characterization, parameter not measured during production

<sup>&</sup>lt;sup>3</sup> Parameter is influenced by reliability requirements. Please contact the local Infineon Sales Office to get an assessment of your application

<sup>&</sup>lt;sup>4</sup> If the SLDO is activated (SLDON pin tied to GNDI), the input-side supply voltage (VDDL) does not correspond to VDDI and can be higher <sup>5</sup> Acc. to JESD22A111

| Parameter      | Symbol   | Va   | lues | Unit | Note or Test Conditions           |

|----------------|----------|------|------|------|-----------------------------------|

|                |          | Min. | Max. |      |                                   |

| ESD capability | Vesd_hbm | -    | 2    | kV   | Human Body Model <sup>1</sup>     |

|                | Vesd_cdm | -    | 1.0  | kV   | Charged Device Model <sup>2</sup> |

## 3.2 Thermal characteristics

#### Table 7Thermal characteristics

| Parameter                               | Symbol |      | Values |      | Unit | Note or Test                                                                          |

|-----------------------------------------|--------|------|--------|------|------|---------------------------------------------------------------------------------------|

|                                         |        | Min. | Тур.   | Max. |      | Conditions                                                                            |

| Thermal resistance junction-case        | RthJC  | -    | -      | 3.0  | °C/W |                                                                                       |

| Thermal resistance junction-<br>ambient | RthJA  | -    | 35     | -    | °C/W | Device mounted on<br>four-layer PCB with<br>600 mm <sup>2</sup> total cooling<br>area |

## 3.3 Recommended operating range

#### Table 8 Recommended operating range

| Parameter                                          | Symbol              |      | Values |                  | Unit | Note or Test<br>Conditions             |

|----------------------------------------------------|---------------------|------|--------|------------------|------|----------------------------------------|

|                                                    |                     | Min. | Тур.   | Max.             |      |                                        |

| Input supply voltage                               | VDDI                | 3    | 3.3    | 3.5              | V    | if operated directly without SLDO      |

| Driver output supply voltages                      | Vddl/h              | 5.5  | 8      | 12               | V    | min. defined by<br>UVLO <sub>out</sub> |

| VDDI blocking capacitance                          | C <sub>VDDI</sub>   | 10   | -      | 22               | nF   | SLDO active                            |

| Logic input voltage at pins INL,<br>INH and ENABLE | Vin                 | 0    | -      | 6.5              | V    |                                        |

| Voltage at pin SLDO                                | Vsldo               | 0    | -      | 3.5              | V    |                                        |

| Gate current, continuous <sup>3 4</sup>            | I <sub>G, avg</sub> | -    | -      | 6.9              | mA   |                                        |

| Junction temperature                               | TJ                  | -40  | -      | 125 <sup>5</sup> | °C   |                                        |

$<sup>^1</sup>$  Acc. to EIA/JESD22-A114-B (discharging 100 pF capacitor through 1.5 k $\Omega$  resistor)

<sup>&</sup>lt;sup>2</sup> Acc. to JESD22-002

<sup>&</sup>lt;sup>3</sup> Parameter is influenced by rel-requirements. Contact the local Infineon Sales Office to get an assessment of your application.

<sup>&</sup>lt;sup>4</sup> We recommend to use RC interface gate drive to optimize the device performance. Please see gate drive application note for details.

<sup>&</sup>lt;sup>5</sup> Continuous operation above 125°C may reduce lifetime

## 3.4 Electrical characteristics

Unless otherwise noted, min/max values of characteristics are the lower and upper limits, resp. They are valid within the full operating range. All values are given at  $T_J = 25$  °C with  $V_{DDI} = 3.3$  V and  $V_{DDL/H} = 8$  V.

#### Table 9Power supply

| Parameter                                                                   | Symbol                   |      | Values | Unit | Note or Test |              |

|-----------------------------------------------------------------------------|--------------------------|------|--------|------|--------------|--------------|

|                                                                             |                          | Min. | Тур.   | Max. |              | Conditions   |

| VDDI quiescent current <sup>1</sup>                                         | IVDDIqu                  | -    | 1.4    | -    | mA           | no switching |

| VDDL quiescent current <sup>1</sup>                                         | IVDDLqu                  | -    | 0.7    | -    | mA           | no switching |

| V <sub>DDH</sub> quiescent current <sup>1</sup>                             | I <sub>VDDHqu</sub>      | -    | 0.7    | -    | mA           | no switching |

| Undervoltage Lockout input<br>(UVLO <sub>VDDI</sub> ) turn-on threshold     | UVLOvddi                 | 2.75 | 2.85   | 2.95 | V            |              |

| UVLO <sub>VDDI</sub> turn-off threshold                                     | UVLO <sub>VDDI-</sub>    | -    | 2.7    | -    | V            |              |

| UVLOVDDI threshold hysteresis                                               |                          | 0.1  | 0.15   | 0.2  | V            |              |

| Undervoltage Lockout outputs<br>(UVLO <sub>VDDL/H</sub> ) turn-on threshold | UVLO <sub>outLH</sub>    | 4.0  | 4.2    | 4.4  | V            |              |

| UVLO <sub>VDDL/H</sub> turn-off threshold                                   | UVLO <sub>VDDL/H</sub> - | -    | 3.9    | -    | V            |              |

| UVLO <sub>VDDL/H</sub> threshold hysteresis                                 |                          | 0.2  | 0.3    | 0.4  | V            |              |

#### Table 10 Logic inputs INL, INH and ENABLE

| Parameter                                 | Symbol              |      | Values |      | Unit | Note or Test<br>Conditions |

|-------------------------------------------|---------------------|------|--------|------|------|----------------------------|

|                                           |                     | Min. | Тур.   | Max. |      |                            |

| Input voltage threshold for transition LH | V <sub>IN+</sub>    | 1.7  | 2.0    | 2.3  | V    | independent of VDDI        |

| Input voltage threshold for transition HL | Vin-                | -    | 1.2    | -    | V    | independent of VDDI        |

| Input voltage threshold hysteresis        | V <sub>IN_hys</sub> | 0.4  | 0.8    | 1.2  | V    |                            |

| Input pull down resistor                  | RIN                 | -    | 150    | -    | kΩ   |                            |

<sup>&</sup>lt;sup>1</sup> Can be completely eliminated in stand-by mode by utilizing external supply switch (see chapter 2.2)

| Parameter                                 | Symbol              |      | Values |      | Unit | Note or Test Conditions    |

|-------------------------------------------|---------------------|------|--------|------|------|----------------------------|

|                                           |                     | Min. | Тур.   | Max. |      |                            |

| High-level (sourcing) output resistance   | Ron                 | 1.4  | 3.1    | 5.8  | Ω    |                            |

| Peak sourcing output current <sup>1</sup> | I <sub>src,pk</sub> | -    | 1      | -    | A    | actively limited to 1.3 A  |

| Low-level (sinking) output resistance     | Roff                | 0.6  | 1.2    | 2.5  | Ω    |                            |

| Peak sinking output current <sup>1</sup>  | I <sub>snk,pk</sub> | -    | -2     | -    | А    | actively limited to -2.6 A |

| Active clamp threshold voltage            | VcImp               | -    | 1      | -    | V    |                            |

### Table 11 Static gate driver output characteristics

#### Table 12 Output characteristics GaN switches

| Parameter                                   | Symbol            |      | Values |      | Unit | Note or Test Conditions                                                               |

|---------------------------------------------|-------------------|------|--------|------|------|---------------------------------------------------------------------------------------|

|                                             | -                 | Min. | Тур.   | Max. |      |                                                                                       |

| R <sub>dson</sub> high-side                 | Rdshs             | -    | 200    | 260  | mΩ   | $I_G = 6.9 \text{ mA}, I_D = 2.1 \text{ A},$<br>$T_J = 25^{\circ}\text{C}$            |

|                                             |                   | -    | 360    | -    | mΩ   | $I_G = 6.9 \text{ mA}, I_D = 2.1 \text{ A},$<br>$T_J = 150^{\circ}\text{C}$           |

| R <sub>dson</sub> low-side                  | R <sub>dsls</sub> | -    | 200    | 260  | mΩ   | $I_G = 6.9 \text{ mA}, I_D = 2.1 \text{ A},$<br>$T_J = 25^{\circ}\text{C}$            |

|                                             |                   | -    | 360    | -    | mΩ   | $I_G = 6.9 \text{ mA}, I_D = 2.1 \text{ A},$<br>$T_J = 150^{\circ}\text{C}$           |

| Drain-source leakage current                | IDSShs, IDSSIs    | -    | 0.26   | -    | μA   | $V_{DS} = 600 \text{ V}, \text{ V}_{GS} = 0 \text{ V},$<br>$T_J = 25^{\circ}\text{C}$ |

|                                             |                   | -    | 5.3    | -    | μA   | $V_{DS} = 600 \text{ V}, \text{ V}_{GS} = 0 \text{ V},$<br>$T_J = 25^{\circ}\text{C}$ |

| Total gate charge (per switch) <sup>1</sup> | Q <sub>G</sub>    | -    | 1.5    | -    | nC   | $I_G = 0$ to 2.6 mA,<br>V <sub>DH</sub> = 400 V, $I_D = 2.1$ A                        |

<sup>&</sup>lt;sup>1</sup>Verified by design / characterization, not tested in production

#### Table 13 Static characteristics GaN switches

| Parameter                            | Symbol                  | Values     |            | Unit       | Note or Test Condition |                                                                                                                                                                                                                        |

|--------------------------------------|-------------------------|------------|------------|------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                         | Min.       | Тур.       | Max.       |                        |                                                                                                                                                                                                                        |

| Gate threshold voltage               | V <sub>GS(th)</sub>     | 0.9<br>0.7 | 1.2<br>1.0 | 1.6<br>1.4 | V<br>V                 | $\label{eq:DS} \begin{array}{l} I_{DS} = 0.69 \text{ mA}, \ V_{DS} = 10 \text{ V}, \ T_{j} = 25 \ ^{\circ}\text{C} \\ I_{DS} = 0.69 \text{ mA}, \ V_{DS} = 10 \text{ V}, \ T_{j} = 125 \ ^{\circ}\text{C} \end{array}$ |

| Gate-source reverse clamping voltage | V <sub>GS</sub> , clamp | -          | -          | -8         | V                      | I <sub>GSS</sub> <sup>1</sup> = -1 mA, T <sub>j</sub> =25 °C                                                                                                                                                           |

| Gate resistance                      | R <sub>G,int</sub>      | -          | 0.80       | -          | Ω                      | LCR impedance measurement                                                                                                                                                                                              |

#### Table 14 Dynamic characteristics GaN switches

| Parameter                                                 | Parameter Symbol Valu |      | Value | s    | Unit | Note or Test Condition                                   |  |

|-----------------------------------------------------------|-----------------------|------|-------|------|------|----------------------------------------------------------|--|

|                                                           |                       | Min. | Тур.  | Max. |      |                                                          |  |

| Input capacitance                                         | Ciss                  | -    | 100   | -    | pF   | $V_{GS} = 0 V, V_{DS} = 400 V; f = 1MHz$                 |  |

| Output capacitance                                        | Coss                  | -    | 19.0  | -    | pF   | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 400 V; f = 1MHz |  |

| Reverse transfer capacitance                              | Crss                  | -    | 0.1   | -    | pF   | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 400 V; f = 1MHz |  |

| Effective output capacitance, energy related <sup>2</sup> | C <sub>o(er)</sub>    | -    | 21.1  | -    | pF   | $V_{GS} = 0 V$ , $V_{DS} = 0$ to 400 V                   |  |

| Effective output capacitance, time related <sup>3</sup>   | C <sub>o(tr)</sub>    | -    | 27.1  | -    | pF   | $V_{GS} = 0 V, V_{DS} = 0 \text{ to } 400 V$             |  |

| Output charge                                             | Q <sub>oss</sub>      | -    | 10.8  | -    | nC   | V <sub>DS</sub> = 0 to 400 V                             |  |

<sup>1</sup> Gate-Source leakage current

<sup>2</sup>  $C_{o(er)}$  is a fixed capacitance that gives the same stored energy as  $C_{oss}$  while  $V_{DS}$  is rising from 0 to 400 V

$<sup>3~</sup>C_{\text{o}(tr)}$  is a fixed capacitance that gives the same charging time as  $C_{\text{oss}}$  while  $V_{\text{DS}}$  is rising from 0 to 400 V

| Parameter                     | Symbol                       | Values |      |      | Unit | Note/Test Condition                             |

|-------------------------------|------------------------------|--------|------|------|------|-------------------------------------------------|

|                               |                              | Min.   | Тур. | Max. |      |                                                 |

| Source-Drain reverse voltage  | VSD                          | -      | 2.2  | 2.5  | V    | $V_{GS} = 0V, I_{SD} = 2.1 A$                   |

| Pulsed current, reverse       | I <sub>S,pulse</sub>         | -      | -    | 15.8 | A    | I <sub>G</sub> = 6.9 mA                         |

| Reverse recovery charge       | Q <sub>rr</sub> <sup>1</sup> | -      | 0    | -    | nC   | I <sub>SD</sub> = 2.1 A, V <sub>DS</sub> = 400V |

| Reverse recovery time         | t <sub>rr</sub>              | -      | 0    | -    | ns   |                                                 |

| Peak reverse recovery current | Irrm                         | -      | 0    | -    | A    |                                                 |

### Table 15 Reverse conduction characteristics

#### Table 16Dynamic Characteristics² (see Figure 4, Figure 5)

| Parameter                                           | Symbol                                                   |          | Values   |        | Unit     | Note or Test<br>Conditions |

|-----------------------------------------------------|----------------------------------------------------------|----------|----------|--------|----------|----------------------------|

|                                                     |                                                          | Min.     | Тур.     | Max.   |          |                            |

| INL to SW propagation delay "on"                    | <b>t</b> PDonL                                           | -        | 47       | -      | ns       | $R_{tr} = 50 \Omega$       |

| INL to SW propagation delay "off"                   | t <sub>PDoffL</sub>                                      | -        | 47       | -      | ns       | $I_{load} = 2 A$           |

| Propagation delay matching high/low-side            | $\Delta t_{	extsf{PDonLH}}$ $\Delta t_{	extsf{PDoffLH}}$ | -5<br>-5 | -        | 5<br>5 | ns<br>ns |                            |

| ENABLE to SW propagation delay                      | tpd_dis_on,<br>tpd_dis_off                               | -        | 70<br>70 | -      | ns<br>ns |                            |

| Rise time SW                                        | t <sub>rise</sub>                                        | -        | 6        | -      | ns       | 10 % to 90 %               |

| Fall time SW                                        | t <sub>fall</sub>                                        | -        | 5        | -      | ns       | 90 % to 10 %               |

| Minimum input pulse width that changes output state | tpw                                                      | -        | 18       | -      | ns       | -                          |

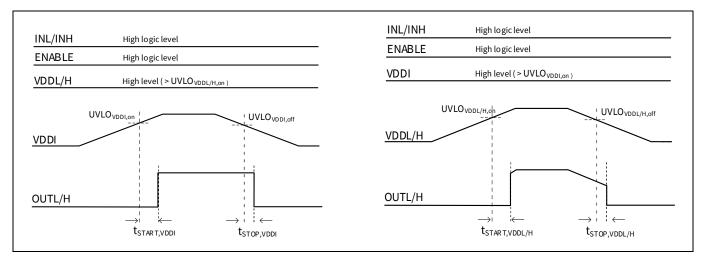

| Input-side start-up time <sup>2</sup>               | tstart,vddi                                              | -        | 7        | -      | μs       | see Figure 6               |

| Input-side deactivation time <sup>2</sup>           | tstop,vddi                                               | -        | 255      | -      | ns       | see Figure 6               |

| Input-side deactivation time <sup>2</sup>           | tstart,vddl/h                                            | -        | 5        | -      | ns       | see Figure 6               |

| Output-side deactivation time <sup>2</sup>          | tstop,vddl/h                                             | -        | 110      | -      | ns       | see Figure 6               |

$<sup>^{\</sup>rm 1}$  Excluding  $Q_{\rm oss}$

<sup>&</sup>lt;sup>2</sup> Verified by design / characterization, not tested in production

| Par                                         | ameter                                                      | Symbol                   | Value | Unit            | Note or Test Conditions                                                                 |

|---------------------------------------------|-------------------------------------------------------------|--------------------------|-------|-----------------|-----------------------------------------------------------------------------------------|

|                                             | Max. Input-to-DH voltage                                    | VInDH                    | >1200 | VDC             | production test > 10 ms                                                                 |

| Functional isolation                        | Max. Input-to-SW<br>voltage                                 | Vinsw                    | >600  | V <sub>DC</sub> |                                                                                         |

|                                             | Max. Input-to-SL voltage                                    | VInSL                    | >100  | VDC             |                                                                                         |

|                                             | Nominal package<br>clearance                                | CLR                      | 1.9   | mm              | shortest distance over air, from<br>any input pin to any high-side<br>output pin        |

| Package<br>characteristics                  | Nominal package<br>creepage                                 | CRP                      | 1.9   | mm              | shortest distance over surface,<br>from any input pin to any high-<br>side output pin   |

|                                             | Comparative Tracking<br>Index of package mold               | CTI                      | >400  | V               | according to DIN EN 60112<br>(VDE 0303-11)                                              |

|                                             | Material group                                              | -                        | П     | -               | according to IEC 60112                                                                  |

|                                             | Static Common Mode<br>Transient Immunity <sup>12</sup>      | CM <sub>Static,H</sub>   | 300   | V/ns            | $V_{CM} = 1500 \text{ V}; \text{ INL, INH}$<br>tied to $V_{DDI}$ (logic<br>high inputs) |

| Common Mode<br>Transient Immunity<br>(CMTI) |                                                             | CM <sub>Static,L</sub>   | 300   | V/ns            | $V_{CM} = 1500 \text{ V}; \text{INL, INH}$<br>tied to GNDI (logic<br>high inputs)       |

|                                             | Dynamic Common<br>Mode Transient<br>Immunity <sup>1 3</sup> | [CM <sub>Dynamic</sub> ] | 300   | V/ns            | $V_{\rm CM}$ = 1500 V; dynamic INL,<br>INH (10 MHz square wave)                         |

#### Table 17Isolation specifications

<sup>&</sup>lt;sup>1</sup> minimum slew rate of a common mode voltage at which the output signal is disturbed

<sup>&</sup>lt;sup>2</sup> parameters verified by characterization according to VDE0884-11 standard definitions and test-methods

<sup>&</sup>lt;sup>3</sup> verified by characterization with ground reference for the common mode pulse generator connected to the coupler intput-side ground to reflect real applications requirements

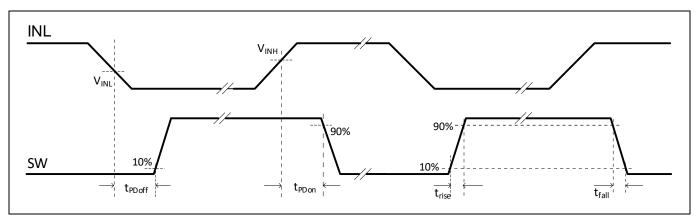

### 3.5 Timing diagrams and test circuit

**Figure 4** depicts rise, fall and delay times measured at the GaN half-bridge output SW. **Figure 5** shows the associated test circuit. The power stage is operated in a boost configuration at a constant current  $I_{load}$ . In this so-called double-pulse arrangement  $I_{load}$  is determined by the high-voltage supply (400 V), the output inductance and the length of the first "on"-phase of the INL-signal. The specified delay and transient times are related to an  $I_{load}$  value of 2 A (particularly the "off" transient strongly depends on this current). INH need not be switched for this measurement.

Figure 4 Propagation delay, rise and fall time

Figure 5 Test circuit

Figure 6 UVLO behavior, start-up and deactivation time (unloaded output)

# **4 Driving CoolGaN<sup>™</sup> HEMTs**

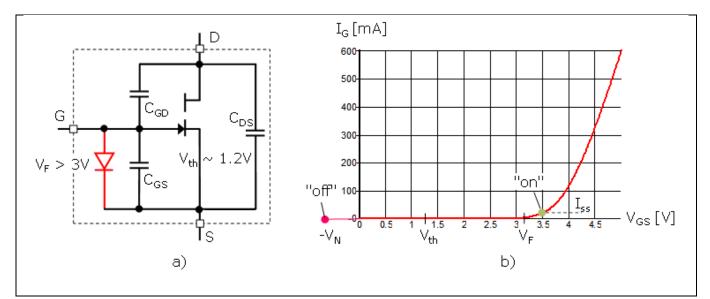

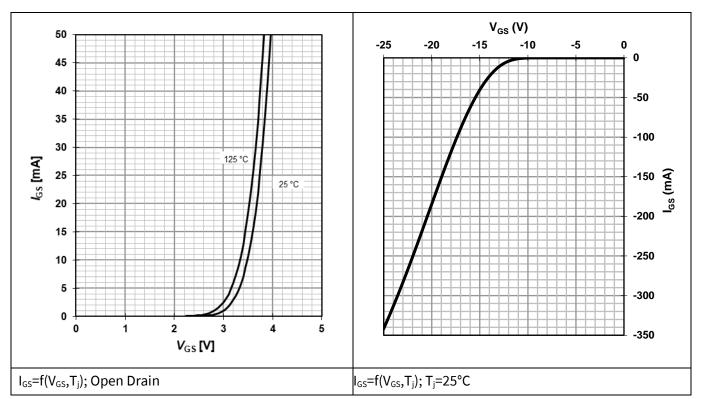

Although Gallium Nitride High Electron Mobility Transistors (GaN HEMTs) with ohmic connection to a pGaN gate are robust enhancement-mode ("normally-off") devices, they differ significantly from MOSFETs. The gate module is not isolated from the channel, but behaves like a diode with a forward voltage V<sub>F</sub> of 3 to 4 V. Equivalent circuit and typical gate input characteristic are given in **Figure 7**. In the steady "on" state a continuous gate current is required to achieve stable operating conditions. The switch is "normally-off", but the threshold voltage V<sub>th</sub> is rather low (~ +1 V). This is why in many applications a negative gate voltage -V<sub>N</sub>, typically in the range of several Volts, is required to safely keep the switch "off" (**Figure 7b**).

Figure 7 Equivalent circuit (a) and gate input characteristics (b) of typical normally-off GaN HEMT

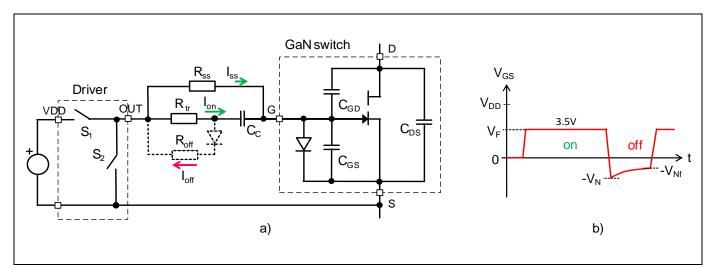

Obviously the transistor in **Figure 7** cannot be driven like a conventional MOSFET due to the need for a steady-state "on" current I<sub>ss</sub> and a negative "off" voltage  $-V_N$ . While an I<sub>ss</sub> of a few mA is sufficient, fast switching transients require gate charging currents I<sub>on</sub> and I<sub>off</sub> in the 1 A range. To avoid a dedicated driver with 2 separate "on" paths and bipolar supply voltage, the solution depicted in **Figure 8** is usually chosen, combining a standard gate driver with a passive RC circuit to achieve the intended behavior. The high-current paths containing the small gate resistors R<sub>on</sub> and R<sub>off</sub>, respectively, are connected to the gate via a coupling capacitance C<sub>c</sub>. C<sub>c</sub> is chosen to have no significant effect on the dynamic gate currents I<sub>on</sub> and I<sub>off</sub>. In parallel to the high-current charging path the much larger resistor R<sub>ss</sub> forms a direct gate connection to continuously deliver the small steady-state gate current I<sub>ss</sub>. In addition, C<sub>c</sub> can be used to generate a negative gate voltage. Obviously, in the "on"-state C<sub>c</sub> is charged to the difference of driver supply V<sub>DD</sub> and diode voltage V<sub>F</sub>. When switching off, this charge is redistributed between C<sub>c</sub> and C<sub>Gs</sub> and causes an initial negative V<sub>Gs</sub> of value:

$$V_N = \frac{C_C \cdot (V_{DD} - V_F) - Q_G}{C_C + C_{GS}}$$

(2)

with  $Q_G$  denoting the total gate charge.  $V_N$  can thus be controlled by proper choice of  $V_{DD}$  and  $C_C$ . During the "off" state the negative  $V_{GS}$  decreases, as  $C_C$  is discharged via  $R_{SS}$ . The associated time constant cannot be chosen independently, but is related to the steady-state current and is typically in the 1  $\mu$ s range. The negative gate voltage at the end of the "off" phase ( $V_{Nf}$  in **Figure 8b**) thus depends on the "off" duration. It lowers the effective driver voltage for the following switching-on event, resulting in a slight dependence of switching dynamics on frequency and duty cycle. However, in most applications the impact of this effect is negligible.

Another situation requires attention, too. If there is by any reason a longer period with both switches of a half-bridge in "off"-state (e.g. during system start-up, burst mode operation etc.), both capacitors  $C_{\rm C}$  will be discharged. That

means, for the first switching pulse after such an extended non-switching period no negative voltage is available. To avoid instabilities due to spurious turn-on effects in such a situation,  $C_c$  should not be chosen lower than 1 nF.

Figure 8 Equivalent circuit of GaN switch with RC gate drive (a) and gate-to-source voltage V<sub>GS</sub> (b)

In the topology of **Figure 8** often a single resistor  $R_{tr}$  can be used for setting the maximum transient charging and discharging current. If this is not acceptable by any reason, an additional resistor  $R_{off}$  with series diode in parallel with  $R_{tr}$  can be used to realize independent gate impedances for the "on" and "off" transient, respectively.

All relevant driving parameters are easily programmable by choosing  $V_{DD}$ ,  $R_{ss}$ ,  $R_{tr}$ ,  $R_{off}$  and  $C_C$  according to the relations

$$V_N = \frac{C_C \cdot (V_{DD} - V_F) - Q_G}{C_C + C_{GS}}$$

$$I_{ss} = \frac{V_{DD} - V_F}{R_{ss}}, \qquad I_{on,max} \sim \frac{V_{DD} - V_{Nf}}{R_{tr}}, \qquad I_{off,max} \sim \frac{(V_{th} + V_N) \cdot (R_{off} + R_{tr})}{R_{off} \cdot R_{tr}}$$

The main guidelines for dimensioning gate drive parameters are as follows:

- $V_N$  must always be positive; a target value of 2 V in soft-switching and 4 V to 5 V in hard-switching systems is recommended

- The target value of Iss is around 3 mA, Rss has to be chosen accordingly

- Rtr sets the transient speed for a hard switching "on" event. Due to the low gate charge, values above 50 Ω typically do not result in significant benefits. For soft switching systems Rtr is anyway uncritical.

- If a separate R<sub>off</sub> is used, it should guarantee sufficient damping of oscillations in the gate loop.

For a given driving voltage the values for the gate drive components can now be derived from equations (3).  $V_{DD} = 8 V$ , for example, yields

- Cc = 1.2 nF

- $R_{ss} = 2 k\Omega$

- R<sub>tr</sub> = 27 ... 68 Ω

- $R_{off} = 10 \Omega$  (if used)

For more information regarding how to drive GaN HEMT refer to [2] [3].

(3)

# 5 Typical characteristics

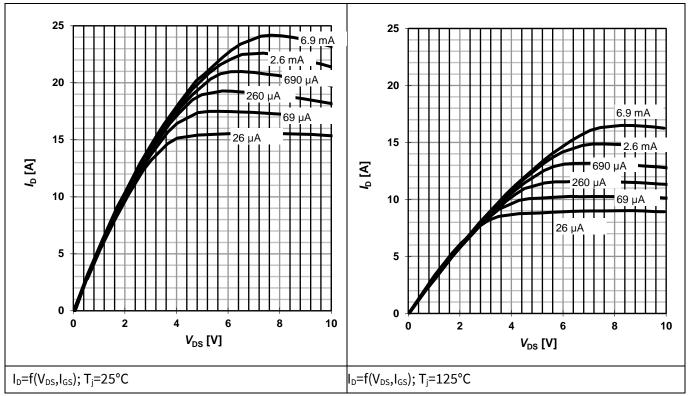

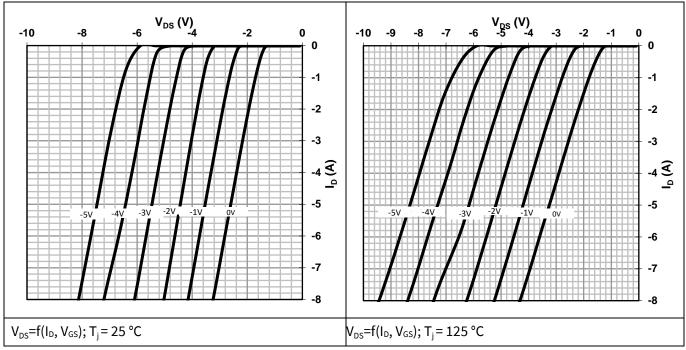

# 5.1 GaN switch characteristics

The following graphs refer to a single GaN switch.

Figure 9 Typical output characteristics

Figure 10 Typical drain-source on-resistance

Figure 11 Typical gate characteristics forward and reverse

Figure 12 Output characteristic  $I_{ds}$  ( $V_{ds}$ ) in reverse operation (parameter  $V_{gs}$ )

Figure 13 Safe Operating Area (SOA)

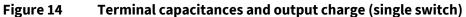

Figure 15 Typical output energy (single switch)

## 5.2 Gate driver characteristics

Figure 16 Supply current VDDI

Figure 18 Logic input thresholds and V<sub>DDI</sub> UVLO

Figure 19 VDDL/H UVLO

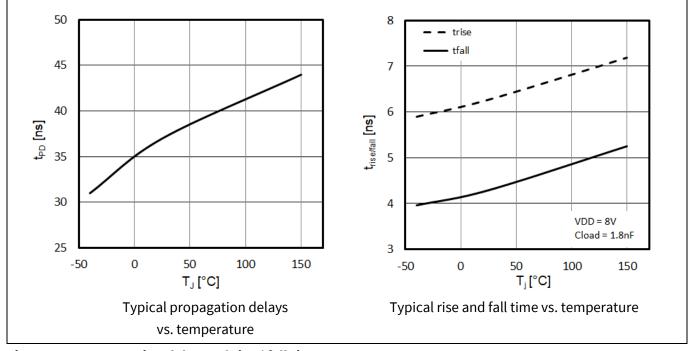

Figure 20 Propagation delay and rise / fall times

# 6 Application circuit

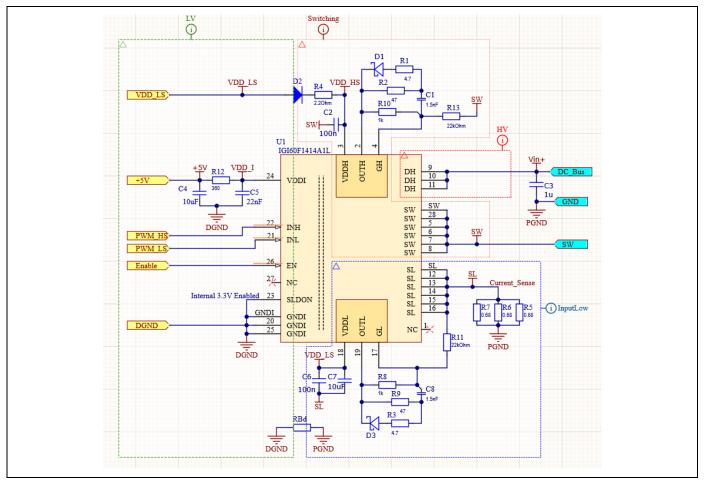

In Figure 21 a typical application example is given with IGI60F2020A1L operated in an actively clamped flyback topology.

In this application the recommended values for the gate drive circuit are as follows:

$V_{DD} = 8 V$

$C_{C} = 1.2 \text{ nF}$

$R_{ss} = 2 \ k\Omega$

$R_{tr} = 27 \dots 68 \ \Omega$

Figure 21 Application Circuit (active clamp flyback converter)

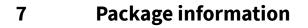

Figure 22 TIQFN-28-1 8x8 package outline and footprint

# 8 Layout guidelines

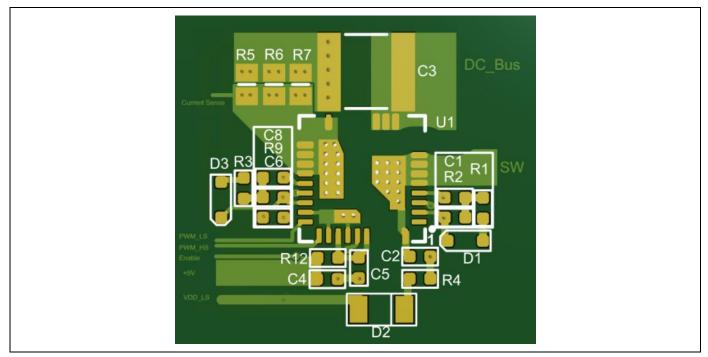

Figure 23 shows the suggested arrangement of the power stage and the external components on the PCB based on the schematic shown in the Figure 24.

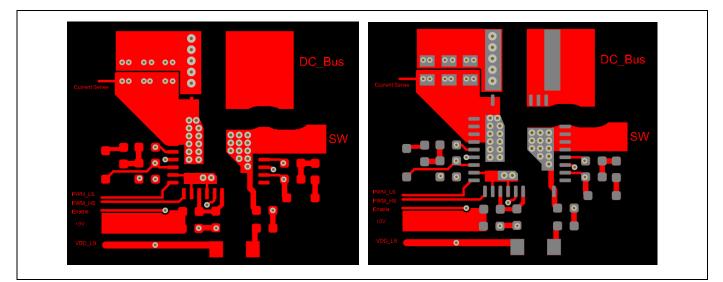

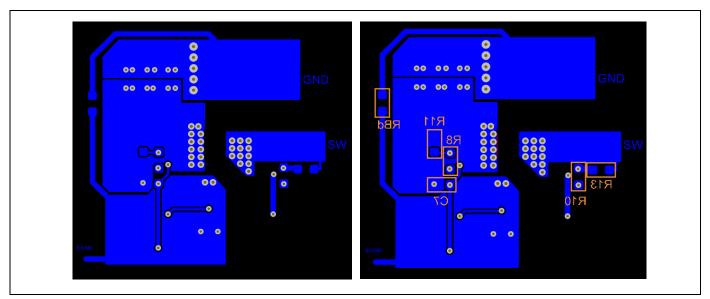

Figure 25 and Figure 26 show the top and bottom layer of the PCB. The following layout recommendations should be considered:

- 1. On the exposed pads' landing area place vias with 0.3mm hole size with <0.7mm space (center to center)

- 2. Use solder mask expansion of 0.05~0.075mm for the chipset footprint pins and pads

- 3. Place and align the GND trace (PGND node for power return) beneath the DC bus trace on the top layer to minimize the inductance loop in the power path.

- For the low voltage controller reference (DGND) on the PGND trace select a location free of any switching current to avoid switching-induced noise in DGND (do not connect the DGND trace to any trace which connects the bypass cap to CoolGaN<sup>™</sup>).

Figure 23 CoolGaN<sup>™</sup> IPS external component placement on the PCB

Figure 24 CoolGaN<sup>™</sup> IPS circuitry with external passive components

Refer to Appendix (I) to download the footprint and the PCB example for Altium. Also, a complete PCB project with this product is available in the <u>CoolGaN<sup>™</sup> Half-Bridge IPS Evaluation Board</u> project.

Figure 25 Top layer of the PCB (trace on the left and top solder paste layer on the right)

Figure 26 Bottom layer of the PCB - top view (Trace on the left and silk mask on the right)

# 9 Appendix

PCB footpriont and Altium file for the reference PCB design can be found in the <u>CoolGaN<sup>™</sup> Half-bridge</u>

<u>IPS</u> webpage (product registration is needed to access the design files)

#### II. Related Links

IFX CoolGaN<sup>™</sup> webpage: <u>www.infineon.com/why-coolgan</u>

IFX CoolGaN<sup>™</sup> reliability white paper: <u>www.infineon.com/gan-reliability</u>

IFX CoolGaN<sup>™</sup> applications information:

www.infineon.com/gan-in-server-telecom

www.infineon.com/gan-in-wirelesscharging

www.infineon.com/gan-in-adapter-charger

# 10 References

- [1] <u>CoolGaN<sup>™</sup> application note</u>

- [2] <u>Driving CoolGaN<sup>™</sup> 600 V high electron mobility transistors</u>

- [3] Quick-reference guide to driving CoolGaN<sup>™</sup> GIT HEMTs 600V

# **Revision history**

| Document version | Date of release | Description of changes                            |

|------------------|-----------------|---------------------------------------------------|

| V1.0             | 2023-02-14      | 1 <sup>st</sup> version of final datasheet        |

| V1.1             | 2023-05-05      | Products overview update with marking information |

|                  |                 |                                                   |

**Other Trademarks** All referenced product or service names and trademarks are the property of their respective owners.

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: <u>erratum@infineon.com</u>

Published by Infineon Technologies AG 81726 München, Germany © 2021 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (<u>www.infineon.com</u>).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

The Infineon Technologies component described in this Data Sheet may be used in life-support devices or systems and/or automotive, aviation and aerospace applications or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support, automotive, aviation and aerospace device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems reintended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.