# Kompakte und leistungsfähige 600-V-Halbbrücken-Treiber

## Gate-Treiber für effiziente und platzsparende Lösungen

Produktentwickler im Bereich der Antriebstechnik in Haushaltsgeräten und der Unterhaltungselektronik sind damit konfrontiert, permanent den Wirkungsgrad der Geräte zu erhöhen, bei gleichzeitig immer kleineren Abmessungen. Wichtige Aspekte beim Stromversorgungsdesign sind dabei das Schaltverhalten und die Leistungsverluste von neuen Leistungs-MOSFETs. Dafür bietet die neueste Coolmos-Generation signifikant reduzierte Gate-Ladungen, während der Einsatz von neuen, dedizierten Treiber-ICs für eine weitere Optimierung sorgt.

Autoren: Jinsheng Song, Dr. Oliver Hellmund, Dr. Wolfgang Frank, Michael Wendt

**M**it der monolithisch integrierten, sehr schnellen Bootstrap-Funktion setzt die neueste Generation der 2EDL Eicedriver Maßstäbe für Treiber-ICs mit mehr als 2 A Ausgangstrom. Derzeit bestehen die 600-V-Gatetreiber-ICs aus zwei Bausteingroupen mit verschiedenen Varianten und Ausgangsströmen von 0,5 beziehungsweise 2,3 A für Anwendungen sowohl mit IGBTs als auch MOSFETs. Zudem eröffnet Infineon mit diesen Treibern ein neues Bauelementsegment, die Klasse Eicedriver Compact („C“) für industrielle und Multimarket-Anwendungen.

Die 2EDL-Halbbrückentreiber-ICs stellen eine neue Klasse von Gate-Treibern mit integrierter Bootstrap-Funktion für die High-Side-Versorgung dar. Bisher sind nur wenige Bauelemente dieser Art auf dem Markt, da eine spürbare Verringerung der Bootstrap-Spannung bei niedrigen Tastverhältnissen des Energiewandlers sowie eine zusätzliche hohe Leistungsaufnahme des ICs bei hohen Schaltfrequenzen zu bewerkstelligen sind. Daher waren bisherige Bauelemente meist auf Low-power-Antriebe im Consumer-Bereich begrenzt. Diese haben üblicherweise eine Sperrspannung von 600 V. Andere Halbbrücken-ICs, die nicht über eine integrierte Bootstrap-Diode verfügen, werden für Low-End-Schaltnetzteile eingesetzt. Da diese über keine integrierte Bootstrap-Funktion verfügen, haben diese Produkte ein etwas besseres Temperatur-

Budget aufgrund der geringeren Leistungsaufnahme gegenüber den Bauteilen mit integrierter Bootstrap-Funktion.

Eine integrierte Bootstrap-Funktion bietet jedoch signifikante Vorteile: einfacheres Layout, weniger Plattenfläche und eine günstigere Bauteilplatzierung in Bezug auf den Abstand zum Gate-Anschluss des Leistungstransistors. Damit wird die elektromagnetische Verträglichkeit (EMV) verbessert und das Schaltverhalten optimiert, was zu geringeren Schaltverlusten führt. Vor diesem Hintergrund hat Infineon das neue Konzept für Halbbrücken-Gatetreiber-ICs entwickelt, das für die Anforderungen im Bereich der Consumer-Elektronik einschließlich der Antriebe in Haushaltgeräten sowie für Stromversorgung und Computing prädestiniert ist. Dabei unterstützen die Halbbrückentreiber-ICs der 2EDL-Familie die wichtigsten Trends in Low-power-Anwendungen, wie einen einfachen Einsatz und reduzierte Materialkosten, bei gleichzeitig umfassender Funktionalität.

### Neues Konzept für Halbbrücken-Gatetreiber-ICs

Die Bausteine mit 0,5 A sind im DSO8- oder DSO14-Gehäuse verfügbar, während die Varianten mit 2,3 A im DSO14 erhältlich sind. Alle Gehäuse sind RoHS-kompatibel sowie blei- und halogenfrei. Bausteine im DSO8-Gehäuse bieten einen Floating-High-Side-Treiber mit Basis-Funktionen. Sehr gut für Schaltnetzteile eignet sich zum Beispiel der 2EDL05I06BF. Er verfügt über keine Totzeit-

### Auf einen Blick

#### Für IGBT und MOSFET

Die neue 2EDL-Halbbrücken-Gate-Treiber-Familie von Infineon ist Teil der Eicedriver-Compact-Familie. Das Treiber-IC-Konzept für Halbbrücken ist vorzugsweise für den Bereich der Antriebstechnik von Haushaltsgeräten, aber auch für Schaltnetzteile und Computer vorgesehen. Sie wurden für die zwei am häufigsten eingesetzten Transistor-Technologien IGBT und MOSFET entwickelt. Die integrierte Bootstrap-Diode hat einen kleinen Serienwiderstand und sie erlaubt dadurch einen weiten Arbeitsbereich der Pulswerte. Die Verlustleistung der Bootstrap-Diode ist minimiert. Spezielle Funktionen wie die asymmetrische Unterspannungsabschaltung und die aktive Abschaltung insbesondere für IGBTs helfen dabei, ein optimales Ergebnis zu erreichen.

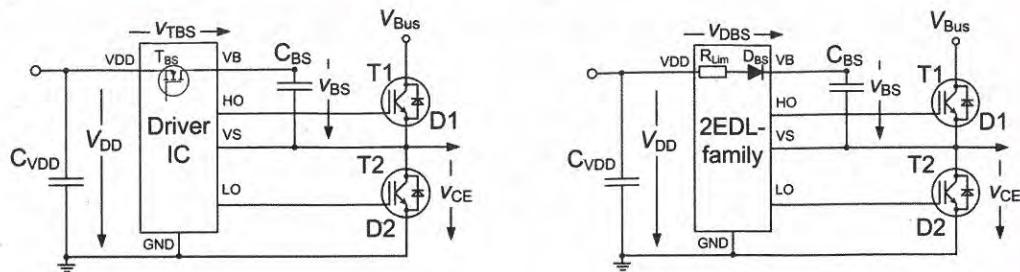

Bild 1: Bootstrap-Schaltung für eine Halbbrücke:

links ein konventioneller FET als Bootstrap-Schalter

und rechts mit hochleistungsfähiger, ultraschneller

Bootstrap-Diode sowie die verfügbaren Gehäuse der

2EDL-Familie.

und Interlock-Funktion, sodass sowohl der High-Side- als auch der Low-Side-Ausgang gleichzeitig aktiviert werden können.

Den vollen Funktionsumfang bieten zwei Bausteine mit dem hohen Ausgangsstrom von 2,3 A im DSO14-Gehäuse. Zu den Features gehören eine Enable-Funktion, Fehlerdiagnose sowie ein separater Rückpfad für den Gate-Strom (Power Ground) einschließlich Überstromschutz. Mit diesen Varianten können alle Applikationen adressiert werden, die eine höhere Integration und Safety-Anforderungen erfordern.

### Integrierte Bootstrap-Diode

Die integrierte Bootstrap-Funktion wird typischerweise wie in Bild 1 links dargestellt mittels Hochvolt-MOSFET-Strukturen realisiert entsprechend  $T_{BS}$  in Bild 1. Diese MOSFET-Strukturen werden in Phase mit dem Low-Side-Transistor  $T_2$  an- und ausgeschaltet. Das ist ein kritischer Punkt, da für den Treiber-IC weder die Verzögerungszeiten des Leistungstransistors noch der Leistungsfaktor des Motors bekannt sind. Daher muss die Ansteuerung des Bootstrap-FET diese mit zusätzlichen Bootstrap-Verzögerungen berücksichtigen. Diese Verzögerungen verringern die verfügbare Zeit für das Boot-

strapping, sodass die Bootstrap-Spannung weiter reduziert wird.

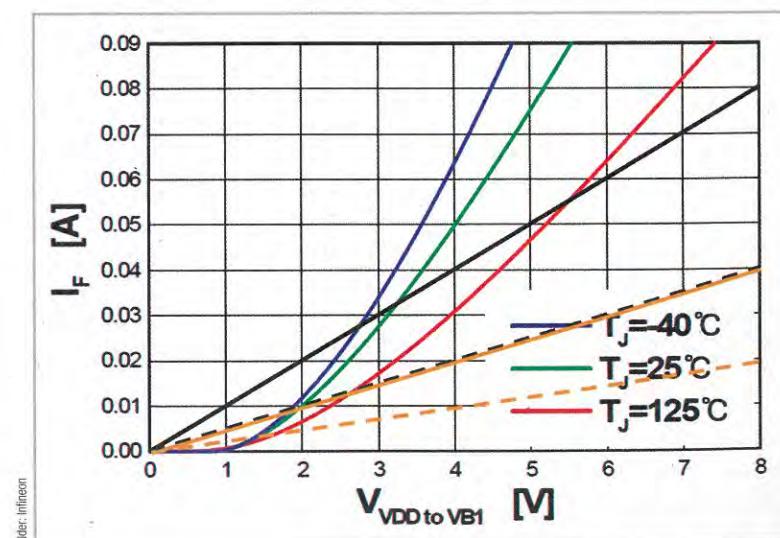

Eine weitere Einschränkung beim Einsatz eines MOSFETs für das Bootstrapping ist die Temperaturabhängigkeit des MOSFETs. Typischerweise verdoppelt sich der Durchlasswiderstand von MOSFETs, wenn die Sperrsichttemperatur um 100 °C zunimmt. Das heißt, dass sich die dargestellte Situation nochmals verschlechtert. Auch führt der höhere Durchlasswiderstand  $R_{DS(on)}$  zu einer höheren Leistungsaufnahme des Treiber-ICs und limitiert den sicheren Betriebsbereich (SOA) in Bezug auf die Schaltfrequenz und die Gate-Ladung. Ein Äquivalent dazu ist der als Serienwiderstand dargestellte Bahnwiderstand  $R_{Lim}$  der Bootstrap-Diode. Wie man Bild 2 entnehmen kann, ist die integrierte Bootstrap-Diode besser als herkömmliche Bootstrap-Funktionen sobald die Vorwärts-Charakteristik der Diode über der des MOSFETs liegt. Das ist der Fall für einen Vorwärtsstrom von etwa 5 bis 10 mA bei erhöhten Temperaturen.

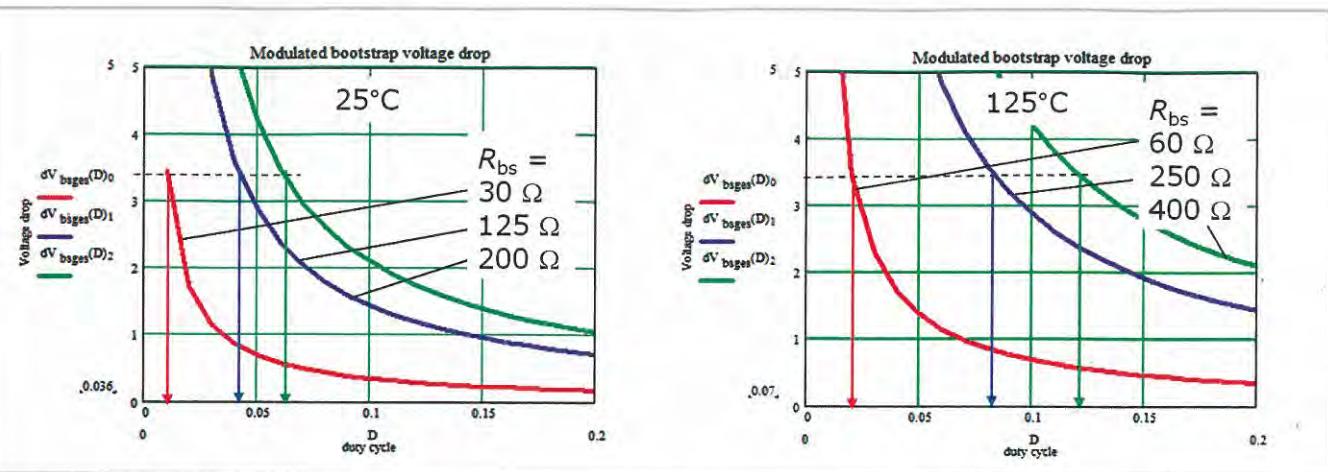

Die Effekte der Ausgangs-Charakteristika sind ersichtlich, stellt man die nominale Spannungsreduzierung der Bootstrap-Kondensatorspannung dem Tastverhältnis gegenüber. Es wird eine Halbbrückenkonfiguration stellvertretend für

Bild 2: Vergleich der Durchlasskennlinien einer Bootstrap-Diode mit Bahnwiderstand  $R_{Lim}$  und eines MOSFETs mit  $R_{ds(on)} = 100 \Omega$  (schwarz:  $T_J = 25^\circ\text{C}$ , gestrichelt:  $T_J = 125^\circ\text{C}$ ) und  $R_{ds(on)} = 200 \Omega$  (orange:  $T_J = 25^\circ\text{C}$ , gestrichelt:  $T_J = 125^\circ\text{C}$ ).

Bild 3: Berechnung des Spannungsabfalls an dem Bootstrap-Kondensator (Steady State) gegenüber dem Tastverhältnis für einen Abwärtsregler (Buck Converter) in Abhängigkeit des Durchlasswiderstands ( $R_{DS(on)}$  beziehungsweise  $R_{LIM}$ ). Links sind die Bedingungen bei einer Sperrsichttemperatur  $T_j = 25^\circ\text{C}$  dargestellt und rechts für  $T_j = 125^\circ\text{C}$ .

eine Schaltnetzteil-Topologie gewählt. Ein niedriges Tastverhältnis beim Low-Side-Transistor oder der -Diode führt zu einer nicht vollständigen Wiederaufladung des Bootstrap-Kondensator  $C_{BS}$  (siehe Bild 1). Als Folge davon sinkt die Bootstrap-Spannung  $V_{BS}$ , bis ein neuer eingeschwungener Betriebszustand (Steady State) in Bezug auf die Versorgungsspannung des Treiber-ICs erreicht wird. Bild 3 zeigt die Betriebsbedingungen für eine Schaltfrequenz  $f_p = 20\text{ kHz}$  und einen Bootstrap-Kondensator mit  $C_{BS} = 22\text{ }\mu\text{F}$ .

### Stabil bei hohen Sperrsicht-Temperaturen

Im linken Teil von Bild 3 sind die Bedingungen bei einer Sperrsichttemperatur  $T_j = 25^\circ\text{C}$  dargestellt und auf der rechten Seite für  $T_j = 125^\circ\text{C}$ . Das vorgeschlagene Treiberkonzept der 2EDL Eicedriver bietet einen Bootstrap-Widerstand  $R_{LIM}$  von  $30\text{ }\Omega$  bei einer Sperrsicht-Temperatur  $T_j = 25^\circ\text{C}$ . Andere Konzepte liegen hier bei 125 oder sogar  $200\text{ }\Omega$ . Aus Vereinfachungsgründen wird angenommen, dass sich der Bootstrap-Widerstand  $R_{LIM}$  ebenfalls alle  $100^\circ\text{C}$  verdoppelt. Es ist zu beachten, dass der Bootstrap-Kondensator keinen Einfluss auf die in Bild 3 dargestellten Diagramme hat. Er beeinflusst nur die Übergangsphase von einem Bias-Punkt zum anderen. Dagegen ist der Einfluss des geringen Widerstands des neuen 2EDL Eicedriver signifikant. Das neue Treiberkonzept ist im Vergleich zu Standardkomponenten viel stabiler bei hohen Sperrsicht-Temperaturen. Das nutzbare Tastverhältnis kann mit den neuen 2EDL-Treibern bis zu einem Prozent herunter gehen, ohne dass die Unterspannungs-Abschaltung aktiviert wird.

Andere Treiber erlauben keine Tastverhältnisse von weniger als vier Prozent ( $R_{BS} = 125\text{ }\Omega$ ) oder sieben Prozent ( $R_{BS} = 200\text{ }\Omega$ ). Das heißt, dass Anwendungen, die den Betrieb mit sehr geringen Tastverhältnissen erfordern, diese Treiber nicht einsetzen können. Zu diesen Anwendungen zählen hart schaltende Schaltnetzteile unter hohen Lasten oder Antriebssysteme, die bei feldorientierter Regelung mit hohen Drehmomenten bei geringen Drehgeschwindigkeiten arbeiten. In diesen Beispielen geht dann die Steuerung in einen eingeschwungenen oder quasi Steady-State-Betrieb im Bereich des kritischen Tastverhältnisses.

### Asymmetrische Unterspannungs-Abschaltung

Die 2EDL-Eicedriver-Familie unterstützt mit speziellen Features auch den Betrieb mit IGBTs. Andere, auf dem Markt verfügbare Treiber-ICs unterstützen zum Beispiel mit der UVLO-Funktion (Under Voltage Lockout) nur MOSFETs. Die Gate-Schwellwert-

spannung von MOSFETs (meist 3 V) erlaubt im Vergleich zu IGBTs (4,6 bis 5 V) den Betrieb mit geringeren Gate-Spannungen, was sich auch in den UVLO-Spannungen widerspiegelt. Andererseits ist es aber gefährlich, IGBTs mit Treiber-ICs zu betreiben, die UVLO-Grenzen für MOSFETs bieten. Diese Grenzen sind so gering, dass der IGBT teilweise oder komplett in die Sättigung gehen kann. Das wiederum führt zu hohen Verlusten, zudem kann ein Betrieb in diesem Modus den IGBT schädigen. Daher ist es erforderlich, dass IGBTs nur mit Treibern angesteuert werden, die angepasste UVLO-Grenzen für IGBTs bieten.

Ein wichtiger Aspekt ist auch, dass die Auslegung der UVLO-Grenze die integrierten Bootstrap-Dioden unterstützt. Diese weisen einen relativ hohen Abfall der Vorwärtsspannung auf, der zur Reduzierung der Bootstrap-Spannung im Vergleich zur Versorgungsspannung  $V_{DD}$  beiträgt (siehe auch Bild 3). Die statische Bootstrap-Spannung ergibt sich aus:

$$V_{BS} = V_{DD} - V_{DBS} - V_{CE}$$

Dabei stellt  $V_{CE}$  die Transistorspannung T2 des Low-Side-Transistors in einer Halbbrücken-Konfiguration nach Bild 1 dar. Aus der Formel ist ersichtlich, dass der High-Side-Ausgang (HO) eine kleinere Spannung erzeugt, da die Spannung  $V_{BS}$  an den IC-Anschlüssen  $V_B$  und  $V_S$  um die Werte  $V_{DBS}$  und  $V_{CE}$  reduziert wird. Allerdings ist es vorteilhaft, die UVLO für die High-Side-Versorgung  $V_{BS}$  zum selben Zeitpunkt wie die Low-Side-Versorgung  $V_{DD}$  zu aktivieren, um eine unzureichende Versorgung des High-Side-Gate zu vermeiden. Daher wird die Low-Side-UVLO auf einem um etwa 1 V höheren Wert als die High-Side-UVLO-Funktion ausgelöst. Dies erlaubt auch ein Verschieben der Abschaltgrenzwerte  $V_{CCUV}$  auf der Low-Side hin zu etwas höheren Werten. Das kann durch die Implementierung einer asymmetrischen UVLO erreicht werden, die verschiedene Werte für die Schwellwert-Spannungen auf der High- und Low-Side erlaubt.

Darüber hinaus ermöglichen die neuen Treiber-ICs auch die Filtrierung von UVLO-Ereignissen. Damit kann man verhindern, dass kurzzeitige Spannungsabfälle (in der Größenordnung von  $1,5\text{ }\mu\text{s}$ ) zu einem UVLO-Ereignis werden. So sind die neuen ICs robuster gegenüber Rauschen in den Versorgungsleitungen. (ah)

Die Autoren: Jinsheng Song, Dr. Oliver Hellmund, Dr. Wolfgang Frank und Michael Wendt arbeiten bei Infineon Technologies Deutschland.