## 64K ビット (8K × 8) シリアル (SPI) 車載用 F-RAM

### 特長

- 8K×8 構成として論理的に設計されたの 64K ビット強誘電体ランダム アクセス メモリ (F-RAM)

- 高いアクセス可能回数: 100兆( $10^{13}$ )回の読み出し／書き込み

- 121年のデータ保持 (データ保持期間およびアクセス可能回数の表を参照)

- NoDelay™ 書き込み

- 高い信頼性がある強誘電体プロセス

- 高速のシリアルペリフェラル インターフェース (SPI)

- 4MHz までの周波数

- シリアル フラッシュおよび EEPROM からの置き換え

- SPI モード 0 (0, 0) およびモード 3 (1, 1) をサポート

- 洗練された書き込み保護スキーム

- 書き込み保護 (WP) ピンを使ったハードウェアによる保護

- 書き込みディスエーブル命令を使用したソフトウェアによる保護

- アレイの 1/4、1/2、全体を対象としたソフトウェア ブロック保護

- 低消費電力

- 1MHz でのアクティブ電流 300 $\mu$ A

- +85°C での 10mA (typ) スタンバイ電流

- 動作電圧:  $V_{DD}=4.5V \sim 5.5V$

- 車載用拡張温度範囲:  $-40^{\circ}C \sim +125^{\circ}C$

- 8 ピン小型集積回路 (SOIC) パッケージ

- AEC Q100 グレード 1 準拠

- RoHS 準拠

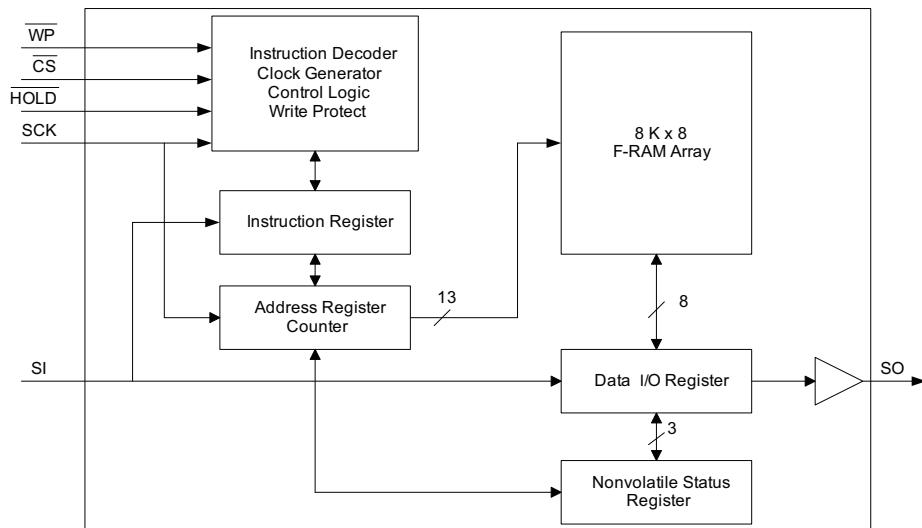

### 論理ブロック図

## 目次

|                           |    |

|---------------------------|----|

| ピン配置                      | 3  |

| ピンの機能                     | 3  |

| 概要                        | 4  |

| メモリーアーキテクチャ               | 4  |

| シリアルペリフェラル インターフェース –     |    |

| SPI バス                    | 4  |

| SPI 概要                    | 4  |

| SPI モード                   | 5  |

| 電源投入時から最初のアクセスまで          | 6  |

| コマンドの構成                   | 6  |

| WREN - 書き込みイネーブル ラッチのセット  | 6  |

| WRDI - 書き込みイネーブル ラッチのリセット | 6  |

| ステータス レジスタおよび書き込み保護       | 6  |

| RDSR - ステータス レジスタの読み出し    | 7  |

| WRSR - ステータス レジスタの書き込み    | 7  |

| メモリの動作                    | 8  |

| 書き込み動作                    | 8  |

| 読み出し動作                    | 8  |

| HOLD ピンの動作                | 9  |

| アクセス可能回数                  | 10 |

| 最大定格                      | 11 |

| 動作範囲                      | 11 |

| DC 電気的特性                  | 11 |

|                        |    |

|------------------------|----|

| データ保持期間およびアクセス可能回数     | 12 |

| AEC-Q100 車載用アプリケーションでの |    |

| F-RAM 製品寿命の例           | 12 |

| 静電容量                   | 12 |

| 熱抵抗                    | 12 |

| AC テスト条件               | 12 |

| AC スイッチング特性            | 13 |

| パワー サイクル タイミング         | 15 |

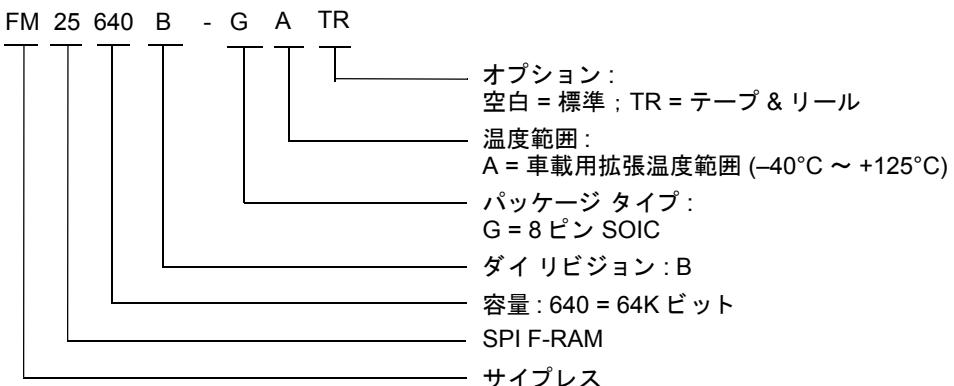

| 注文情報                   | 16 |

| 注文コードの定義               | 16 |

| パッケージ図                 | 17 |

| 略語                     | 18 |

| 本書の表記法                 | 18 |

| 測定単位                   | 18 |

| 改訂履歴                   | 19 |

| セールス、ソリューションおよび法律情報    | 20 |

| ワールドワイドな販売と設計サポート      | 20 |

| 製品                     | 20 |

| PSoC® ソリューション          | 20 |

| サイプレス開発者コミュニティ         | 20 |

| テクニカル サポート             | 20 |

## ピン配置

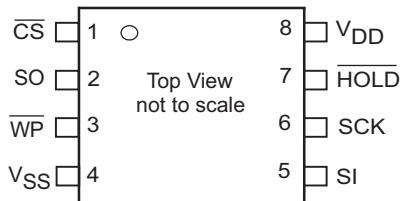

図 1. 8 ピン SOIC ピン配置

## ピンの機能

| ピン名               | 入出力 | 説明                                                                                                                                                                                                                                                                      |

|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS                | 入力  | チップ セレクト。このアクティブ LOW 入力でデバイスを起動させる。HIGH になった場合、デバイスは低消費電力のスタンバイ モードに入り、他の入力を無視し、出力をトライステートにする。LOW になった場合、デバイスが SCK 信号を内部でアクティブにする。CS の立ち下がりエッジは、すべてのオペコードの発行前に発生しなければならない                                                                                               |

| SCK               | 入力  | シリアル クロック。入出力はシリアル クロックに同期される。入力は立ち上がりエッジでラッチされ、出力は立ち下がりエッジで発生。同期デバイスであるため、クロック周波数は 0 ~ 4MHz 範囲内であり、いつでも割り込まれる可能性がある                                                                                                                                                    |

| SI <sup>[1]</sup> | 入力  | シリアル 入力。このピンからデバイスにすべてのデータを入力。入力は SCK の立ち上がりエッジでサンプリングされ、その時以外では無視。IDD 仕様を満たすため、入力を有効な論理レベルに駆動する必要がある                                                                                                                                                                   |

| SO <sup>[1]</sup> | 出力  | シリアル出力。これはデータ出力ピン。このピンは読み出し中に駆動。その時以外では HOLD が LOW になる時も含めトライステートのままになる。データ遷移はシリアル クロックの立ち下がりエッジで実現                                                                                                                                                                     |

| WP                | 入力  | 書き込み保護。このLOW アクティブ ピンは、WPEN が「1」にセットされる際のステータス レジスタへの書き込み動作を防止。その他の書き込み保護機能がステータス レジスタによって制御されるため、このことは重要。書き込み保護の詳細については、 <a href="#">ページ 7 のステータス レジスタおよび書き込み保護</a> を参照。このピンを使用しない場合、V <sub>DD</sub> に接続しなければならない WP の機能は、デバイスへの書き込みを禁止にする FM25040 の機能と異なることを注意してください。 |

| HOLD              | 入力  | <b>HOLD ピン。</b> ホスト CPU が他のタスクのためメモリ動作に割り込む必要がある場合、HOLD ピンを使用。HOLD が LOW になると、当時点の動作が一時停止。デバイスは、SCK もしくは CS の変化を無視。HOLD のすべての変化は SCK が LOW の間に発生する必要がある。このピンを使用しない場合、V <sub>DD</sub> に接続しなければならない                                                                       |

| V <sub>SS</sub>   | 電源  | デバイスのグランドで、システムのグランドに接続する必要がある                                                                                                                                                                                                                                          |

| V <sub>DD</sub>   | 電源  | デバイスへの電源入力                                                                                                                                                                                                                                                              |

### 注

- SI を SO と接続し 1 本のデータ インターフェースとして利用されることがあります。

## 概要

FM25640B はシリアル F-RAM メモリです。メモリ アレイは、8,192×8 ビットに論理構成され、業界標準のシリアル ペリフェラル インターフェース (SPI) バスを使用してアクセスされます。F-RAM の機能動作はシリアル フラッシュ、シリアル EEPROM と同じです。同じピン配置の FM25640B とシリアル フラッシュや EEPROM と違う点は、F-RAM の優れた書き込み性能、高アクセス可能回数、低消費電力です。

## メモリ アーキテクチャ

FM25640B のアクセスには、8 データ ビット毎に 8K 箇所の位置をアドレス指定します。これら 8 つのデータ ビットは順次シフトイン／シフトアウトされます。アドレスは、チップ セレクト (バス上で複数デバイスを許可する用) とオペコード、2 バイトのアドレスを含む SPI プロトコルを使ってアクセスされます。アドレス範囲の上位 3 ビットは「ドント ケア」値です。13 ビットの完全なアドレスは、各バイト専用アドレスを指定します。

FM25640B の殆どの機能は、SPI インターフェースにより制御されるか、または基板に搭載された回路によって処理されます。メモリ動作に対応したアクセス時間は基本的に 0 であり、シリアルプロトコルに必要な時間も考慮すべきです。すなわち、メモリは SPI バスの速度で読み書きされます。シリアル フラッシュや EEPROM と異なり、書き込み処理がバス速度で行われるので、デバイスの書き込み準備を知るためにポーリングする必要はありません。新しいバス トランザクションがデバイスに送り込まれるまでに書き込み動作は完了します。これはインターフェースの節で詳しく説明されています。

**注：**FM25640B は、簡単な内部パワーオン リセット回路以外に他の電源管理回路を備えていません。誤った動作を防ぐために  $V_{DD}$  がデータシートに記載された許容誤差以内であることを保証するのは、ユーザーの責任です。チップ イネーブルがアクティブになった時、デバイスへの電源を切断しないことをお勧めします。

## シリアル ペリフェラル インターフェース – SPI バス

FM25640B は SPI スレーブ デバイスであり、最速 4MHz で動作します。この高速シリアル バスにより、SPI マスターとの間で高性能のシリアル通信が可能です。多くの一般的なマイクロコントローラーは、ハードウェア SPI ポートを持っているため、直接インターフェースを可能にします。SPI ポートを持たないマイクロコントローラーで、通常のポートを使用して SPI ポートをエミュレートするのは非常に簡単です。FM25640B は、SPI モード 0 および 3 で動作します。

### SPI 概要

SPI は、チップ セレクト ( $\overline{CS}$ ) とシリアル入力 (SI)、シリアル出力 (SO)、シリアル クロック (SCK) ピンの 4 ピン インターフェースです。

SPI は、メモリ アクセスにクロックとデータ ピンを使用し、データ バス上の複数デバイスをサポートする同期シリアル インターフェースです。SPI バス上のデバイスは、CS ピンを使用してアクティブにされます。

チップ セレクト、クロック、データの間の関係は、SPI モードによります。このデバイスは、SPI モード 0 および 3 をサポートします。これらの両モードで、CS がアクティブになった後

の最初の立ち上がりエッジから始まる SCK の立ち上がりエッジで、データが F-RAM にクロック入力されます。

SPI プロトコルはオペコードによって制御されます。これらのオペコードは、バス マスターからスレーブ デバイスへのコマンドを指定します。 $\overline{CS}$  がアクティブにされた後、バス マスターから転送される最初のバイトがオペコードです。オペコードに続いて、任意のアドレスとデータが転送されます。処理が完了した後、新しいオペコードが発行される前に、CS を非アクティブにする必要があります。SPI プロトコルで一般的に使用される用語は以下です。

### SPI マスター

SPI マスター デバイスは SPI バスを制御します。SPI バスは、1つまたは複数のスレーブ デバイスを制御するマスターを 1 つのみ持つことができます。すべてのスレーブが同じ SPI バス ラインを共有し、マスターは CS ピンを使用してスレーブ デバイスのいずれかを選択することができます。すべての処理は、マスターがスレーブの CS ピンを LOW にプルダウンすることによってスレーブ デバイスをアクティブにして開始する必要があります。また、マスターは SCK を生成し、SI と SO ライン上のすべてのデータ送信はこのクロックと同期されます。

### SPI スレーブ

SPI スレーブ デバイスは、チップ セレクト ラインを介してマスターによってアクティブにされます。スレーブ デバイスは SPI マスターからの入力として SCK を取得し、すべての通信はこのクロックと同期されます。SPI スレーブが SPI バス上で通信を開始することはなく、単にマスターからの命令に従い実行します。

FM25640B は SPI スレーブとして動作し、他の SPI スレーブ デバイスと SPI バスを共有する場合があります。

### チップ セレクト ( $\overline{CS}$ )

すべてのスレーブ デバイスを選択するためには、マスターは対応する CS ピンをプルダウンする必要があります。CS ピンが LOW になっている時のみ、命令をスレーブ デバイスに発行することができます。デバイスが選択されていない場合、SI ピン経由のデータは無視され、シリアル出力ピン (SO) は高インピーダンス状態のままであります。

**注：**新しい命令は  $\overline{CS}$  の立ち下がりエッジで開始される必要があります。したがって、アクティブなチップ セレクト サイクル毎に 1 つのオペコードのみが発行されます。

### シリアル クロック (SCK)

シリアル クロックは SPI マスターによって生成され、 $\overline{CS}$  が LOW になった後、通信がこのクロックと同期されます。

FM25640B はデータ通信のために SPI モード 0 と 3 を有効にします。これらの両モードにおいて、入力は SCK の立ち上がりエッジでスレーブ デバイスによってラッシュされ、出力は立ち下がりエッジで発行されます。そのため、SCK の最初の立ち上がりエッジは、SI ピンに SPI 命令の最初のビット (MSB) が到着したことを意味します。さらに、すべてのデータの入力と出力は SCK と同期されます。

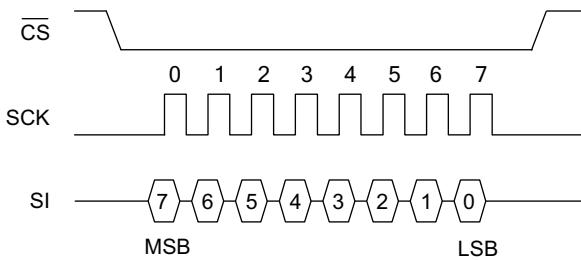

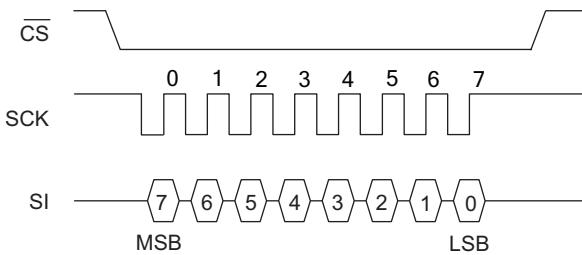

### データ転送 (SI / SO)

SPI データ バスは、シリアル データ通信用に SI と SO の 2 ラインで構成されます。SI はマスター アウト スレーブ イン (MOSI)、SO はマスター イン スレーブ アウト (MISO) とも呼ばれています。マスターは SI ピンを介してスレーブに命令を発行し、スレーブは SO ピンを介して応答します。複数のスレーブ

デバイスは、前述のように SI と SO ラインを共有する場合があります。

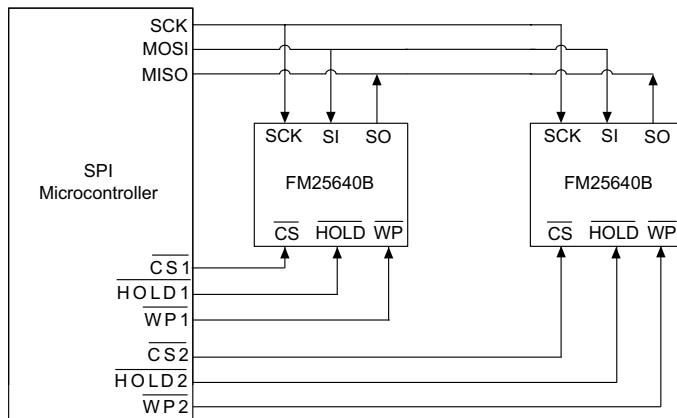

図 2 に示すように、FM25640B にはマスターと接続することができる SI と SO 用の 2 つの独立したピンがあります。

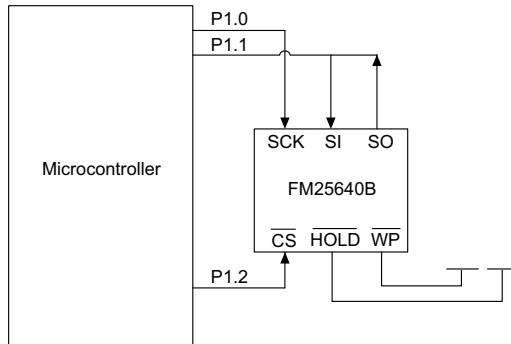

専用 SPI バスを持たないマイクロコントローラーでは、汎用ポートが使用されることもあります。マイコンのハードウェアリソースを減らすために、2 つのデータピン (SI, SO) を 1 つにまとめて接続し、HOLD ピンと WP ピンを HIGH に固定接続することができます。図 3 はマイコンのピンを 3 本のみ使用しているこのコンフィギュレーションを示します。

#### 最上位ビット (MSB)

SPI プロトコルでは、送信される最初のビットが最上位ビット (MSB) である必要があります。この方式はアドレスとデータ転送共に適用されます。

64K ビットシリアル F-RAM は、すべての読み出しままたは書き込み動作に対応して 2 バイトのアドレスを必要とします。アドレスは 13 ビットであるため、入力された最初の 3 ビットはデバイスによって無視されます。これらの 3 ビットは「ドントケ

ア」ですが、より高容量メモリへの円滑な移行を可能にするために、これらを 0 に設定することをサイプレスはお勧めします。

#### シリアルオペコード

CS が LOW になる状態でスレーブデバイスが選択された後、最初に受信されたバイトは、意図されている動作用のオペコードとして扱われます。FM25640B は、メモリアクセスのために標準オペコードを使用します。

#### 無効なオペコード

無効なオペコードが受信されるとそのオペコードは無視され、デバイスは SI ピン上にある追加のシリアルデータを次の CS の立ち下がりエッジまで無視し、SO ピンはトライステートのままとなります。

#### ステータスレジスタ

FM25640B には、8 ビットのステータスレジスタが 1 個あります。ステータスレジスタ内のビットはデバイスをコンフィギュレーションするために使用されます。これらのビットは [ページ 7 の表 3](#) で説明されています。

図 2. SPI ポートを使ったシステムコンフィギュレーション

図 3. SPI ポートを使用しないシステムコンフィギュレーション

#### SPI モード

FM25640B は、SPI ペリフェラルが次の 2 つのモードのいずれかで動作しているマイクロコントローラによって駆動することができます。

##### ■ SPI モード 0 (CPOL = 0, CPHA = 0)

##### ■ SPI モード 3 (CPOL = 1, CPHA = 1)

この両モードでは、入力データは CS がアクティブにされた後の最初の立ち上がりエッジから始まる SCK の立ち上がりエッジでラッチされます。クロックが HIGH 状態から起動される場合 (モード 3) では、クロックトグル後の最初の立ち上がりエッジ

ジになります。出力データは SCK の立ち下がりエッジで利用可能となります。

2つのSPIモードはページ6の図4とページ6の図5に示されています。バスマスターがデータを転送していない時のクロックの状態は以下の通りです。

■モード0では、SCKが0のままで。

■モード3では、SCKが1のままで。

CSピンをLOWにすることによりデバイスが選択された時、デバイスはSCKピンの状態からSPIモードを検出します。デバイスが選択された時に、SCKピンがLOWならデバイスはSPIモード0で動作し、SCKピンがHIGHならデバイスはSPIモード3で動作します。

図4. SPIモード0

図5. SPIモード3

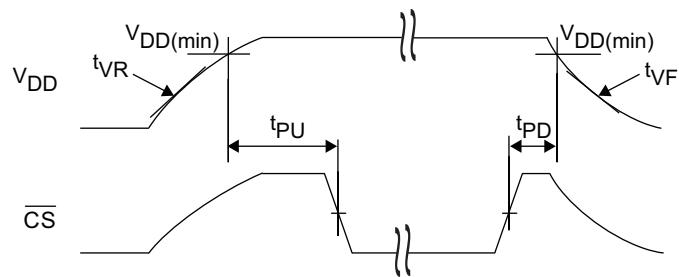

### 電源投入時から最初のアクセスまで

電源投入後の  $t_{PU}$  の間、FM25640B へはアクセスできません。ユーザーはタイミングパラメーター、 $t_{PU}(V_{DD}(\min))$  から CS が初めてLOWになる時までの最短期間)に従わねばなりません。

### コマンドの構成

バスマスターがFM25640Bに発行するコマンド(オペコードと呼ばれる)は6個あります。これらを表1に示します。これらのオペコードはメモリが実行する機能を制御します。

表1. オペコードのコマンド

| 名称    | 説明                | オペコード      |

|-------|-------------------|------------|

| WREN  | 書き込みイネーブル ラッチのセット | 0000 0110b |

| WRDI  | 書き込みディスエーブル       | 0000 0100b |

| RDSR  | ステータスレジスタの読み出し    | 0000 0101b |

| WRSR  | ステータスレジスタの書き込み    | 0000 0001b |

| READ  | メモリデータの読み出し       | 0000 0011b |

| WRITE | メモリデータの書き込み       | 0000 0010b |

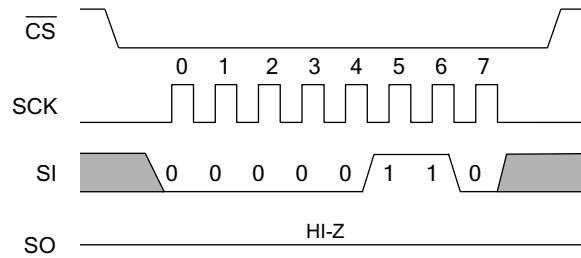

### WREN - 書き込みイネーブル ラッチのセット

FM25640Bは、書き込みが無効の状態で電源投入されます。WRENコマンドを書き込み動作の前に発行する必要があります。WRENオペコードを送信することにより、ユーザーは書き込み動作用に次のオペコードを発行することができます。これらはステータスレジスタへの書き込み(WRSR)とメモリへの書き込み(WRITE)を含みます。

WRENオペコードを発行すると、内部書き込みイネーブルラッチはセットされます。WELと呼ばれるステータスレジスタ内のフラグビットはラッチの状態を示します。WEL = 「1」は、書き込みが許可されることを示します。ステータスレジスタのWELビットに書き込んでもこのビットの状態に影響を与えません。WRENオペコードのみがこのビットをセットできます。WELビットは、WRDIやWRSR、WRITE動作に続くCSの立ち上がりエッジで自動的にクリアされます。これにより、別のWRENコマンドを発行せず、ステータスレジスタまたはF-RAMアレイへの二重の書き込みを防ぐことができます。図6は、WRENコマンドのバスコンフィギュレーションを示します。

図6. WRENバスコンフィギュレーション

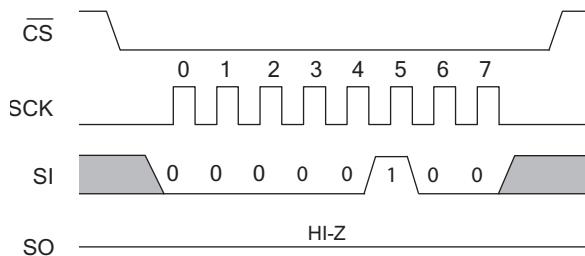

### WRDI - 書き込みイネーブル ラッチのリセット

WRDIコマンドは、書き込みイネーブルラッチをクリアすることによりすべての書き込み動作を無効にします。ステータスレジスタ内のWELビットを読み出し、WELビットが「0」であることを確認することにより、ユーザーは書き込みが無効であることを確認できます。図7は、WRDIコマンドのバスコンフィギュレーションを示します。

図7. WRDIバスコンフィギュレーション

## ステータス レジスタおよび書き込み保護

FM25640B の書き込み保護機能は多層的であり、ステータス レジスタを介して有効にされます。ステータス レジスタは以下のとおりです。

表 2. ステータス レジスタ

| ビット 7    | ビット 6 | ビット 5 | ビット 4 | ビット 3   | ビット 2   | ビット 1   | ビット 0 |

|----------|-------|-------|-------|---------|---------|---------|-------|

| WPEN (0) | X (0) | X (0) | X (0) | BP1 (0) | BP1 (0) | WEL (0) | X (0) |

表 3. ステータス レジスタのビット定義

| ビット          | 定義              | 説明                                                                                               |

|--------------|-----------------|--------------------------------------------------------------------------------------------------|

| ビット 0        | ドント ケア          | このビットは書き込み不可であり、読み出し時に常に「0」を返す                                                                   |

| ビット 1 (WEL)  | 書き込みイネーブル ラッチ   | WEL はデバイスの書き込みが有効かどうかを示す。電源投入時、このビットの初期値は「0」(無効)<br>WEL = 「1」--> 書き込みが有効<br>WEL = 「0」--> 書き込みが無効 |

| ビット 2 (BP0)  | ブロック保護ビット「0」    | ブロック保護のために使用。詳細は、 <a href="#">ページ 7 の表 4</a> を参照                                                 |

| ビット 3 (BP1)  | ブロック保護ビット「1」    | ブロック保護のために使用。詳細は、 <a href="#">ページ 7 の表 4</a> を参照                                                 |

| ビット 4 ~ 6    | ドント ケア          | これらのビットは書き込み不可であり、読み出し時に常に「0」を返す                                                                 |

| ビット 7 (WPEN) | 書き込み保護イネーブル ビット | 書き込み保護ピン (WP) の機能を有効にするために使用。詳細は、 <a href="#">ページ 7 の表 5</a> を参照                                 |

ビット 0 と 4 ~ 6 は、「0」に固定され、これらのビットは修正できません。F-RAM はリアルタイムで書き込まれ、ビジーの時がないため、ビット 0 (シリアル フラッシュや EEPROM での「Ready or Write in progress (待機または書き込み中)」の状態を示すビット) は不要であり、「0」として読み出されます。BP1 および BP0 はソフトウェアの書き込み保護機能を制御する不揮発性ビットです。WEL フラグは、書き込みイネーブル ラッチの状態を示します。ステータス レジスタの WEL ビットに直接書き込んでも状態は変りません。このビットは内部でそれぞれ WREN、WRDI コマンドを介してセット、クリアされます。

BP1 および BP0 はメモリ ブロックの書き込み保護ビットです。それらは表 4 に示すように書き込み保護されるメモリ領域を指定します。

表 4. ブロック メモリへの書き込み保護

| BP1 | BP0 | 保護されたアドレス範囲            |

|-----|-----|------------------------|

| 0   | 0   | なし                     |

| 0   | 1   | 1800h ~ 1FFFh (上位 1/4) |

| 1   | 0   | 1000h ~ 1FFFh (上位 1/2) |

| 1   | 1   | 0000h ~ 1FFFh (全部)     |

BP1 と BP0 ビットと書き込みイネーブル ラッチは、メモリへの書き込みを防止する唯一のメカニズムです。残りの書き込み保護機能は、ブロック保護ビットへの不用意な変更を防止します。

ステータス レジスタの書き込み保護イネーブル ビット (WPEN) は、ハードウェア書き込み保護 (WP) ピンの効果を制御します。WPEN ビットが「0」にクリアされると、WP ピンの状態は無視されます。WPEN ビットが「1」にセットされた

ように構成されています (工場出荷時、このステータス レジスタ内のビットのデフォルト値は 0 です)。

時、WP ピンが LOW になるとステータス レジスタへの書き込みが禁止されます。そのためステータス レジスタは、WPEN = 「1」および WP = 「0」の場合のみ書き込み保護されます。

表 5 に書き込み保護条件をまとめます。

表 5. 書き込み保護

| WEL | WPEN | WP | 保護<br>ブロック | 非保護<br>ブロック | ステータス<br>レジスタ |

|-----|------|----|------------|-------------|---------------|

| 0   | X    | X  | 保護         | 保護          | 保護            |

| 1   | 0    | X  | 保護         | 非保護         | 非保護           |

| 1   | 1    | 0  | 保護         | 非保護         | 保護            |

| 1   | 1    | 1  | 保護         | 非保護         | 非保護           |

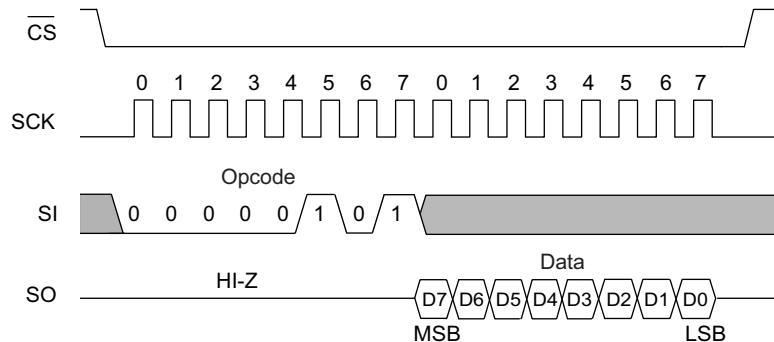

### RDSR - ステータス レジスタの読み出し

RDSR コマンドでは、バス マスターがステータス レジスタの内容を検証することができます。ステータス レジスタを読み出すごことで、書き込み保護機能の現時点の状態に関する情報を得ます。RDSR オペコードに続いて、FM25640B はステータス レジスタの内容を持つ 1 バイトを返します。

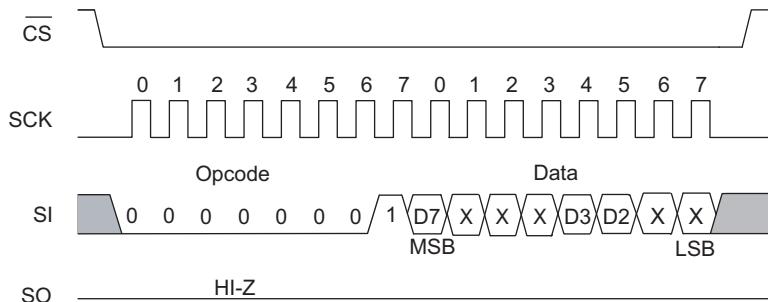

### WRSR - ステータス レジスタの書き込み

WRSR コマンドを使って、SPI バス マスターがステータス レジスタへ書き込み、WPEN、BP0、BP1 ビットを必要に応じて設定することで書き込み保護のコンフィギュレーションを変更することができます。WRSR コマンドを発行する前には、WP ピンが HIGH または非アクティブである必要があります。FM25640B では、WP がメモリ アレイではなくステータス レジスタのみへの書き込みのみを防止することに注意してください。WRSR コマンドを送信する前に、書き込みを有効にするため WREN コマンドを送信する必要があります。WRSR コマンドの実行は書き込み動作に相当するため、書き込みイネーブル ラッチがクリアされます。

**図 8. RDSR バス コンフィギュレーション**

**図 9. WRSR バス コンフィギュレーション (WREN が非表示)**

## メモリの動作

高いクロック周波数での動作が可能な SPI インターフェースは、F-RAM 技術の高速書き込み機能を際立たせます。シリアルフラッシュやEEPROMと違って、FM25640Bはバス速度でシーケンシャルに書き込みを実行します。ページレジスタは不要であり、シーケンシャルな書き込みは何回でも実行できます。

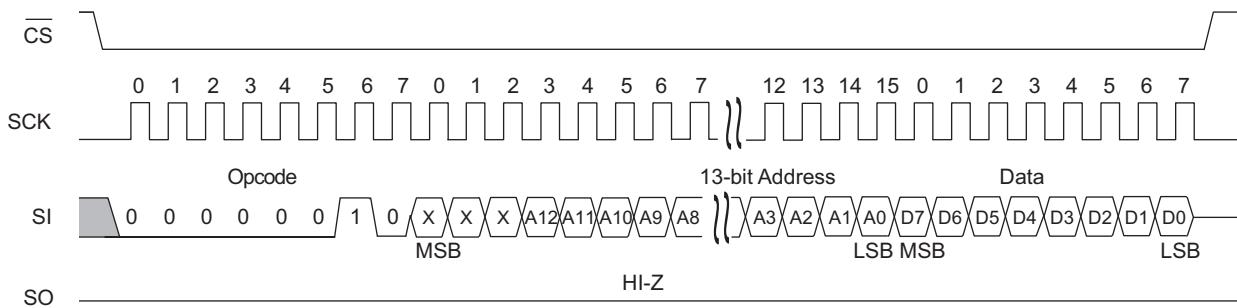

### 書き込み動作

すべてのメモリへの書き込みは WREN オペコードから開始します。WRITE オペコードに続き、メモリへ書き込む最初のデータバイトを指定する 13 ビット アドレス (A12 ~ A0) を含む 2 バイト アドレスが続きます。2 バイト アドレスの上位 3 ビットは無視されます。後続のバイトはシーケンシャルに書き込まれるデータバイトです。バスマスターがクロックを送り、CS を LOW に維持している限り、アドレスは内部でインクリメントされます。1FFFh の最終アドレスに達すると、カウントは 0000h に戻ります。データは MSB から書き込みます。CS の立ち上がりエッジで書き込み動作を終了します。書き込み動作を図 10 に示します。

注：バースト書き込みが保護されたブロックに達すると、アドレスの自動インクリメントは停止し、書き込み用に受信された後続のデータバイトのすべてはデバイスに無視されます。

EEPROM はページ バッファを使用して書き込みスループットを上げます。ページ バッファは、書き込み動作が遅いという本来の特性を補完するものです。F-RAM メモリは、データ バイトが(8番目のクロックの後)クロック入力された直後に F-RAM アレイに書き込まれるので、ページ バッファを持たいません。そのため、ページ バッファの遅延なしにバイトをいくつも書き込むことができます。

注：書き込み中に電力を喪失すると、最後に完了したバイトのみが書き込まれます。

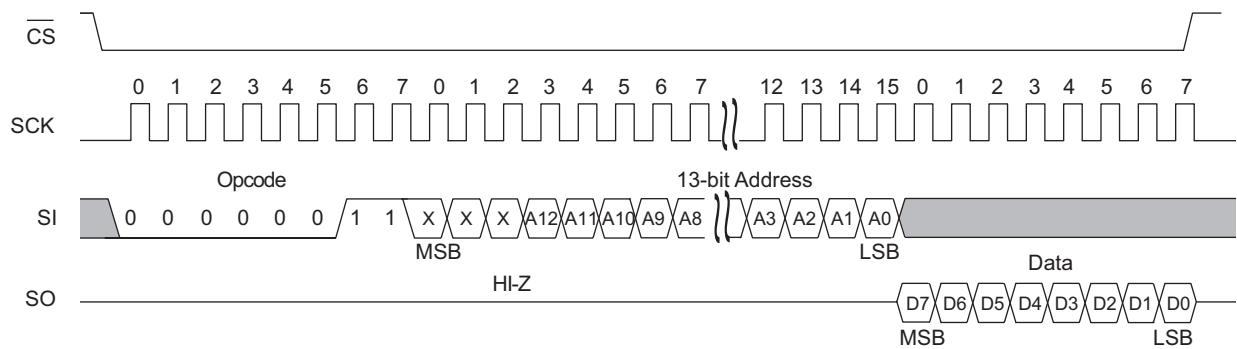

### 読み出し動作

CS の立ち下がりエッジの後に、バスマスターは READ オペコードを発行できます。READ コマンドの後には、読み出し動作の開始アドレスを指定する 13 ビット アドレス (A12 ~ A0) を含む 2 バイトのアドレスが続きます。アドレスの上位 3 ビットは無視されます。オペコードとアドレスが発行された後、デバイスは次の 8 つのクロックで読み出しデータを出力します。SI 入力は読み出しデータ バイトの出力中には無視されます。後続のバイトは順々に読み出されるデータ バイトです。バスマスターがクロックを送り、CS が LOW である限り、アドレスは内部でインクリメントされます。1FFFh の最終アドレスに達すると、カウントは 0000h に戻ります。データは MSB から読み出します。CS の立ち上がりエッジで読み出し動作を停止し、SO ピンをトライステートにします。読み出し動作を図 11 に示します。

**図 10. メモリ書き込み (WREN が非表示) 動作**

**図 11. メモリ読み出し**

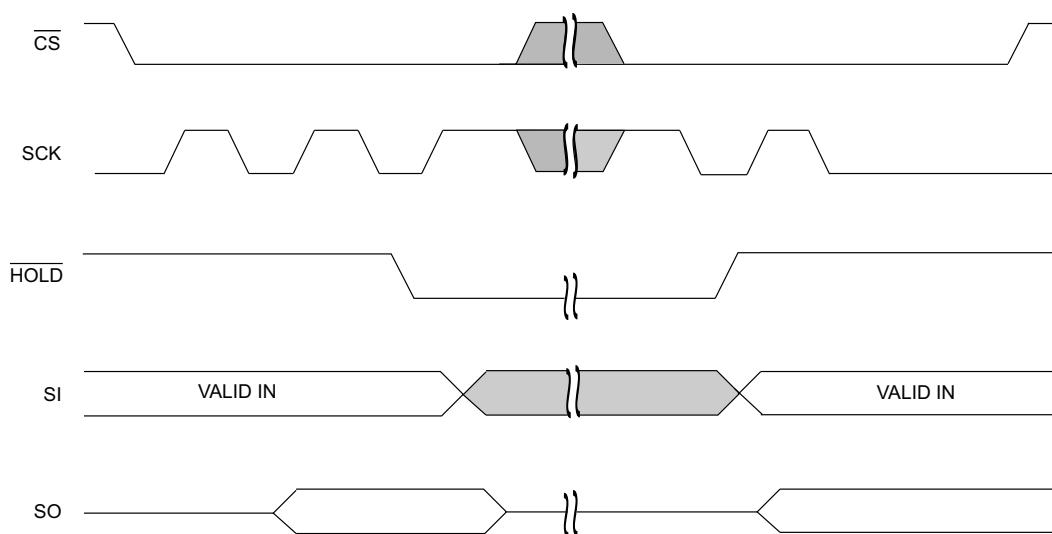

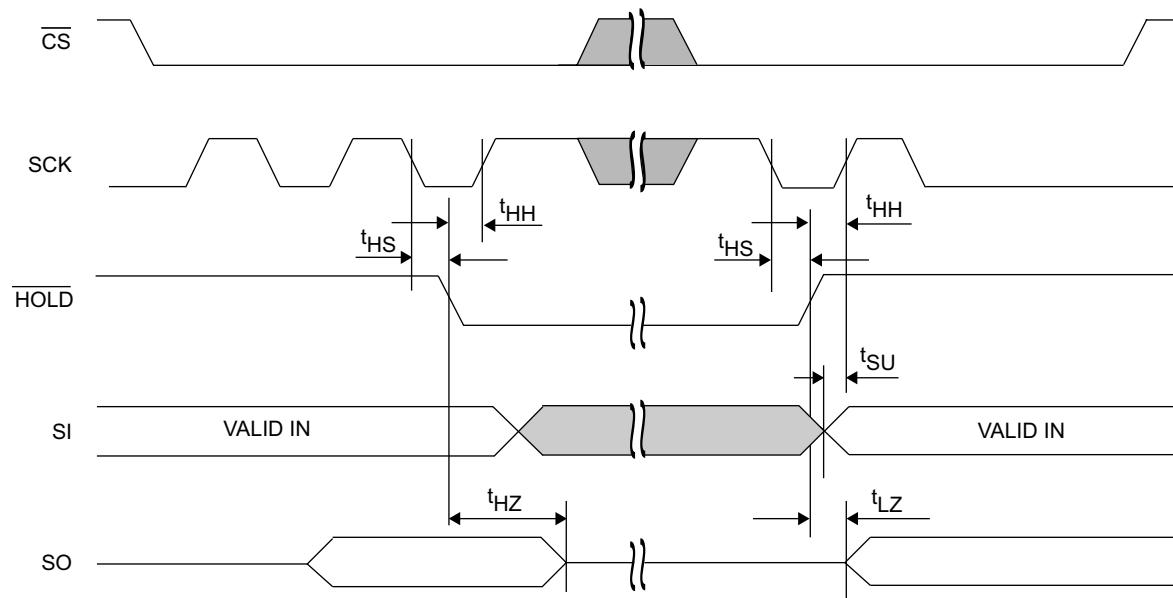

### HOLD ピンの動作

HOLD ピンを使って、連続動作を中断しないでそれに割り込むことができます。SCK が LOW の間に、バス マスターが HOLD ピンを LOW にすると、当時点の動作は一時停止します。SCK

が LOW の間に HOLD ピンを HIGH にすると、動作を再開します。SCK が LOW の間に HOLD の遷移を行なう必要がありますが、SCK と CS ピンはホールド状態中に切り替えることができます。

**図 12. HOLD 動作 [2]**

### 注

2. 図は、入力モードと出力モードでの HOLD ピンの動作を示します。

## アクセス可能回数

FM25640B デバイスには  $10^{13}$  回以上、読み書きを問わずアクセスすることができます。F-RAM メモリは読み出しと格納メカニズムを併用する動作します。そのため、メモリアレイへのアクセス（読み出し／書き込み）に対して、アクセス サイクルが行単位で適用されます。F-RAM のアーキテクチャは、64 ビットの行と 1K の列からなるアレイを基にしています。読み出しまでは書き込みは行単位に行われます。1 行内のデータのアクセス バイト数に関係なく内部的に行に対するアクセスは 1 回です。行内の各バイトは、アクセス可能回数の計算では 1 回だけカウントされます。[表 6](#) は、オペコード、開始アドレス、順々の 64 バイト データの流れを含む、64 バイトの繰り返しループに対応したアクセス可能回数を示しています。これはループによって各バイトが 1 回のアクセス回数を費やしたことになります。

F-RAM の読み出しと書き込み可能回数は、4MHz のクロック速度でも事実上無制限です。

表 6. 64 バイト ループの繰り返しでアクセス回数が限界に達する期間

| SCK 周波数 (MHz) | アクセス可能回数 (サイクル/秒) | アクセス可能回数 (サイクル/秒)     | 限界到達年数 |

|---------------|-------------------|-----------------------|--------|

| 4             | 7,480             | $2.36 \times 10^{11}$ | 42.3   |

| 1             | 1,870             | $5.88 \times 10^{10}$ | 170.1  |

## 最大定格

最大定格を超えるとデバイスの寿命が短くなる可能性があります。これらのユーザー ガイドラインはテストは行われていません。

保存温度 .....  $-55^{\circ}\text{C} \sim +125^{\circ}\text{C}$

最大接合部温度 .....  $135^{\circ}\text{C}$

$V_{\text{SS}}$  を基準とした  $V_{\text{DD}}$  の電源電圧 .....  $-1.0\text{V} \sim +7\text{V}$

入力電圧 .....  $-1.0\text{V} \sim +7.0\text{V}$ ,  $V_{\text{IN}} < V_{\text{DD}} + 1.0\text{V}$

High-Z 状態の出力

に印加する DC 電圧 .....  $-0.5\text{V} \sim V_{\text{DD}} + 0.5\text{V}$

グランド電位を基準にした任意のピンの過渡電圧

( $<20\text{ns}$ ) .....  $-2.0\text{V} \sim V_{\text{DD}} + 2.0\text{V}$

パッケージ許容電力損失 ( $T_A = 25^{\circ}\text{C}$ ) ..... 1.0W

## DC 電気的特性

### 動作範囲において

| パラメーター                 | 説明                                             | テスト条件                                                                                                                                                                                    | Min                                                       | Typ <sup>[5]</sup> | Max                         | 単位            |               |

|------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------|-----------------------------|---------------|---------------|

| $V_{\text{DD}}$        | 電源                                             |                                                                                                                                                                                          | 4.5                                                       | 5.0                | 5.5                         | V             |               |

| $I_{\text{DD}}$        | $V_{\text{DD}}$ 電源電流                           | $V_{\text{DD}} - 0.3\text{V} \leq V_{\text{SS}} \leq V_{\text{DD}}$<br>$f_{\text{SCK}} = 1\text{MHz}$<br>$V_{\text{SS}} = V_{\text{DD}} - 0.3\text{V}$<br>$f_{\text{SCK}} = 4\text{MHz}$ | -                                                         | -                  | 0.3                         | mA            |               |

| $I_{\text{SB}}$        | $V_{\text{DD}}$ スタンバイ電流                        | $\overline{\text{CS}} = V_{\text{DD}}$ 。他の全ての入力<br>は $V_{\text{SS}}$ または $V_{\text{DD}}$ を印加                                                                                             | $T_A = 85^{\circ}\text{C}$<br>$T_A = 125^{\circ}\text{C}$ | -                  | -                           | 10            | $\mu\text{A}$ |

| $I_{\text{LI}}$        | 入力リーク電流                                        | $V_{\text{SS}} \leq V_{\text{IN}} \leq V_{\text{DD}}$                                                                                                                                    | -                                                         | -                  | $\pm 1$                     | $\mu\text{A}$ |               |

| $I_{\text{LO}}$        | 出力リーク電流                                        | $V_{\text{SS}} \leq V_{\text{OUT}} \leq V_{\text{DD}}$                                                                                                                                   | -                                                         | -                  | $\pm 1$                     | $\mu\text{A}$ |               |

| $V_{\text{IH}}$        | 入力 HIGH 電圧                                     |                                                                                                                                                                                          | $0.75 \times V_{\text{DD}}$                               | -                  | $V_{\text{DD}} + 0.3$       | V             |               |

| $V_{\text{IL}}$        | 入力 LOW 電圧                                      |                                                                                                                                                                                          | -0.3                                                      | -                  | $0.25 \times V_{\text{DD}}$ | V             |               |

| $V_{\text{OH}}$        | 出力 HIGH 電圧                                     | $I_{\text{OH}} = -2\text{mA}$                                                                                                                                                            | $V_{\text{DD}} - 0.8$                                     | -                  | -                           | V             |               |

| $V_{\text{OL}}$        | 出力 LOW 電圧                                      | $I_{\text{OL}} = 2\text{mA}$                                                                                                                                                             | -                                                         | -                  | 0.4                         | V             |               |

| $V_{\text{HYS}}^{[6]}$ | 入力ヒステリシス ( $\overline{\text{CS}}$ と SCK<br>ピン) |                                                                                                                                                                                          | $0.05 \times V_{\text{DD}}$                               | -                  | -                           | V             |               |

### 主

- 標準値は  $25^{\circ}\text{C}$ 、 $V_{\text{DD}} = V_{\text{DD}} \text{ (typ)}$  で測定されるものです。すべてのデバイスでテストされていません。

- このパラメーターは特性付けされていますが、すべてのデバイスでテストされていません。

## データ保持期間およびアクセス可能回数

| パラメーター   | 説明       | テスト条件                     | Min       | Max | 単位   |

|----------|----------|---------------------------|-----------|-----|------|

| $T_{DR}$ | データ保持期間  | $T_A = 125^\circ\text{C}$ | 11000     | —   | 時間   |

|          |          | $T_A = 105^\circ\text{C}$ | 11        | —   | 年    |

|          |          | $T_A = 85^\circ\text{C}$  | 121       | —   |      |

| $NV_C$   | アクセス可能回数 | 動作温度範囲内                   | $10^{13}$ | —   | サイクル |

## AEC-Q100 車載用アプリケーションでの F-RAM 製品寿命の例

アプリケーションは、寿命にわたって安定した温度で動作するわけではありません。その代わりに、アプリケーションの使用可能な寿命にわたって温度が異なった環境で動作することを期待されています。その結果として、アプリケーションに使用する F-RAM の保持仕様は累積的に計算されるものです。多重温度の熱プロファイルの推定例は、以下の通りです。

| 温度<br>$T$                | 時間<br>$t$   | Tmax A [5] に応じる加速係数                                                                             | プロファイル要因<br>$P$                                                                              | プロファイル寿命<br>$L(P)$           |

|--------------------------|-------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------|

|                          |             | $A = \frac{L(T)}{L(T_{max})} = e^{\frac{Ea}{k} \left( \frac{1}{T} - \frac{1}{T_{max}} \right)}$ | $P = \frac{1}{\left( \frac{t1}{A1} + \frac{t2}{A2} + \frac{t3}{A3} + \frac{t4}{A4} \right)}$ | $L(P) = P \times L(T_{max})$ |

| $T1 = 125^\circ\text{C}$ | $t1 = 0.1$  | $A1 = 1$                                                                                        | 8.33                                                                                         | $> 10.46$ 年                  |

| $T2 = 105^\circ\text{C}$ | $t2 = 0.15$ | $A2 = 8.67$                                                                                     |                                                                                              |                              |

| $T3 = 85^\circ\text{C}$  | $t3 = 0.25$ | $A3 = 95.68$                                                                                    |                                                                                              |                              |

| $T4 = 55^\circ\text{C}$  | $t4 = 0.50$ | $A4 = 6074.80$                                                                                  |                                                                                              |                              |

## 静電容量

| パラメーター [6] | 説明            | テスト条件                                                                         | Max | 単位 |

|------------|---------------|-------------------------------------------------------------------------------|-----|----|

| $C_O$      | 出力ピン静電容量 (SO) | $T_A = 25^\circ\text{C}$ 、 $f = 1\text{ MHz}$ 、 $V_{DD} = V_{DD}(\text{typ})$ | 8   | pF |

| $C_I$      | 入力ピン静電容量      |                                                                               | 6   | pF |

## 熱抵抗

| パラメーター        | 説明                | テスト条件                                              | 8 ピン SOIC | 単位   |

|---------------|-------------------|----------------------------------------------------|-----------|------|

| $\Theta_{JA}$ | 熱抵抗<br>(接合部から周囲)  | テスト条件は、EIA/JESD51 による、熱インピーダンスを測定するための標準試験方法と手順に従う | 147       | °C/W |

| $\Theta_{JC}$ | 熱抵抗<br>(接合部からケース) |                                                    | 47        | °C/W |

## AC テスト条件

- 入力パルスレベル .....  $V_{DD}$  の 10% および 90%

- 入力の立ち上がりと立ち下がり時間 ..... 5ns

- 入力と出力タイミングの基準レベル .....  $0.5 \times V_{DD}$

- 出力負荷容量 ..... 30pF

### 注

5. ここでは、 $k$  は、Boltzmann 定数  $8.617 \times 10^{-5}\text{ eV/K}$  で、 $T_{max}$  は、製品の指定した最大温度で、 $T$  は F-RAM 製品の仕様範囲内の任意の温度です。式では、すべての温度の単位は、ケルビンです。

6. このパラメーターは特性付けされますが、すべてのデバイスでテストされていません。

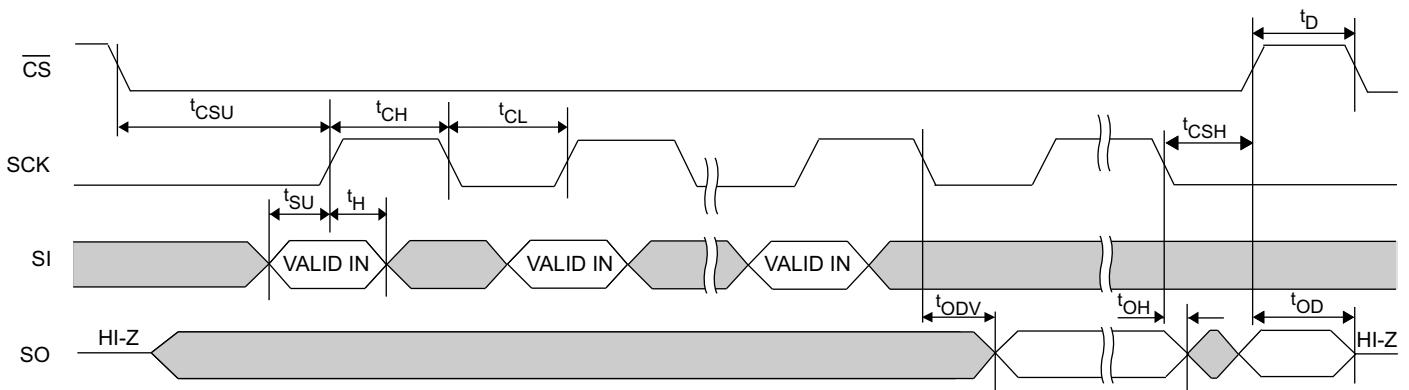

## AC スイッチング特性

動作範囲において

| パラメーター <sup>[7]</sup> |               | 説明                           | Min | Max | 単位  |

|-----------------------|---------------|------------------------------|-----|-----|-----|

| サイプレスの<br>パラメーター      | 他社の<br>パラメーター |                              |     |     |     |

| $f_{SCK}$             | —             | SCK クロック周波数                  | 0   | 4   | MHz |

| $t_{CH}$              | —             | クロック HIGH 時間                 | 100 | —   | ns  |

| $t_{CL}$              | —             | クロック LOW 時間                  | 100 | —   | ns  |

| $t_{CSU}$             | $t_{CSS}$     | チップ セレクトのセットアップ時間            | 100 | —   | ns  |

| $t_{CSH}$             | $t_{CSH}$     | チップ セレクトのホールド時間              | 100 | —   | ns  |

| $t_{OD}^{[8, 9]}$     | $t_{HZCS}$    | 出力ディスエーブル時間                  | —   | 100 | ns  |

| $t_{ODV}$             | $t_{CO}$      | 出力データ有効時間                    | —   | 75  | ns  |

| $t_{OH}$              | —             | 出力ホールド時間                     | 0   | —   | ns  |

| $t_D$                 | —             | 選択解除時間                       | 100 | —   | ns  |

| $t_R^{[10, 11]}$      | —             | データ入力の立ち上がり時間                | —   | 50  | ns  |

| $t_F^{[10, 11]}$      | —             | データ入力の立ち下がり時間                | —   | 50  | ns  |

| $t_{SU}$              | $t_{SD}$      | データ セットアップ時間                 | 30  | —   | ns  |

| $t_H$                 | $t_{HD}$      | データ ホールド時間                   | 20  | —   | ns  |

| $t_{HS}$              | $t_{SH}$      | HOLD ピンのセットアップ時間             | 70  | —   | ns  |

| $t_{HH}$              | $t_{HH}$      | HOLD ピンのホールド時間               | 40  | —   | ns  |

| $t_{HZ}^{[8, 9]}$     | $t_{HZ}$      | HOLD が LOW から HI-Z までの時間     | —   | 100 | ns  |

| $t_{LZ}^{[9]}$        | $t_{HLZ}$     | HOLD が HIGH からデータ アクティブまでの時間 | —   | 50  | ns  |

注

7. [ページ 12 の AC テスト条件](#)に示すように、テスト条件では、5ns 以下の信号遷移時間、 $0.5 \times V_{DD}$  のタイミング リファレンス レベル、 $V_{DD0}$  の 10% ~ 90% の入力パルス レベル、指定の  $I_{OL} / I_{OH}$  の出力負荷、30pF の負荷容量を前提にしています。

8.  $t_{OD}$  および  $t_{HZ}$  は、5pF の負荷容量で規定されています。出力が高インピーダンス状態に入ると、遷移が測定されます。

9. このパラメーターは特性付けされますが、すべてのデバイスでテストされていません。

10. 立ち上がりと立ち下がり時間は波形の 10% と 90% の間で測定されます。

11. これらのパラメーターは設計保証されますが、テストされていません。

**図 13. 同期データタイミング(モード 0)**

**図 14.  $\overline{\text{HOLD}}$  のタイミング**

## パワー サイクル タイミング

動作範囲において

| パラメーター          | 説明                                                              | Min | Max | 単位   |

|-----------------|-----------------------------------------------------------------|-----|-----|------|

| $t_{PU}$        | 電源投入時の $V_{DD(min)}$ から最初のアクセス ( $\overline{CS}$ LOW) までの時間     | 1   | –   | ms   |

| $t_{PD}$        | 最後のアクセス ( $\overline{CS}$ HIGH) から電源切断 ( $V_{DD(min)}$ ) 時までの時間 | 0   | –   | μs   |

| $t_{VR}^{[12]}$ | $V_{DD}$ 電源投入時のランプレート                                           | 30  | –   | μs/V |

| $t_{VF}^{[12]}$ | $V_{DD}$ 電源切断時のランプレート                                           | 20  | –   | μs/V |

図 15. パワー サイクル タイミング

注

12.  $V_{DD}$  波形上の任意の点で測定した傾きです。

## 注文情報

| 注文コード         | パッケージ図   | パッケージ タイプ | 動作範囲   |

|---------------|----------|-----------|--------|

| FM25640B-GA   | 51-85066 | 8 ピン SOIC | 車載用    |

| FM25640B-GATR | 51-85066 | 8 ピン SOIC | 拡張温度範囲 |

これらすべての部品は鉛フリー。在庫状況については、最寄りのサイプレスの販売代理店にお問い合わせください。

## 注文コードの定義

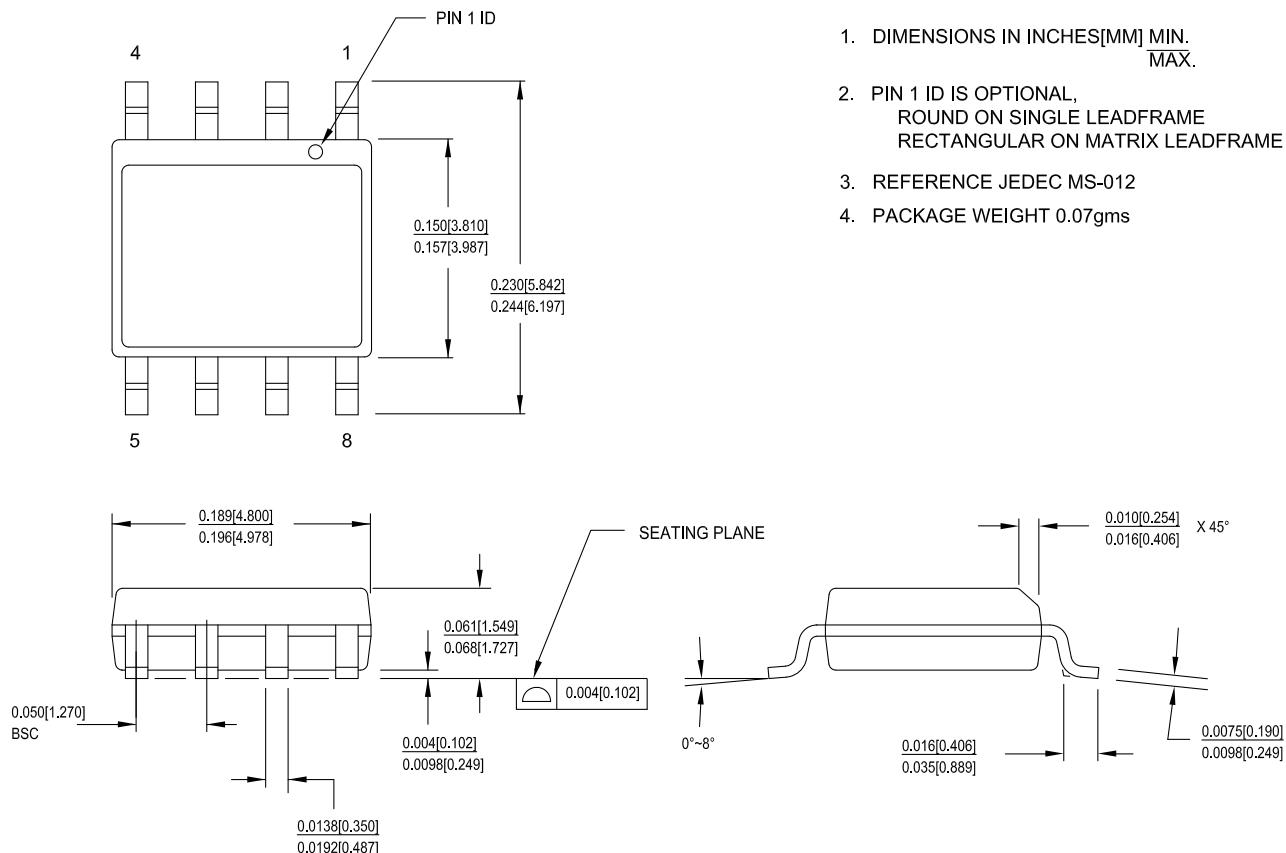

## パッケージ図

図 16. 8 ピン SOIC (150Mil) パッケージ図、51-85066

51-85066 \*F

**略語**

| 略語     | 説明                                                                             |

|--------|--------------------------------------------------------------------------------|

| AEC    | Automotive Electronics Council<br>(米国車載電子部品評議会)                                |

| CPHA   | Clock Phase (クロック位相)                                                           |

| CPOL   | Clock Polarity (クロック極性)                                                        |

| EEPROM | Electrically Erasable Programmable Read-Only Memory<br>(電気的消去書き込み可能な読み出し専用メモリ) |

| EIA    | Electronic Industries Alliance (米国電子工業会)                                       |

| I/O    | Input/Output (入力／出力)                                                           |

| JEDEC  | Joint Electron Devices Engineering Council<br>(半導体技術協会)                        |

| JESD   | JEDEC Standards (JEDEC 準拠)                                                     |

| LSB    | Least Significant Bit (最下位ビット)                                                 |

| MSB    | Most significant bit (最上位ビット)                                                  |

| F-RAM  | Ferroelectric Random Access Memory<br>(強誘電体ランダム アクセス メモリ)                      |

| RoHS   | Restriction of Hazardous Substances<br>(特定有害物質使用制限指令)                          |

| SPI    | Serial Peripheral Interface<br>(シリアル ペリフェラル インターフェース)                          |

| SOIC   | Small Outline Integrated Circuit<br>(小型外形集積回路)                                 |

**本書の表記法**

**測定単位**

| 記号   | 測定単位     |

|------|----------|

| °C   | 摂氏温度     |

| Hz   | ヘルツ      |

| kHz  | キロヘルツ    |

| KΩ   | キロオーム    |

| Kbit | キロビット    |

| kV   | キロボルト    |

| MHz  | メガヘルツ    |

| μA   | マイクロアンペア |

| μs   | マイクロ秒    |

| mA   | ミリアンペア   |

| ms   | ミリ秒      |

| ns   | ナノ秒      |

| Ω    | オーム      |

| %    | パーセント    |

| pF   | ピコファラッド  |

| V    | ボルト      |

| W    | ワット      |

## 改訂履歴

文書名 : FM25640B、64K ビット (8K × 8) シリアル (SPI) 車載用 F-RAM

文書番号 : 001-95866

| 版  | ECN 番号  | 変更者 | 発行日        | 変更内容                                                 |

|----|---------|-----|------------|------------------------------------------------------|

| ** | 4700356 | IYM | 04/10/2015 | これは英語版001-86148 Rev. *Aを翻訳した日本語版001-95866 Rev. **です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューション センター、メーカー代理店および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーション ページ](#)をご覧ください。

#### 製品

|             |                                                                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 車載用         | <a href="http://cypress.com/go/automotive">cypress.com/go/automotive</a>                                                             |

| クロック&バッファ   | <a href="http://cypress.com/go/clocks">cypress.com/go/clocks</a>                                                                     |

| インターフェース    | <a href="http://cypress.com/go/interface">cypress.com/go/interface</a>                                                               |

| 照明&電力制御     | <a href="http://cypress.com/go/powerpsoc">cypress.com/go/powerpsoc</a><br><a href="http://cypress.com/go/plc">cypress.com/go/plc</a> |

| メモリ         | <a href="http://cypress.com/go/memory">cypress.com/go/memory</a>                                                                     |

| PSoC        | <a href="http://cypress.com/go/psoc">cypress.com/go/psoc</a>                                                                         |

| タッチ センシング   | <a href="http://cypress.com/go/touch">cypress.com/go/touch</a>                                                                       |

| USB コントローラー | <a href="http://cypress.com/go/USB">cypress.com/go/USB</a>                                                                           |

| ワイヤレス／RF    | <a href="http://cypress.com/go/wireless">cypress.com/go/wireless</a>                                                                 |

#### PSoC® ソリューション

|                                                                                                     |

|-----------------------------------------------------------------------------------------------------|

| <a href="http://psoc.cypress.com/solutions">psoc.cypress.com/solutions</a>                          |

| <a href="#">PSoC 1</a>   <a href="#">PSoC 3</a>   <a href="#">PSoC 4</a>   <a href="#">PSoC 5LP</a> |

#### サイプレス開発者コミュニティ

[コミュニティ](#) | [フォーラム](#) | [ブログ](#) | [ビデオ](#) | [トレーニング](#)

#### テクニカル サポート

[cypress.com/go/support](http://cypress.com/go/support)

全てのソース コード（ソフトウェアおよび／またはファームウェア）はサイプレス セミコンダクタ社（以下「サイプレス」）が所有し、全世界の特許権保護（米国およびその他の国）、米国の著作権法ならびに国際協定の条項により保護され、かつそれらに従います。サイプレスが本書面によりライセンサーに付与するライセンスは、個人的、非独占かつ譲渡不能のライセンスであり、適用される契約で指定されたサイプレスの集積回路と併用されるライセンサーの製品のみをサポートするカスタム ソフトウェアおよび／またはカスタム ファームウェアを作成する目的に限って、サイプレスのソース コードの派生著作物をコピー、使用、変更そして作成するためのライセンス、ならびにサイプレスのソース コードおよび派生著作物をコンパイルするためのライセンスです。上記で指定された場合を除き、サイプレスの書面による明示的な許可なくして本ソース コードを複製、変更、変換、コンパイル、または表示することはすべて禁止します。

全てのソース コード（ソフトウェアおよび／またはファームウェア）はサイプレス セミコンダクタ社（以下「サイプレス」）が所有し、全世界の特許権保護（米国およびその他の国）、米国の著作権法ならびに国際協定の条項により保護され、かつそれらに従います。サイプレスが本書面によりライセンサーに付与するライセンスは、個人的、非独占かつ譲渡不能のライセンスであり、適用される契約で指定されたサイプレスの集積回路と併用されるライセンサーの製品のみをサポートするカスタム ソフトウェアおよび／またはカスタム ファームウェアを作成する目的に限って、サイプレスのソース コードの派生著作物をコピー、使用、変更そして作成するためのライセンス、ならびにサイプレスのソース コードおよび派生著作物をコンパイルするためのライセンスです。上記で指定された場合を除き、サイプレスの書面による明示的な許可なくして本ソース コードを複製、変更、変換、コンパイル、または表示することはすべて禁止します。

免責条項：サイプレスは、明示的または默示的を問わず、本資料に関するいかなる種類の保証も行いません。これには、商品性または特定目的への適合性の默示的な保証が含まれますが、これに限定されません。サイプレスは、本書面に記載される資料に対して今後予告なく変更を加える権利を留保します。サイプレスは、本書面に記載されるいかなる製品または回路を適用または使用したことによって生ずるいかなる責任も負いません。サイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

ソフトウェアの使用は、適用されるサイプレス ソフトウェア ライセンス契約によって制限され、かつ契約の対象となる場合があります。