# User manual for MA evaluation boards

EVAL\_AUDIO\_MA2304DNS\_B and EVAL\_AUDIO\_MA2304PNS\_B

### About this document

#### Scope and purpose

This document describes the use and operation of the EVAL\_AUDIO\_MA2304xNS\_B evaluation kit (EVK). The MA2304xNS EVK is an evaluation and demonstration kit for MA2304DNS and MA2304PNS proprietary multilevel amplifiers.

#### **Intended** audience

Audio amplifier design engineers.

# Attention: Please read this user manual before operating the board. When powering up the board, make sure to follow the instructions in the "MA2304xNS start-up sequence" section.

### Stuck or in need of help?

Support for Infineon's class D audio portfolio can be found quickly and easily by visiting the Class D Audio Amplifier IC Forum or community.infineon.com. The community forum features members of the audio applications team who are ready to provide timely support, helping you get your designs done quickly, reliably and right the first time.

### **Safety precautions**

*Note:* Please note the following warning regarding hazards associated with development systems.

### Table 1Safety precautions

**Caution:** The evaluation or reference board contains parts and assemblies sensitive to electrostatic discharge (ESD). Electrostatic control precautions are required when installing, testing, servicing or repairing the assembly. Component damage may result if ESD control procedures are not followed. If you are not familiar with ESD control procedures, refer to the applicable ESD protection handbooks and guidelines.

Table of contents

### Table of contents

| About this        | document                                 | 1 |

|-------------------|------------------------------------------|---|

| Stuck or in       | n need of help?                          | 1 |

| Safety pre        | cautions                                 | 1 |

| Table of co       | ontents                                  | 2 |

| 1 Over            | rview                                    | 3 |

| 1.1               | Board features and audio performance     | 3 |

| 1.2               | EVK device type                          | 3 |

| 2 Setu            | ıp guide                                 | 4 |

| 2.1               | EVK connections and interfaces           | 5 |

| 2.1.1             | EVAL_AUDIO_MA2304xNS_B board             | 5 |

| 2.1.2             | Interface boards                         | 6 |

| 2.1.3             | Optional heatsink                        | 7 |

| 2.1.4             | EVK headers and connectors               | 7 |

| 2.2               | Notes on the digital I/O breakout header | 9 |

| 3 Oper            | rating the demonstration board10         | D |

| 3.1               | Recommended operating conditions1        | 0 |

| 3.2               | Toggle switches1                         | 0 |

| 3.3               | Speaker load1                            | 0 |

| 3.4               | MERUS™ audio amplifier configurator1     | 1 |

| 3.5               | MA2304xNS start-up sequence1             | 1 |

| 4 Meas            | surement methods12                       | 2 |

| 5 Sche            | ematic14                                 | 4 |

| 5.1               | Main page14                              | 4 |

| 5.2               | Amp page1                                | 5 |

| 5.3               | Power page1                              | 6 |

| 5.4               | MCU page1                                | 7 |

| 6 PCB             | layout18                                 | 8 |

| 7 Bill c          | of materials2                            | 1 |

| <b>Revision</b> h | istory2                                  | 5 |

| Disclaimer        | r21                                      | 6 |

Overview

### 1 Overview

The demonstration board EVAL\_AUDIO\_MA2304xNS\_B is an evaluation and demonstration board for MERUS™ audio's MA2304DNS and MA2304PNS amplifiers.

It contains digital input/output (I/O) and a variety of output and setup/selection features. It also contains one onboard buck power supply generator (1.8 V/3.3 V selectable) so only one external power supply (PVDD) is necessary.

The board can be used to evaluate or demonstrate key features/advantages of the MERUS<sup>™</sup> technology:

- Energy efficiency

- Power losses at typical audio listening levels

- Idle power loss

- Adaptive power management system

- No output filter components

- Solution cost and size reduction

- Audio performance

- THD performance and audio quality

### **1.1** Board features and audio performance

| • | Number of audio channels        | 2 (BTL) or 1 (PBTL)                                   |

|---|---------------------------------|-------------------------------------------------------|

| ٠ | Audio input format              | Digital (I <sup>2</sup> S, LJF, RJF or TDM)           |

| ٠ | Typical supply voltage          | 18 V (PVDD)                                           |

| ٠ | Output noise level              | 52 $\mu V_{\text{RMS}}$ (high audio performance mode) |

| ٠ | Dynamic range                   | 106 dB (high audio performance mode)                  |

| ٠ | Idle consumption at PVDD = 18 V | 52 mW (low power consumption mode)                    |

| ٠ | Efficiency                      |                                                       |

|   | - 1W,8Ω                         | More than 79 percent                                  |

|   | – Full-scale, 8 Ω               | More than 90 percent                                  |

Note: Idle consumption is the sum of output stage (PVDD) current, VDD and VDD\_IO supply current. As all the supplies are tied to PVDD, the efficiency of the buck converter should be considered when measuring idle current consumption directly from PVDD. Features on the EVK make it possible to break the input and output of the buck converters for these purposes (see Table 3). Please refer to the MA2304xNS device datasheet for exact current figures.

### **1.2 EVK device type**

The type of device – MA2304DNS/MA2304PNS – is printed on the top of the EVK, and is also stated on the serial number label on the bottom side of the EVK PCB.

### 2 Setup guide

The following is included in the MA2304xNS evaluation kit:

- EVAL\_AUDIO\_MA2304xNS\_B board

- I<sup>2</sup>S interface boards: analog in, S/PDIF coax and S/PDIF optical

- Micro-USB cable

- 22 µH power inductor

Additional equipment required for operation and evaluation:

- 10 to 20 V DC power supply capable of driving 6 A (BTL) or 12 A (PBTL)

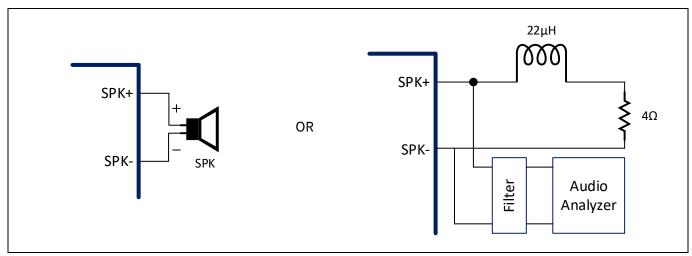

- Loudspeaker and speaker wires, as shown in Figure 1

In addition, for datasheet spec testing, as shown in Figure 1:

- $2 \text{ to } 8 \Omega \text{ resistor load}$

- Audio analyzer with class D measurement filter

Figure 1 Setup for "speaker test" or "datasheet spec test"

### 2.1 EVK connections and interfaces

The MA2304xNS EVK includes the main EVAL\_AUDIO\_MA2304xNS\_B board and three interface boards.

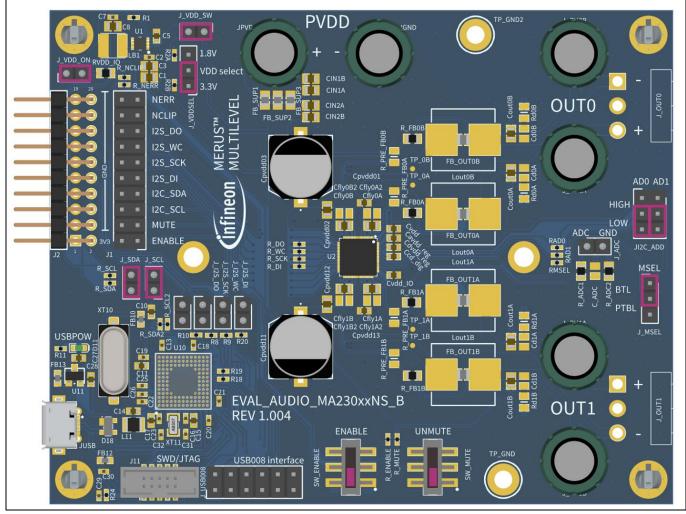

### 2.1.1 EVAL\_AUDIO\_MA2304xNS\_B board

The board features MA2304xNS silicon, digital I/O headers, enable and mute switches, speaker terminals, power supply terminal blocks, and a USB port.

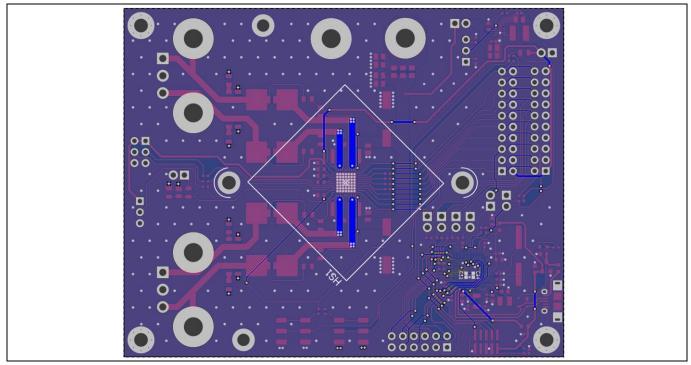

Figure 2 EVAL\_AUDIO\_MA230xxNS\_B board (top view)

### Setup guide

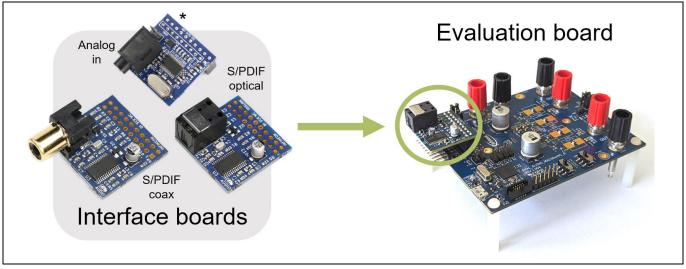

### 2.1.2 Interface boards

Three interface boards are included: analog in, S/PDIF coax and S/PDIF optical. These are plugged in to the J1 digital I/O breakout header for simple evaluation.

Figure 3 Interface boards

There is no need to configure the MA2304xNS when using these interface boards, as its digital audio output format matches the MA2304xNS defaults.

Note that the interface boards are not compatible with a 1.8 V supply. When using the onboard buck converter, ensure that the MA2304xNS board's VDD\_SEL jumper is configured for 3.3 V (pins 1 and 2).

Interface board input/output specifications are provided in Table 2.

| Interface board        | Input                            | Output                                         |

|------------------------|----------------------------------|------------------------------------------------|

| Analog in <sup>1</sup> | 3.5 mm (1/8 in.) stereo TRS jack | I <sup>2</sup> S, 24-bit serial audio at 3.3 V |

|                        | 2.1 V <sub>RMS</sub> full-scale  | SCK = 64 x WCK                                 |

|                        |                                  | WCK = 48 kHz                                   |

| S/PDIF coax            | RCA jack                         | I <sup>2</sup> S, 24-bit serial audio at 3.3 V |

|                        | 0.2 V minimum, 5 V tolerant      | SCK = 64 x WCK                                 |

|                        | 32 to 96 kHz support             | WCK = 32 to 96 kHz                             |

| S/PDIF optical         | Optical input jack               | I <sup>2</sup> S, 24-bit serial audio at 3.3 V |

|                        | 32 to 96 kHz support             | SCK = 64 x WCK                                 |

|                        |                                  | WCK = 32 to 96 kHz                             |

| Table 2 | Interface board I/O specifications |

|---------|------------------------------------|

|---------|------------------------------------|

<sup>1</sup>Noise measurements and other specs will show degraded performance when using the analog in interface board.

### 2.1.3 Optional heatsink

EVAL\_AUDIO\_MA2304xNS\_B boards include holes for an optional heatsink. When high continuous output power is required, it is recommended to use a heatsink. Recommended parts are Wakefield-Vette 960-31-28-D-AB-0. Thermal conductivity material may be 3M Electronic Specialty 5519-155x210.

Figure 4 Recommended optional heatsink for continuous output power evaluation

### 2.1.4 EVK headers and connectors

The following table provides a description of each jumper, header, switch and test point. Defaults are shown in the "Comment" column.

| Table 5 EVK neaders and connectors |                                                                       |                                    |  |

|------------------------------------|-----------------------------------------------------------------------|------------------------------------|--|

| Name                               | Description                                                           | Comment                            |  |

| J1                                 | Digital I/O breakout header. Refer to Section 2.2 for details.        | I/O pins. Do not jumper.           |  |

| J2                                 | Interface board connector                                             | I/O pins. Do not jumper.           |  |

| J_MSEL                             | Selects amplifier output mode between PBTL (L) and BTL (H)            | Default:                           |  |

|                                    |                                                                       | BTL (pins 1 and 2)                 |  |

| JI2C_ADD                           | These headers select the I <sup>2</sup> C slave address (see Table 4) | Default:                           |  |

|                                    |                                                                       | I <sup>2</sup> C address 0b0100000 |  |

|                                    |                                                                       | AD1: Low (pins 4 and 6)            |  |

|                                    |                                                                       | AD0: Low (pins 3 and 5)            |  |

| SW_ENABLE                          | Controls the amplifier's ENABLE pin. Sets the amplifier into          | Default:                           |  |

|                                    | enabled state when set to on.                                         | Off                                |  |

| SW_MUTE                            | Controls the amplifier's NMUTE pin. Mutes the amplifier when          | Default:                           |  |

|                                    | set to mute.                                                          | Mute                               |  |

| J_CH0A                             | OUT0A speaker connection                                              | CH0 positive speaker               |  |

|                                    |                                                                       | output terminal                    |  |

| J_CH0B                             | OUT0B speaker connection                                              | CH0 negative speaker               |  |

|                                    |                                                                       | output terminal                    |  |

| J_CH1A                             | OUT1A speaker connection                                              | CH1 positive speaker               |  |

|                                    |                                                                       | output terminal                    |  |

| J_CH1B                             | OUT1B speaker connection                                              | CH1 negative speaker               |  |

|                                    |                                                                       | output terminal                    |  |

### User manual for MA evaluation boards EVAL\_AUDIO\_MA2304DNS\_B and EVAL\_AUDIO\_MA2304PNS\_B

### Setup guide

| Name         | Description                                               | Comment              |

|--------------|-----------------------------------------------------------|----------------------|

| J_OUT0       | OUT0 speaker connector                                    | Pin 1: OUT0B         |

|              |                                                           | Pin 2: GND           |

|              |                                                           | Pin 3: OUT0A         |

| J_OUT1       | OUT1 speaker connector                                    | Pin 1: OUT1A         |

|              |                                                           | Pin 2: GND           |

|              |                                                           | Pin 3: OUT1B         |

| J_ADC        | AUX_ADC input header                                      | Pin 1: ADC input     |

|              |                                                           | Pin 2: GND           |

| J_VDDSEL     | Sets the onboard buck converter output as:                | Default:             |

|              | 3.3 V (pins 1 and 2)                                      | 3.3 V (pins 1 and 2) |

|              | 1.8 V (pins 2 and 3)                                      |                      |

| J_VDD_SW     | Provides the option to measure PVDD current into the buck | Default:             |

|              | converter                                                 | Jumpered             |

| J_VDD_ON     | Provides the option to measure the buck converter output  | Default:             |

|              | current                                                   | Jumpered             |

| J_SCL        | Provides the option to isolate I2C_SCL from the MCU       | Default:             |

|              |                                                           | Jumpered             |

| J_SDA        | Provides the option to isolate I2C_SDA from the MCU       | Default:             |

|              |                                                           | Jumpered             |

| J_I2S_SCK    | Provides the option to isolate I2S_SCK from the MCU       | Default:             |

|              |                                                           | Removed              |

| J_I2S_WC     | Provides the option to isolate I2S_WC from the MCU        | Default:             |

|              |                                                           | Removed              |

| J_I2S_DO     | Provides the option to isolate I2S_DO from the MCU        | Default:             |

|              |                                                           | Removed              |

| J_I2S_DI     | Provides the option to isolate I2S_DI from the MCU        | Default:             |

|              |                                                           | Removed              |

| J11          | SWD/JTAG header for the onboard MCU                       |                      |

| J_USB008     | For future use                                            |                      |

| <br>TP_OUT0A | Direct connection to device output node OUT0A             | Output measurement   |

| _            |                                                           | pin                  |

| TP_OUT0B     | Direct connection to device output node OUT0B             | Output measurement   |

|              |                                                           | pin                  |

| TP_OUT1A     | Direct connection to device output node OUT1A             | Output measurement   |

|              |                                                           | pin                  |

| TP_OUT1B     | Direct connection to device output node OUT1B             | Output measurement   |

|              |                                                           | pin                  |

| TP_GND       | Ground test points                                        |                      |

| TP_GND2      |                                                           |                      |

| MH1          | Ground-connected mounting holes                           |                      |

| MH2          |                                                           |                      |

### Setup guide

| Name | Description | Comment |

|------|-------------|---------|

| MH3  |             |         |

| MH4  |             |         |

#### Table 4 I<sup>2</sup>C address decoding (JI2C\_ADD)

| I <sup>2</sup> C device address | AD1 | AD0 | 7-bit I <sup>2</sup> C address |  |

|---------------------------------|-----|-----|--------------------------------|--|

| 0x20                            | L   | L   | 0b0100000                      |  |

| 0x21                            | L   | Н   | 0b0100001                      |  |

| 0x22                            | Н   | L   | 0b0100010                      |  |

| 0x23                            | Н   | Н   | 0b0100011                      |  |

### 2.2 Notes on the digital I/O breakout header

The digital I/O breakout header (J1) provides access to audio and control signals (I<sup>2</sup>S and I<sup>2</sup>C, respectively) as well as several MA2304xNS GPIO pins and the onboard VDD supply (3.3 or 1.8 V). The J1 header is meant for use with the interface boards, and/or external connections (external I<sup>2</sup>S, MCU, etc.) for measurements and debugging. The J2 header contains exactly the same signals as J1 but can be used for monitoring the I/O digital signals.

The MA2304xNS acts as an I<sup>2</sup>S slave, accepting SCK (bit clock) and WC (word clock) as inputs, with SCK = 64 x WC as default.

| Pin | Signal | Signal     | Pin |  |

|-----|--------|------------|-----|--|

| 20  | GND    | /AMP_ERR   | 19  |  |

| 18  | GND    | /AMP_CLIP  | 17  |  |

| 16  | GND    | I2S_DO     | 15  |  |

| 14  | GND    | I2S_WC     | 13  |  |

| 12  | GND    | I2S_SCK    | 11  |  |

| 10  | GND    | 12S_DI     | 9   |  |

| 8   | GND    | I2C_SDA    | 7   |  |

| 6   | GND    | I2C_SCL    | 5   |  |

| 4   | GND    | /AMP_MUTE  | 3   |  |

| 2   | 3.3V   | AMP_ENABLE | 1   |  |

|     |        |            |     |  |

#### Table 5Digital I/O breakout header

### **3 Operating the demonstration board**

### **3.1** Recommended operating conditions

#### Table 6 Recommended operating conditions

| Parameter                  | Minimum | Nominal | Maximum | Unit |

|----------------------------|---------|---------|---------|------|

| PVDD                       | 10      | 18      | 20      | V    |

| Output peak current (BTL)  |         |         | 6.0     | А    |

| Output peak current (PBTL) |         |         | 12.0    | А    |

### 3.2 Toggle switches

The board has two MA2304xNS-related toggle switches, as shown in Table 7. The toggle switches have the following functions:

#### Table 7Switch function

| Switch    | Function                            |

|-----------|-------------------------------------|

| SW_ENABLE | Off/enable (default set to "off")   |

| SW_MUTE   | Mute/unmute (default set to "mute") |

### 3.3 Speaker load

The demonstration board is configured as a filterless amplifier. This means that no LC filter is placed between the amplifier outputs and the load. In normal use the amplifier relies on the inherent inductance of the loudspeaker, so no extra inductance is needed.

Inductors for use in series with power resistors are included with the demonstration board. These can be used when making any measurements without a real loudspeaker as the load, and having no external low-pass filter (LPF) in front of the audio analyzer input section.

Please note that many audio measurement analyzers do not perform correctly when connected directly to a filterless amplifier output. Please refer to Section 4 for more information on measurement methods.

### 3.4 MERUS<sup>™</sup> audio amplifier configurator

The demonstration board is used with PC graphical user interface (GUI) software to control the MA2304xNS device.

The MA2304xNS can play audio by default without configuration, but to take advantage of the many features the chip offers it is necessary to configure the device.

Refer to the MERUS<sup>™</sup> audio amplifier configurator user manual for details on how to install and use this software.

Figure 5 MA2304DNS GUI main window

### 3.5 MA2304xNS start-up sequence

Follow this (recommended) sequence to start the board:

- 1. Make sure toggle buttons are in "off" and "mute" positions.

- 2. Connect all cables (speakers/load, USB and power) to the EVK.

- 3. Connect an external I<sup>2</sup>S digital audio source to the EVK digital I/O header (J1). The EVK default I/O voltage is 3.3 V.

- 4. Turn on the PVDD power supply.

- 5. Make sure the I<sup>2</sup>S clocks are present before enabling the amplifier.

- 6. Start board by setting the SW\_ENABLE toggle switch to the "on" position.

- 7. Start playing sound by setting the SW\_MUTE toggle switch to the "unmute" position.

Mute and turn off the PVDD power supply when finished.

**Measurement methods**

### 4 Measurement methods

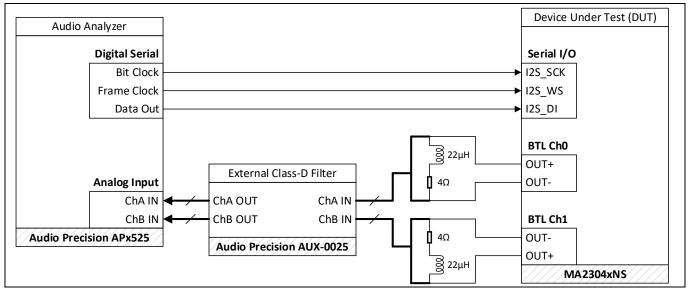

Setting up a reliable measurement configuration for the MA2304DNS or the MA2304PNS takes a little more effort than for linear amplifiers, and even "regular" switching amplifiers. This is mainly because the MA2304xNS is a filterless amplifier, which means it does not require an external (usually expensive and bulky) LC filter to remove switching residuals. The filterless application is enabled by the MERUS<sup>™</sup> audio multilevel technique, which ensures the switching residual is orders lower compared to "regular" switching amplifiers. For more information on the multilevel switching technique, please refer to the datasheet.

To obtain reliable measurement results, the MA2304xNS devices require a separate external LPF in front of the input stage of the audio analyzer. Most audio analyzers are bandwidth-limited at their input stage, which means they cannot follow the rapid changes of the amplifier's output stage. This can result in inaccurate and high THD+N measurements.

Figure 6 shows the recommended measurement setup. The setup shows a LPF stage (AUX-0025) in front of the audio analyzer (APx525 with the serial interface I/O option installed). In this case the measurement setup has been built around Audio Precision hardware, but this can also be some other audio analyzer hardware. Please note that it is recommended to use a balanced input measurement configuration.

Figure 6 Recommended audio measurement setup

#### Measurement methods

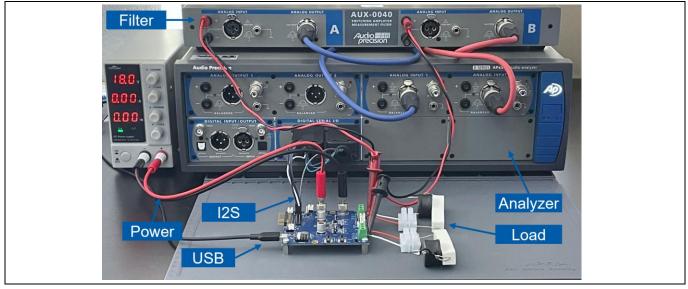

Figure 7 shows an example measurement setup using an 8  $\Omega/22 \mu$ H load, similar to the setup shown in Figure 6.

FFT Spectrum 4/7/2022 3:20:32.251 PM Data AD 0 🗹 🔳 Ch1 🗹 📕 Ch2 -20 -40 -60 08- 100- 100 -120 -140 -160 -180 L 20 50 100 200 2k 5k 10k 20k 500 1k Frequency (Hz) THD+N Level dBrA - 🖂 - 🔅 Ľ × -107.533 dBrA Ch1 Ch2 -108.217dBrA

Figure 8 shows an example dynamic range measurement performed with the previous measurement setup.

### Figure 8

Dynamic range measurement example

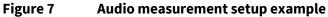

### 5 Schematic

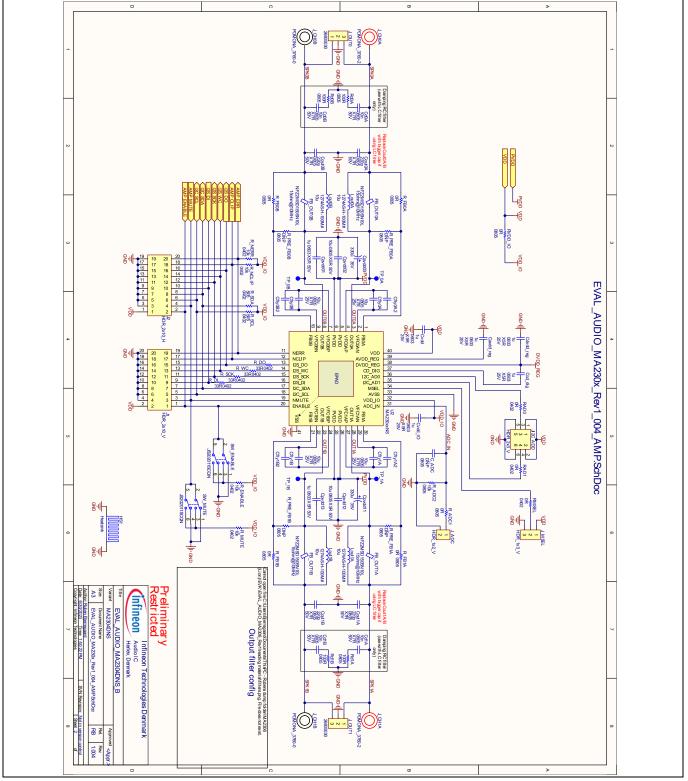

Figure 9 Main page

### 5.2 Amp page

Amp page

### User manual for MA evaluation boards EVAL\_AUDIO\_MA2304DNS\_B and EVAL\_AUDIO\_MA2304PNS\_B Schematic

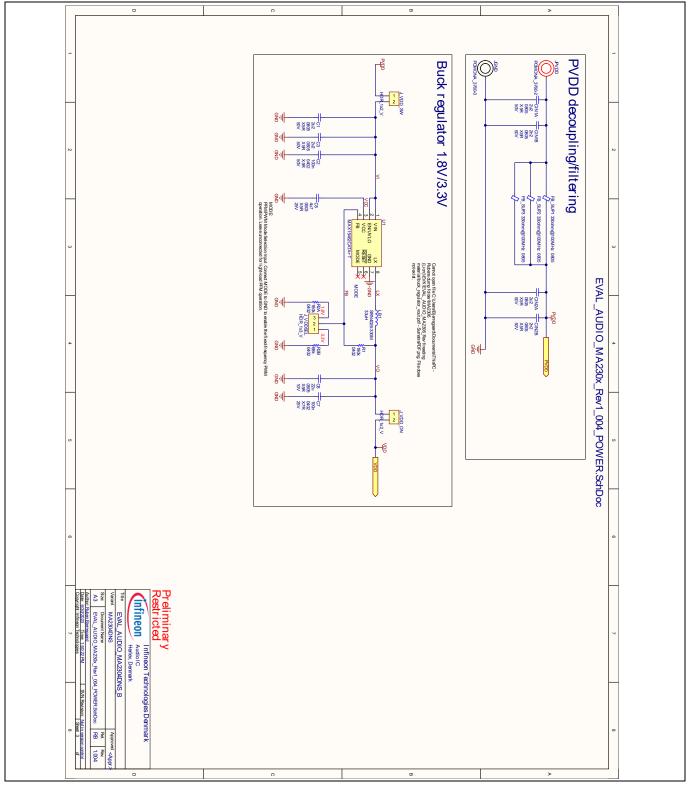

### 5.3 Power page

Power page

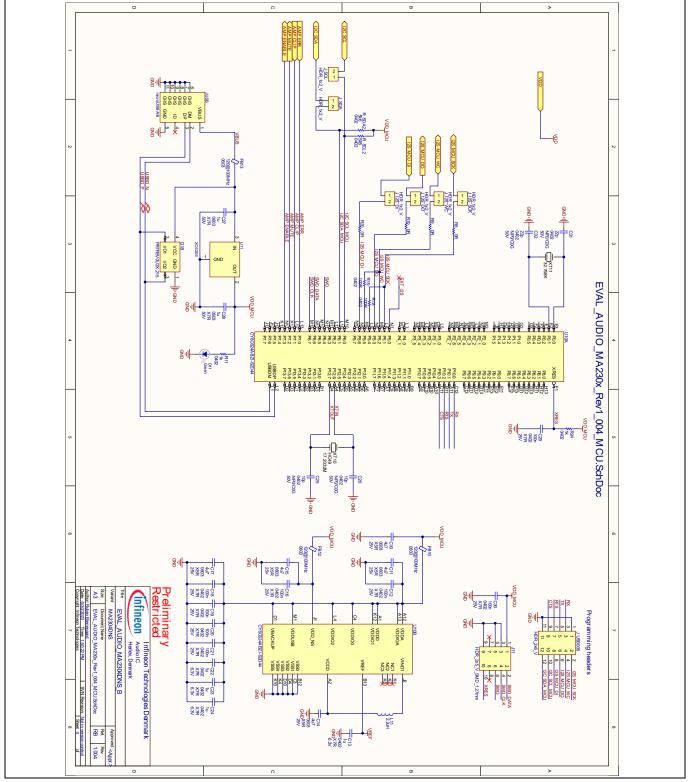

### 5.4 MCU page

Figure 12

MCU page

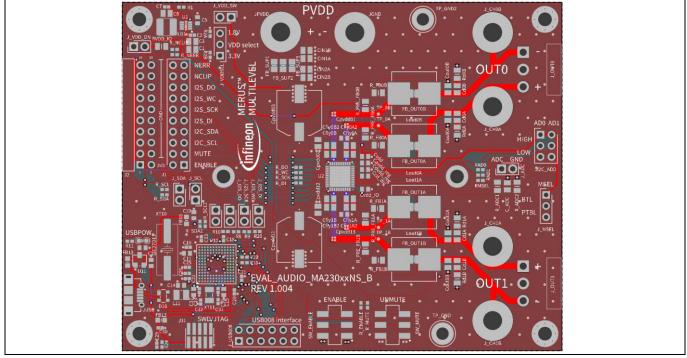

## 6 PCB layout

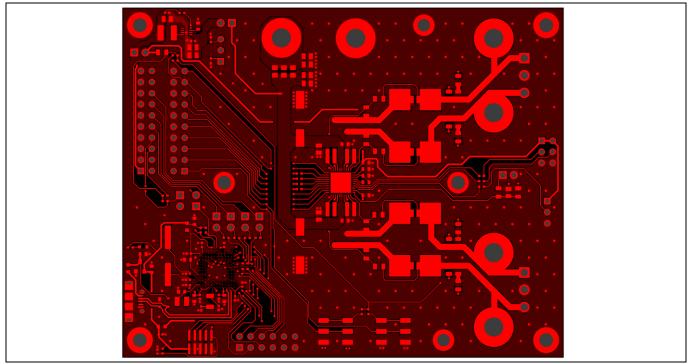

Figure 13 PCB layout (top x-ray view)

Figure 14 PCB layout (top layer)

### PCB layout

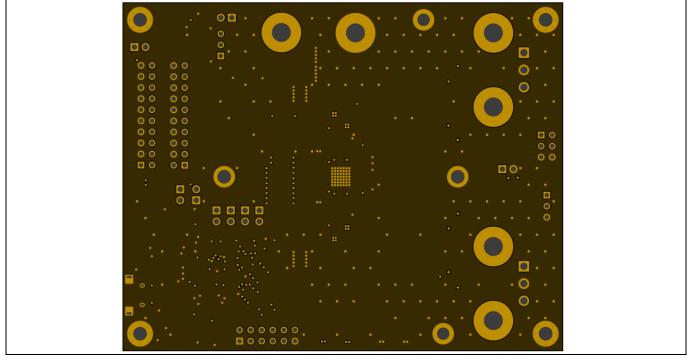

Figure 15 PCB layout (layer 1)

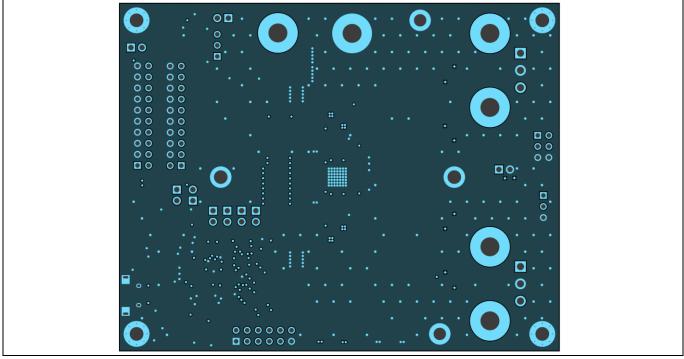

Figure 16 PCB layout (layer 2)

### PCB layout

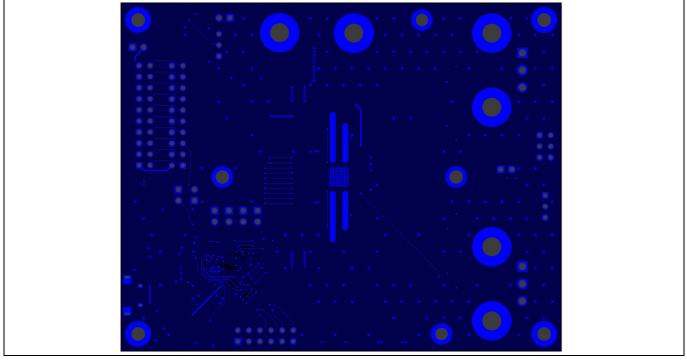

Figure 17 PCB layout (bottom layer)

Figure 18 PCB layout (bottom x-ray view, mirrored)

| Table 8 | <b>Bill of materials</b> |

|---------|--------------------------|

| Iableo  | Dill UI IIIalei Ialo     |

| S. no. | Reference                            | Qty. | Description                                       | Manufacturer             | Part number                        |

|--------|--------------------------------------|------|---------------------------------------------------|--------------------------|------------------------------------|

| 1      | XT11                                 | 1    | Crystal 32.7680 kHz<br>9 pF SMD                   | Abracon                  | ABS07-32.768KHZ-9-1-T              |

| 2      | XT10                                 | 1    | 2.2 μF 50 V X5R 0805                              | Würth Elektronik         | WE-XTAL QUARTZ<br>CRYSTAL 17.20320 |

| 3      | U11                                  | 1    | 40 dB at (1 kHz)<br>100 mA 240 mV at<br>(50 mA) F | Torex                    | XC6206P332MR                       |

| 4      | U10                                  | 1    | IC dual-core MCU<br>32 B 1 M 124 BGA              | Cypress<br>Semiconductor | CY8C624ABZI-S2D44                  |

| 5      | U2                                   | 1    | DUT                                               | Infineon<br>Technologies | MA2304xxx                          |

| 6      | U1                                   | 1    | IC buck regulator<br>ADJ 300 mA 8TDFN             | Maxim<br>Integrated      | MAX15462CATA+T                     |

| 7      | TP_0A, TP_0B,<br>TP_1A, TP_1B        | 4    |                                                   |                          |                                    |

| 8      | SW_ENABLE,<br>SW_MUTE                | 2    | Slide switch DPDT<br>300 mA 6 V                   | C&K<br>Components        | JS202011SCQN                       |

| 9      | SPA1, SPA2, SPA3,<br>SPA4            | 4    | Hex standoff M3<br>Nylon 30 mm                    | Essentra<br>Components   | MTS-30                             |

| 10     | SCRW1, SCRW2,<br>SCRW3, SCRW4        | 4    | Slotted mach. screw<br>pan M3X0.5                 | Keystone                 | 29341                              |

| 11     | RAD0, RAD1, RMSEL                    | 3    | Resistor 0 Ω jumper<br>1/16 W 0402                | Vishay/Dale              | CRCW04020000Z0EDC                  |

| 12     | R_SCL, R_SCL2,<br>R_SDA, R_SDA2      | 4    | Resistor SMD 5.6K Ω<br>1% 1/10 W 0402             | Panasonic                | ERJ-2RKF5601X                      |

| 13     | R_FB0A, R_FB0B,<br>R_FB1A, R_FB1B    | 4    | Resistor SMD 0 Ω<br>jumper 1/8W 0805              | Bourns                   | CR0805-J/-000ELF                   |

| 14     | R_ENABLE, R_MUTE,<br>R_NCLIP, R_NERR | 4    | Resistor 10K Ω 1%<br>1/16W 0402                   | Vishay/Dale              | CRCW040210K0FKEDC                  |

| 15     | R_DI, R_DO, R_SCK,<br>R_WC           | 4    | Resistor 33 Ω 1%<br>1/16W 0402                    | Vishay/Dale              | CRCW040233R0FKEDC                  |

| 16     | R_ADC2                               | 1    | Resistor SMD 10K Ω<br>1% 1/8W 0805                | Bourns                   | CR0805-FX-1002ELF                  |

| 17     | R_ADC1, RVDD_IO                      | 2    | Resistor 0 Ω jumper<br>1/8 W 0805                 | Yageo                    | AC0805FR-070RL                     |

| 18     | R18, R19                             | 2    | Resistor SMD 100 Ω<br>1% 1/10 W 0402              | Panasonic                | ERJ-2RKF1000X                      |

| 19     | R11, R24                             | 2    | Resistor SMD 1K Ω<br>1% 1/10 W 0402               | Panasonic                | ERJ-2RKF1001X                      |

| S. no. | Reference                                                                                         | Qty. | Description                                         | Manufacturer     | Part number      |

|--------|---------------------------------------------------------------------------------------------------|------|-----------------------------------------------------|------------------|------------------|

| 20     | R8, R9, R10, R20                                                                                  | 4    | Resistor 0 Ω jumper<br>1/16 W 0402                  | Yageo            | RC0402FR-070RL   |

| 21     | R2B                                                                                               | 1    | Resistor SMD 68K Ω<br>1% 1/10 W 0402                | Panasonic        | ERJ-2RKF6802X    |

| 22     | R1, R2A                                                                                           | 2    | Resistor SMD<br>180K Ω 1% 1/10 W<br>0402            | Panasonic        | ERJ-2RKF1803X    |

| 23     | MH1, MH2, MH3, MH4                                                                                | 4    |                                                     |                  |                  |

| 24     | LB1                                                                                               | 1    | Fixed inductor<br>33 μΗ 500 mA<br>366 mΩ SMD        | Bourns           | SRN4026-330M     |

| 25     | L11                                                                                               | 1    | Fixed inductor<br>2.2 μH 1.15 A<br>216 mΩ SM        | Sunlord          | SWPA252012S2R2MT |

| 26     | JUSB                                                                                              | 1    | Connector receptor<br>micro-USB AB 5P<br>SMD RA     | Molex            | 47589-0001       |

| 27     | JP1, JP2, JP3, JP4,<br>JP5, JP6, JP7, JP8,<br>JP9, JP10, JP11,<br>JP12, JP13, JP14,<br>JP15, JP16 | 8    | Jumper with test<br>point 1 x 2 pins<br>2.54 mm     | Würth Elektronik | 60900213421      |

| 28     | JI2C_ADD                                                                                          | 1    | Vertical header<br>connector 6<br>position 2.54 mm  | Würth Elektronik | 61300621121      |

| 29     | J_USB008                                                                                          | 1    | Vertical header<br>connector 12<br>position 2.54 mm | Würth Elektronik | 61301221121      |

| 30     | J_MSEL, J_VDDSEL                                                                                  | 2    | Vertical header<br>connector 3<br>position 2.54 mm  | Würth Elektronik | 61300311121      |

| 31     | J_CH0B, J_CH1B,<br>JGND                                                                           | 3    | Connector bind post knurled black                   | Pomona           | 3760-0           |

| 32     | J_CH0A, J_CH1A,<br>JPVDD                                                                          | 3    | Connector bind post knurled red                     | Pomona           | 3760-2           |

| 33     | J_ADC, J_I2S_DI,<br>J_I2S_DO,<br>J_I2S_SCK,<br>J_I2S_WC, J_SCL,<br>J_SDA, J_VDD_ON,<br>J_VDD_SW   | 9    | Vertical header<br>connector 2<br>position 2.54 mm  | Würth Elektronik | 61300211121      |

| 34     | J11                                                                                               | 1    | Header connector<br>SMD 10 position<br>1.27 mm      | CNC Tech         | 3221-10-0300-00  |

| S. no. | Reference                                          | Qty. | Description                                         | Manufacturer                     | Part number         |

|--------|----------------------------------------------------|------|-----------------------------------------------------|----------------------------------|---------------------|

| 35     | J2                                                 | 1    | Header connector<br>R/A 20 position<br>2.54 mm      | Würth Elektronik                 | 61302021021         |

| 36     | J1                                                 | 1    | Vertical header<br>connector 20<br>position 2.54 mm | Würth Elektronik                 | 61302021121         |

| 37     | HS1                                                | 1    | Heatsink 31 x<br>23 mm diameter<br>push pin         | Wakefield                        | 960-31-23-D-AB-0    |

| 38     | FB_SUP1, FB_SUP2,<br>FB_SUP3                       | 3    | Ferrite bead 330 Ω<br>0805 1LN                      | Murata                           | BLM21SP331SZ1#      |

| 39     | FB_OUT0A,<br>FB_OUT0B,<br>FB_OUT1A,<br>FB_OUT1B    | 4    | Ferrite bead 15 Ω<br>0806 1LN                       | Murata<br>Electronics            | NFZ2MSD150SN10L     |

| 40     | FB10, FB12, FB13                                   | 3    | Ferrite bead 120 Ω<br>0603 1LN                      | Murata                           | BLM18KG121TN1D      |

| 41     | D18                                                | 1    | TVS diode 5.5 V WM<br>SOT-143B                      | NXP<br>Semiconductors            | PRTR5V0U2X,215      |

| 42     | D11                                                | 1    | LED green clear chip<br>SMD                         | Lite-On                          | LTST-C190KGKT       |

| 43     | Cpvdd03, Cpvdd11                                   | 2    | Aluminum capacitor<br>330 μF 20% 35 V<br>SMD        | Vishay/BC<br>Components          | MAL215099003E3      |

| 44     | Cpvdd02, Cpvdd12                                   | 2    | Ceramic capacitor<br>10 µF 50 V X5R 0805            | Murata                           | GRM21BR61H106KE43L  |

| 45     | Cpvdd01, Cpvdd13                                   | 2    | Ceramic capacitor<br>1 μF 50 V X5R 0603             | ток                              | C1608X5R1H105K080AB |

| 46     | Cout0A, Cout0B,<br>Cout1A, Cout1B                  | 4    | Ceramic capacitor<br>220 pF 50 V X7R<br>0805        | Kemet                            | C0805C221K5RAC      |

| 47     | CIN1B, CIN2B                                       | 2    | Ceramic capacitor<br>2200 pF 50 V X7R<br>0805       | Murata                           | GCJ216R71H222KA01D  |

| 48     | CIN1A, CIN2A                                       | 2    | Ceramic capacitor<br>2.2 μF 50 V X7R 0805           | Taiyo Yuden                      | UMK212BB7225KG-T    |

| 49     | Cfly0A, Cfly0B,<br>Cfly1A, Cfly1B                  | 4    | Ceramic capacitor<br>10 μF 25 V X7R 0805            | Samsung<br>Electro-<br>Mechanics | CL21B106KAYQNNE     |

| 50     | Cavdd_reg, Ccd_dig,<br>Cdvdd_reg, Cvdd,<br>Cvdd_IO | 5    | Ceramic capacitor<br>1 µF 25 V X5R 0603             | Samsung                          | CL10A105KA8NFNC     |

| 51     | C31, C32                                           | 2    | Ceramic capacitor<br>22 pF 50 V C0G/NP0<br>0402     | Kemet                            | CBR04C220J5GACAUTO  |

| S. no. | Reference                                | Qty. | Description                                     | Manufacturer | Part number          |

|--------|------------------------------------------|------|-------------------------------------------------|--------------|----------------------|

| 52     | C27, C28                                 | 2    | Ceramic capacitor<br>1 μF 50 V X5R 0603         | Murata       | GRT188R61H105ME13D   |

| 53     | C25, C26                                 | 2    | Ceramic capacitor<br>10 pF 50 V C0G/NP0<br>0402 | Kemet        | C0402C100F5GACTU     |

| 54     | C13, C22, C23                            | 3    | Ceramic capacitor<br>1 μF 6.3 V X6S 0402        | ТДК          | CGB2A1X6S0J105M033BC |

| 55     | C8                                       | 1    | Ceramic capacitor<br>22 μF 10 V X5R 0805        | Samsung      | CL21A226MPCLRNC      |

| 56     | C7, C16, C18, C19,<br>C20, C21, C29, C30 | 8    | Ceramic capacitor<br>0.1 μF 25 V X5R 0402       | Samsung      | CL05A104KA5NNND      |

| 57     | C5, C10, C11, C14,<br>C15, C17           | 6    | Ceramic capacitor<br>4.7 μF 25 V X5R 0603       | Samsung      | CL10A475KA8NQNC      |

| 58     | C2                                       | 1    | Ceramic capacitor<br>0.1 μF 50 V X7R 0402       | Murata       | GRM155R71H104KE14D   |

| 59     | C1, C3                                   | 2    | Ceramic capacitor<br>2.2 μF 50 V X5R 0805       | Samsung      | CL21A225KBQNNNE      |

### **Revision history**

| Document<br>version | Date of release | Description of changes |

|---------------------|-----------------|------------------------|

| V 1.0               | 2023-07-14      | Initial release        |

| V 1.1               | 2023-09-22      | Updated Figure 3       |

**Trademarks** All referenced product or service names and trademarks are the property of their respective owners.

Edition 2023-09-22 Published by Infineon Technologies AG 81726 Munich, Germany

© 2023 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

Document reference UM\_2307\_PL88\_2307\_020213

#### IMPORTANT NOTICE

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of noninfringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.