# **About this document**

## Scope and purpose

Introduction of the hybrid-flyback (HFB) converter and its novel digital control IC XDP™ digital power XDPS2201, converter main stage design, parametrization via .dp vision tool and PCB layout hints.

#### **Intended audience**

Design engineers of power supply with high performance and ultrahigh power density.

## **Table of contents**

|       | About this document                                 | 1  |

|-------|-----------------------------------------------------|----|

|       | Table of contents                                   | 1  |

| 1     | Introduction                                        | 3  |

| 2     | HFB topology and operating principle                | 4  |

| 2.1   | Hybrid-flyback topology                             | 4  |

| 2.2   | Operating principle                                 | 6  |

| 2.2.1 | Voltage transfer function                           | 7  |

| 2.2.2 | Current transfer function                           | 7  |

| 2.2.3 | Two resonant periods                                | 8  |

| 3     | HFB control IC XDPS2201                             | 10 |

| 3.1   | Pin configuration                                   | 10 |

| 3.2   | Peak current control and zero-voltage turn-on       | 11 |

| 3.3   | Output regulation and operation modes               | 12 |

| 3.4   | Frequency jitter                                    | 15 |

| 3.5   | Protection                                          | 16 |

| 4     | HFB power stage design                              | 18 |

| 4.1   | Key initial design parameters                       | 18 |

| 4.2   | Transformer key parameters and resonant capacitance | 18 |

| 4.2.1 | Transformer key parameters                          | 18 |

| 4.2.2 | Resonant capacitor                                  | 21 |

| 4.2.3 | Design constraints                                  | 22 |

| 4.3   | Components connected to IC pins                     | 24 |

| 4.3.1 | CS pin: shunt resistor                              | 24 |

| 4.3.2 | VS pin: voltage divider                             | 25 |

| 4.3.3 | Auxiliary winding turns ratio and voltage divider   | 25 |

| 4.3.4 | HV pin: HV resistor                                 | 26 |

| 4.3.5 | FB pin: filter capacitor                            | 27 |

| 4.3.6 | FMIO pin: external thermal resistor                 | 27 |

| 4.3.7 | LSGD and HSGD: gate resistor and bootstrap circuit  | 27 |

|       |                                                     |    |

# Table of contents

| 4.3.8  | VCC supply: VCC capacitor            | 27 |

|--------|--------------------------------------|----|

| 4.4    | Output regulator                     | 28 |

| 5      | Parameterization                     | 29 |

| 5.1    | Required hardware                    | 29 |

| 5.2    | .dp vision tool                      | 30 |

| 5.2.1  | .dp vision GUI                       | 30 |

| 5.2.2  | Parameter value change               | 31 |

| 5.2.3  | Procedure for test configuration set | 31 |

| 5.2.4  | Procedure for burn configuration set | 32 |

| 5.2.5  | .csv file                            | 33 |

| 5.3    | Configurable parameters              | 34 |

| 5.3.1  | System setting                       | 35 |

| 5.3.2  | Dimensioning                         | 36 |

| 5.3.3  | HB                                   | 39 |

| 5.3.4  | RVS/DCM operation                    | 42 |

| 5.3.5  | Burst                                | 43 |

| 5.3.6  | Start-up                             |    |

| 5.3.7  | Protections                          | 49 |

| 5.3.8  | Mode threshold                       |    |

| 5.3.9  | Jitter                               | 57 |

| 5.3.10 | Others                               | 58 |

| 6      | PCB design tips                      | 59 |

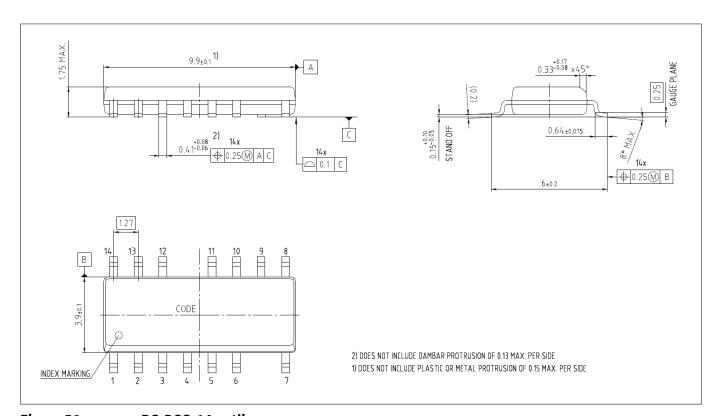

| 6.1    | IC package and footprint             | 59 |

| 6.2    | Consideration for PCB layout         | 60 |

| 7      | Other information                    | 64 |

| 7.1    | Design for a good EMI performance    | 64 |

| 7.2    | Parameter adjustment for ZVS         | 64 |

| 7.3    | Output capacitance                   | 65 |

| 7.4    | Resonant capacitor                   | 65 |

| 7.5    | Wide output voltage range design     | 65 |

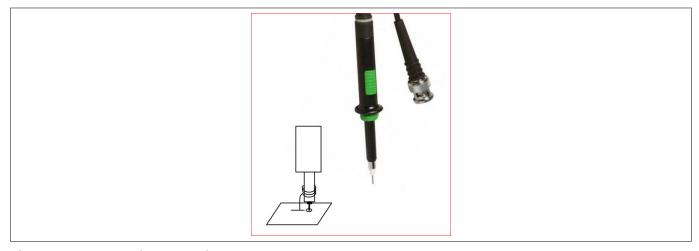

| 7.6    | Probing signal on the board          | 65 |

| 8      | Summary                              | 66 |

| 9      | References                           | 66 |

| 10     | Related links and support material   | 66 |

| 11     | Change history                       | 67 |

|        | Disclaimer                           | 68 |

#### 1 Introduction

#### Introduction 1

Hybrid-flyback (HFB) is the most promising topology for ultrahigh power density and cost effective switching mode power supplies (SMPS). In this topology, both the transformer and the resonant capacitor store energy intermediately during the energy transferring from the primary to the secondary side. This reduces the necessary transformer size in comparison to the flyback converter and its variants. Additionally, due to the resonant characteristics, this topology operates very well with a wide input range while the switching frequency is limited within a relatively small range, which is beneficial for the EMI filter design.

XDPS2201 is a novel controller IC for this HFB converter. The key features and advantages of the IC are:

- 600 V depletion MOSFET integrated to support the VCC charge-up

- Integrated high-side (HS) and low-side (LS) MOSFET driver enabling a compact design

- Zero-voltage (ZV) switching without additional components for high efficiency, low system cost and ultrahigh power density design

- Multiple operation modes for optimized efficiency over the line, load current and output voltage ranges

- Complete configurable parameter set, and easy configuration via MFIO pin for easy design and platform approach

- High system robustness through comprehensive protection features

- Failure code communicated at the MFIO pin for ease of use

This document provides information about the control IC XDPS2201, and the HFB design describes the following topics:

- HFB topology and operating principle (*Chapter 2*)

- HFB control IC XDPS2201 (Chapter 3)

- HFB power stage design (Chapter 4)

- Parametrization (Chapter 5)

- PCB design tips (Chapter 6)

- Other information (Chapter 7)

- Summary (Chapter 8)

- References (Chapter 9)

2 HFB topology and operating principle

# 2 HFB topology and operating principle

## 2.1 Hybrid-flyback topology

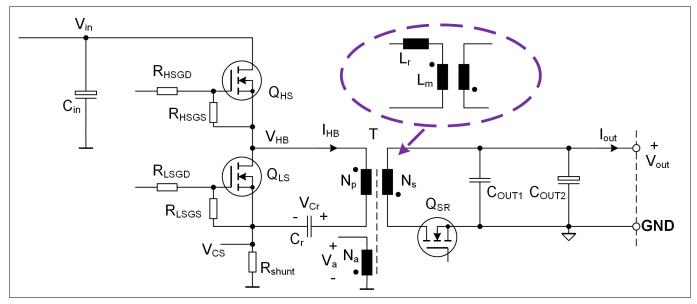

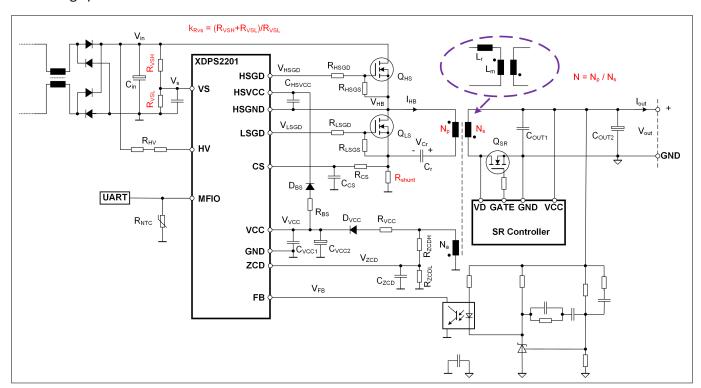

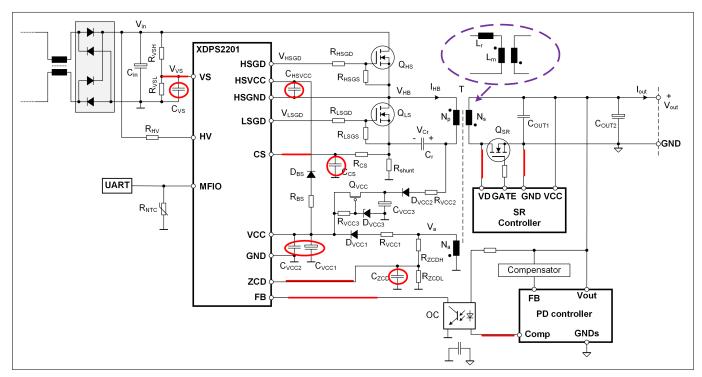

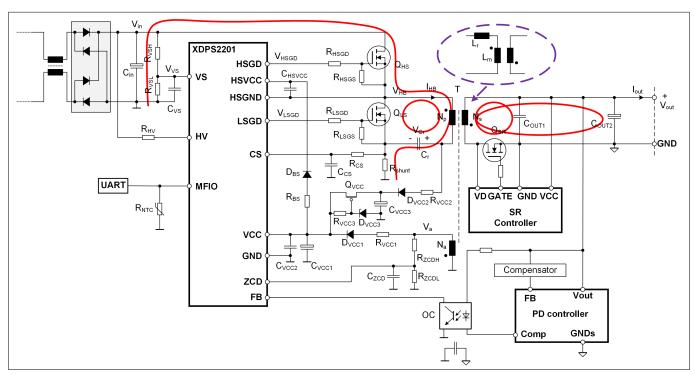

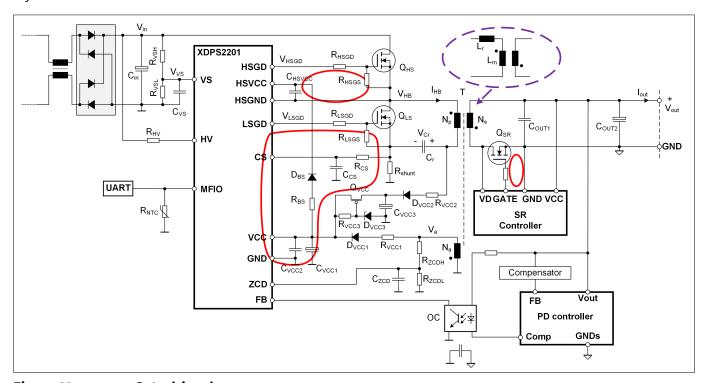

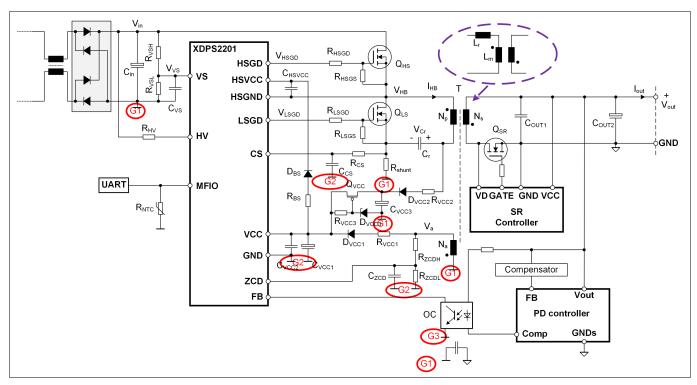

Figure 1 shows the HFB converter main stage.

Figure 1 HFB main stage

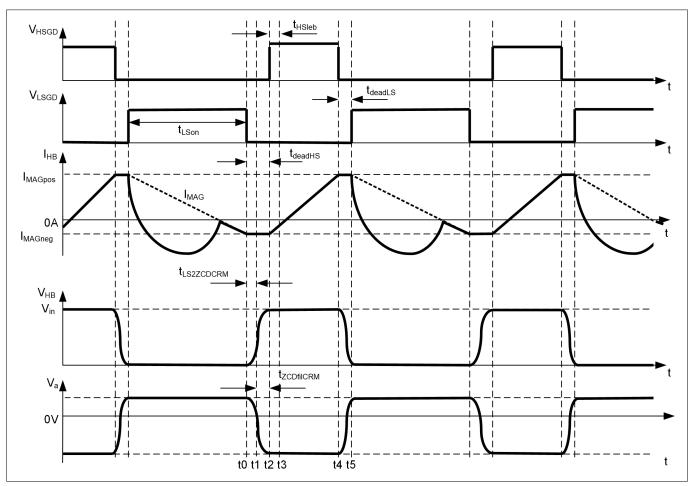

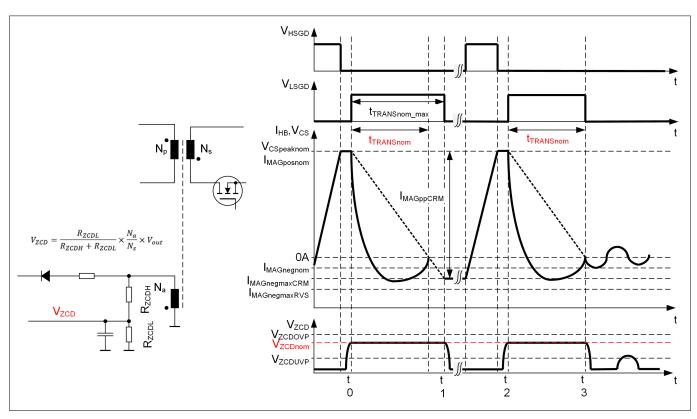

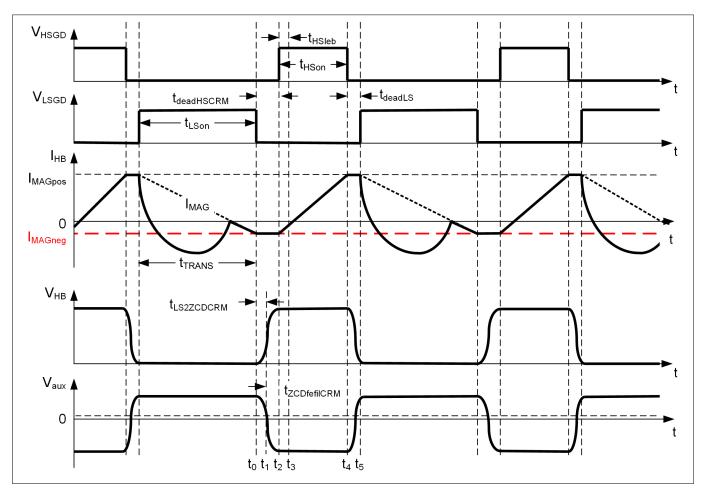

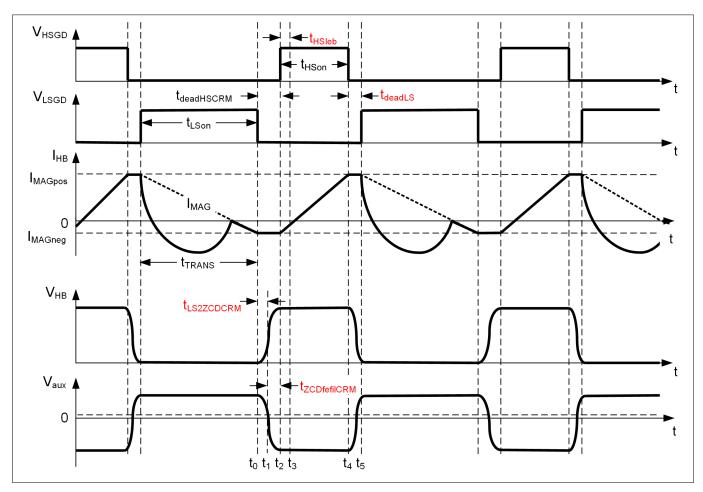

The HFB converter consists of a HS switch ( $Q_{HS}$ ) and a LS switch ( $Q_{LS}$ ), the energy transfer elements out of a transformer T and a resonant capacitor  $C_r$ , and the output stage out of a synchronous rectifier (SR) MOSFET and output capacitors. In **Figure 2**, the typical operating waveforms are shown in the continuous resonant mode (CRM) at the nominal output power  $P_{\text{outnom}}$ , defined as:

$$P_{\rm outnom} = V_{\rm outnom} \cdot I_{\rm outnom}$$

## **Equation 1**

with

- V<sub>outnom</sub> as the maximum nominal output voltage, and

- I<sub>outnom</sub> the maximum nominal output current

In the CRM operation, the primary inductance is magnetized during the on-time of the switch  $Q_{\rm LS}$  ( $t_{\rm LSon}$ ). Per a proper time control, HFB is running under the ZV turn-on for both MOSFETs. The ZV turn-on of the LS MOSFET is always achieved, since the current  $i_{\rm HB}$  at that moment is adequate to force the body diode of the LS MOSFET to conduct before the LS MOSFET is turned on. The controller IC controls the LS gate pulse width to generate sufficient negative current to bring the voltage  $V_{\rm HB}$  back to the voltage  $V_{\rm in}$  before the HS MOSFET is turned on. In this way, the ZV turn-on is ensured for both MOSFETs, which ensures high system efficiency without additional components. Therefore, this HFB topology is very promising for cost effective and ultrahigh power density converters, such as USB-PD fast charger. A typical application circuit for this application is illustrated in *Figure 3*.

## 2 HFB topology and operating principle

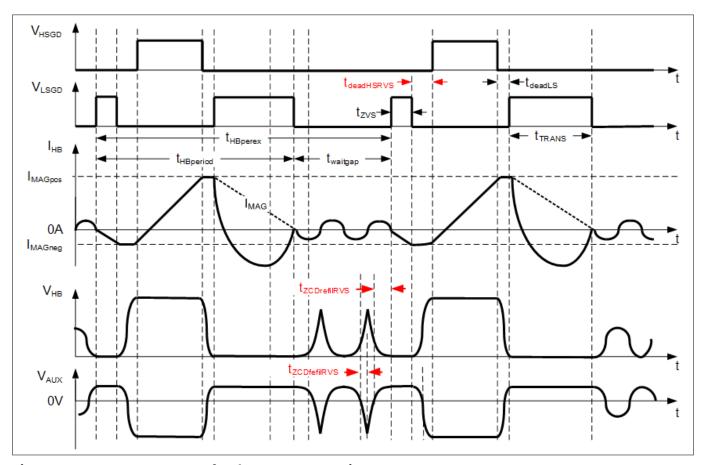

Figure 2 Typical waveforms in the CRM operation

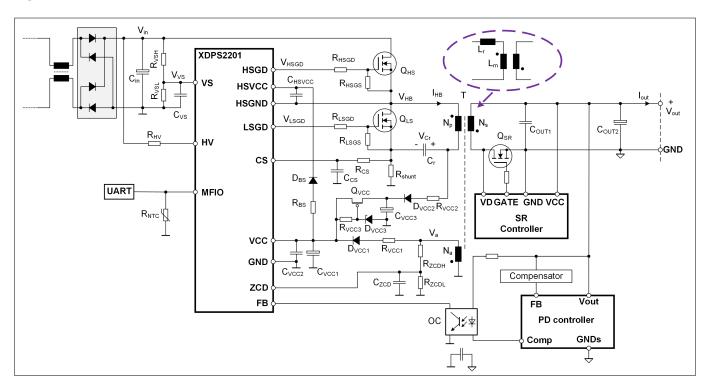

Figure 3 HFB in the USB-PD application

#### 2 HFB topology and operating principle

In this application, the PD controller senses the output voltage and sends the feedback signal at the Comp pin. Through the opto-coupler, the signal  $V_{\rm FB}$  is generated at the FB pin of the controller XDPS2201, which is utilized to regulate the output voltage. Since the output is of wide range for the USB-PD application, the controller XDPS2201 cannot be powered only via the auxiliary winding  $N_a$  as in a convention flyback with only one output voltage level. A linear regulator is also required to generate the VCC supply voltage from the resonant capacitor at low output voltage.

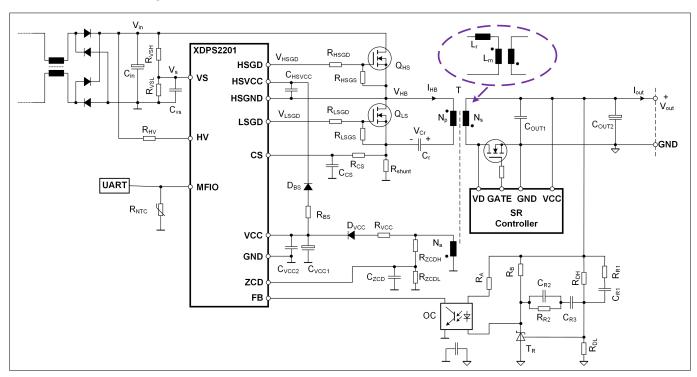

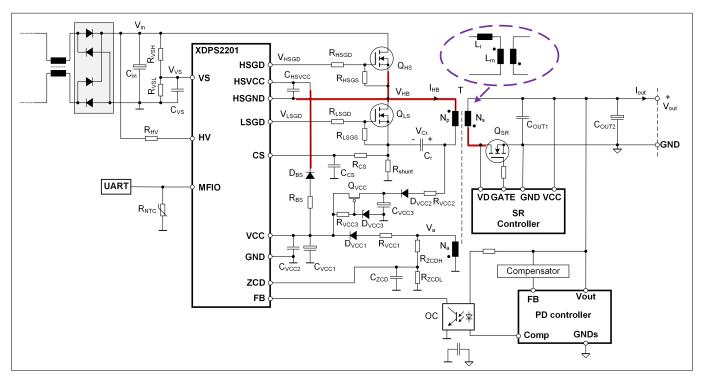

Naturally, HFB is not only suitable for this USB-PD application, but also promising for conventional SMPS due to its outstanding performance. A typical application circuit for SMPS is shown in *Figure 4*. Depending on the rated output power, a PFC stage may apply which is not depicted here.

Figure 4 HFB in the conventional SMPS application

#### **Operating principle** 2.2

The following assumptions are made to simplify the analysis:

- CRM operation at the nominal load

- Dead-time before the HS and LS switches turn-on  $t_{\rm deadHSCRM}$  and  $t_{\rm deadLS}$  (Figure 2) ignored

- Much lower ripple than the average value of the voltage across the resonant capacitor

- Transformer magnetizing inductance  $L_{\rm m}$  much higher than the leakage inductance  $L_{\rm r}$

- On-time of the HS switch  $t_{HSon}$  much shorter than the resonant period  $T_{r2}$  based on the primary magnetizing inductance  $L_p$  and the resonant capacitance  $C_r$  (Figure 5)

- Conduction voltage drop of the SR MOSFET ignored

- All losses ignored

The operating principle of HFB, along with these assumptions, is discussed as follows:

- Voltage transfer function (Chapter 2.2.1)

- Current transfer function (Chapter 2.2.2)

- Two resonant periods (Chapter 2.2.3)

## 2 HFB topology and operating principle

## 2.2.1 Voltage transfer function

As shown in the typical application waveforms (*Figure 2*), the magnetizing inductance is regulated by the voltage-second balance law during the steady-state operation, which gives:

$$(V_{\text{in}} - V_{\text{cr}}) \cdot D = N \cdot V_{\text{out}} \cdot (1 - D)$$

#### **Equation 2**

with

- $V_{\rm in}$  as the HB input voltage across the input capacitor  $C_{\rm in}$

- $V_{\rm cr}$  the average voltage across the resonant capacitor  $C_{\rm r}$

- D the HS MOSFET  $Q_{HS}$  on-time duty ratio  $\frac{t_{HSon}}{T}$

- N the transformer turns ratio  $\frac{N_p}{N_s}$ , and

- V<sub>out</sub> the output voltage

In the steady-state operation, the average voltage across the resonant capacitor in HFB is described as:

$$V_{\rm cr} = N \cdot V_{\rm out}$$

## **Equation 3**

From these equations, the voltage transfer function  $k_v$  is given by:

$$k_{\rm v} = \frac{V_{\rm out}}{V_{\rm in}} = \frac{D}{N}$$

#### **Equation 4**

This indicates the output voltage is controlled by the on-time duty ratio of the HS switch D.

## 2.2.2 Current transfer function

During the steady-state operation in CRM, the following equations are valid:

$$T = t_{\rm HSon} + t_{\rm LSon}$$

#### **Equation 5**

$$t_{\rm LSon} = \frac{\left(I_{\rm MAGpos} - I_{\rm MAGneg}\right) \cdot L_{\rm p}}{N \cdot V_{\rm out}}$$

#### **Equation 6**

$$P_{\mathrm{in}} = V_{\mathrm{in}} \cdot \frac{1}{2} \cdot \left( I_{\mathrm{MAGpos}} + I_{\mathrm{MAGneg}} \right) \cdot D$$

#### **Equation 7**

$$P_{\text{out}} = V_{\text{out}} \cdot I_{\text{out}}$$

## **Equation 8**

## 2 HFB topology and operating principle

From these equations, the output current can be expressed as:

$$I_{\text{out}} = \frac{N}{2} \cdot \left( I_{\text{MAGpos}} + I_{\text{MAGneg}} \right)$$

#### **Equation 9**

This equation shows the output current  $I_{out}$  is purely dependent on the positive and negative peak currents in the primary magnetizing inductor.

Based on the voltage and current transfer functions, the output voltage can be regulated by peak current control, where the feedback signal  $V_{\rm FB}$  sets the peak of the positive current  $I_{\rm MAGpos}$ . A proper LS gate pulse controls the amplitude of the negative current for the ZV switching of the HS switch.

#### 2.2.3 Two resonant periods

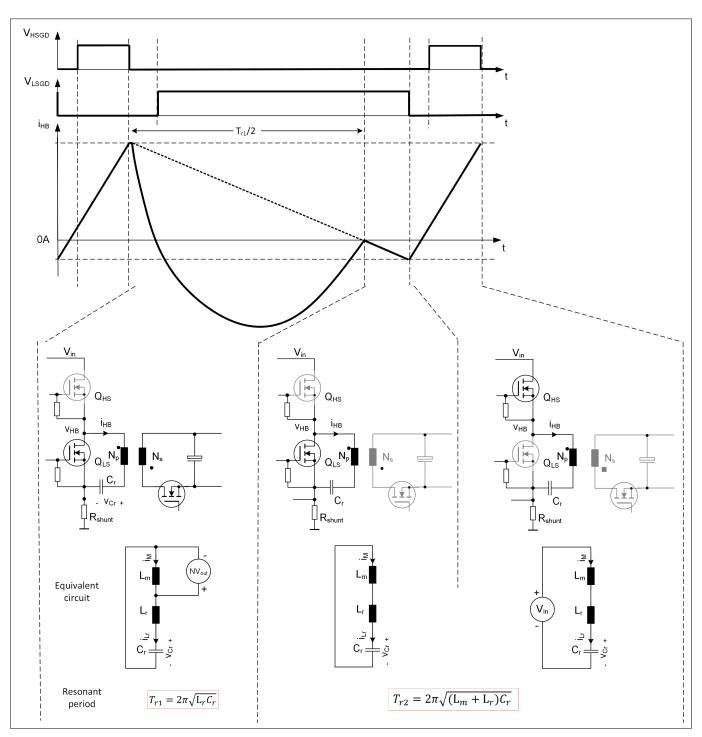

The detailed operation intervals of HFB in CRM is illustrated in the datasheet [2], while the equivalent circuit at different switching time phases and the related resonant periods are illustrated in Figure 5.

Once the LS switch is turned on, a resonant circuit is built out of the transformer leakage inductance  $L_r$  and the resonant capacitor C<sub>r</sub>, while the entire secondary side circuitry is acting as a voltage source in parallel to the magnetizing inductance since the SR MOSFET diode is forwarded biased. The energy stored in the magnetizing inductance  $L_{\rm m}$  and the capacitor  $C_{\rm r}$  charges the secondary side capacitors. This energy transfer lasts until the time reaches half of the period  $T_{r1}$ , which is mainly defined by the resonant inductance  $L_r$  and the capacitance  $C_{r}$ :

$$T_{\rm r1} = 2\pi \sqrt{L_{\rm r} \cdot C_{\rm r}}$$

#### **Equation 10**

Up the time  $\frac{T_{r1}}{2}$ , the secondary side rectifier is reverse biased and blocks, and the primary side circuit begins to resonant including the main magnetizing inductance  $L_{\rm m}$ . The resonant period  $T_{\rm r2}$  is defined by:

$$T_{\rm r2} = 2\pi\sqrt{(L_{\rm r} + L_{\rm m}) \cdot C_{\rm r}} = 2\pi\sqrt{L_{\rm p} \cdot C_{\rm r}}$$

#### **Equation 11**

This equation is valid until the switch Q<sub>HS</sub> is turned off. For the system design, these two different resonant periods have to be taken into account, which is explained in **Chapter 4**.

## 2 HFB topology and operating principle

Figure 5 Equivalent circuit and resonant period at different intervals

#### 3 HFB control IC XDPS2201

#### 3 **HFB control IC XDPS2201**

The control IC XDPS2201 is a digital control IC for HFB. The basic operating principle is explained in the following sub-chapters:

- Pin configuration (Chapter 3.1)

- Peak current control and zero-voltage turn-on (Chapter 3.2)

- Output regulation and operation modes (Chapter 3.3)

- Frequency jitter (Chapter 3.4)

- Protection (Chapter 3.5)

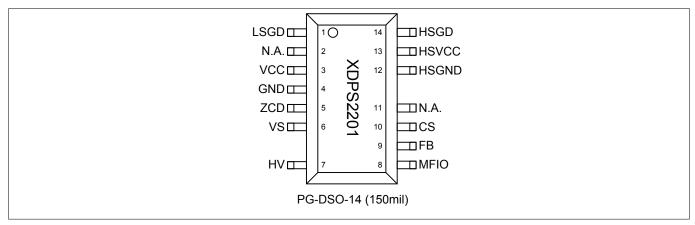

#### **Pin configuration** 3.1

The pin configuration is shown in *Figure 6* and *Table 1*. The pin functions are described in the sequel.

Figure 6 Pin configuration

Table 1 Pin definitions and functions

| Symbol                          | Pin                    | Туре                    | Function                                                                                                                                                                                                                                                             |  |

|---------------------------------|------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LSGD 1 O Low-side gate dr       |                        | 0                       | Low-side gate driver                                                                                                                                                                                                                                                 |  |

|                                 |                        |                         | Low-side gate driver of half-bridge driver stage                                                                                                                                                                                                                     |  |

| N.A.                            | N.A. 2 — Not available |                         | Not available                                                                                                                                                                                                                                                        |  |

|                                 |                        |                         | This pin is internally connected but not used, and should be connected to GND                                                                                                                                                                                        |  |

| VCC                             | 3                      | 1                       | Positive voltage supply                                                                                                                                                                                                                                              |  |

|                                 |                        |                         | IC power supply                                                                                                                                                                                                                                                      |  |

| GND 4 O Ground                  |                        | 0                       | Ground                                                                                                                                                                                                                                                               |  |

|                                 |                        |                         | Combined power and signal ground                                                                                                                                                                                                                                     |  |

| ZCD 5 I Zero-crossing detection |                        | Zero-crossing detection |                                                                                                                                                                                                                                                                      |  |

|                                 |                        |                         | ZCD pin provides zero-crossing detection after the low-side gate driver is turned off, during pause phase in skip cycle and burst mode. Furthermore, the reflected output voltage at auxiliary winding can be measured during the low-side gate driver turn-on phase |  |

| VS                              | 6                      | I                       | Voltage sensing                                                                                                                                                                                                                                                      |  |

|                                 |                        |                         | Low leakage input voltage sensing pin for controlling the negative magnetization and protections. VS pin is connected to a resistor divider for measuring the bulk voltage                                                                                           |  |

#### 3 HFB control IC XDPS2201

Table 1 Pin definitions and functions (continued)

| Symbol                      | Pin | Туре             | Function                                                                                                                                                  |

|-----------------------------|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| HV                          | 7   | I                | High-voltage input                                                                                                                                        |

|                             |     |                  | HV pin is connected to the AC line via external resistors and 2 diodes. An internally connected 600 V HV start-up cell is used for the initial VCC charge |

| MFIO 8 IO Multi-            |     | Ю                | Multi-functional input-output                                                                                                                             |

|                             |     |                  | UART communication for parameter configuration and failure mode reporting is provided by this pin. In addition, a connected NTC can be measured           |

| FB 9 I Feedback             |     | I                | Feedback                                                                                                                                                  |

|                             |     |                  | Input pin receiving the feedback control signal from the optocoupler                                                                                      |

| CS                          | 10  | 1                | Current sensing                                                                                                                                           |

|                             |     |                  | Input pin for current sensing during the high-side gate driver turn-on phase                                                                              |

| N.A.                        | 11  | _                | Not available                                                                                                                                             |

|                             |     |                  | This pin is internally connected but not used, and should be connected to GND                                                                             |

| HSGND 12 O High-side ground |     | High-side ground |                                                                                                                                                           |

|                             |     |                  | Ground reference node for floating driver domain                                                                                                          |

| HSVCC                       | 13  | 1                | High-side power supply                                                                                                                                    |

|                             |     |                  | Power supply input for floating driver domain                                                                                                             |

| HSGD                        | 14  | 0                | High-side gate driver                                                                                                                                     |

|                             |     |                  | Floating high-side gate driver of half-bridge driver stage                                                                                                |

# 3.2 Peak current control and zero-voltage turn-on

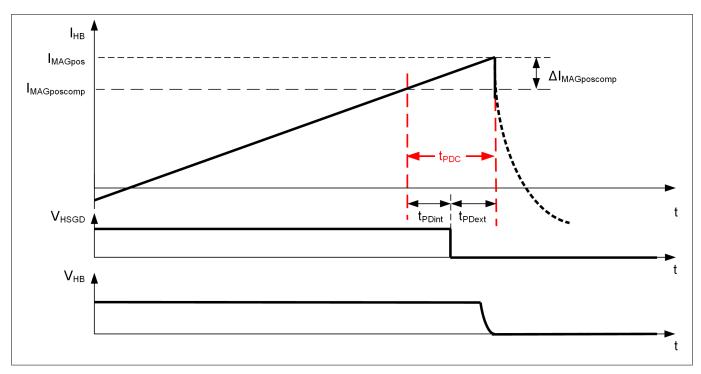

In the controller XDPS2201, the peak current control is implemented for the primary inductor current, both positive and negative peaks. *Figure 7* shows the positive peak control scheme.

Figure 7 Positive peak current setting

The controller sets the target peak current  $I_{\text{MAGpos}}$  based on the feedback signal  $V_{\text{FB}}$ , bus voltage and output voltage level. The target voltage  $V_{\text{CSSET}}$  is then calculated and compared with the voltage  $V_{\text{CS}}$  at the CS pin. Once the voltage  $V_{\text{CS}}$  exceeds the target  $V_{\text{CSSET}}$ , the HS switch  $Q_{\text{HS}}$  is turned off. This defines the on-time of the HS switch  $Q_{\text{HS}}$  based on the feedback signal, input voltage and output voltage level for the output voltage regulation.

To ensure ZV turn-on of the HS switch, the negative current requires a certain amplitude. As from the main stage of HFB (*Figure 1*), the negative peak current during on-time of the LS switch cannot be sensed via the shunt

#### 3 HFB control IC XDPS2201

resistor. For the inductor negative peak current control, an adaptive control is implemented in the controller XDPS2201.

The on-time of the LS switch is calculated based on the parameter  $t_{\rm TRANS}$ , voltage  $V_{\rm in}$ , and time setting of  $t_{\rm LS2ZCDnom}$  and  $t_{\rm LS2ZCDmin}$ . After the LS switch is turned off, the LS gate on-time for the next switching cycle is adjusted based on the measured time  $t_{\rm LS2ZCDCRM}$ , to ensure the necessary negative current amplitude for ZV turn-on of the HS switch. The measured time  $t_{\rm LS2ZCDCRM}$  has information about the amplitude of the negative current: the higher the amplitude of the negative current, the shorter the measured time  $t_{\rm LS2ZCDCRM}$ . If the measured time  $t_{\rm LS2ZCDCRM}$  is longer than the internal target time, the magnitude of the negative peak current is smaller than its target. In this case, the controller will increase the on-time of the LS switch in the next cycle or vice versa. In this way, the amplitude of the negative current is controlled in a certain level to achieve ZV turn-on of the HS switch and for high efficiency of the power transferring as low as possible.

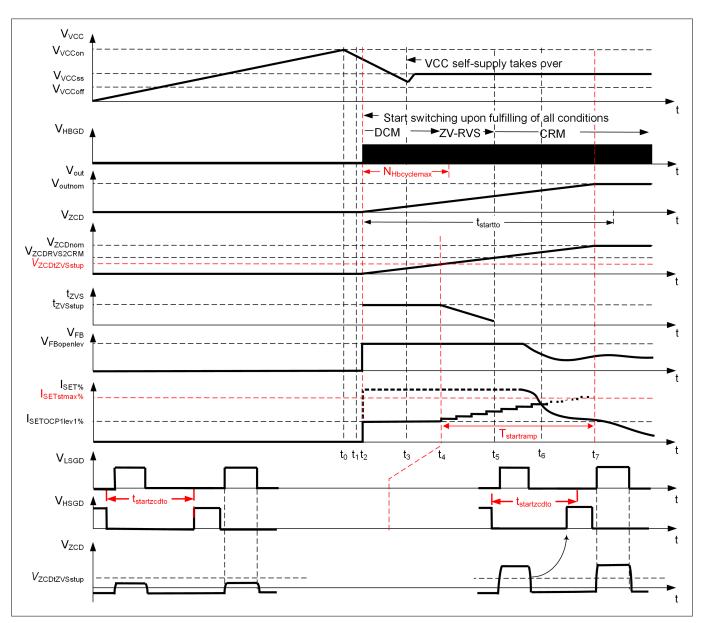

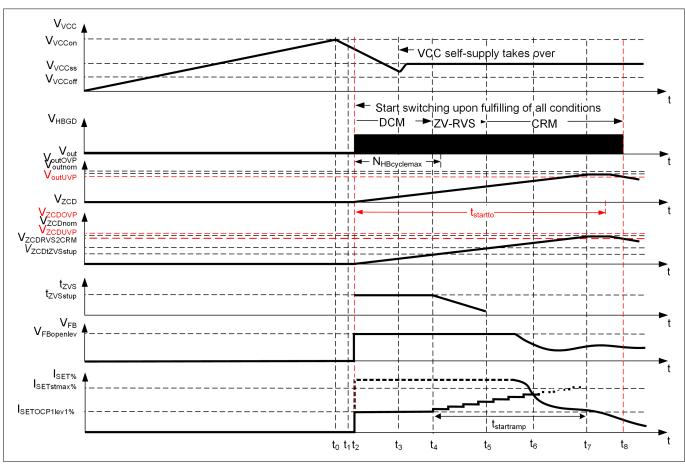

## 3.3 Output regulation and operation modes

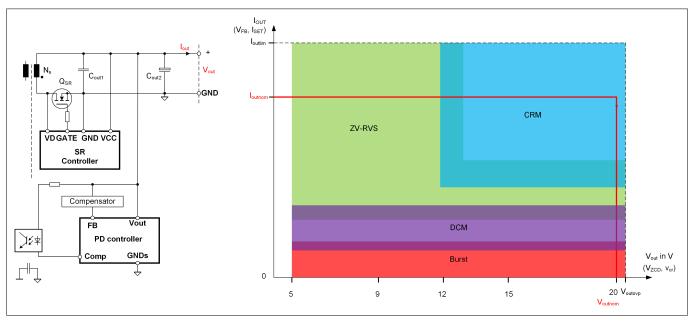

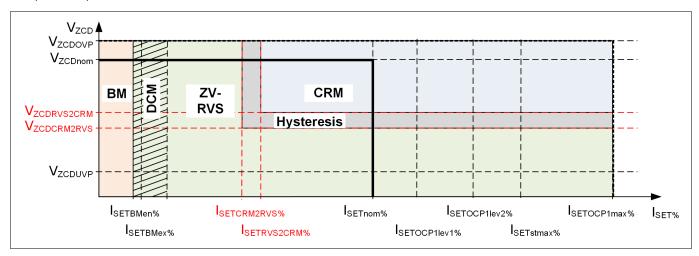

The control IC XDPS2201 employs several operation modes to ensure high system efficiency over the whole input and output ranges.

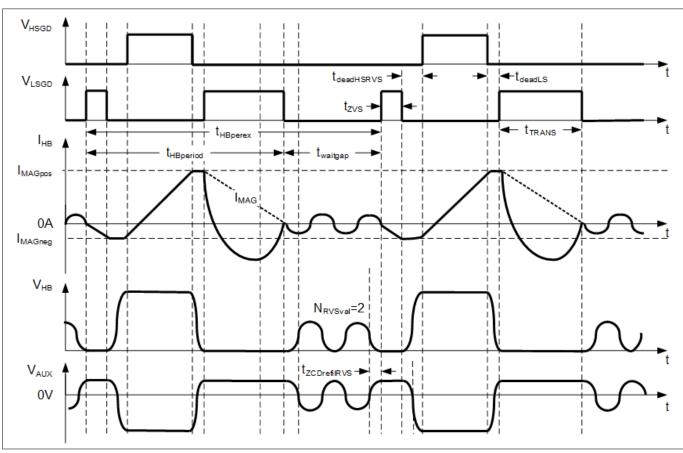

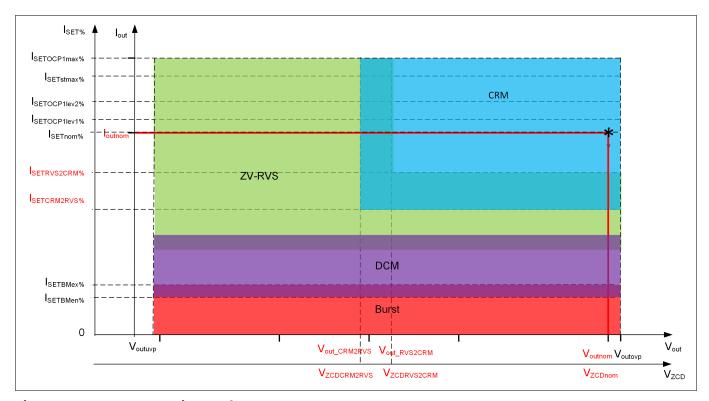

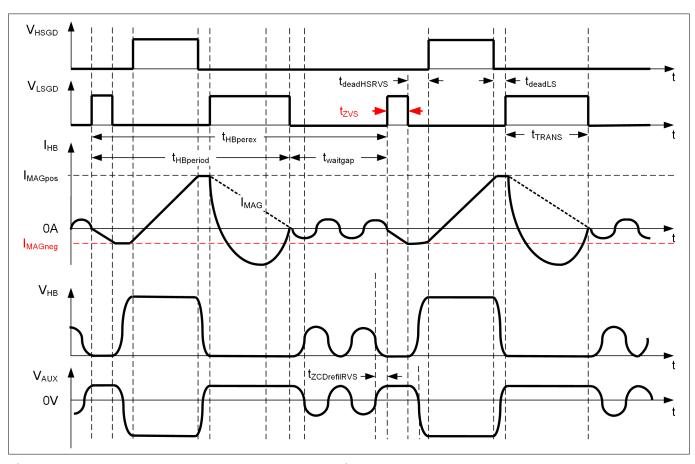

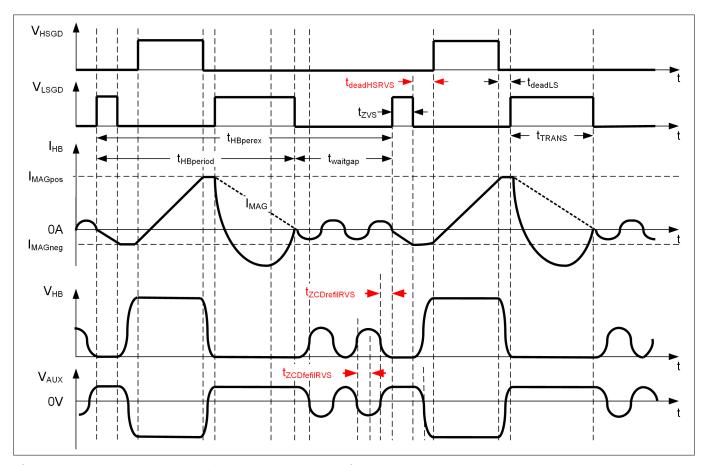

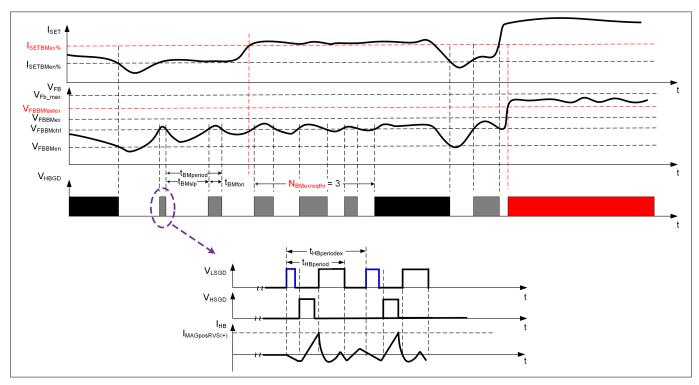

**Figure 2** shows the waveform in CRM at the nominal output condition. In a certain power range around the nominal output power, the controller just modifies the amplitude of the positive peak current for the output voltage regulation. The lower the load level, the smaller the amplitude of the positive current and the shorter the on-time of the HS switch, while the negative peak current is adjusted according to the HFB input voltage. At the same level of the voltage  $V_{\rm in}$  and therefore the same level of the negative peak current, the switching frequency at lighter load increases and the system efficiency decreases. To avoid this, the controller XDPS2201 implements the first discontinuous operation – zero-voltage resonant valley switching (ZV-RVS) – for the load in a certain range with the typical switching waveforms, as shown in **Figure 8**.

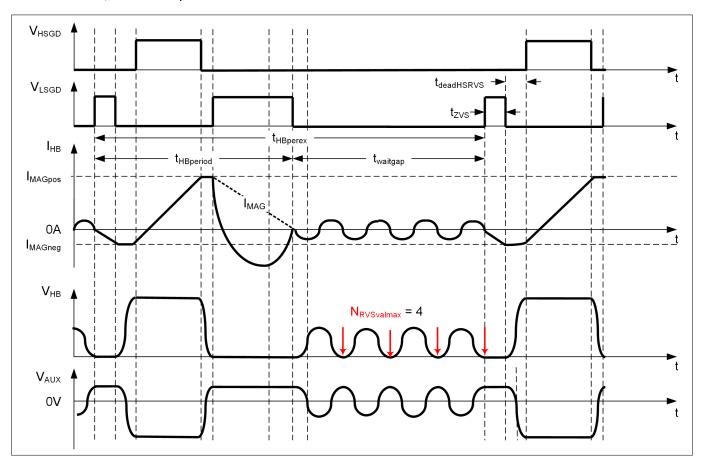

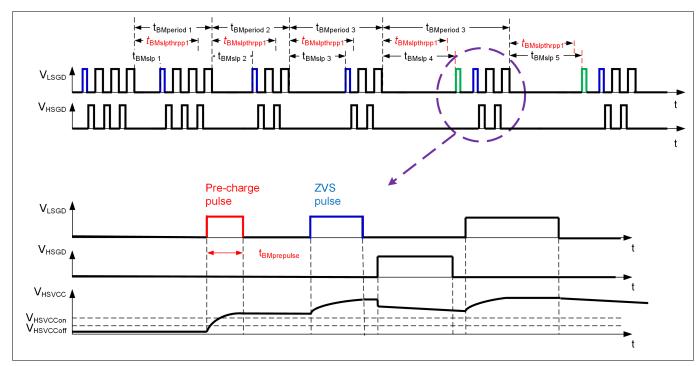

In this operation mode, a waiting time  $t_{\text{waitgap}}$  is added after the LS switch is turned off at  $t_{\text{TRANS}}$ , once the amplitude of the positive current reduces to below the value from  $I_{\text{SETCRM2RVS}}$  ( $I_{\text{setnom}} \cdot I_{\text{SETCRM2RVS\_perc}}$ ) (**Figure 9**). In this way, the effective switching period  $t_{\text{HBperex}}$  is increased and the system efficiency is improved. In the controller XDPS2201, the added time break  $t_{\text{waitgap}}$  depends on the load current. The lower the load current, the higher the number of ringing cycles  $N_{\text{RVSval}}$  and, therefore, the longer the waiting time  $t_{\text{waitgap}}$ .

To generate the required amplitude of the negative current for the ZV turn-on of the HS switch in the next switching cycle, the LS switch is turned on at a time of  $t_{\rm ZCDrefilRVS}$  after the rising edge of the ZCD signal, where the valleys  $N_{\rm RVSval}$  is counted after the LS gate turn-off. This LS gate pulse is called ZVS pulse, and has a pulse width of  $t_{\rm ZVS}$ . The SR MOSFET is forward biased during the time of  $t_{\rm ZVS}$  and conducts. This will cause the energy flows from the secondary side to the primary side of the converter. The backward energy transferring does not have much impact on the system efficiency since the energy is not consumed as power losses, but it helps to build up the required negative current in the magnetizing inductance while the resonant capacitor is charged up.

Note:

In the real application, the minimum time of  $t_{zvs}$  should at least be equal to or higher than the minimum on-time of the SR controller to avoid a conduction overlap of the HS switch and the SR MOSFET.

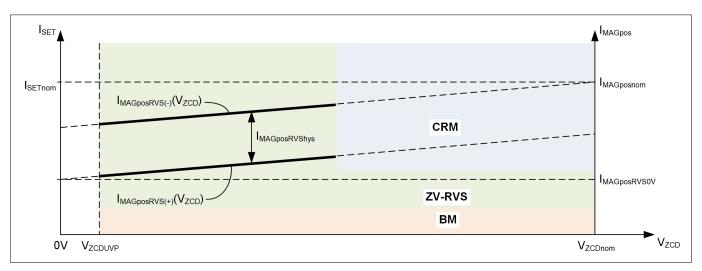

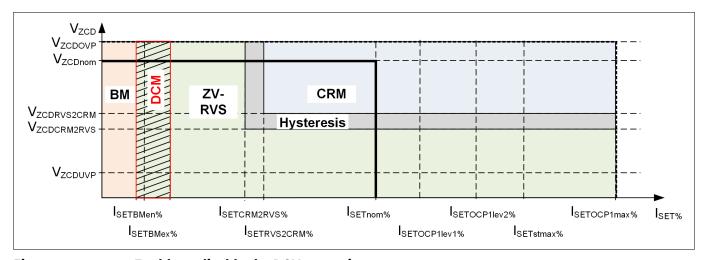

If the load current increases while the system is running in the ZV-RVS mode, the operation may revert back into CRM, depending on the load voltage and current level. This transition is controlled by the programmable parameters:  $I_{\text{SETCRM2RVS\_perc}}$ ,  $I_{\text{SETRVS2CRM\_perc}}$ ,  $I_{\text{SETRVS2CRM\_perc}}$ ,  $I_{\text{SETRVS2CRM\_perc}}$ , and  $I_{\text{Out\_RVS2CRM}}$ . Figure 9 shows an overview of the different operating modes. While the boundary between the CRM and ZV-RVS mode can be set by these parameters, the time  $I_{\text{Waitgap}}$  is controlled with a right number of ZC  $I_{\text{RVSVal}}$ , as shown in Figure 10.

## 3 HFB control IC XDPS2201

Figure 8 Discontinuous operation case 1 – ZV-RVS

Figure 9 Operating modes

#### 3 HFB control IC XDPS2201

Figure 10 ZV-RVS waiting time control

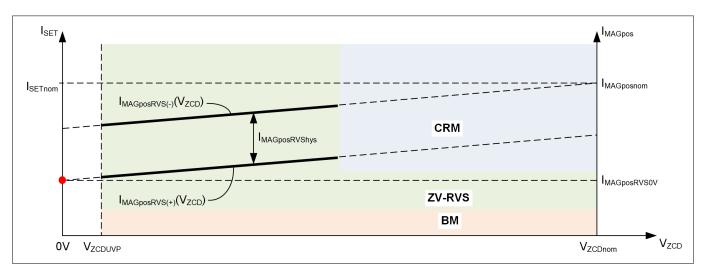

In the ZV-RVS mode, the break time  $t_{\text{waitgap}}$  is realized by counting the number of the ZC valley  $N_{\text{RVSval}}$  (*Figure 8*). If the set peak current is higher than the threshold  $I_{\text{MAGposRVS}(-)}$  at the set output voltage level, then the target number for the ZC valley  $N_{\text{RVSval}}$  will be reduced by 1. On the other hand, if the set peak current is lower than the threshold  $I_{\text{MAGposRVS}(+)}$  at the set output voltage level, then the target number for the ZC valley  $N_{\text{RVSval}}$  will be increased by 1. The hysteresis is determined by:

$$I_{\text{MAGposRVShys}} = \frac{1}{3} \cdot I_{\text{MAGposnom}}$$

## **Equation 12**

The straight line  $I_{\text{MAGposRVS(+)}}$  is determined by two end points (0,  $I_{\text{MAGposRVSOV}}$ ) and ( $V_{\text{ZCDnom}}$ ,  $I_{\text{MAGposnom}}$ ). The value  $I_{\text{MAGposRVSOV}}$  can be configured via the parameter  $I_{\text{MAGposRVSOV\_perc}}$  by  $I_{\text{MAGposnom}} \cdot I_{\text{MAGposRVSOV\_perc}}$ , while the value of  $I_{\text{MAGposnom}}$  is constant. Together with the hysteresis  $I_{\text{MAGposRVShys}}$ , the line  $I_{\text{MAGposRVS(-)}}$  is determined. In the real system, the ringing during the time  $t_{\text{waitgap}}$  is damped and the amplitude is decreasing with time. Therefore, the number of this ringing  $N_{\text{RVSval}}$  is limited to the configurable  $N_{\text{RVSvalmax}}$  for a reliable ZC detection. When the counted ZC number reaches the value of  $N_{\text{RVSvalmax}}$ , the system may operate in the discontinuous conduction mode (DCM), which is enabled or disabled by the parameter  $EN_{\text{DCM}}$ .

Directly after the system enters the DCM mode, the system operates with a slightly increased peak current of  $125\,\%\,\cdot I_{\mathrm{MAGposRVS(}\,+\,)}$  to have a hysteresis for the stable mode transition from ZV-RVS to the DCM operation. With a decreasing load current, the switching frequency sinks, but is limited by the set DCM minimum switching frequency  $F_{\mathrm{DCMmin}}$ . With a further decreasing load current, the peak current is reduced for the output voltage regulation.

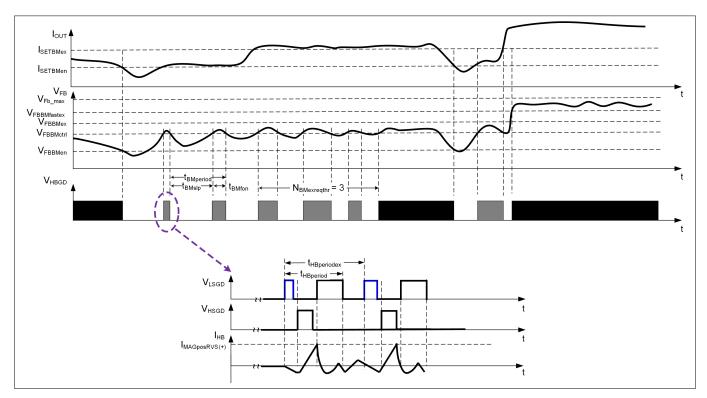

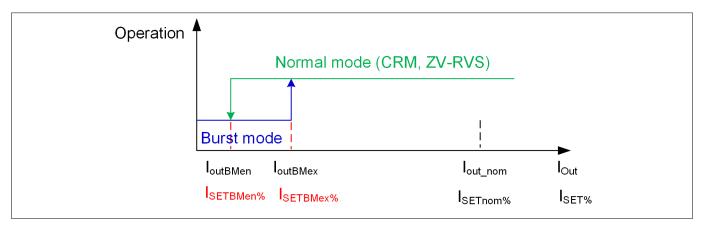

In case the output current sinks further and reaches the burst entry level  $I_{\text{outBMen}}$  configured per the parameter  $I_{\text{SETBMen\_perc}}$  by  $I_{\text{outnom}} \cdot I_{\text{SETBMen\_perc}}$ , the system enters another discontinuous operation – burst mode (BM) – for a further decreasing of the equivalent switching frequency and improvement of the system efficiency. The operation of the burst mode is illustrated in *Figure 11*.

#### 3 HFB control IC XDPS2201

Figure 11 Discontinuous operation case 2 – burst mode operation

Based on the parameter  $I_{\text{SETBMen\_perc}}$ , the respected voltage at the FB pin  $V_{\text{FBBMen}}$  for burst entry is derived. Once the voltage  $V_{\text{FB}}$  is lower than the value of  $V_{\text{FBBMen}}$ , the system enters burst mode operation, beginning with a burst break – burst frame off-time. Later, when the feedback voltage rises above the threshold  $V_{\text{FBBMctrl}}$ , the break time ends and the next burst – burst frame on-time – begins. During the burst frame on-time, the feedback voltage sinks. When the feedback voltage under-crosses the threshold  $V_{\text{FBBMctrl}}$ , the next burst break begins. During the burst operation, the peak current is set by the line  $I_{\text{MAGposRVS}(+)}$  according to the output voltage level (*Figure 10*).

Once the load power increases, the system may exit the BM operation. There are two types of burst exits: a fast and a slow burst exit. In case of a large load power jump-up, the feedback voltage rises above the set threshold  $V_{\rm FBBMfastex}$ , the system exits the burst mode operation, and begins to operate in CRM or in the ZV-RVS mode, controlled by  $EN_{\rm BMfastexCRM}$ . This is the fast burst exit scheme. In the other case, the output power increases slowly. During the BM operation, the output current is estimated based on the peak current set point  $I_{\rm MAGposRVS(+)}$ , the burst frame on-time  $t_{\rm BMfon}$  and the burst frame period  $t_{\rm BMperiod}$ . Once the estimated output current is above the threshold  $I_{\rm SETBMex}$  (configurable per the parameter  $I_{\rm SETBMenx\_perc}$  by  $I_{\rm outnom} \cdot I_{\rm SETBMex\_perc}$ ) for consecutive burst cycles defined by  $N_{\rm BMexreqthr}$ , the system exits the burst mode operation. This is the slow burst exit scheme. With this fast and slow burst mode exit controls, the controller ensures a well-regulated output voltage and reliable burst exit transition.

# 3.4 Frequency jitter

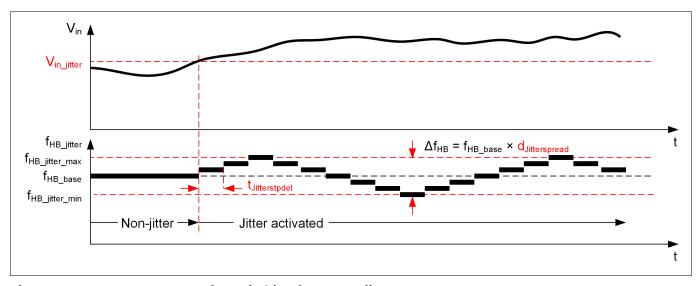

Switching frequency jitter spreads the switching frequency spectrum around its center point to achieve a lower noise level, which is beneficial for the EMI filter design.

Two conditions must be fulfilled for activating the jitter function: system in the CRM operation and up the configured instantaneous input voltage  $V_{\text{in\_jitter}}$ . The time duration of each frequency jitter step  $t_{\text{Jitterstpdel}}$  must be much longer than the settling time of the regulation loop.

#### 3 HFB control IC XDPS2201

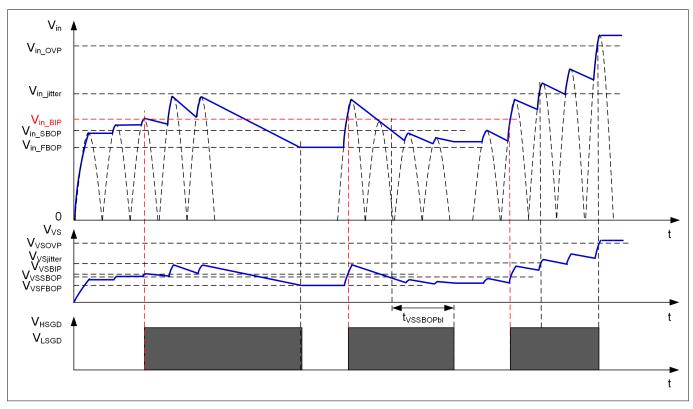

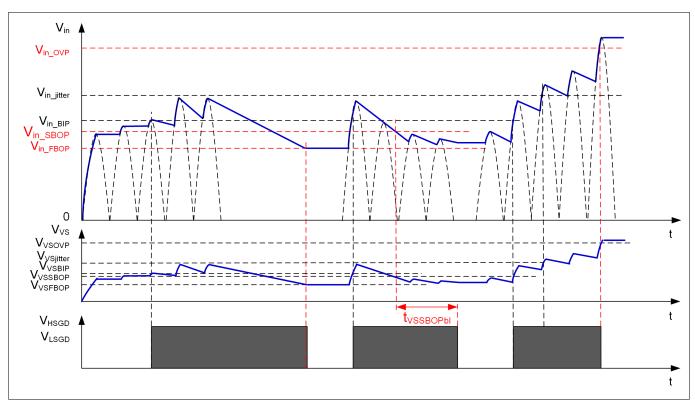

## 3.5 Protection

The IC pin MFIO is the interface for the communication between IC and computer for the parametrization. Additionally, the error code is sent out from this pin once a protection is triggered. The following table shows the protection features implemented in the control IC, failure code, reaction, evaluation criterion and the possible root cause.

Table 2 Failure code versus protection features

| Failure<br>code | Failure                  | Reaction              | Evaluation criteria                                                                                                                                                        | Possible root cause                                                                                                               |

|-----------------|--------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 1               | Slow<br>BROWN_OU<br>T1   | Immediate<br>restart  | V <sub>in</sub> average value over 25.6 ms<br>below V <sub>brownout_avg</sub> 1)                                                                                           | V <sub>in</sub> average voltage too low                                                                                           |

| 2               | Slow<br>BROWN_OU<br>T 2  | Immediate<br>restart  | V <sub>in</sub> peak did not reach V <sub>in_SBOP</sub> for longer than 44 ms                                                                                              | $V_{\rm in}$ value too low for more than 44 ms; too high capacitance at the VS pin                                                |

| 3               | START-<br>UP_TONMA<br>X  | Auto restart          | $t_{ m HSon} > t_{ m HSonmax}$ with $t_{ m HSonmax} = 2 \cdot t_{ m TRANSnom}$ for the first $\cdot rac{V_{ m Outnom} \cdot N}{V_{ m VS} \cdot k_{ m Rvs}}$ HS gate pulse | Shunt resistor shorted; HS gate shorted to HS GND; HS VCC too low; improper connection of the CS pin or any of the HS driver pins |

| 4               | START-<br>UP_TIMEOU<br>T | Auto restart          | Start-up failure due to timeout of no drop of the signal $V_{\rm FB}$ before the timeout threshold defined by $t_{\rm startto}$                                            | Output overload; output shorted; feedback circuit or pin open                                                                     |

| 5               | START-<br>UP_NO_ZCD      | Auto restart          | No ZCD detected during start-up time phase                                                                                                                                 | Output shorted; wrong dimensioning of the ZCD voltage or ZCD voltage divider; wrong polarity of the auxiliary winding             |

| 6               | VOUT_OVP                 | Latch/auto<br>restart | $V_{\rm ZCD} > V_{\rm ZCDOVP}$ , output overvoltage                                                                                                                        | Output overvoltage; open loop;<br>wrong ZCD divider ratio;<br>disturbance on the ZCD signal                                       |

| 7               | VOUT_UVP                 | Auto restart          | $V_{ m out} < V_{ m out\_UVP}$ during normal operation                                                                                                                     | Output overloaded; wrong ZCD divider ratio; disturbance on the ZCD signal                                                         |

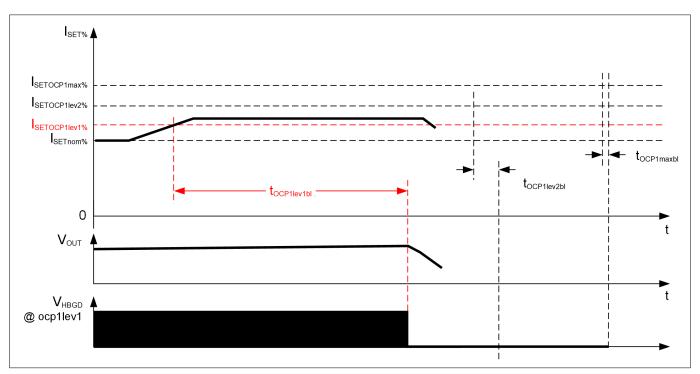

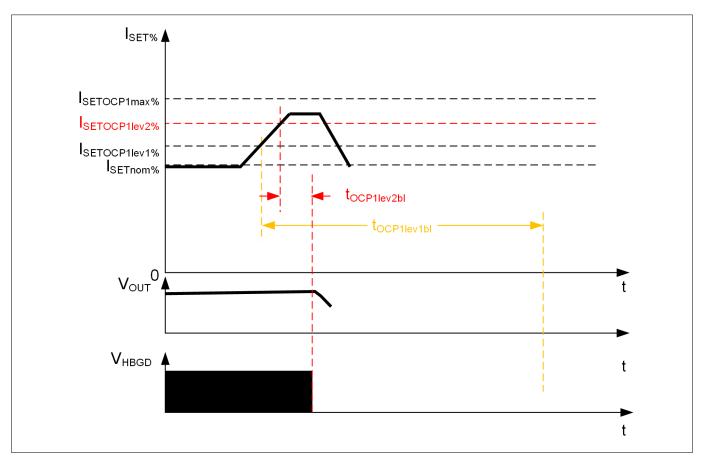

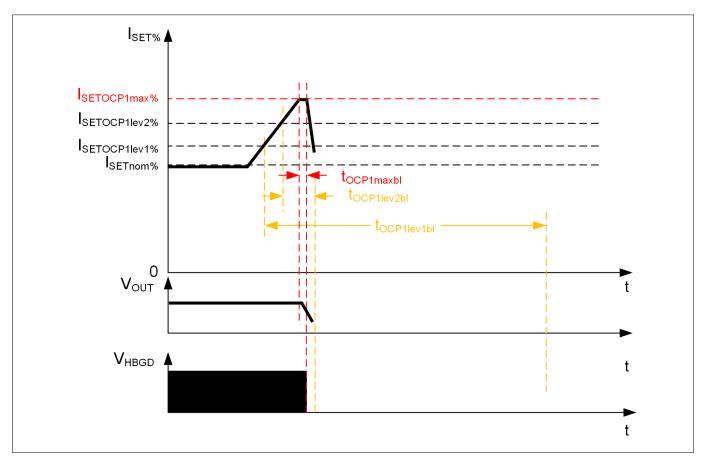

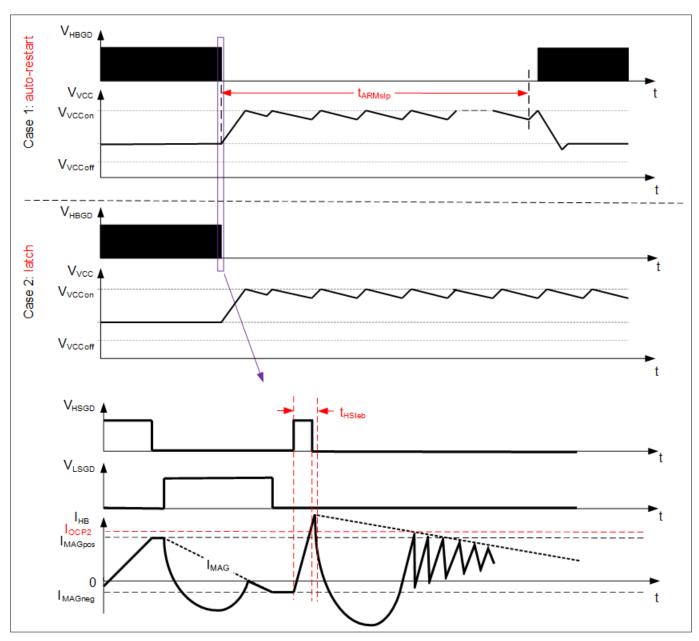

| 8               | OCP1max                  | Auto restart          | $I_{ m OUT} > I_{ m outnom} \cdot I_{ m SETOCP1max\_perc}$ for longer than the blanking time $t_{ m OCP1maxbl}$                                                            | Output shorted; heavy overload; disturbance on signal at the FB pin                                                               |

| 9               | OCP1lev1                 | Auto restart          | $I_{ m OUT} > I_{ m outnom} \cdot I_{ m SETOCP1lev1\_perc}$ for longer than the blanking time $t_{ m OCP1lev1bl}$                                                          | Overpower; wrong shunt resistor value                                                                                             |

| 10              | OCP1lev2                 | Auto restart          | $I_{ m OUT} > I_{ m outnom} \cdot I_{ m SETOCP1lev2\_perc}$ for longer than the blanking time $t_{ m OCP1lev2bl}$                                                          | Overpower; wrong shunt resistor value                                                                                             |

<sup>&</sup>lt;sup>1</sup> The threshold is set to zero in FW = this protection disabled.

#### 3 HFB control IC XDPS2201

Table 2 Failure code versus protection features (continued)

| 11 | Fast brown-<br>out<br>(VIN_UVP) | Immediate<br>restart                                  | $V_{\rm in} < V_{\rm in\_FBOP}$ during normal operation                                              | V <sub>in</sub> too low; bus capacitor too small                                                         |

|----|---------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 12 | VIN_OVP                         | Auto restart                                          | $V_{\rm in} > V_{\rm in\_OVP}$ during normal operation                                               | $V_{\rm in}$ too high; wrong divider ratio for $V_{\rm VS}$                                              |

| 13 | OCP2                            | Latch                                                 | $V_{\rm CS} > V_{\rm CSOCP2}$                                                                        | Damaged HS MOSFET; shorted transformer primary winding; charge current of the bootstrap circuit too high |

| 14 | START-<br>UP_VFB_LO<br>W        | Auto restart                                          | $V_{ m FB} < V_{ m FBBMctrl}$ before start-up                                                        | Output capacitor charged; wrong feedback signal                                                          |

| 15 | ZCD_ERROR at overload           | Auto restart                                          | Missing ZCD during normal operation                                                                  | Output shorted; overload; erroneous ZCD signal                                                           |

| 16 | ОТР                             | Auto restart<br>and latch, or<br>auto restart<br>only | $R_{ m NTC} < V_{ m MFIOOTPtrig}$                                                                    | V <sub>MFIO</sub> pulled down; over temperature                                                          |

| 17 | OTP_START-<br>UP                | Auto restart                                          | $R_{ m NTC} < V_{ m MFIOOTPrel}$ during start-up                                                     | V <sub>MFIO</sub> pulled down at start up; over temperature                                              |

| 18 | VIN_OO_RA<br>NGE                | Immediate restart                                     | $V_{\rm in} < V_{\rm in\_FBOP}$ or $V_{\rm in} < V_{\rm in\_SBOP}$ or $V_{\rm in} > V_{\rm in\_OVP}$ | $V_{\text{in}}$ either too high or too low; wrong $V_{\text{VS}}$ divider or settings                    |

| 19 | Watchdog<br>bite                | Auto restart or latch                                 | Reset timeout                                                                                        | CPU overload or run timing                                                                               |

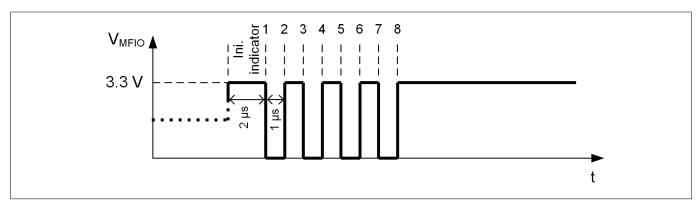

For example, *Figure 12* shows the signal at the MFIO when the output overcurrent protection OCP1max (*Figure 46*) is triggered. The failure code begins with an initial indicator pulse which is of 2 µs. The total number of all the falling and rising edges after the initial pulse gives the failure code number as shown in *Table 2*. For easy capture of the failure code, the oscilloscope trigger can be set to be *single trigger* with a pulse width above 1.5 µs at the level of 3 V.

Figure 12 Failure code at the OCP1max triggered

#### 4 HFB power stage design

# 4 HFB power stage design

This chapter focuses on the general design flow and design consideration of a HFB power converter including:

- Key initial design parameters (Chapter 4.1)

- Transformer key parameters and resonant capacitance (Chapter 4.2)

- Components connected to IC pins (Chapter 4.3)

- Output regulator (Chapter 4.4)

## 4.1 Key initial design parameters

Besides the previously mentioned parameters ( $V_{\text{outnom}}$ ,  $I_{\text{outnom}}$  and  $V_{\text{in\_OVP}}$ ), the following parameters are defined:

- The minimum operating input voltage  $V_{\text{in\_min}}$

- The blocking voltage of the secondary side rectifier diode or synchronous rectifier (SR) MOSFET, here the SR MOSFET  $V_{\rm DS-SR}$

- Voltage derating factor of the SR MOSFET k<sub>VDS SR</sub>

## 4.2 Transformer key parameters and resonant capacitance

The following topics are discussed here:

- Transformer key parameters (Chapter 4.2.1)

- Resonant capacitor (Chapter 4.2.2)

- Design constraints (*Chapter 4.2.3*)

## 4.2.1 Transformer key parameters

#### Determination of the transformer turns ratio N

The transformer turns ratio is related to the SR MOSFET blocking voltage and the switch  $Q_{HS}$  maximum on-time duty ratio selection. The explanation is provided as follows.

In general, the SR MOSFET drain-source voltage during on-time of the HS switch is:

$$V_{\mathrm{DS\_SR\_op}} = \frac{V_{\mathrm{in}} - V_{\mathrm{Cr}}}{N} + V_{\mathrm{out}}$$

#### **Equation 13**

In this equation, the value of the voltages  $V_{Cr}$  and  $V_{out}$  depends on the operating condition, such as:

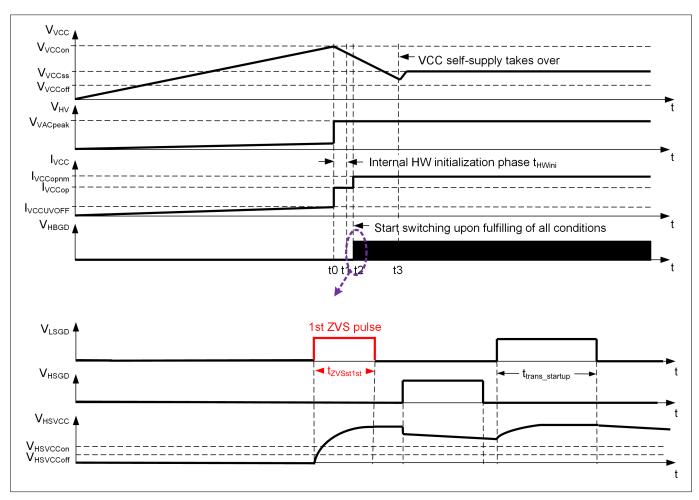

- The initial LS pulse at cold start-up

- During the normal operation

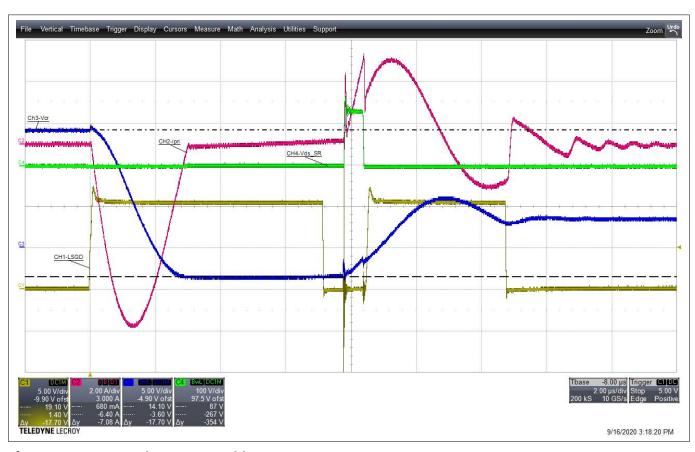

The HFB system operation begins with turn-on of the LS switch, to enable the charge-up of the capacitor  $C_{\rm HSVCC}$  of the HS MOSFET  $Q_{\rm HS}$  driver. At this first LS gate pulse, the resonant capacitor is discharged, which has been pre-charged by the HFB input voltage through the capacitive voltage divider built up by the drain-source capacitance of the switches  $Q_{\rm HS}$  and  $Q_{\rm LS}$ , and the resonant capacitor  $C_{\rm r}$ . This is illustrated in *Figure 13*.

## 4 HFB power stage design

Figure 13 Voltage  $V_{Cr}$  at cold start-up

Here, the blue curve shows the voltage across the resonant capacitor, the pink curve represents the resonant tank current, and the green curve shows the voltage across the drain-source of the SR MOSFET. It is seen that the voltage across the resonant capacitor is around -3.6 V at turn-on of the switch  $Q_{\rm HS}$ .

In the case of a normal operation, the voltage  $V_{ds\_SR\_op}$  can be simplified, taking **Equation 3** into consideration as:

$$V_{\mathrm{DS\_SR\_op}} = \frac{V_{\mathrm{IN}}}{N}$$

#### **Equation 14**

Considering both the cases, the overvoltage protection level  $V_{\text{in\_OVP}}$  defines the required minimum turns ratio of the transformer  $N_{\text{min}}$  by:

$$N_{\min} = \frac{V_{\text{in\_OVP}}}{V_{\text{DS\_SR}} \cdot k_{\text{VDS\_SR}}}$$

## **Equation 15**

For a conventional flyback converter, the value of  $k_{\text{VDS\_SR}}$  is typically around 80%. To determine the maximum of the turns ratio  $N_{\text{max}}$ , the value of the minimum operating bus voltage  $V_{\text{in\_min}}$  and the maximum duty ratio of the HS switch  $D_{\text{max}}$  must be considered. From the voltage-second balance, it is valid that:

$$N_{\max} = D_{\max} \cdot \frac{V_{\text{in\_min}}}{V_{\text{outnom}}}$$

#### **Equation 16**

#### 4 HFB power stage design

Here, the  $N_{\text{max}}$  depends on the values of  $D_{\text{max}}$  and  $V_{\text{in\_min}}$ . While the dependence of the maximum value  $D_{\text{max}}$  on the transformer inductance ratio  $\frac{L_r}{L_D}$  is discussed in **Chapter 4.2.3**, the determinative factors for the minimum operating voltage  $V_{\text{in min}}$  are discussed in the following text.

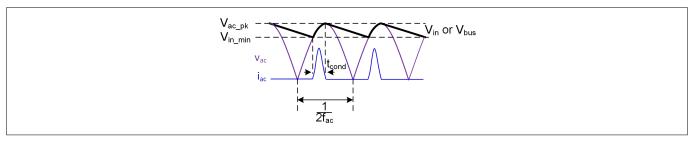

For a AC-DC converter without PFC stage, the input current conducts only during a portion of the AC half-cycle  $t_{cond}$ , as shown in *Figure 14*, and can be described by:

Figure 14 AC input current conduction period  $t_{cond}$

$$t_{\rm cond} = \frac{1}{2 \cdot f_{\rm ac}} \cdot \left( \frac{1}{2} - \frac{\sin^{-1} \left( \frac{V_{\rm in\_min}}{\sqrt{2} \cdot V_{\rm ac\_minRMS}} \right)}{\pi} \right)$$

#### **Equation 17**

The minimum voltage  $V_{\text{in\_min}}$  is related to many factors: the system maximum output power  $P_{\text{out\_max}}$ , the system efficiency  $\eta$ , the selected bus capacitance  $C_{in}$ , the minimum input voltage  $V_{ac\ minRMS}$  and the line frequency  $f_{ac}$ , which is described by the following equations.

The energy change in the capacitor  $C_{in}$  within half-cycle of the AC voltage is:

$$\Delta E_{\text{Cin}} = \frac{1}{2} \cdot C_{\text{in}} \cdot \left( 2 \cdot V_{\text{ac\_minRMS}}^2 - V_{\text{in\_min}}^2 \right)$$

#### **Equation 18**

The energy drown by the output:

$$\Delta \mathrm{E_{Cin}} = rac{P_{\mathrm{out\_max}}}{\eta} \cdot \left( rac{1}{2 \cdot f_{\mathrm{ac}}} - t_{\mathrm{cond}} \right)$$

#### **Equation 19**

Based on these equations, the capacitance  $C_{in}$  and the related  $V_{in\_min}$  can be expressed as:

$$C_{\text{in}} = \left(\frac{1}{2} + \frac{\sin^{-1}\left(\frac{V_{\text{in\_min}}}{\sqrt{2} \cdot V_{\text{ac\_minRMS}}}\right)}{\pi}\right) \cdot \frac{P_{\text{out\_cont}}}{\eta} \cdot \frac{1}{f_{\text{ac}}} \cdot \frac{1}{\left(2 \cdot V_{\text{ac\_minRMS}}^2 - V_{\text{in\_min}}^2\right)}$$

#### **Equation 20**

Here,  $P_{\text{out cont}}$  is the maximum continuous output power.

A further factor for the turns ratio determination is the transformer construction, such as the used core, bobbin and wires. Based on this information, the desired turns ratio of the transformer can be decided as N.

#### **Determination of the transformer inductance**

The HS switch on-time duty ratio D is 50% for operation at the nominal output condition and the input voltage  $V_{\text{in OpC1}}$  (OpC1 = operating condition case 1, to distinguish this condition from others) is:

## 4 HFB power stage design

$$V_{\text{in\_OpC1}} = 2 \cdot N \cdot V_{\text{outnom}}$$

#### **Equation 21**

Based on the current transfer function of HFB, the positive peak current will be:

$$I_{\text{MAGposnom}} = 2 \cdot \left(1 + I_{\text{MAGnegnom\_perc}}\right) \cdot \frac{I_{\text{outnom}}}{N}$$

## **Equation 22**

Here, the parameter  $I_{\text{MAGnegnom\_perc}}$  is the factor of the negative peak current  $I_{\text{MAGneg}}$  (*Figure 2*) over the current  $2 \cdot \frac{I_{\text{Outnom}}}{N}$  for the ZV switching of the switch  $Q_{\text{HS}}$  and set to 15% as the starting point.

The peak-peak current in the magnetizing inductance will be:

$$I_{\rm MAGpkpknom} = 2 \cdot \left(1 + 2 \cdot I_{\rm MAGnegnom\_perc}\right) \cdot \frac{I_{\rm outnom}}{N}$$

#### **Equation 23**

By giving a desired switching frequency  $f_{\text{des}}$  at the condition OpC1, the on-time of the LS switch  $t_{\text{LSon\_OpC1}}$  is calculated by:

$$t_{\text{LSon\_OpC1}} = \frac{1}{f_{\text{des}}} \cdot \frac{v_{\text{in\_OpC1}} - N \cdot v_{\text{outnom}}}{v_{\text{in\_OpC1}}}$$

#### **Equation 24**

Now, the required magnetizing inductance  $L_{\rm p}$  can be calculated from:

$$L_p = \frac{^{t} \text{LSon\_OpC1} \cdot N \cdot V_{\text{outnom}}}{^{I} \text{MAGpkpknom}}$$

#### **Equation 25**

Based on the given turns ratio and core shape, the magnetizing inductance  $L_p$  is decided. The factor of the leakage inductance  $k_{Lr}$  can be estimated based on the core shape and the winding construction. From this, the leakage inductance  $L_r$  can be calculated from:

$$L_r = k_{\rm Lr} \cdot L_p$$

#### **Equation 26**

Naturally, this leakage inductance can be measured if the transformer is available.

# 4.2.2 Resonant capacitor

#### Determination of the value of the resonant capacitor

The resonant capacitance  $C_r$  can be calculated by:

$$C_r = \left(\frac{t_{\rm LSon\_OpC1}}{\pi}\right)^2 \cdot \frac{1}{L_r}$$

#### **Equation 27**

#### 4 HFB power stage design

So far, the design process of the main circuit is described and the value of the main stage parameters are calculated.

## 4.2.3 Design constraints

For a cost effective design, the resonant capacitance should be as low as possible, and with as few capacitors as possible in case many capacitors are connected in parallel to achieve a certain value. But there are some design constraints for choosing the value of both  $C_r$  and  $L_r$  for a certain value of  $t_{TRANS}$ .

## Maximum duty ratio $D_{\text{max}}$ for the switch $Q_{\text{HS}}$

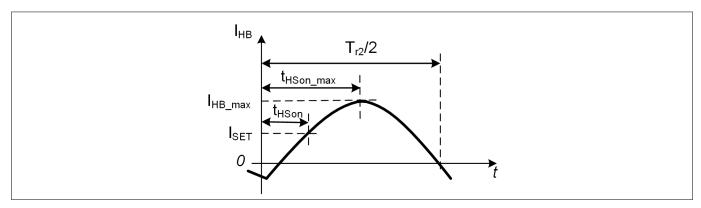

**Figure 5** shows the two resonant periods in the HFB converter. These resonant periods and the peak current control method set the limitation for the maximum on-time duty ratio for the HS switch  $D_{\text{max}}$ .

The HFB employs a peak current control. Usually, the on-time of the switch  $Q_{\rm HS}$  is a small portion of the resonant period  $T_{\rm r2}$  ( $t_{\rm HSon}$  in **Figure 15**), and the primary current arises almost linearly during this on-time  $t_{\rm HSon}$ . Considering the extreme case, the possible maximum on-time of the switch  $Q_{\rm HS}$   $t_{\rm HSon\_max}$  is ¼ of the resonant period  $T_{\rm r2}$  for the peak current control.

Figure 15 Possible resonant current during HS on-time and the maximal possible HS on-time

$$t_{\mathrm{HSon\_max}} = \frac{T_{\mathrm{r2}}}{4}$$

#### **Equation 28**

Ignoring the dead-time for both switches and the time for the negative current, the complete switching period is:

$$T_1 = t_{\text{HSon\_max}} + \frac{T_{\text{r1}}}{2} = \frac{T_{\text{r2}}}{4} + \frac{T_{\text{r1}}}{2}$$

#### **Equation 29**

Based on this equation, the relationship between the maximum duty ratio  $D_{\text{max}}$  and the transformer inductance ratio is:

$$D_{\text{max}} = \frac{\frac{T_{\text{r2}}}{4}}{\frac{T_{\text{r2}}}{4} + \frac{T_{\text{r1}}}{2}}$$

## **Equation 30**

Applying **Equation 10** and **Equation 11**, it is given that:

## 4 HFB power stage design

$$\frac{L_{\rm r}}{L_{\rm p}} = \frac{1}{4} \cdot \left(\frac{1}{D_{\rm max}} - 1\right)^2$$

#### **Equation 31**

From this equation, the maximum duty ratio  $D_{\text{max}}$  of the switch  $Q_{\text{HS}}$  is limited by the transformer inductance ratio  $\frac{L_{\text{T}}}{L_{\text{p}}}$ , which is defined by the transformer structure and technique. With 55%, 70% and 75% for the  $D_{\text{max}}$ , the ratio  $\frac{L_{\text{T}}}{L_{\text{p}}}$  are 16.7%, 4.59% and 2.78%, respectively.

Note: A high  $D_{\text{max}}$  means high RMS current at the secondary side, which has negative impact on the system efficiency curve.

## Selection of resonant capacitance C<sub>r</sub>

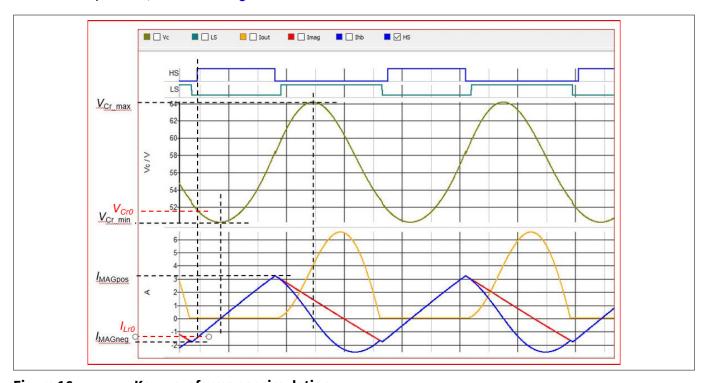

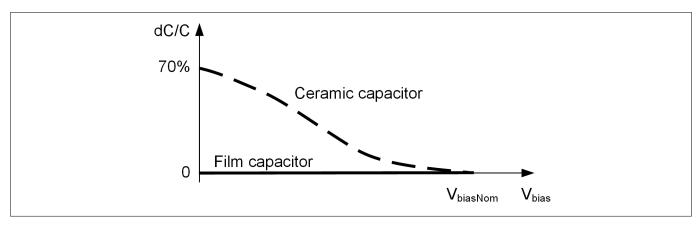

The USB-PD application has a wide range of output voltage. For this application, the resonant capacitor will be less dependent on the operating voltage, for example, film capacitor. For the cost effective and ultrahigh power density design, the value of the resonant capacitor must be as low as possible. However, there are some physical limitations for using a small resonant capacitance. This is discussed based on the simulated waveform for the CRM operation, as shown in *Figure 16*.

Figure 16 Key waveforms per simulation

During the on-time of the switch  $Q_{HS}$ , the current through the primary winding of the transformer (blue curve at the bottom) can be described as:

$$i_{\rm Lp}(t) = i_{\rm Lr0} \cdot \cos(w_{\rm r2}t) + \frac{V_{\rm in} - V_{\rm Cr0}}{Z_{\rm r2}} \cdot \sin(w_{\rm r2}t)$$

#### **Equation 32**

The voltage across the resonant capacitor (yellow curve) is:

#### 4 HFB power stage design

$$v_{\rm Cr}(t) = V_{\rm in} - (V_{\rm in} - V_{\rm Cr0}) \cdot \cos(w_{\rm r2}t) + Z_{\rm r2} \cdot i_{\rm Lro} \cdot \sin(w_{\rm r2}t)$$

#### **Equation 33**

with

$$w_{\rm r2} = \frac{2\pi}{T_{\rm r2}}$$

#### **Equation 34**

$$Z_{\rm r2} = \sqrt{\frac{L_{\rm p}}{C_{\rm r}}}$$

## **Equation 35**

From these equations, the maximum achievable primary side current is limited by the parameter  $Z_{r2}$ . Keeping  $L_p$  and  $V_{in}$  constant, the lower the capacitance  $C_r$ , the smaller the maximum peak current and the smaller the deliverable power. Therefore, for a certain maximal deliverable power, the capacitance  $C_r$  is limited. Furthermore, by using a small capacitance  $C_r$ , the voltage  $V_{in\_min}$  has to be increased for a certain peak current, which needs a higher value for the capacitor  $C_{in}$ . This may be critical due to the size limitation. Additionally, the voltage ripple across the resonant capacitor  $C_r$  is higher with a lower capacitance  $C_r$ . Accordingly, a higher voltage rating for the resonant capacitor  $C_r$  is required. This leads to a higher cost, and it is contrary to the original intention for lowering down the system cost with a smaller capacitance  $C_r$ .

For the system optimization, it is recommended to follow the provided design flow, and optimize the system based on that design and the measurement results.

# 4.3 Components connected to IC pins

The design of the components connected to the IC pins are described, considering the schematic shown in *Figure 3* as an example.

# 4.3.1 CS pin: shunt resistor

The maximum value for the peak current control through the CS pin ( $V_{CSOCP1max}$ ) is typically 0.437 V. The shunt value is given by:

$$R_{\text{shunt}} = \frac{V_{\text{CSOCP1max}} \cdot I_{\text{setnom\_perc}}}{\frac{2 \cdot I_{\text{outnom}}}{N}}$$

#### **Equation 36**

With  $I_{\text{setnom perc}}$  is set to 50% for good overpower capability.

For the shunt resistor on the board, the value must be close to this calculated value. Once the shunt resistor's value is determined, the worst case peak current can be calculated by:

$$I_{\mathrm{HB\_pk\_wc}} = \frac{v_{\mathrm{CSOCP2}}}{r_{\mathrm{shunt}}} + \frac{v_{\mathrm{in\_OVP}} - N \cdot v_{\mathrm{outnom}}}{L_{\mathrm{p}}} \cdot t_{\mathrm{CSOCP2pd}}$$

#### **Equation 37**

where, the second part of the equation derives from the propagation delay at the HS switch turn-off.

#### 4 HFB power stage design

## 4.3.2 VS pin: voltage divider

The VS pin is utilized for the HFB input voltage  $V_{\rm in}$  sensing, via the voltage divider from the resistor  $R_{\rm VSH}$  and  $R_{\rm VSI}$ . The following are the three main factors for the value selection of these resistors:

- The measurement range of the pin VS

- The pin leakage current

- The power losses in these resistors

Accordingly, the voltage divider resistors need to fulfill the following conditions:

$$k_{\text{R_VS}} = \frac{R_{\text{VSL}}}{R_{\text{VSL}} + R_{\text{VSH}}} \le \frac{V_{\text{VSmax}}}{V_{\text{in_max}}}$$

#### **Equation 38**

$$\frac{\textit{V}_{\text{in\_min}}}{\textit{R}_{\text{VSL}} + \textit{R}_{\text{VSH}}} \geq \textit{k}_{\text{I\_vs}} \cdot \textit{I}_{\text{VSlkmax}}$$

#### **Equation 39**

with

- V<sub>VSmax</sub> as the maximal measurable voltage at the VS pin

- V<sub>in max</sub> the maximum bus voltage

- I<sub>VSlkmax</sub> the VS pin maximum leakage current, and

- $K_{l\_vs}$  the ratio of the current through the voltage divider resistor and the pin leakage current, normally 10 Once these requirements are fulfilled, the resistor value must be as high as possible to minimize the power losses in these resistors.

For this pin, a capacitor with a small capacitance may be needed to filter the switching noise. It is normally up to several hundred pF, while a large capacitance results in a greater time delay, and therefore, a lower value of the signal  $V_{VS}$  at the AC valley where the fast brown-out protection may be triggered.

# 4.3.3 Auxiliary winding turns ratio and voltage divider

Conventionally, the auxiliary winding voltage  $V_a$  is used for supplying the control IC and for ZCD. In the controller XDPS2201, this voltage is additionally utilized for the output voltage level measurement. For a proper output voltage measurement, the values of both the turns ratio of the auxiliary winding  $N_a$  over the secondary side winding  $N_S(\frac{N_a}{N_S})$  and the resistive voltage divider ratio  $\frac{R_{\rm ZCDL}}{R_{\rm ZCDH}+R_{\rm ZCDL}}$  have to be properly designed.

For the turns ratio  $\frac{N_a}{N_s}$ , the main factors are the maximum output voltage level  $V_{\text{out\_OVP}}$  and the IC maximum operating voltage  $V_{\text{VCCmax}}$ . This turns ratio  $\frac{N_a}{N_s}$  must fulfill the following requirement, while the value should be as high as possible:

$$\frac{N_a}{N_S} \le \frac{V_{\text{VCCmax}}}{V_{\text{out\_OVP}}}$$

#### **Equation 40**

Once this turns ratio is decided, the voltage divider ratio can be calculated based on:

- The output overvoltage level setting V<sub>out\_OVP</sub>

- The pin leakage current

#### 4 HFB power stage design

This IC provides the output overvoltage protection by comparing the voltage at the ZCD pin during the on-time of the switch  $Q_{LS}$  with the fixed overvoltage protection threshold  $V_{ZCDOVP}$ . Based on this factor, the divider ratio of the ZCD pin resistors is defined by:

$$k_{\text{Rzcd}} = \frac{R_{\text{ZCDL}}}{R_{\text{ZCDL}} + R_{\text{ZCDH}}} = \frac{V_{\text{ZCDOVP}}}{V_{\text{out\_OVP}}} \cdot \frac{N_{\text{S}}}{N_{\text{a}}}$$

#### **Equation 41**

If this resistance ratio is met, the resistor value can be further calculated by taking the pin leakage current into account. A minimum current through the voltage divider resistors is necessary for minimizing the error of the measured output voltage, as the voltage divider resistors of the VS pin.

Note:

The ZCD pin leakage current given in the datasheet is the clamping current, which is much higher than the leakage current when the voltage at the ZCD pin is lower for ZC detection and output voltage measurement. Considering this leakage current as a reference for design, the factor of the current through the resistive divider over the leakage current does not need to be as high as usual, such as 10 for the VS pin voltage divider, but a factor of 2 or 3 is sufficient.

A capacitor  $C_{\text{ZCD}}$  may be needed for a ZCD signal with minimized switching noise. But its capacitance must be as low as possible to minimize the time delay of the ZCD signal in comparison with the voltage  $V_{\text{HB}}$ . The value of the resistive voltage divider should not be too high for the same reason as the low time delay of the ZCD signal, since the power losses in these resistors are usually not of a concern.

For the application with a wide output voltage range and ceramic capacitors used in the resonant tank, the resonant capacitance changes often according to the output voltage. If this dependence is not well compensated by the parameter  $t_{\text{TRANSRVSOV\_perc}}$  and the switch  $Q_{\text{LS}}$  on-time is shorter than  $\frac{T_{r1}}{2}$  at a lower output voltage, the ZCD signal has a glitch and the ZC detection is disturbed. This kind of disturbance can only be resolved by a proper value for the parameter  $t_{\text{TransRVSOV\_perc}}$ , but not with a larger  $C_{\text{ZCD}}$ .

## 4.3.4 HV pin: HV resistor

The HV pin has external resistors to limit power losses inside the IC during the VCC charge-up. The values of the resistor is limited mainly by the charge-up time of the capacitor  $C_{VCC}$  as:

$$R_{\rm HV} \le \frac{V_{\rm in\_min} \cdot t_{\rm VCC\_chargeup}}{C_{\rm VCC} \cdot V_{\rm VCCon}}$$

## **Equation 42**

where, the  $t_{VCC\_chargeup}$  is the target time to charge up the VCC capacitor to the IC VCC turn-on threshold  $V_{VCCon}$ . The following are the two options to connect the HV pin resistors for the VCC charge-up:

- Connected to the input capacitor C<sub>in</sub>, as shown in Figure 3

- Connected to the AC line and neutral of the supply terminals via the two high-voltage diodes, as shown in the datasheet

Both of these options have their own advantages and drawbacks. The first option does not need high-voltage diodes and, therefore, is more cost effective. But de-latch of the system takes longer time than that with the second option, since it is only possible after the capacitor  $C_{\rm in}$  is discharged to be below the  $V_{\rm VCC-UVLO}$  level. The real de-latch time depends on the value of  $C_{\rm in}$  and the instantaneous input voltage  $V_{\rm in}$ . The higher the value of  $C_{\rm in}$  and  $V_{\rm in}$ , the longer the de-latch time.

4 HFB power stage design

## 4.3.5 FB pin: filter capacitor

The FB pin has an internal pull-up resistor  $R_{\text{FBpu}}$ . In the application, this pin is connected to the feedback opto-coupler, while a small capacitor  $C_{\text{FB}}$  helps to filter the high-frequent switching noise for a stable operation. Typically, this capacitor has a value of around 100 pF.

## 4.3.6 FMIO pin: external thermal resistor

The following are the three functions that are integrated via the MFIO pin:

- UART communication for parametrization

- External temperature sensing with an external NTC resistor

- Failure code output for debugging purpose

For the UART communication, the necessary hardware and software are described in *Chapter 5.1* and *Chapter 5.2*.

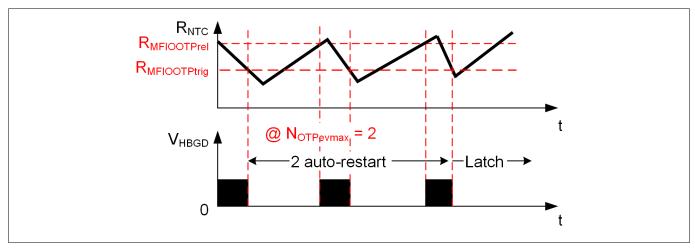

The MFIO pin has an internal resistor  $R_{\rm MFIOpu}$ . Along with an external NTC resistor, the control IC checks the NTC temperature by measuring the voltage level at the MFIO pin and indirectly the NTC resistance, and compares that with the over-temperature protection (OTP) trigger and release threshold  $R_{\rm MFIOOTPtrig}$  and  $R_{\rm MFIOOTPtrig}$  for the OTP protection.

Note:

In the case of open MFIO pin, the pin is pulled up by the internal resistor to the reference voltage V<sub>REF</sub>, which is well above the default equivalent OTP triggering voltage threshold, and the OTP is disabled.

Additionally, this pin is utilized for the failure code output if a protection is triggered. The details about the failure code is discussed in *Chapter 3.5*.

# 4.3.7 LSGD and HSGD: gate resistor and bootstrap circuit

The driver for a half-bridge configuration is integrated inside the IC. For a typical USB-PD application (*Figure 3*) and the other SMPS (*Figure 4*) below several hundred watts, the driver output can be connected to each MOSFET with just a resistor around 10  $\Omega$  for thermal consideration ( $R_{HSGD}$  and  $R_{LSGD}$ ), while the resistors around 10 k $\Omega$  between the MOSFET gate and source ( $R_{HSGS}$  and  $R_{LSGS}$ ) are needed as usual.

A bootstrap circuit is required for the HS driver. The resistor in the bootstrap circuit ( $R_{\rm BS}$ ) should not be too small. Otherwise, it may mis-trigger the protection OCP2 due to the resulted high charging current which flows through the shunt resistor. On the contrary, a very high resistor causes a non-effective charge-up of the HS driver capacitor. Normally, a 2 to 5.1  $\Omega$  resistance is used, and a capacitor around 100 nF for the HS gate driver ( $C_{\rm HSVCC}$ ) will satisfy the application.

# 4.3.8 VCC supply: VCC capacitor

The following are the three possible sources for the VCC supply:

- The start-up cell, mainly for VCC charge-up at the cold start-up and during protection

- The auxiliary winding during operation with a relatively high output voltage

- The resonant capacitor at a low output voltage

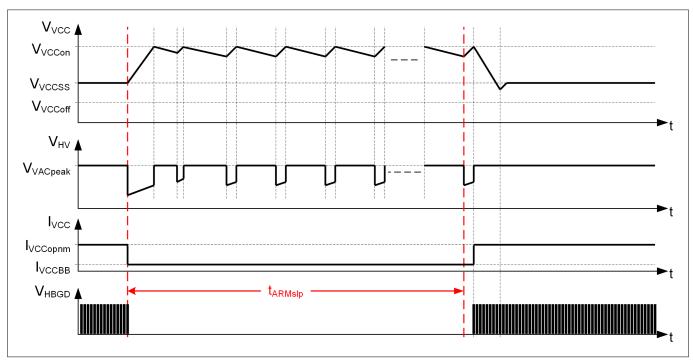

The VCC supply during the normal operation, including burst mode operation, should be generated from the auxiliary winding and the resonant capacitor. The start-up cell may be turned on during the burst mode operation to maintain the VCC voltage, in case that the VCC capacitor voltage drops below the level  $V_{\text{VCCslpHVon}}$  during a very long burst break. However, this turn-on of the start-up cell during the burst mode operation should be avoided to keep the system efficiency high at a light-load condition. For this purpose, a relatively high value of the VCC capacitor helps either the capacitor  $C_{\text{VCC1}}$  connected to the VCC pin or the buffer capacitor  $C_{\text{VCC3}}$ , as shown in *Figure 3*.

## 4 HFB power stage design

For the VCC capacitors, the total value is mainly dependent on the VCC charge-up time, the system start-up time requirement and the burst break time. For a long burst break time, the value of this capacitor must be high. Typically, a value between 47 and 100  $\mu$ F should satisfy most of the application cases.

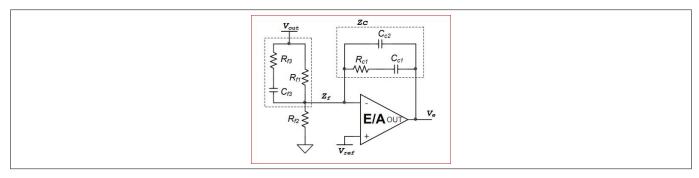

## 4.4 Output regulator

HFB supports fast line and load response via feedback signal with a wide bandwidth. This requires a type III (*Figure 17*) or a similar compensator. The characteristic and parameter design of such a compensator is well explained in the literature [3]. For the USB-PD application, the HFB controller reacts on the feedback signal for the voltage regulation in terms of speed or output ripple, while the output voltage offset or accuracy is controlled by the secondary side PD device.

Figure 17 Type III compensator

#### 5 Parameterization

#### **Parameterization** 5

The controller IC offers a flexible parameter configuration for ease of use. For the parameter configuration, a certain assistant hardware and software are needed. These are illustrated as follows:

- Required hardware (*Chapter 5.1*)

- .dp vision tool (Chapter 5.2)

- Configurable parameters (*Chapter 5.3*)

#### 5.1 Required hardware

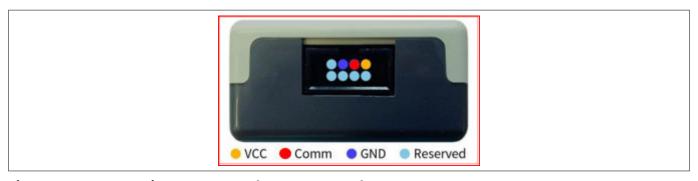

To communicate with the control IC, the dp interface board Gen 2 is required, as shown in *Figure 18*.

Figure 18 dp interface board

The dp interface board is connected to a computer via the mini-B USB port at the left-side end of the board. Upon a successful communication with the computer, the LED USB is ON. At the right-side end of the interface board, an 8-pin connector is available for the communication with the control IC XDPS2201 (Figure 19), where the pin VCC, Comm and GND must be connected to the IC VCC, MFIO and ground pin, respectively.

Figure 19 8-Pin connector to the target control IC

Note:

Both the connecting cables to the computer and the application IC must be as short as possible. For example, the USB cable to the computer must not be longer than 1 m to avoid the voltage drop along that cable, which is critical for burning the parameter into the control IC XDPS2201.

The interface board requires the FW version 2.5 (dplfGen2\_V2.5.0\_2017\_6\_27) or later for the communication with the control IC XDPS2201. This can be verified in the .dp vision tool under **Tools\DpifGen2 firmware** update.

#### 5 Parameterization

## 5.2 .dp vision tool

This chapter provides information about the .dp vision tool, the procedure for test and burn configuration set, and the .csv file.

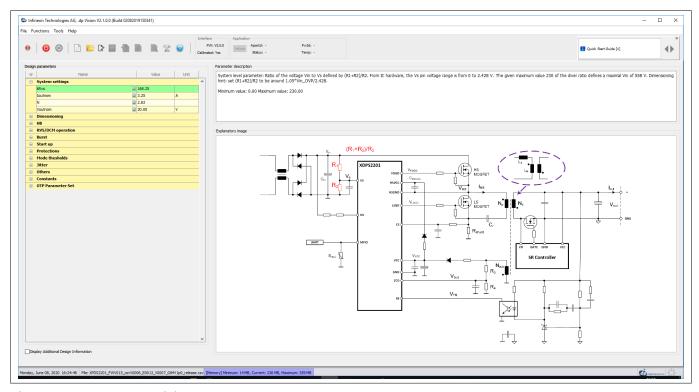

## 5.2.1 .dp vision GUI

Besides the dp interface board, the .dp vision tool is required. To support the control IC XDPS2201, the .dp vision version 2.1.0.0 or later is required. The graphical user interface (GUI) of this tool is shown in *Figure 20*.

Figure 20 .dp vision GUI

The version number of the .dp vision is shown at the upper-left corner of the GUI. The command icons enable fast access to the functions, which can also be accessed via the command on the top of the main window. For the parameters, three sub-windows are available: design parameter, parameter description and explanatory image. The use of these windows is self-explained, while the user manual about the .dp vision is available under the **Help** menu. Once a .csv file is successfully loaded, the loaded .csv file name is shown at the bottom-left corner of the GUI.

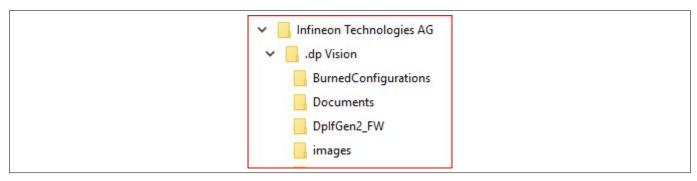

Note:

If the explanatory images are not included in the installation package, the zip file containing all of the images must be unzipped and saved to the **images** folder under the .dp vision, as shown in **Figure 21**. The **Infineon Technologies AG** folder can be found under the **user folder** window.

Figure 21 Images folder

#### 5 Parameterization

There is a check-box "Display Additional Design Information" at the bottom-left corner of the .dp vision GUI. Once checked, some of the derived parameters are shown that have important information for the system setup, such as the shunt resistor R<sub>shunt</sub> in the "System settings" group.

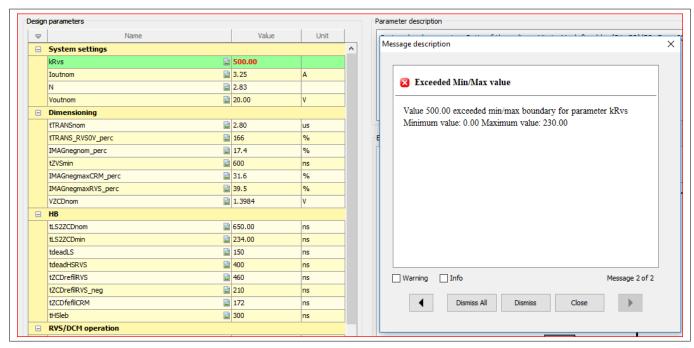

#### 5.2.2 Parameter value change

In the .dp vision GUI, the value of all input parameters can be changed. While changing the value, it is highly recommended to read the description of that parameter and its limit(s). Once the value change of a parameter is confirmed by pressing the return key, the .dp vision will check the plausibility of the parameter value. If the input value violates any of the limits, the .dp vision turns that value into red, gives a warning sound and then shows the error in the sub-window at the upper-right corner (Figure 22). If one parameter value is correlated to the other parameter(s), the change of that parameter may cause the other parameter value(s) to be invalid. It is mandatory to correct the invalid value before saving the configuration, test or burning the configuration set.

Figure 22 Error message from .dp vision

#### **Procedure for test configuration set** 5.2.3

Depending on the application, the default parameter value set may need some fine adjustment for a better performance. For a trial with the new parameter set, the .dp vision enables test for the parameter set without burning it to the memory cells of the control IC. This is the **Test Configuration Set** function, and the following sequential steps need to be performed:

- 1. Load the .csv file

- 2. Set the value properly

- 3. Save the .csv file

- 4. Power on device

- 5. Turn on the AC source

- 6. **Test Configuration Set**

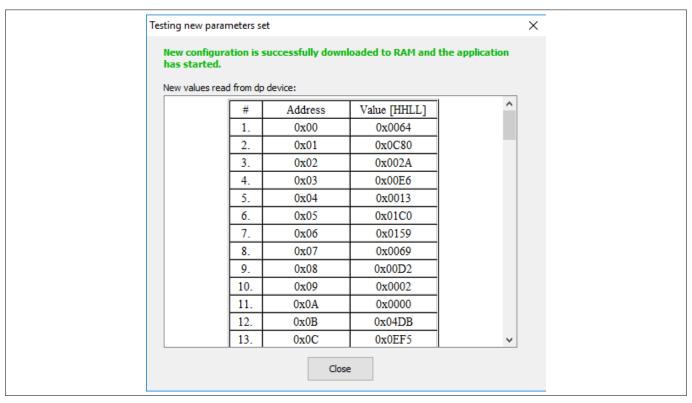

After these steps, the following message window (Figure 23) displays, while the application is started automatically with the newly configured parameter set.

#### 5 Parameterization

Figure 23 Message at Test Configuration Set

Note: If Step 6 "Test Configuration Set" is executed before Step 5 "Turn on the AC source", then the latest stored parameter set is used instead of the newly configured parameter set.

The message in *Figure 23* shows only the affected FW application parameter (APARAM): address and the corresponding values, but not the original input parameters. In fact, the input parameter values have to be calculated, converted into the defined format and arranged in the correct order by the .dp vision tool based on the loaded .csv file, respectively. Only in this way, the control IC can receive the APARAM values and run accordingly.

#### **Procedure for burn configuration set** 5.2.4

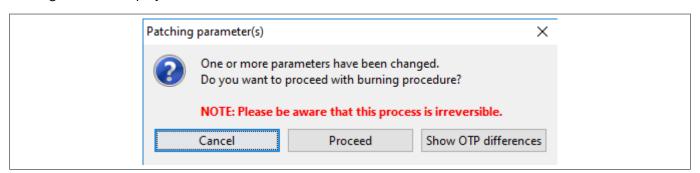

After the parameter set is tested and fixed, the parameter can be burnt into the memory cells to avoid repeating the above-mentioned steps with **Test Configuration Set**. Click the **Burn Configuration Set** icon, the following message window displays:

Figure 24 **Message at Burn Configuration Set**

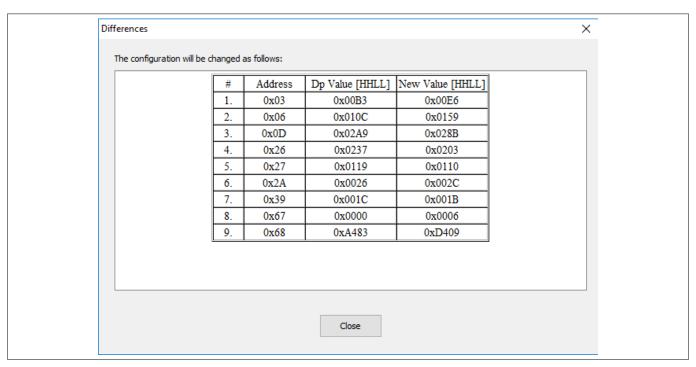

As the title of the message window "Patching parameter(s)" indicates, the **Burn Configuration Set** changes only those APARAM values which are different from the ones stored in the control IC XDPS2201, and not the entire APARAM set. With the **Show OTP differences** button, the parameters with different values will be shown, as seen in *Figure 25*, where only the input parameter *I*<sub>outnom</sub> was changed.

#### 5 Parameterization

Figure 25 Message at Show OTP differences

As shown in the figure, the value of several parameters are different even though only the input parameter  $I_{\rm outnom}$  is changed. In this example, the first seven changes are dependent on that input parameter. The item no. 8 at address 0x67 is related to the .csv file version number. The IC from factory is burnt with a certain firmware .ahex file containing a default .csv file version number, here 0x0000, but the currently loaded .csv file has another version number, here 0x0006. This .csv file version number is only for the tracking purpose, and has no impact on the system performance. The item no. 9 at the address 0x68 is the CRC checksum of the parameter values and varies according to the value setting. In case the default parameter set satisfies the application, the **Burn Configuration Set** is not necessary. But if it is already performed, then this window will display only the change of the item at addresses 0x67 and 0x68, due to different .csv file version numbers and the CRC checksum result.

For burning a configuration set, the procedure is as follows:

- **1.** Load the .csv file

- 2. Set the appropriate parameter value

- **3.** Save the .csv file

- 4. Burn Configuration Set

After Step 4, the IC is ready for application with the newly burnt parameter set.

## 5.2.5 .csv file

For parameter value adjustment, a .csv file is required. The .csv file is just an intermediate means to get the correct APARAM for the IC operation, which takes customer **Design parameters**, calculates some important derived parameters for customer information and the APARAMs for IC. Therefore, the .csv file is necessary if the application parameter value is different from the default setting.

Additionally, the .csv file includes the information about the FW version number. The FW version number stored in the IC and the loaded .csv file must match. If not, then it is impossible to change the IC APARAM with that .csv file.

Normally, the APARAM burning can be performed several times with the same IC, since only the parameter with a new value will be burnt to the IC each time. Depending on the number of parameters with a changed value, the times of parameter re-burning varies. In general, the memory size is big enough for the design phase. In case the left free memory cells are not big enough, then a new IC is required for a new parametrization.

#### 5 Parameterization