## XMC4000

32-bit Microcontroller Series for Industrial Applications

## Digital to Analog Converter (DAC)

AP32301

**Application Note**

## **About this document**

### **Scope and purpose**

This document describes the features of the DAC peripheral and how to configure it for common cases such as data processing, pattern generation and noise generation.

### **Applicable Products**

• XMC4000 Microcontrollers Family

### References

Infineon: Example code: <a href="http://www.infineon.com/XMC4000">http://www.infineon.com/XMC4000</a> Tab: Documents

Infineon: XMC Lib, <a href="http://www.infineon.com/DAVE">http://www.infineon.com/DAVE</a>

Infineon: DAVE™, <a href="http://www.infineon.com/DAVE">http://www.infineon.com/DAVE</a>

Infineon: XMC Reference Manual, <a href="http://www.infineon.com/XMC4000">http://www.infineon.com/XMC4000</a> Tab: Documents

Infineon: XMC Data Sheet, <a href="http://www.infineon.com/XMC4000">http://www.infineon.com/XMC4000</a> Tab: Documents

## **Table of Contents**

## **Table of Contents**

| About   | this document                     | 1  |

|---------|-----------------------------------|----|

| Table o | of Contents                       |    |

| 1       | Digital to Analog Converter (DAC) |    |

| 1.1     | XMC DAC operation modes           |    |

| 1.2     | XMC DAC input types               |    |

| 1.3     | XMC DAC data refinement           |    |

| 1.4     | Basic DAC equations               | 6  |

| 2       | Single Value mode                 | 7  |

| 2.1     | XMC Lib configuration             |    |

| 2.2     | XMC Lib initialization            | 8  |

| 2.3     | Function implementation           | 8  |

| 3       | Data Processing mode              | g  |

| 3.1     | XMC Lib configuration             | g  |

| 3.2     | XMC Lib initialization            | c  |

| 3.3     | Function implementation           | 10 |

| 4       | Pattern Generator mode            | 11 |

| 4.1     | XMC Lib configuration             | 12 |

| 4.2     | XMC Lib initialization            | 12 |

| 5       | Noise Generator mode              | 13 |

| 5.1     | XMC Lib configuration             | 14 |

| 5.2     | XMC Lib initialization            | 14 |

| 6       | Ramp Generator mode               | 15 |

| 6.1     | XMC Lib configuration             | 16 |

| 6.2     | XMC Lib initialization            | 16 |

| 7       | Revision History                  | 17 |

### **Digital to Analog Converter (DAC)** 1

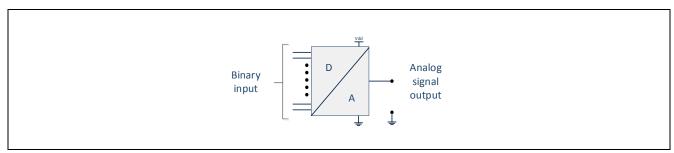

**Digital to Analog Converter** Figure 1

A digital to analog converter is a module to convert one or multiple bits digital value into an analog value. It is defined through:

- resolution

- conversation rate

- offset

- accuracy of the analog output

- drive capability

The DAC refill method has an influence on the system performance. To reduce the load on the CPU, the DAC can be refilled by Direct Memory Access (DMA) or the DAC module itself provides waveform generating parts. In addition in some applications a data refinement, for example a static offset or multiplication, is necessary.

### **XMC DAC operation modes** 1.1

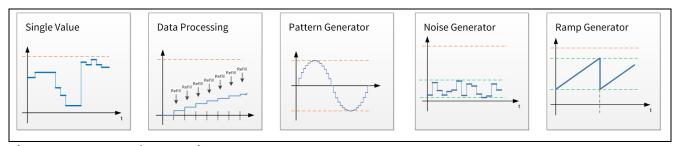

The DAC module provides five operation modes:

**DAC** modes overview Figure 2

The modes differentiate in the refill method to reduce the CPU load. The operation modes are described in the following sections.

**Digital to Analog Converter (DAC)**

#### 1.2 **XMC DAC input types**

For each operation mode a specific input type is available.

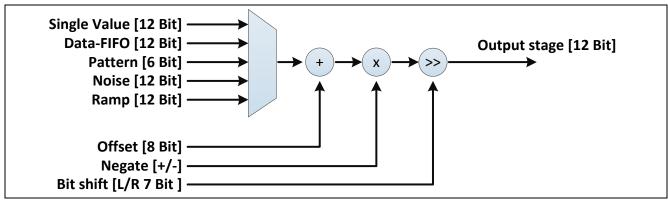

Figure 3 DAC input types and data manipulation

The Single Value input provides a fast access to the analog output. This input is used for non-periodic or software controlled output.

The Data-FIFO input enables the fill stage and the DAC output stage to be decoupled. This input is used for periodic updates. The refill can be done by software (SW) or hardware (HW) via DMA trigger.

The **Pattern** generator has a 6 bit output. A customized symmetric pattern can be generated, where the first quarter of the pattern is defined by the user.

The **Noise** generator provides a pseudo random value with 12 bit resolution.

The **Ramp** generator provides a ramp with 12 bit resolution, where the value is increased by each clock cycle and the start and stop value can be defined by the user.

The five inputs represent also the five modes of the DAC

Single Value input: Single Value mode Data-FIFO input: **Data Processing mode** Pattern input: **Pattern Generator mode** Noise input: **Noise Generator mode** Ramp input: **Ramp Generator mode**

**Digital to Analog Converter (DAC)**

#### **XMC DAC data refinement** 1.3

The Output stage is the 12 bit value which is transformed into an analog value. It can be interpreted as unsigned or signed value. In unsigned mode, a 0 is interpreted as lowest analog value. In signed mode, a 0 generates the center voltage. The data can be refined between input and the Output stage. The refinement options are: Offset, Negate and Bit shift.

The XMC provides an 8 bit Offset which is added to the input. The sign interpretation of the Offset follows the Output stage.

A Negate bit inverts the sign of the input. This can be used with the Single Value or Data Processing mode as HW inversion, in the **Pattern Generator mode** to start with a negative half wave or in **Ramp Generator mode** to generate a falling ramp. The negate bit is available on specific devices only.

The **Bit shift** allows a multiplication or division of the input. This means the input can either multiplied or divided by 2<sup>1</sup> to 2<sup>7</sup> [2...128]. This can then used for the following use cases:

- scaling in Single Value or Data Processing mode

- scale the pattern from the **Pattern Generator mode** to the DAC output range

- reduce the scale in the **Noise Generator mode**

- expand the minimum and maximum frequency in the Ramp Generator mode

**Digital to Analog Converter (DAC)**

### 1.4 Basic DAC equations

The transformation from unsigned output stage to analog value can be done with following calculations.

DEC<sub>target</sub>

Target decimal value in the DAC output register

S\_DEC<sub>target</sub>

Target signed decimal value in the DAC output register

DEC<sub>res</sub> Decimal resolution of the DAC

V<sub>target</sub> Target DAC output Voltage

V<sub>max</sub> Maximum DAC output Voltage

• V<sub>offset</sub> DAC offset Voltage

$DAC_{res}$ ,  $V_{max}$  and  $V_{offset}$  can be found in the Datasheet.

$$\textit{DEC}_{target} = \frac{\textit{V}_{target} - \textit{V}_{offset}}{\textit{V}_{max} - \textit{V}_{offset}} * \textit{DEC}_{res}$$

$$V_{target} = \left( DEC_{target} * \frac{\left( V_{max} - V_{offset} \right)}{DEC_{res}} \right) + V_{offset}$$

If the Output stage is interpreted as signed, the following calculations can be used:

$$S\_DEC_{target} = \left(\frac{V_{target} - V_{offset}}{V_{max} - V_{offset}} * DEC_{res}\right) - \frac{DEC_{res} + 1}{2}$$

$$V_{target} = \left( \left( S\_DEC_{target} + \frac{DEC_{res} + 1}{2} \right) * \frac{\left( V_{max} - V_{offset} \right)}{DEC_{res}} \right) + V_{offset}$$

The following example shows the equations with  $V_{max}$ =2.5V,  $V_{offset}$ =0.3V, DAC<sub>res</sub>=(2<sup>12</sup>-1):

$$DEC_{target} = \frac{V_{target} - 0.3V}{2.2V} * 4095$$

$$V_{target} = \left(DEC_{target} * \frac{2,2V}{4095}\right) + 0.3V$$

$$S\_DEC_{target} = \left(\frac{V_{target} - 0.3V}{2.2V} * 4095\right) - 2048$$

$$V_{target} = \left( \left( S\_DEC_{target} + 2048 \right) * \frac{2,2V}{4095} \right)$$

6

Single Value mode

### Single Value mode 2

The single value mode can be used for simple digital to analog conversion. Writing to the DATA Register leads to a change of the analogue output. The DAC can be modified to accept unsigned or signed data. The following data refinement is available: offset, scaling and negation.

If channel 0 and channel 1 are used and have to be updated simultaneously, the synchronization feature can be used. In this mode the data for both channels can be written into one register. With a trigger of channel 0 both values are updated. A trigger can either be a software trigger or a pseudo write access to the original channel 0 data register.

### 2.1 **XMC Lib configuration**

This example shows two DAC configurations in Single Value mode. The DACs are filled by software. If a new value is written into the data register it is emitted with the next DAC clock. The channels are not synchronized. The first channel is configured for unsigned, the second for signed values. Both channels do not use the scaling and negation feature. Both channels are initialized with the corresponding configuration: Channel 0 as unsigned DAC and channel 1 as signed DAC.

```

#define DAC CH NR 0

0U

#define DAC CH NR 1

1U

XMC DAC CH CONFIG t ch config0=

.output_offset

0U,

.data type

XMC DAC CH DATA TYPE UNSIGNED,

.output_scale

XMC DAC CH OUTPUT SCALE NONE,

.output negation =

XMC DAC CH OUTPUT NEGATION DISABLED,

};

XMC DAC CH CONFIG t ch config1=

.output offset =

0U,

XMC DAC CH_DATA_TYPE_SIGNED,

.data type

.output scale

XMC DAC CH OUTPUT SCALE NONE,

XMC DAC CH OUTPUT NEGATION DISABLED,

.output negation =

};

```

Single Value mode

### 2.2 XMC Lib initialization

The DAC channel is initialized in general and then configured to the specific mode.

```

XMC_DAC_CH_Init(XMC_DAC0, DAC_CH_NR_0, &ch_config0);

XMC_DAC_CH_Init(XMC_DAC0, DAC_CH_NR_1, &ch_config1);

```

After the initialization the DAC mode is changed to "Single Value Mode".

```

XMC_DAC_CH_StartSingleValueMode(XMC_DAC0, DAC_CH_NR_0);

XMC DAC CH StartSingleValueMode(XMC DAC0, DAC CH NR 1);

```

## 2.3 Function implementation

And the DAC channels are filled with the value 0. As the channel 0 is configured as unsigned the zero will be interpreted as minimum voltage. While the channel 1 is configured as signed the value zero will be interpreted as center voltage. Channel 0 needs to be filled with unsigned 12 bit values and channel 1 with signed 12 bit values. The "XMC\_DAC\_CH\_Write()" function can be called periodically in order to update and trigger the DAC conversion. The call frequency should not exceed the maximum DAC update frequency.

```

XMC_DAC_CH_Write(XMC_DAC0, DAC_CH_NR_0, 0x0000U);

XMC_DAC_CH_Write(XMC_DAC0, DAC_CH_NR_1, 0x0000U);

```

**Data Processing mode**

## 3 Data Processing mode

The Data Processing mode is similar to the Single Value mode expect that it supports an interrupt based reload of the DAC. The reload does not trigger a conversion and can be done via DMA or SW.

The Data Processing mode allows large and precise tables for waveform generation, where data are stored in the flash or RAM.

## 3.1 XMC Lib configuration

This example shows a DAC configuration in Data Processing mode. When a trigger occurs the DAC is filled by software in the interrupt service routine (ISR). The DAC module generates a trigger with 10 kHz by itself.

### 3.2 XMC Lib initialization

The DAC channel is initialized in general and then configured to the specific mode.

```

XMC DAC CH Init(XMC DACO, DAC CH NR 0, &ch config0);

```

After the general initialization the DAC needs to be configured to Data Process mode ("DataMode"). The DAC trigger is generated by the DAC module. Therefore the frequency is set to 10 kHz. If an external trigger is used, the frequency selection is not required and can be set to zero. After the DAC is initialized, the DAC event and service request are enabled.

### **Data Processing mode**

## **3.3** Function implementation

In the DACO ISR the new value from the data table is written into the DATA register.

**Pattern Generator mode**

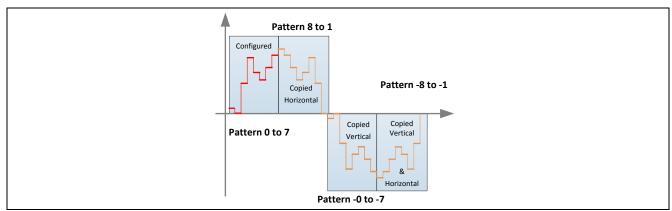

### 4 Pattern Generator mode

The Pattern Generator mode generates a pattern without software load. One quarter of the waveform needs to be defined. The rest of the waveform is generated by horizontal and vertical mirroring of the first quarter.

**DAC pattern configuration** Figure 4

Figure 5 **DAC** pattern wave

The wave is fixed to a length resolution of 32 steps and an amplitude resolution of 64 steps. The 6 bit amplitude resolution can be scaled to reach the 12 bit DAC output.

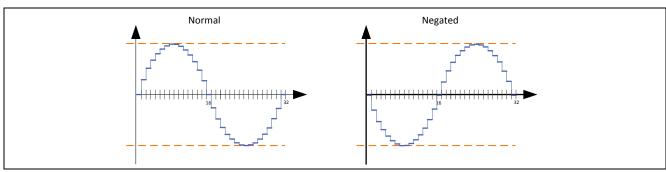

With negation enabled the wave starts inverted:

Figure 6 **DAC Pattern negated**

An offset can also be added. The offset is in the Pattern Generator scale (6 bit). If a scaling is added, the pattern is scaled after adding the offset.

The Pattern Generator also provides a sign output. This can be used to trigger the ADC or routed through the ERU to trigger other peripherals such as a timer. The signal can also be routed through the ERU to a GPIO.

### **Pattern Generator mode**

### **XMC Lib configuration** 4.1

This example shows how the DAC can be configured in Pattern Generator mode. Channel 0 is configured to generate a 500Hz sine wave. The output of the Pattern Generator is a 6 bit signed data. Therefore the DAC is configured in signed mode. To reach the 12 bit DAC scale the data need to be multiplied by 64 (shifted by 6 bit). Neither the offset nor the negation is used.

The channel 0 is initialized with the corresponding configuration:

```

#define DAC CH NR 0

0 U

XMC DAC_CH_CONFIG_t ch_config0=

.output offset =

OU,

.data_type = XMC_DAC_CH_DATA_TYPE_SIGNED,

.output scale = XMC DAC CH OUTPUT SCALE MUL 64,

.output negation = XMC DAC CH OUTPUT NEGATION DISABLED,

};

```

#### 4.2 **XMC Lib initialization**

The DAC channel is initialized in general and then configured to the specific mode.

```

XMC DAC CH Init (XMC DACO, DAC CH NR O, &ch config0);

```

After the general initialization the DAC needs to be configured to Pattern Generator mode ("PatternMode"). One of the three predefined patterns, the sine pattern, is used. The sign output is disabled, the DAC clock source is set to intern and the pattern frequency is set to 500Hz.

```

const uint8_t pattern[] = XMC_DAC_PATTERN_SINE;

XMC DAC CH StartPatternMode (XMC DACO, DAC CH NR 0,

pattern,

XMC DAC CH PATTERN SIGN OUTPUT DISABLED,

XMC DAC CH TRIGGER INTERNAL,

500);

```

An additional function implementation is not necessary.

**Noise Generator mode**

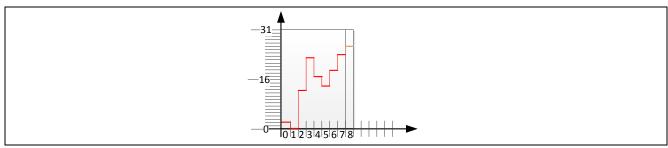

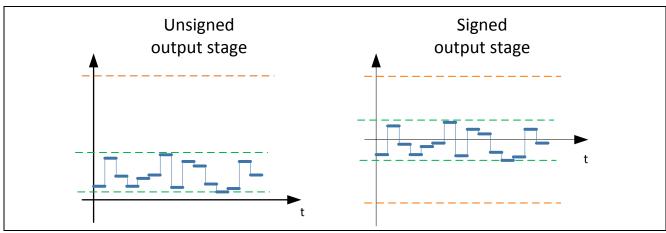

### 5 **Noise Generator mode**

The noise generator mode provides a 20 bit linear feedback shift register to produce a pseudo random number. The 12 bit random numbers are sampled with the preselected trigger. The output can be additionally scrambled by changing the scaling, the offset, the negation and the signed/unsigned interpretation at runtime.

By using negative scaling (division by 2x) the amplitude can be limited. If the Output stage is interpreted as signed value, an offset of half the DAC output is generated.

Figure 7 DAC noise sign and unsigned output stage

**Noise Generator mode**

### 5.1 **XMC Lib configuration**

In this example the DAC is configured in Noise Generator mode. The output of the noise generator is 12 bit unsigned data. Therefore the offset is set to zero, the data type is set to unsigned and the scaling and the negation are disabled.

The channel 0 is initialized with the corresponding configuration:

```

#define DAC CH NR 0

ΟIJ

XMC DAC CH CONFIG t ch config0 =

{

.output offset =

OU,

.data_type = XMC_DAC_CH_DATA_TYPE_UNSIGNED,

.output scale = XMC DAC CH OUTPUT SCALE NONE,

.output negation = XMC DAC CH OUTPUT NEGATION DISABLED,

};

```

#### **XMC Lib initialization** 5.2

The DAC channel is initialized in general and then configured to the specific mode.

```

XMC_DAC_CH_Init(XMC_DAC0, DAC_CH_NR_0, &ch_config0);

```

After the general initialization the DAC needs to be configured to Noise Generator mode ("NoiseMode"). The DAC clock source is set to internal and the noise frequency is set to 50 kHz.

```

XMC DAC CH StartNoiseMode (XMC DACO, DAC CH NR 0,

XMC DAC CH TRIGGER INTERNAL,

50000U);

```

An additional function implementation is not necessary.

**Ramp Generator mode**

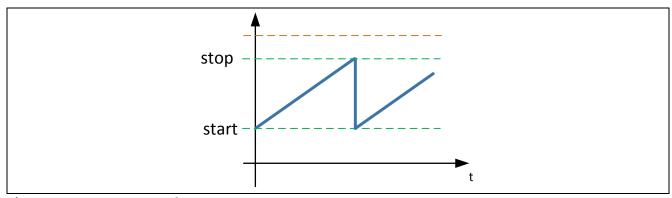

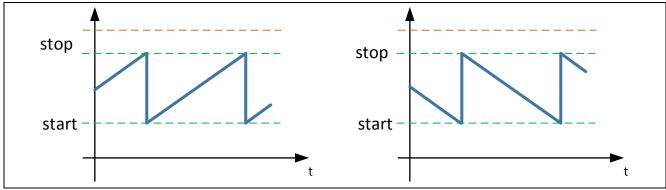

### **Ramp Generator mode** 6

The Ramp Generator mode generates a voltage ramp with a 12 bit resolution. The amplitude is defined by the start and stop value. The slope is defined by the clock input.

Figure 8 **DAC ramp mode**

The negation feature allows also a negative ramp. The negation bit builds the 2's complement of the start and stop value in 12 bit format. Therefore the initial start and stop values also need to be 2's complement format and swapped. For example original start value is 100U and stop value is 3500U. The 2's complement of 100 in 12 bit format is 3996U and of 3500U is 569U. Now the values need to be swapped. The new start value is 596U and stop value is 3996U.

Figure 9 DAC ramp positive and negative slope

With the scaling feature minimum and maximum ramp frequency can be enlarged:

The slope of the ramp is defined by the DAC clock. Each clock cycle increases the digital output by one. When small amplitudes are used, this can limit the minimum ramp frequency. This can be compensated by doubling the start and stop value and adding a negative scale 2<sup>x-1</sup>.

This can also be done in the opposite way. Full scaled amplitude limits the maximum ramp frequency. This can be changed by halving the start and stop values and multiplying two. This reduces the ramp resolution.

**Ramp Generator mode**

### 6.1 **XMC Lib configuration**

This example configures a DAC channel in Ramp Generator mode. The Ramp Generator output is a 12 bit unsigned value. Therefore the DAC channel is configured as unsigned and unscaled. The offset and the negation are disabled.

```

#define DAC CH NR 0

0 U

XMC DAC CH CONFIG t ch config0=

.output offset =

0U,

.data type = XMC_DAC_CH_DATA_TYPE_UNSIGNED,

.output scale = XMC DAC CH OUTPUT SCALE NONE,

.output negation = XMC DAC CH OUTPUT NEGATION DISABLED,

};

```

#### 6.2 **XMC Lib initialization**

The DAC channel is initialized in general and then configured to the specific mode.

```

XMC DAC CH Init (XMC DACO, DAC CH NR 0, &ch config0);

```

After the general initialization the DAC needs to be configured to Ramp Generator mode ("RampMode"). The START\_VALUE is defined as 80 the STOP\_VALUE as 3500. The DAC clock source is set to internal and the ramp frequency is set to 500Hz.

```

#define START VALUE

80

#define STOP VALUE

3500

XMC DAC CH StartRampMode (XMC DACO, DAC CH NR 0,

START VALUE,

STOP VALUE,

XMC DAC CH TRIGGER INTERNAL,

500U);

```

An additional function implementation is not necessary.

**Revision History**

## **7** Revision History

Current Version is V1.0, 2015-07

| Page or Reference | Description of change |

|-------------------|-----------------------|

| V1.0, 2015-07     |                       |

|                   | Initial Version       |

17

### **Trademarks of Infineon Technologies AG**

AURIX™, C166™, Canpak™, CIPOS™, CIPURSE™, CoolGan™, CoolMoS™, CoolSiC™, Corecontrol™, Crossave™, Dave™, Di-Pol™, Diblade™, EasyPIM™, EconoBridge™, EconoPack™, EconoPim™, Eicedriver™, eupec™, FCOS™, HITFET™, HybridPack™, IsoFace™, IsoPack™, i-Wafer™, Mipaq™, ModStack™, my-d™, Novalithic™, Omnitune™, OPTIGA™, OptiMoS™, ORIGA™, POWERCODE™, PRIMARION™, PrimeStack™, PROFET™, PRO-Sil™, Rasic™, Reversave™, Satric™, Sieget™, Sipmos™, SmartLewis™, Solid Flash™, Spoc™, thinQ!™, Trenchstop™, Tricore™.

### Other Trademarks

Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. ANSI™ of American National Standards Institute. AUTOSAR™ of AUTOSAR development partnership. Bluetooth™ of Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. HYPERTERMINAL™ of Hilgraeve Incorporated. MCS™ of Intel Corp. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Integrated Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ of Openwave Systems Inc. RED HAT™ of Red Hat, Inc. RFMD™ of RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2014-07-17

### www.infineon.com

**Edition 2015-07 Published by Infineon Technologies AG** 81726 Munich, Germany

© 2015 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com

Document reference AP32301

### **Legal Disclaimer**

THE INFORMATION GIVEN IN THIS APPLICATION NOTE (INCLUDING BUT NOT LIMITED TO CONTENTS OF REFERENCED WEBSITES) IS GIVEN AS A HINT FOR THE IMPLEMENTATION OF THE INFINEON TECHNOLOGIES COMPONENT ONLY AND SHALL NOT BE REGARDED AS ANY DESCRIPTION OR WARRANTY OF A CERTAIN FUNCTIONALITY, CONDITION OR QUALITY OF THE INFINEON TECHNOLOGIES COMPONENT. THE RECIPIENT OF THIS APPLICATION NOTE MUST VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE REAL APPLICATION. INFINEON TECHNOLOGIES HEREBY DISCLAIMS ANY AND ALL WARRANTIES AND LIABILITIES OF ANY KIND (INCLUDING WITHOUT LIMITATION WARRANTIES OF NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS OF ANY THIRD PARTY) WITH RESPECT TO ANY AND ALL INFORMATION GIVEN IN THIS APPLICATION NOTE.

### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office. Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.