# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

### **PRELIMINARY**

# Single-Chip 5G WiFi IEEE 802.11ac MAC/ Baseband/Radio with Integrated Bluetooth 4.1

### **General Description**

The Cypress® CYW4339 single-chip device provides the highest level of integration for Internet of Things and handheld wireless system with integrated single-stream IEEE 802.11ac MAC/baseband/radio and Bluetooth 4.1. In IEEE 802.11ac mode, the WLAN operation supports rates of MCS0–MCS9 (up to 256 QAM) in 20 MHz, 40 MHz, and 80 MHz channels for data rates up to 433.3 Mbps. In addition, all the rates specified in IEEE 802.11a/b/g/n are supported. Included on-chip are 2.4 GHz and 5 GHz transmit amplifiers, and receive low-noise amplifiers. Optional external PAs, LNAs, and antenna diversity are also supported.

For the WLAN section, several alternative host interface options are included: an SDIO v3.0 interface that can operate in 4b or 1b and a PCIe Gen1 interface (3.0 compliant). For the Bluetooth section, host interface options of a high-speed 4-wire UART and USB 2.0 full-speed (12 Mbps) are provided.

Using advanced design techniques and process technology to reduce active and idle power, the CYW4339 is designed to address the needs of mobile devices that require minimal power consumption and compact size. It includes a power management unit which simplifies the system power topology and allows for direct operation from a mobile platform battery while maximizing battery life.

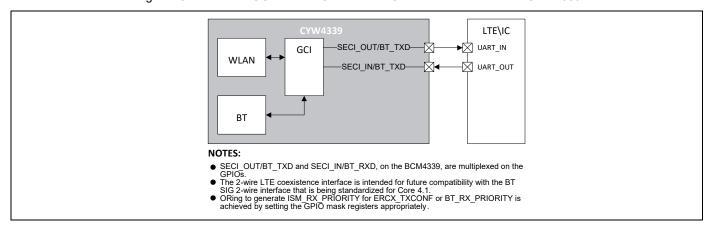

The CYW4339 implements highly sophisticated enhanced collaborative coexistence hardware mechanisms and algorithms, which ensure that WLAN and Bluetooth collaboration is optimized for maximum performance. In addition, coexistence support for external radios (such as LTE cellular, GPS, and WiMAX) is provided via an external interface. As a result, enhanced overall quality for simultaneous voice, video, and data transmission is achieved.

### **Features**

### IEEE 802.11x Key Features

- IEEE 802.11ac compliant.

- Single-stream spatial multiplexing up to 433.3 Mbps data rate.

- Supports 20, 40, and 80 MHz channels with optional SGI (256 QAM modulation).

- Full IEEE 802.11a/b/g/n legacy compatibility with enhanced performance.

- Supports Rx space-time block coding (STBC)

- Supports IEEE 802.11ac/n beamforming.

- On-chip power amplifiers and low-noise amplifiers for both bands.

- Support for optional front-end modules (FEM) with external PAs and LNAs

- Shared Bluetooth and WLAN receive signal path eliminates the need for an external power splitter while maintaining excellent sensitivity for both Bluetooth and WLAN.

- Internal fractional nPLL allows support for a wide range of reference clock frequencies

- Supports IEEE 802.15.2 external coexistence interface to optimize bandwidth utilization with other co-

- located wireless technologies such as LTE, GPS, or WiMAX

- Supports standard SDIO v3.0 (including DDR50 mode at 50 MHz and SDR104 mode at 208 MHz, 4-bit and 1-bit) host interfaces.

- Backward compatible with SDIO v2.0 host interfaces.

- PCIe mode (FCBGA package only) complies with PCI Express base specification revision 3.0 compliant Gen1 interface for ×1 lane and power management base specification.

- Integrated ARMCR4<sup>™</sup> processor with tightly coupled memory for complete WLAN subsystem functionality, minimizing the need to wake up the applications processor for standard WLAN functions. This allows for further minimization of power consumption, while maintaining the ability to field upgrade with future features. On-chip memory includes 768 KB SRAM and 640 KB ROM.

- OneDriver<sup>™</sup> software architecture for easy migration from existing embedded WLAN and Bluetooth devices as well as future devices.

#### **Bluetooth Key Features**

- Complies with Bluetooth Core Specification Version 4.1 with provisions for supporting future specifications.

- Bluetooth Class 1 or Class 2 transmitter operation.

- Supports extended synchronous connections (eSCO), for enhanced voice quality by allowing for retransmission of dropped packets.

- Adaptive frequency hopping (AFH) for reducing radio frequency interference.

- Interface support, host controller interface (HCI) using a USB or high-speed UART interface and PCM for audio data.

- USB 2.0 full-speed (12 Mbps) supported (FCFBGA and WLCSP packages).

- Low power consumption improves battery life of handheld devices.

- Supports multiple simultaneous Advanced Audio Distribution Profiles (A2DP) for stereo sound.

- Automatic frequency detection for standard crystal and TCXO values.

- Supports serial flash interfaces.

#### **General Features**

- Supports battery voltage range from 3.0V to 5.25V supplies with internal switching regulator.

- Programmable dynamic power management

- OTP: 502 bytes of user-accessible memory

- GPIOs: 12 on FCFBGA, nine on WLBGA, and 16 on **WLCSP**

- Package options:

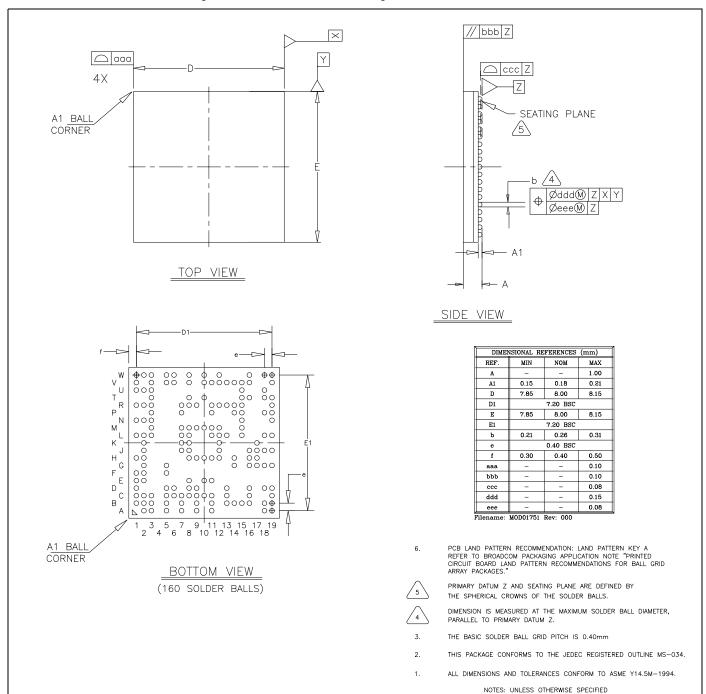

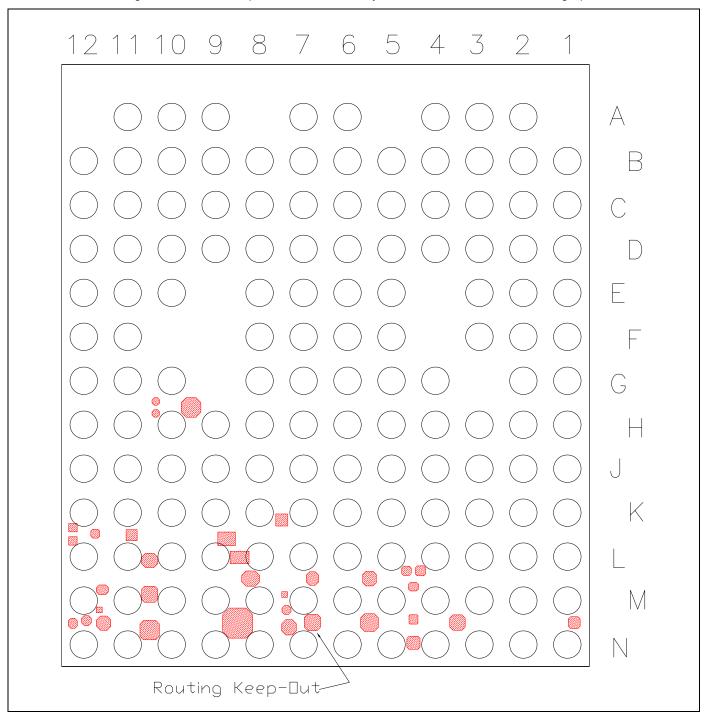

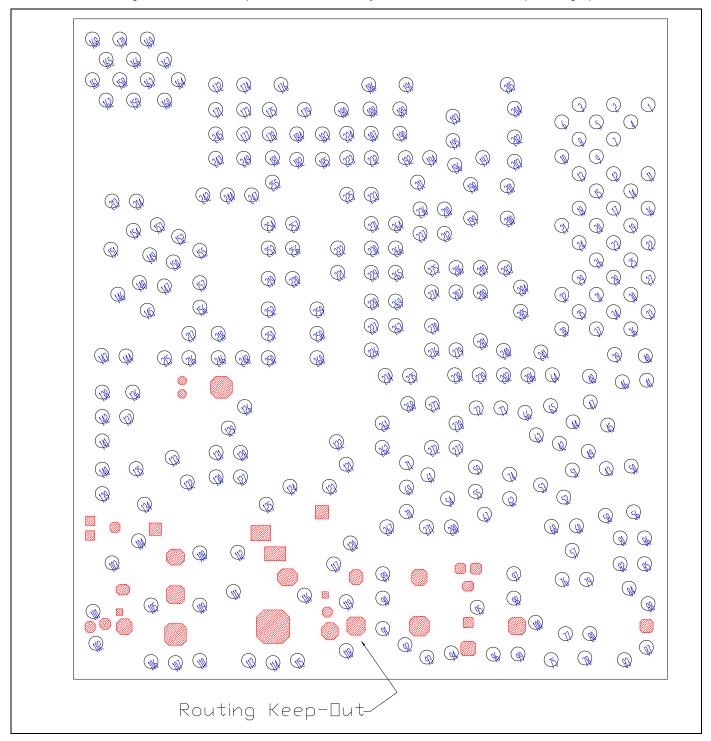

- 160 ball FCFBGA (8 mm x 8 mm, 0.4 mm pitch)

- □ 145 ball WLBGA (4.87 mm × 5.413 mm, 0.4 mm pitch)

- 286 bump WLCSP (4.87 mm × 5.413 mm, 0.2 mm) pitch)Security:

- □ WPA<sup>™</sup> and WPA2<sup>™</sup> (Personal) support for powerful encryption and authentication

- AES and TKIP in hardware for faster data encryption and IEEE 802.11i compatibility

- □ Reference WLAN subsystem provides Cisco® Compatible Extensions (CCX, CCX 2.0, CCX 3.0, CCX 4.0, CCX 5.0)

- Reference WLAN subsystem provides Wi-Fi Protected Setup (WPS)

- Worldwide regulatory support: Global products supported with worldwide homologated design.

Figure 1.Functional Block Diagram VIO VRAT WL REG ON 5 GHz WLAN TX WLAN FEM or PCle Host I/F T/R 5 GHz WLAN RX SDIO\* Switch External COEX < Coexistence I/F 2.4 GHz WLAN TX FEM or 2.4 GHz WLAN/BT RX T/R CYW4339 Switch Bluetooth TX CLK\_REQ ← BT\_REG\_ON UART ◀ USB 2.0 ◀ Bluetooth Host I/F PCM BT DEV WAKE BT HOST WAKE 4

# **Contents**

| 1. | Ove | erview 5                                                                                                                |

|----|-----|-------------------------------------------------------------------------------------------------------------------------|

|    | 1.1 | Overview 5                                                                                                              |

|    | 1.2 | Features 6                                                                                                              |

|    | 1.3 | Standards Compliance 7                                                                                                  |

| 2. | Pov | ver Supplies and Power Management 8                                                                                     |

|    | 2.1 | Power Supply Topology 8                                                                                                 |

|    | 2.2 | PMU Features 8                                                                                                          |

|    | 2.3 | WLAN Power Management 10                                                                                                |

|    | 2.4 | PMU Sequencing10                                                                                                        |

|    | 2.5 | Power-Off Shutdown11                                                                                                    |

|    | 2.6 | Power-Up/Power-Down/Reset Circuits11                                                                                    |

| 3. | Fre | quency References 12                                                                                                    |

|    | 3.1 | Crystal Interface and Clock Generation 12                                                                               |

|    | 3.2 | External Frequency Reference                                                                                            |

|    | 3.3 | Frequency Selection                                                                                                     |

|    | 3.4 | External 32.768 kHz Low-Power Oscillator 15                                                                             |

| 4. | Blu | etooth Subsystem Overview 16                                                                                            |

|    | 4.1 | Features16                                                                                                              |

|    | 4.2 | Bluetooth Radio17                                                                                                       |

|    |     | 4.2.1 Transmit                                                                                                          |

|    |     | <ul><li>4.2.2 Digital Modulator</li></ul>                                                                               |

|    |     | 4.2.4 Power Amplifier                                                                                                   |

|    |     | 4.2.5 Receiver                                                                                                          |

|    |     | <ul><li>4.2.6 Digital Demodulator and Bit Synchronizer 17</li><li>4.2.7 Receiver Signal Strength Indicator 17</li></ul> |

|    |     | 4.2.8 Local Oscillator Generation                                                                                       |

|    |     | 4.2.9 Calibration                                                                                                       |

| 5. | Blu | etooth Baseband Core19                                                                                                  |

|    | 5.1 | Bluetooth 4.1 Features                                                                                                  |

|    | 5.2 | Bluetooth Low Energy19                                                                                                  |

|    | 5.3 | Link Control Layer                                                                                                      |

|    | 5.4 | Test Mode Support                                                                                                       |

|    | 5.5 | Bluetooth Power Management Unit                                                                                         |

|    |     | 5.5.1 RF Power Management 21 5.5.2 Host Controller Power Management 21                                                  |

|    |     | 5.5.3 BBC Power Management                                                                                              |

|    |     | 5.5.4 Wideband Speech                                                                                                   |

|    |     | 5.5.5 Packet Loss Concealment                                                                                           |

|    |     | 5.5.6 Audio Rate-Matching Algorithms                                                                                    |

|    |     | 5.5.8 Multiple Simultaneous A2DP Audio                                                                                  |

|    |     | Streams24                                                                                                               |

|    |     | 5.5.9 Burst Buffer Operation                                                                                            |

|    | 5.6 | Adaptive Frequency Hopping24                                                                                            |

|    | 5.7 | Advanced Bluetooth/WLAN Coexistence 25                                                                                  |

|    | 5.8           | Fast Connection (Interlaced Page and Inquiry Scans) | 25 |

|----|---------------|-----------------------------------------------------|----|

| 6. |               | roprocessor and Memory Unit for etooth              | 26 |

|    | 6.1           | RAM, ROM, and Patch Memory                          |    |

|    | 6.2           |                                                     |    |

| 7. | Blue          | etooth Peripheral Transport Unit                    | 27 |

| •  | 7.1           | SPI Interface                                       |    |

|    | 7.2           | SPI/UART Transport Detection                        |    |

|    | 7.3           | PCM Interface                                       |    |

|    | 7.5           | 7.3.1 Slot Mapping                                  |    |

|    |               | 7.3.2 Frame Synchronization                         | 28 |

|    |               | 7.3.3 Data Formatting                               |    |

|    |               | 7.3.4 Wideband Speech Support                       |    |

|    |               | 7.3.6 PCM Interface Timing                          |    |

|    | 7.4           | USB Interface                                       |    |

|    |               | 7.4.1 Features                                      |    |

|    |               | 7.4.2 Operation                                     |    |

|    |               | 7.4.3 USB Hub and UHE Support                       |    |

|    | 7.5           | 7.4.4 USB Full-Speed Timing                         |    |

|    | 7.5           | UART Interface                                      |    |

|    | 7.6           | I <sup>2</sup> S Interface                          |    |

| 8. | WL            | AN Global Functions                                 |    |

|    | 8.1           | WLAN CPU and Memory Subsystem                       | 41 |

|    | 8.2           | One-Time Programmable Memory                        |    |

|    | 8.3           | GPIO Interface                                      |    |

|    | 8.4           | External Coexistence Interface                      |    |

|    | 8.5           | UART Interface                                      |    |

|    | 8.6           | JTAG Interface                                      |    |

|    | 8.7           | SPROM Interface (FCBGA Package only)                |    |

| 9. | WL            | AN Host Interfaces                                  | 43 |

|    | 9.1           | SDIO v3.0                                           | 43 |

|    |               | 9.1.1 SDIO Pins                                     | 43 |

|    | 9.2           | PCI Express Interface (FCBGA Package Only)          |    |

|    |               | 9.2.1 Transaction Layer Interface                   |    |

|    |               | 9.2.2 Data Link Layer                               |    |

|    |               | 9.2.4 Logical Subblock                              |    |

|    |               | 9.2.5 Scrambler/Descrambler                         | 46 |

|    |               | 9.2.6 8B/10B Encoder/Decoder                        |    |

|    |               | 9.2.7 Elastic FIFO                                  |    |

|    |               | 9.2.9 Configuration Space                           |    |

|    |               |                                                     |    |

| 10 | \ <b>\</b> /: | eless LAN MAC and PHY                               | 47 |

| 10.1.1 PSM                                                            | 48                     | Specifications                                      | 99    |

|-----------------------------------------------------------------------|------------------------|-----------------------------------------------------|-------|

| 10.1.2 WEP                                                            |                        | 15.7 General Spurious Emissions Specifications .    | 100   |

| 10.1.3 TXE<br>10.1.4 RXE                                              |                        | 16.Internal Regulator Electrical Specification      | s 100 |

| 10.1.5 IFS                                                            |                        | 16.1 Core Buck Switching Regulator                  |       |

| 10.1.6 TSF                                                            | 49                     | 16.2 3.3V LDO (LDO3P3)                              |       |

| 10.1.7 NAV                                                            |                        | 16.3 2.5V LDO (BTLDO2P5)                            |       |

| 10.2 IEEE 802.11ac PHY                                                | 50                     | 16.4 CLDO                                           |       |

| 1. WLAN Radio Subsystem                                               | 52                     | 16.5 LNLDO                                          |       |

| 11.1 Receiver Path                                                    |                        |                                                     |       |

| 11.2 Transmit Path                                                    |                        | 17. System Power Consumption                        | 105   |

| 11.3 Calibration                                                      |                        | 17.1 WLAN Current Consumption                       | 10    |

|                                                                       |                        | 17.2 Bluetooth Current Consumption                  | 107   |

| 2. Pinout and Signal Descriptions.                                    |                        | 18.Interface Timing and AC Characteristics          | 108   |

| 12.1 Ball Maps                                                        |                        | 18.1 SDIO Timing                                    |       |

| 12.2 Pin Lists                                                        |                        | 18.1.1 SDIO Default Mode Timing                     |       |

| 12.3 Signal Descriptions                                              |                        | 18.1.2 SDIO High-Speed Mode Timing                  |       |

| 12.4 WLAN GPIO Signals and Strappi<br>12.4.1 Multiplexed Bluetooth GP |                        | 18.1.3 SDIO Bus Timing Specifications in SI Modes   |       |

| 12.5 GPIO/SDIO Alternative Signal Fu                                  | unctions 75            | 18.1.4 SDIO Bus Timing Specifications in            |       |

| 12.6 I/O States                                                       | 76                     | DDR50 Mode                                          |       |

| 3.DC Characteristics                                                  | 80                     | 18.2 PCI Express Interface Parameters               |       |

| 13.1 Absolute Maximum Ratings                                         |                        | 18.3 JTAG Timing                                    | 117   |

|                                                                       |                        | 19. Power-Up Sequence and Timing                    | 118   |

| 13.2 Environmental Ratings                                            |                        | 19.1 Sequencing of Reset and Regulator Control      |       |

| 13.3 Electrostatic Discharge Specifica                                |                        | Signals                                             |       |

| 13.4 Recommended Operating Condit Characteristics                     |                        | 19.1.1 Description of Control Signals               |       |

|                                                                       |                        | 19.1.2 Control Signal Timing Diagrams               |       |

| 4. Bluetooth RF Specifications                                        | 83                     | 20. Package Information                             | 121   |

| 5.WLAN RF Specifications                                              | 89                     | 20.1 Package Thermal Characteristics                | 12    |

| 15.1 Introduction                                                     | 89                     | 20.2 Junction Temperature Estimation and $PSI_{JT}$ |       |

| 15.2 All WLAN specifications are spec                                 | cified at the RF port, | Versus THETA <sub>JC</sub>                          |       |

| inless otherwise specified.2.4 GHz Band                               |                        | 20.3 Environmental Characteristics                  | 12    |

| Specifications                                                        | 89                     | 21. Mechanical Information                          | 122   |

| 15.3 WLAN 2.4 GHz Receiver Perforn Specifications                     |                        | 22. Ordering Information                            | . 127 |

| 15.4 WLAN 2.4 GHz Transmitter Perfo                                   | ormance                | 23. IoT Resources                                   | 128   |

| Specifications                                                        | 94                     | 23.1 References                                     | 128   |

| 15.5 WLAN 5 GHz Receiver Performa                                     |                        | Document History Page                               |       |

| Specifications                                                        |                        | Sales, Solutions, and Legal Information             |       |

| 15.6 WLAN 5 GHz Transmitter Perform                                   | mance                  |                                                     |       |

### 1. Overview

#### 1.1 Overview

The Cypress CYW4339 single-chip device provides the highest level of integration for IoT applications or handheld wireless system, with integrated IEEE 802.11 a/b/g/n/ac MAC/baseband/radio, Bluetooth 4.1 + enhanced data rate (EDR).

It provides a small form-factor solution with minimal external components to drive down cost for mass volumes and allows for handheld device flexibility in size, form, and function. Comprehensive power management circuitry and software ensure the system can meet the needs of highly mobile devices that require minimal power consumption and reliable operation.

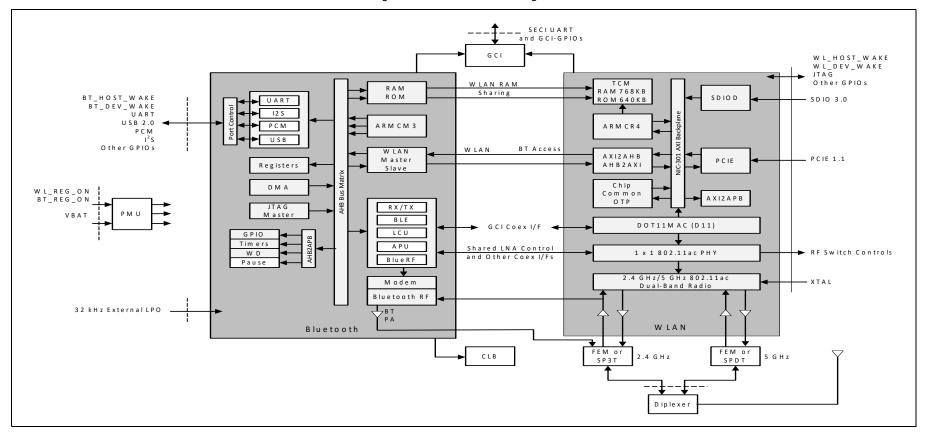

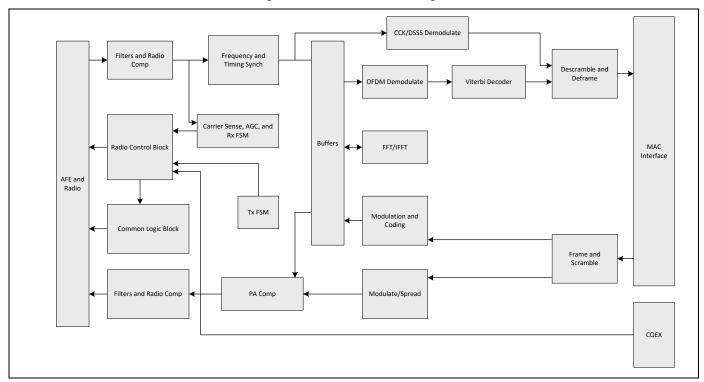

The following figure shows the interconnect of all the major physical blocks in the CYW4339 and their associated external interfaces, which are described in greater detail in the following sections.

Figure 1. CYW4339 Block Diagram

Document No. 002-14784 Rev. \*I

### 1.2 Features

The CYW4339 supports the following features:

- IEEE 802.11a/b/g/n/ac dual-band radio with virtual-simultaneous dual-band operation

- Bluetooth v4.1 + EDR with integrated Class 1 PA

- Concurrent Bluetooth, and WLAN operation

- On-chip WLAN driver execution capable of supporting IEEE 802.11 functionality

- WLAN host interface options:

- □ SDIO v3.0 (1-bit/4-bit)—up to 208 MHz clock rate in SDR104 mode

- BT host digital interface (which can be used concurrently with the above interfaces):

- □ UART (up to 4 Mbps)

- BT supports full-speed USB version 1.1 for FCBGA package.

- ECI—enhanced coexistence support, ability to coordinate BT SCO transmissions around WLAN receptions

- I<sup>2</sup>S/PCM for BT audio

- HCI high-speed UART (H4, H4+, H5) transport support

- Wideband speech support (16 bits linear data, MSB first, left justified at 4K samples/s for transparent air coding, both through I<sup>2</sup>S and PCM interface)

- Bluetooth SmartAudio<sup>®</sup> technology improves voice and music quality to headsets

- Bluetooth low-power inquiry and page scan

- Bluetooth Low Energy (BLE) support

- Bluetooth Packet Loss Concealment (PLC)

- Bluetooth Wide Band Speech (WBS)

- Audio rate-matching algorithms

- Multiple simultaneous A2DP audio streams

### 1.3 Standards Compliance

The CYW4339 supports the following standards:

- Bluetooth 2.1 + EDR

- Bluetooth 3.0

- Bluetooth 4.1 (Bluetooth Low Energy)

- IEEE802.11ac single-stream mandatory and optional requirements for 20 MHz, 40 MHz, and 80 MHz channels

- IEEE 802.11n—Handheld Device Class (Section 11)

- IEEE 802.11a

- IEEE 802.11b

- IEEE 802.11g

- IEEE 802.11d

- IEEE 802.11h

- IEEE 802.11i

- Security:

- □ WEP

- □ WPA<sup>™</sup> Personal

- □ WPA2<sup>™</sup> Personal

- □ WMM

- □ WMM-PS (U-APSD)

- □ WMM-SA

- □ AES (Hardware Accelerator)

- □ TKIP (HW Accelerator)

- □ CKIP (SW Support)

- Proprietary Protocols:

- □ CCXv2

- □ CCXv3

- □ CCXv4

- □ CCXv5

- IEEE 802.15.2 Coexistence Compliance—on silicon solution compliant with IEEE 3 wire requirements

The CYW4339 will support the following future drafts/standards:

- IEEE 802.11r—Fast Roaming (between APs)

- IEEE 802.11w—Secure Management Frames

- IEEE 802.11 Extensions:

- ☐ IEEE 802.11e QoS Enhancements (as per the WMM<sup>®</sup> specification is already supported)

- □ IEEE 802.11h 5 GHz Extensions

- □ IEEE 802.11i MAC Enhancements

- □ IEEE 802.11k Radio Resource Measurement

### 2. Power Supplies and Power Management

### 2.1 Power Supply Topology

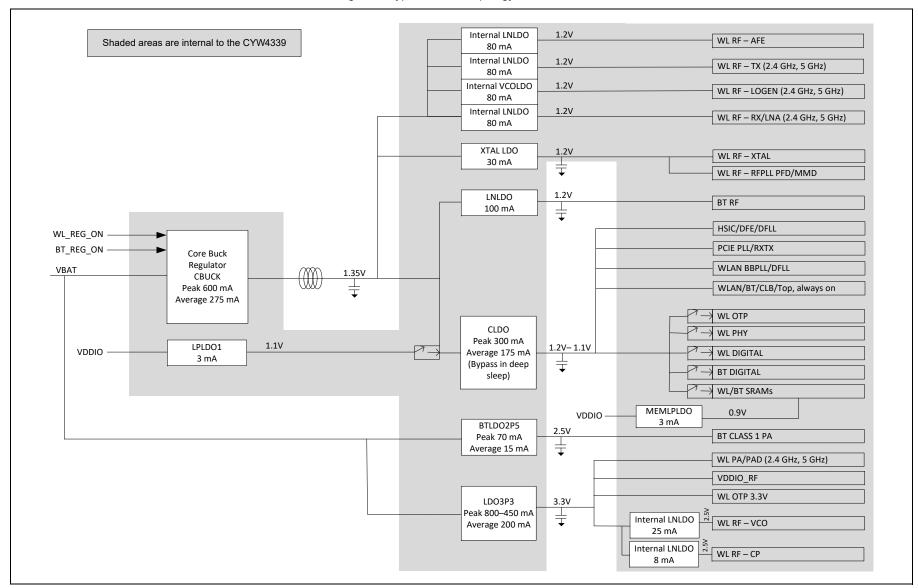

One buck regulator, multiple LDO regulators, and a power management unit (PMU) are integrated into the CYW4339. All regulators are programmable via the PMU. These blocks simplify power supply design for Bluetooth and WLAN functions in embedded designs.

A single VBAT (3.0V to 5.25V DC maximum) and VIO supply (1.8V to 3.3V) can be used, with all additional voltages being provided by the regulators in the CYW4339.

Two control signals, BT\_REG\_ON and WL\_REG\_ON, are used to power up the regulators and take the respective section out of reset. The CBUCK CLDO and LNLDO power up when any of the reset signals are deasserted. All regulators are powered down only when both BT\_REG\_ON and WL\_REG\_ON are deasserted. The CLDO and LNLDO may be turned off and on based on the dynamic demands of the digital baseband.

The CYW4339 allows for an extremely low power-consumption mode by completely shutting down the CBUCK, CLDO, and LNLDO regulators. When in this state, LPLDO1 and LPLDO2 (which are low-power linear regulators that are supplied by the system VIO supply) provide the CYW4339 with all the voltages it requires, further reducing leakage currents.

#### 2.2 PMU Features

- VBAT to 1.35V (275 mA nominal, 600 mA maximum) Core-Buck (CBUCK) switching regulator

- VBAT to 3.3V (200 mA nominal, 450 mA maximum) LDO3P3

- VBAT to 2.5V (15 mA nominal, 70 mA maximum) BTLDO2P5

- 1.35V to 1.2V (100 mA nominal, 150 mA maximum) LNLDO

- 1.35V to 1.2V (175 mA nominal, 300 mA maximum) CLDO with bypass mode for deep-sleep

- Additional internal LDOs (not externally accessible)

The following figure shows the regulators and a typical power topology.

Figure 2. Typical Power Topology for CYW4339

Document No. 002-14784 Rev. \*I

#### 2.3 WLAN Power Management

The CYW4339 has been designed with the stringent power consumption requirements of mobile devices in mind. All areas of the chip design are optimized to minimize power consumption. Silicon processes and cell libraries were chosen to reduce leakage current and supply voltages. Additionally, the CYW4339 integrated RAM is a high Vt memory with dynamic clock control. The dominant supply current consumed by the RAM is leakage current only. Additionally, the CYW4339 includes an advanced WLAN power management unit (PMU) sequencer. The PMU sequencer provides significant power savings by putting the CYW4339 into various power management states appropriate to the current environment and activities that are being performed. The power management unit enables and disables internal regulators, switches, and other blocks based on a computation of the required resources and a table that describes the relationship between resources and the time needed to enable and disable them. Power-up sequences are fully programmable. Configurable, free-running counters (running at the 32.768 kHz LPO clock frequency) in the PMU sequencer are used to turn on and turn off individual regulators and power switches. Clock speeds are dynamically changed (or gated altogether) for the current mode. Slower clock speeds are used wherever possible.

The CYW4339 WLAN power states are described as follows:

- Active mode—All WLAN blocks in the CYW4339 are powered up and fully functional with active carrier sensing and frame transmission and receiving. All required regulators are enabled and put in the most efficient mode based on the load current. Clock speeds are dynamically adjusted by the PMU sequencer.

- Doze mode—The radio, analog domains, and most of the linear regulators are powered down. The rest of the CYW4339 remains powered up in an IDLE state. All main clocks (PLL, crystal oscillator or TCXO) are shut down to reduce active power consumption to the minimum. The 32.768 kHz LPO clock is available only for the PMU sequencer. This condition is necessary to allow the PMU sequencer to wake up the chip and transition to Active mode. In Doze mode, the primary power consumed is due to leakage current.

- Deep-sleep mode—Most of the chip, including both analog and digital domains, and most of the regulators are powered off. Logic states in the digital core are saved and preserved into a retention memory in the always-ON domain before the digital core is powered off. Upon a wake-up event triggered by the PMU timers, an external interrupt, or a host resume through the SDIO bus, logic states in the digital core are restored to their pre-deep-sleep settings to avoid lengthy HW reinitialization.

- Power-down mode—The CYW4339 is effectively powered off by shutting down all internal regulators. The chip is brought out of this mode by external logic reenabling the internal regulators.

### 2.4 PMU Sequencing

The PMU sequencer is responsible for minimizing system power consumption. It enables and disables various system resources based on a computation of the required resources and a table that describes the relationship between resources and the time needed to enable and disable them.

Resource requests may come from several sources: clock requests from cores, the minimum resources defined in the ResourceMin register, and the resources requested by any active resource request timers. The PMU sequencer maps clock requests into a set of resources required to produce the requested clocks.

Each resource is in one of four states (enabled, disabled, transition\_on, and transition\_off) and has a timer that contains 0 when the resource is enabled or disabled and a nonzero value in the transition states. The timer is loaded with the time\_on or time\_off value of the resource when the PMU determines that the resource must be enabled or disabled. That timer decrements on each 32.768 kHz PMU clock. When it reaches 0, the state changes from transition\_off to disabled or transition\_on to enabled. If the time\_on value is 0, the resource can go immediately from disabled to enabled. Similarly, a time\_off value of 0 indicates that the resource can go immediately from enabled to disabled. The terms enable sequence and disable sequence refer to either the immediate transition or the timer load-decrement sequence.

During each clock cycle, the PMU sequencer performs the following actions:

- Computes the required resource set based on requests and the resource dependency table.

- Decrements all timers whose values are non zero. If a timer reaches 0, the PMU clears the Resource Pending bit for the resource and inverts the Resource State bit.

- Compares the request with the current resource status and determines which resources must be enabled or disabled.

- Initiates a disable sequence for each resource that is enabled, no longer being requested, and has no powered up dependents.

- Initiates an enable sequence for each resource that is disabled, is being requested, and has all of its dependencies enabled.

### 2.5 Power-Off Shutdown

The CYW4339 provides a low-power shutdown feature that allows the device to be turned off while the host, and any other devices in the system, remain operational. When the CYW4339 is not needed in the system, VDDIO\_RF and VDDC are shut down while VDDIO remains powered. This allows the CYW4339 to be effectively off while keeping the I/O pins powered so that they do not draw extra current from any other devices connected to the I/O.

During a low-power shut-down state, the provided VDDIO remains applied to the CYW4339, all outputs are tristated, and most input signals are disabled. Input voltages must remain within the limits defined for normal operation. This is done to prevent current paths or create loading on any digital signals in the system, and enables the CYW4339 to be fully integrated in an embedded device and take full advantage of the lowest power-savings modes.

When the CYW4339 is powered on from this state, it is the same as a normal power-up, and the device does not retain any information about its state from before it was powered down.

#### 2.6 Power-Up/Power-Down/Reset Circuits

The CYW4339 has two signals (see Table 1) that enable or disable the Bluetooth and WLAN circuits and the internal regulator blocks, allowing the host to control power consumption. For timing diagrams of these signals and the required power-up sequences, see Power-Up Sequence and Timing on page 118.

Table 1. Power-Up/Power-Down/Reset Control Signals

| Signal    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WL_REG_ON | This signal is used by the PMU (with BT_REG_ON) to power up the WLAN section. It is also OR-gated with the BT_REG_ON input to control the internal CYW4339 regulators. When this pin is high, the regulators are enabled and the WLAN section is out of reset. When this pin is low, the WLAN section is in reset. If BT_REG_ON and WL_REG_ON are both low, the regulators are disabled. This pin has an internal 200 k $\Omega$ pull-down resistor that is enabled by default. It can be disabled through programming. |

| BT_REG_ON | This signal is used by the PMU (with WL_REG_ON) to decide whether or not to power down the internal CYW4339 regulators. If BT_REG_ON and WL_REG_ON are low, the regulators will be disabled. This pin has an internal 200 k $\Omega$ pull-down resistor that is enabled by default. It can be disabled through programming.                                                                                                                                                                                             |

### 3. Frequency References

An external crystal is used for generating all radio frequencies and normal operation clocking. As an alternative, an external frequency reference may be used. In addition, a low-power oscillator (LPO) is provided for lower power mode timing.

#### 3.1 Crystal Interface and Clock Generation

The CYW4339 can use an external crystal to provide a frequency reference. The recommended configuration for the crystal oscillator, including all external components, is shown in Figure 3. Consult the reference schematics for the latest configuration and recommended components.

WRF\_XTAL\_IN

C\*

X ohms\*

WRF\_XTAL\_OUT

\* Values determined by crystal drive level. See reference schematics for details.

Figure 3. Recommended Oscillator Configuration

A fractional-N synthesizer in the CYW4339 generates the radio frequencies, clocks, and data/packet timing, enabling the CYW4339 to operate using a wide selection of frequency references.

For SDIO applications, the recommended default frequency reference is a 37.4 MHz crystal. The signal characteristics for the crystal interface are listed in Table 2.

**Note:** Although the fractional-N synthesizer can support alternative reference frequencies, frequencies other than the default require support to be added in the driver, plus additional extensive system testing. Contact Cypress for details.

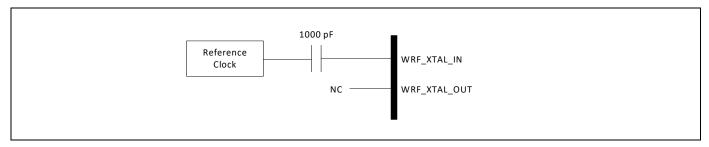

### 3.2 External Frequency Reference

As an alternative to a crystal, an external precision frequency reference can be used. The recommended default frequency is 37.4 MHz. This must meet the phase noise requirements listed in Table 2.

If used, the external clock should be connected to the WRF\_XTAL\_IN pin through an external 1000 pF coupling capacitor, as shown in Figure 4. The internal clock buffer connected to this pin will be turned off when the CYW4339 goes into sleep mode. When the clock buffer turns on and off, there will be a small impedance variation. Power must be supplied to the WRF\_XTAL\_BUCK\_VDD1P5 pin.

Figure 4. Recommended Circuit to Use with an External Reference Clock

Table 2. Crystal Oscillator and External Clock—Requirements and Performance

| Parameter                                                                                  | Conditions/Notes                                                                      |      | Crystal <sup>1</sup> |           |          | External Frequency<br>Reference <sup>2 3</sup> |                     |                   |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------|----------------------|-----------|----------|------------------------------------------------|---------------------|-------------------|

|                                                                                            |                                                                                       | Min. | Тур.                 | Max.      | Min.     | Тур.                                           | Max.                | Units             |

| Frequency                                                                                  | 2.4 GHz and 5 GHz bands,<br>IEEE 802.11ac operation                                   | 35   | 37.4                 | 38.4      | _        | 37.4                                           | _                   | MHz               |

| Frequency                                                                                  | 5 GHz band, IEEE 802.11n operation only                                               | 19   | 37.4                 | 38.4      | 35       | 37.4                                           | 38.4                | MHz               |

| Frequency                                                                                  | 2.4 GHz band IEEE 802.11n operation, and both bands legacy 802.11a/b/g operation only |      | Rang                 | ges betwe | en 19 MF | Iz and 38                                      | .4 MHz <sup>4</sup> |                   |

| Frequency tolerance over the lifetime of the equipment, including temperature <sup>5</sup> | Without trimming                                                                      | -20  | _                    | 20        | -20      | _                                              | 20                  | ppm               |

| Crystal load capacitance                                                                   | -                                                                                     | _    | 12                   | _         | _        | _                                              | _                   | pF                |

| ESR                                                                                        | -                                                                                     | _    | -                    | 60        | _        | _                                              | _                   | Ω                 |

| Drive level                                                                                | External crystal must be able to tolerate this drive level.                           | 200  | -                    | -         | _        | -                                              | -                   | μW                |

| Input impedance                                                                            | Resistive                                                                             | _    | -                    | -         | 30k      | 100k                                           | -                   | Ω                 |

| (WRF_XTAL_IN)                                                                              | Capacitive                                                                            | _    | _                    | 7.5       | -        | -                                              | 7.5                 | pF                |

| WRF_XTAL_IN input low level                                                                | DC-coupled digital signal                                                             | -    | -                    | _         | 0        | -                                              | 0.2                 | V                 |

| WRF_XTAL_IN input high level                                                               | DC-coupled digital signal                                                             | -    | -                    | _         | 1.0      | -                                              | 1.26                | V                 |

| WRF_XTAL_IN input voltage (see Figure 4)                                                   | AC-coupled analog signal                                                              | -    | _                    | _         | 1000     | -                                              | 1200                | mV <sub>p-p</sub> |

| Duty cycle                                                                                 | 37.4 MHz clock                                                                        | -    | -                    | _         | 40       | 50                                             | 60                  | %                 |

| Phase noise <sup>6</sup>                                                                   | 37.4 MHz clock at 10 kHz offset                                                       | -    | -                    | -         | _        | _                                              | -129                | dBc/Hz            |

| (IEEE 802.11b/g)                                                                           | 37.4 MHz clock at 100 kHz offset                                                      | -    | -                    | -         | _        | _                                              | -136                | dBc/Hz            |

| Phase noise <sup>6</sup>                                                                   | 37.4 MHz clock at 10 kHz offset                                                       | _    | -                    | _         | _        | _                                              | -137                | dBc/Hz            |

| (IEEE 802.11a)                                                                             | 37.4 MHz clock at 100 kHz offset                                                      | -    | _                    | _         | _        | _                                              | -144                | dBc/Hz            |

Table 2. Crystal Oscillator and External Clock—Requirements and Performance (Cont.)

| Parameter                | Conditions/Notes                 |      | Crystal <sup>1</sup> |      |      | External Frequency<br>Reference <sup>2 3</sup> |      |        |

|--------------------------|----------------------------------|------|----------------------|------|------|------------------------------------------------|------|--------|

|                          |                                  | Min. | Тур.                 | Max. | Min. | Тур.                                           | Max. | Units  |

| Phase noise <sup>6</sup> | 37.4 MHz clock at 10 kHz offset  | -    | -                    | _    | -    | _                                              | -134 | dBc/Hz |

| (IEEE 802.11n, 2.4 GHz)  | 37.4 MHz clock at 100 kHz offset | _    | _                    | _    | -    | _                                              | -141 | dBc/Hz |

| Phase noise <sup>6</sup> | 37.4 MHz clock at 10 kHz offset  | -    | -                    | -    | -    | -                                              | -142 | dBc/Hz |

| (IEEE 802.11n, 5 GHz)    | 37.4 MHz clock at 100 kHz offset | _    | _                    | _    | -    | _                                              | -149 | dBc/Hz |

| Phase noise <sup>6</sup> | 37.4 MHz clock at 10 kHz offset  | -    | _                    | _    | -    | -                                              | -148 | dBc/Hz |

| (IEEE 802.11ac, 5 GHz)   | 37.4 MHz clock at 100 kHz offset | -    | -                    | -    | -    | -                                              | -155 | dBc/Hz |

<sup>1. (</sup>Crystal) Use WRF XTAL IN and WRF XTAL OUT.

- 3. For a clock reference other than 37.4 MHz, 20 × log10(f/37.4) dB should be added to the limits, where f = the reference clock frequency in MHz.

- 4. The frequency step size is approximately 80 Hz.

- 5. It is the responsibility of the equipment designer to select oscillator components that comply with these specifications.

- 6. Assumes that external clock has a flat phase-noise response above 100 kHz.

#### 3.3 Frequency Selection

Any frequency within the ranges specified for the crystal and TCXO reference may be used. These include not only the standard mobile platform reference frequencies of 19.2, 19.8, 24, 26, 33.6, 37.4, and 38.4 MHz, but also other frequencies in this range with an approximate resolution of 80 Hz. The CYW4339 must have the reference frequency set correctly in order for any of the UART or PCM interfaces to function correctly, since all bit timing is derived from the reference frequency.

**Note:** The fractional-N synthesizer can support many reference frequencies. However, frequencies other than the default require support to be added in the driver plus additional, extensive system testing. Contact Cypress for details.

The reference frequency for the CYW4339 may be set in the following ways:

- Set the xtalfreq=xxxxx parameter in the nvram.txt file (used to load the driver) to correctly match the crystal frequency.

- Autodetect any of the standard handset reference frequencies using an external LPO clock.

For applications such as handsets and portable smart communication devices, where the reference frequency is one of the standard frequencies commonly used, the CYW4339 automatically detects the reference frequency and programs itself to the correct reference frequency. In order for automatic frequency detection to work correctly, the CYW4339 must have a valid and stable 32.768 kHz LPO clock that meets the requirements listed in Table 3 and is present during power-on reset.

<sup>2.</sup> See External Frequency Reference for alternative connection methods.

### 3.4 External 32.768 kHz Low-Power Oscillator

The CYW4339 uses a secondary low-frequency clock for low-power-mode timing. Either the internal low-precision LPO or an external 32.768 kHz precision oscillator is required. The internal LPO frequency range is approximately 33 kHz ± 30% over process, voltage, and temperature, which is adequate for some applications. However, one trade-off caused by this wide LPO tolerance is a small current consumption increase during power save mode that is incurred by the need to wake up earlier to avoid missing beacons. Whenever possible, the preferred approach is to use a precision external 32.768 kHz clock that meets the requirements listed in Table 3.

Table 3. External 32.768 kHz Sleep Clock Specifications

| Parameter                              | LPO Clock                | Units   |

|----------------------------------------|--------------------------|---------|

| Nominal input frequency                | 32.768                   | kHz     |

| Frequency accuracy                     | ±200                     | ppm     |

| Duty cycle                             | 30–70                    | %       |

| Input signal amplitude                 | 200–1800                 | mV, p-p |

| Signal type                            | Square-wave or sine-wave | _       |

| Input impedance <sup>1</sup>           | >100k<br><5              | Ω<br>pF |

| Clock jitter (during initial start-up) | <10,000                  | ppm     |

<sup>1.</sup> When power is applied or switched off.

### 4. Bluetooth Subsystem Overview

The Cypress CYW4339 is a Bluetooth 4.1 + EDR-compliant, baseband processor/2.4 GHz transceiver. It features the highest level of integration and eliminates all critical external components, thus minimizing the footprint, power consumption, and system cost of a Bluetooth plus Wi-Fi system.

The CYW4339 is the optimal solution for any Bluetooth voice and/or data application. The Bluetooth subsystem presents a standard Host Controller Interface (HCI) via a high-speed UART and PCM for audio. The CYW4339 incorporates all Bluetooth 4.1 features including Secure Simple Pairing, Sniff Subrating, and Encryption Pause and Resume.

The CYW4339 Bluetooth radio transceiver provides enhanced radio performance to meet the most stringent mobile phone temperature applications and the tightest integration into handsets and portable devices. It is fully compatible with any of the standard TCXO frequencies and provides full radio compatibility to operate simultaneously with GPS, WLAN, and cellular radios.

The Bluetooth transmitter also features a Class 1 power amplifier with Class 2 capability.

#### 4.1 Features

### Major Bluetooth features of the CYW4339 include:

- Supports key features of upcoming Bluetooth standards

- Fully supports Bluetooth Core Specification version 4.1 + (Enhanced Data Rate) EDR features:

- ☐ Adaptive Frequency Hopping (AFH)

- Quality of Service (QoS)

- Extended Synchronous Connections (eSCO)—Voice Connections

- □ Fast Connect (interlaced page and inquiry scans)

- Secure Simple Pairing (SSP)

- □ Sniff Subrating (SSR)

- □ Encryption Pause Resume (EPR)

- Extended Inquiry Response (EIR)

- □ Link Supervision Timeout (LST)

- UART baud rates up to 4 Mbps

- Supports Bluetooth 4.1 packet types

- Supports maximum Bluetooth data rates over HCI UART

- BT supports full-speed USB version 1.1 in the FCBGA package

- Multipoint operation with up to seven active slaves

- Maximum of seven simultaneous active ACL links

- Maximum of three simultaneous active SCO and eSCO connections with scatternet support

- Trigger Cypress fast connect (TBFC)

- Narrowband and wideband packet loss concealment

- Scatternet operation with up to four active piconets with background scan and support for scatter mode

- High-speed HCI UART transport support with low-power out-of-band BT\_DEV\_WAKE and BT\_HOST\_WAKE signaling (see Host Controller Power Management )

- Channel quality driven data rate and packet type selection

- Standard Bluetooth test modes

- Extended radio and production test mode features

- Full support for power savings modes

- Bluetooth clock request

- Bluetooth standard sniff

- Deep-sleep modes and software regulator shutdown

- TCXO input and autodetection of all standard handset clock frequencies. Also supports a low-power crystal, which can be used during power save mode for better timing accuracy.

#### 4.2 Bluetooth Radio

The CYW4339 has an integrated radio transceiver that has been optimized for use in 2.4 GHz Bluetooth wireless systems. It has been designed to provide low-power, low-cost, robust communications for applications operating in the globally available 2.4 GHz unlicensed ISM band. It is fully compliant with the Bluetooth Radio Specification and EDR specification and meets or exceeds the requirements to provide the highest communication link quality.

#### 4.2.1 Transmit

The CYW4339 features a fully integrated zero-IF transmitter. The baseband transmit data is GFSK-modulated in the modem block and upconverted to the 2.4 GHz ISM band in the transmitter path. The transmitter path performs signal filtering, I/Q upconversion, output power amplification, and RF filtering. The transmitter path also incorporates  $\pi$ /4-DQPSK and 8-DPSK modulations for 2 Mbps and 3 Mbps EDR support, respectively. The transmitter section is compatible to the Bluetooth Low Energy specification. The transmitter PA bias can also be adjusted to provide Bluetooth Class 1 or Class 2 operation.

#### 4.2.2 Digital Modulator

The digital modulator performs the data modulation and filtering required for the GFSK,  $\pi$ /4-DQPSK, and 8-DPSK signal. The fully digital modulator minimizes any frequency drift or anomalies in the modulation characteristics of the transmitted signal and is much more stable than direct VCO modulation schemes.

#### 4.2.3 Digital Demodulator and Bit Synchronizer

The digital demodulator and bit synchronizer take the low-IF received signal and perform an optimal frequency tracking and bit-synchronization algorithm.

### 4.2.4 Power Amplifier

The fully integrated PA supports Class 1 or Class 2 output using a highly linearized, temperature-compensated design. This provides greater flexibility in front-end matching and filtering. Due to the linear nature of the PA combined with some integrated filtering, external filtering is required to meet the Bluetooth and regulatory harmonic and spurious requirements. For integrated handset applications in which Bluetooth is integrated next to the cellular radio, external filtering can be applied to achieve near-thermal-noise levels for spurious and radiated noise emissions. The transmitter features a sophisticated on-chip transmit signal strength indicator (TSSI) block to keep the absolute output power variation within a tight range across process, voltage, and temperature.

### 4.2.5 Receiver

The receiver path uses a low-IF scheme to downconvert the received signal for demodulation in the digital demodulator and bit synchronizer. The receiver path provides a high degree of linearity, an extended dynamic range, and high-order on-chip channel filtering to ensure reliable operation in the noisy 2.4 GHz ISM band. The front-end topology, with built-in out-of-band attenuation, enables the CYW4339 to be used in most applications with minimal off-chip filtering. For integrated handset operation, in which the Bluetooth function is integrated close to the cellular transmitter, external filtering is required to eliminate the desensitization of the receiver by the cellular transmit signal.

#### 4.2.6 Digital Demodulator and Bit Synchronizer

The digital demodulator and bit synchronizer take the low-IF received signal and perform an optimal frequency tracking and bit synchronization algorithm.

#### 4.2.7 Receiver Signal Strength Indicator

The radio portion of the CYW4339 provides a Receiver Signal Strength Indicator (RSSI) signal to the baseband, so that the controller can determine whether the transmitter should increase or decrease its output power.

#### 4.2.8 Local Oscillator Generation

Local Oscillator (LO) generation provides fast frequency hopping (1600 hops/second) across the 79 maximum available channels. The LO generation subblock employs an architecture for high immunity to LO pulling during PA operation. The CYW4339 uses an internal RF and IF loop filter.

#### 4.2.9 Calibration

The CYW4339 radio transceiver features an automated calibration scheme that is fully self contained in the radio. No user interaction is required during normal operation or during manufacturing to provide the optimal performance. Calibration optimizes the performance of all the major blocks within the radio to within 2% of optimal conditions, including gain and phase characteristics of filters, matching between key components, and key gain blocks. This takes into account process variation and temperature variation. Calibration occurs during normal operation during the settling time of the hops and calibrates for temperature variations as the device cools and heats during normal operation in its environment.

#### 5. Bluetooth Baseband Core

The Bluetooth Baseband Core (BBC) implements all of the time critical functions required for high-performance Bluetooth operation. The BBC manages the buffering, segmentation, and routing of data for all connections. It also buffers data that passes through it, handles data flow control, schedules SCO/ACLTX/RX transactions, monitors Bluetooth slot usage, optimally segments and packages data into baseband packets, manages connection status indicators, and composes and decodes HCI packets. In addition to these functions, it independently handles HCI event types, and HCI command types.

The following transmit and receive functions are also implemented in the BBC hardware to increase reliability and security of the TX/RX data:

- Symbol timing recovery, data deframing, forward error correction (FEC), header error control (HEC), cyclic redundancy check (CRC), data decryption, and data dewhitening in the receiver.

- Data framing, FEC generation, HEC generation, CRC generation, key generation, data encryption, and data whitening in the transmitter.

#### 5.1 Bluetooth 4.1 Features

The BBC supports all Bluetooth 4.1 features, with the following benefits:

- Dual-mode bluetooth Low Energy (BT and BLE operation)

- Extended Inquiry Response (EIR): Shortens the time to retrieve the device name, specific profile, and operating mode.

- Encryption Pause Resume (EPR): Enables the use of Bluetooth technology in a much more secure environment.

- Sniff Subrating (SSR): Optimizes power consumption for low duty cycle asymmetric data flow, which subsequently extends battery life.

- Secure Simple Pairing (SSP): Reduces the number of steps for connecting two devices, with minimal or no user interaction required.

- Link Supervision Time Out (LSTO): Additional commands added to HCI and Link Management Protocol (LMP) for improved link time-out supervision.

- QoS enhancements: Changes to data traffic control, which results in better link performance. Audio, human interface device (HID), bulk traffic, SCO, and enhanced SCO (eSCO) are improved with the erroneous data (ED) and packet boundary flag (PBF) enhancements.

#### 5.2 Bluetooth Low Energy

The CYW4339 supports the Bluetooth Low Energy operating mode.

### 5.3 Link Control Layer

The link control layer is part of the Bluetooth link control functions that are implemented in dedicated logic in the link control unit (LCU). This layer consists of the command controller that takes commands from the software, and other controllers that are activated or configured by the command controller to perform the link control tasks. Each task performs a different state in the Bluetooth Link Controller.

- Major states:

- Standby

- □ Connection

- Substates:

- □ Page

- □ Page Scan

- Inquiry

- Inquiry Scan

- □ Sniff

### 5.4 Test Mode Support

The CYW4339 fully supports Bluetooth Test mode as described in Part I:1 of the *Specification of the Bluetooth System Version 3.0*. This includes the transmitter tests, normal and delayed loopback tests, and reduced hopping sequence.

In addition to the standard Bluetooth Test Mode, the CYW4339 also supports enhanced testing features to simplify RF debugging, qualification, and type-approval testing. These features include:

- Fixed-frequency carrier-wave (unmodulated) transmission

- □ Simplifies some type-approval measurements (Japan)

- Aids in transmitter performance analysis

- Fixed-frequency constant-receiver mode

- □ Receiver output directed to I/O pin

- Allows for direct BER measurements using standard RF test equipment

- □ Facilitates spurious emissions testing for receive mode

- Fixed frequency constant transmission

- □ Eight-bit fixed pattern or PRBS-9

- Enables modulated signal measurements with standard RF test equipment

### 5.5 Bluetooth Power Management Unit

The Bluetooth Power Management Unit (PMU) provides power management features that can be invoked by either software through power management registers or packet handling in the baseband core. The power management functions provided by the CYW4339 are:

- RF Power Management

- Host Controller Power Management

- BBC Power Management

#### 5.5.1 RF Power Management

The BBC generates power-down control signals to the 2.4 GHz transceiver for the transmit path, receive path, PLL, and power amplifier. The transceiver then processes the power-down functions accordingly.

#### 5.5.2 Host Controller Power Management

When running in UART mode, the CYW4339 may be configured so that dedicated signals are used for power management handshaking between the CYW4339 and the host. The basic power saving functions supported by those handshaking signals include the standard Bluetooth defined power savings modes and standby modes of operation.

Table 4 describes the power-control handshake signals used with the UART interface.

**Table 4. Power Control Pin Description**

| Signal                | Mapped to Pin                     | Type          | Description                                                                                                                                                                                                                                                                                              |

|-----------------------|-----------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BT_DEV_WAKE           | BT_GPIO_0                         | 1             | Bluetooth device wake-up: Signal from the host to the CYW4339 indicating that the host requires attention.                                                                                                                                                                                               |

|                       |                                   |               | Asserted: The Bluetooth device must wake-up or remain awake.     Deasserted: The Bluetooth device may sleep when sleep criteria are met.                                                                                                                                                                 |

|                       |                                   |               | The polarity of this signal is software configurable and can be asserted high or low.                                                                                                                                                                                                                    |

| BT_HOST_WAKE          | BT_GPIO_1                         | 0             | Host wake up. Signal from the CYW4339 to the host indicating that the CYW4339 requires attention.                                                                                                                                                                                                        |

|                       |                                   |               | Asserted: host device must wake-up or remain awake.     Deasserted: host device may sleep when sleep criteria are met.     The polarity of this signal is software configurable and can be asserted high or low.                                                                                         |

| CLK_REQ               | BT_CLK_REQ_OUT<br>WL_CLK_REQ_OUT  | 0             | The CYW4339 asserts CLK_REQ when either the Bluetooth or WLAN block wants the host to turn on the reference clock. The CLK_REQ polarity is active-high. Add an external 100 k $\Omega$ pull-down resistor to ensure the signal is deasserted when the CYW4339 powers up or resets when VDDIO is present. |

| Note: Pad function Co | ntrol Register is set to 0 for th | ese pins. See | DC Characteristics for more details.                                                                                                                                                                                                                                                                     |

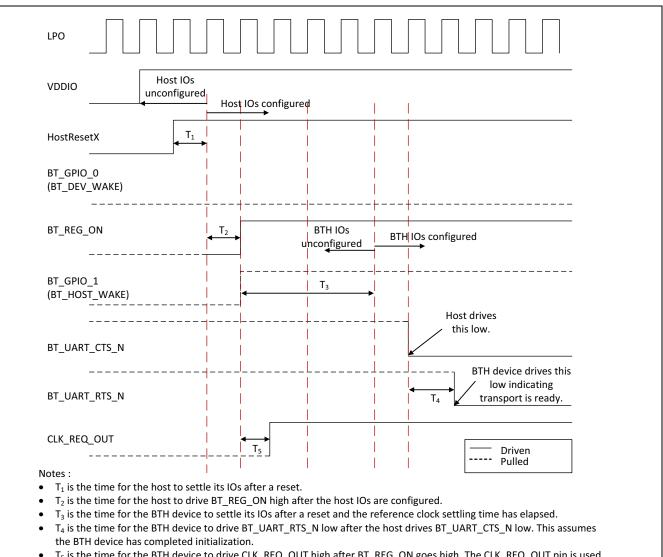

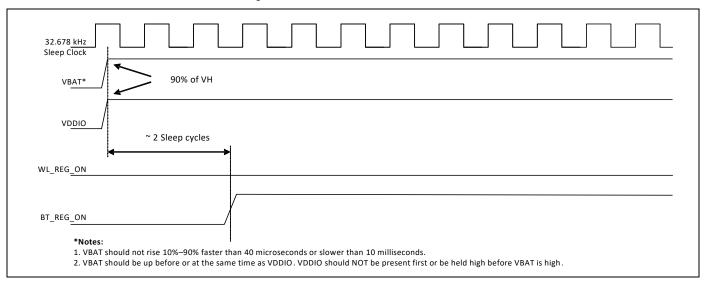

Figure 5. Startup Signaling Sequence

- T<sub>5</sub> is the time for the BTH device to drive CLK\_REQ\_OUT high after BT\_REG\_ON goes high. The CLK\_REQ\_OUT pin is used in designs that have an external reference clock source from the host. It is irrelevant on clock-based designs where the BTH device generates its own reference clock from an external crystal connected to its oscillator circuit.

- The timing diagram assumes that VBAT is present.

#### 5.5.3 BBC Power Management

The following are low-power operations for the BBC:

- Physical layer packet-handling turns the RF on and off dynamically within transmit/receive packets.

- Bluetooth-specified low-power connection modes: sniff, hold, and park. While in these modes, the CYW4339 runs on the low-power oscillator and wakes up after a predefined time period.

- A low-power shutdown feature allows the device to be turned off while the host and any other devices in the system remain operational. When the CYW4339 is not needed in the system, the RF and core supplies are shut down while the I/O remains powered. This allows the CYW4339 to effectively be off while keeping the I/O pins powered so they do not draw extra current from any other devices connected to the I/O.

During the low-power shut-down state, provided VDDIO remains applied to the CYW4339, all outputs are tristated, and most input signals are disabled. Input voltages must remain within the limits defined for normal operation. This is done to prevent current paths or create loading on any digital signals in the system and enables the CYW4339 to be fully integrated in an embedded device to take full advantage of the lowest power-saving modes.

Two CYW4339 input signals are designed to be high-impedance inputs that do not load the driving signal even if the chip does not have VDDIO power supplied to it: the frequency reference input (WRF\_TCXO\_IN) and the 32.768 kHz input (LPO). When the CYW4339 is powered on from this state, it is the same as a normal power-up, and the device does not contain any information about its state from the time before it was powered down.

#### 5.5.4 Wideband Speech

The CYW4339 provides support for wideband speech (WBS) using on-chip SmartAudio technology. The CYW4339 can perform subband-codec (SBC), as well as mSBC, encoding and decoding of linear 16 bits at 16 kHz (256 kbps rate) transferred over the PCM bus.

#### 5.5.5 Packet Loss Concealment

Packet Loss Concealment (PLC) improves apparent audio quality for systems with marginal link performance. Bluetooth messages are sent in packets. When a packet is lost, it creates a gap in the received audio bitstream. Packet loss can be mitigated in several ways:

- Fill in zeros.

- Ramp down the output audio signal toward zero (this is the method used in current Bluetooth headsets).

- Repeat the last frame (or packet) of the received bitstream and decode it as usual (frame repeat).

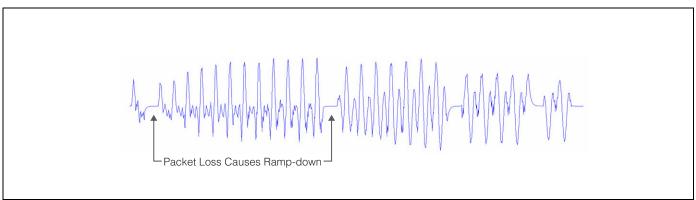

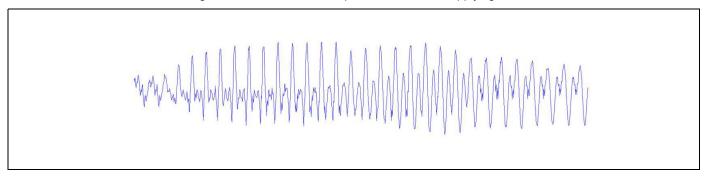

These techniques cause distortion and popping in the audio stream. The CYW4339 uses a proprietary waveform extension algorithm to provide dramatic improvement in the audio quality. Figure 6 and Figure 7 show audio waveforms with and without Packet Loss Concealment. Cypress PLC and bit-error correction (BEC) algorithms also support wideband speech.

Figure 6. CVSD Decoder Output Waveform Without PLC

Figure 7. CVSD Decoder Output Waveform After Applying PLC

#### 5.5.6 Audio Rate-Matching Algorithms

The CYW4339 has an enhanced rate-matching algorithm that uses interpolation algorithms to reduce audio stream jitter that may be present when the rate of audio data coming from the host is not the same as the Bluetooth audio data rates.

#### 5.5.7 Codec Encoding

The CYW4339 can support SBC and mSBC encoding and decoding for wideband speech.

#### 5.5.8 Multiple Simultaneous A2DP Audio Streams

The CYW4339 has the ability to take a single audio stream and output it to multiple Bluetooth devices simultaneously. This allows a user to share his or her music (or any audio stream) with a friend.

#### 5.5.9 Burst Buffer Operation

The CYW4339 has a data buffer that can buffer data being sent over the HCl and audio transports, then send the data at an increased rate. This mode of operation allows the host to sleep for the maximum amount of time, dramatically reducing system current consumption.

#### 5.6 Adaptive Frequency Hopping

The CYW4339 gathers link quality statistics on a channel by channel basis to facilitate channel assessment and channel map selection. The link quality is determined using both RF and baseband signal processing to provide a more accurate frequency-hop map.

### 5.7 Advanced Bluetooth/WLAN Coexistence

The CYW4339 includes advanced coexistence technologies that are only possible with a Bluetooth/WLAN integrated die solution. These coexistence technologies are targeted at small form-factor platforms, such as cell phones and media players, including applications such as VoWLAN + SCO and Video-over-WLAN + High Fidelity BT Stereo.

Support is provided for platforms that share a single antenna between Bluetooth and WLAN. The CYW4339 radio architecture allows for lossless simultaneous Bluetooth and WLAN reception for shared antenna applications. This is possible only via an integrated solution (shared LNA and joint AGC algorithm). It has superior performance versus implementations that need to arbitrate between Bluetooth and WLAN reception.

The CYW4339 integrated solution enables MAC-layer signaling (firmware) and a greater degree of sharing via an enhanced coexistence interface. Information is exchanged between the Bluetooth and WLAN cores without host processor involvement.

The CYW4339 also supports Transmit Power Control (TPC) on the STA together with standard Bluetooth TPC to limit mutual interference and receiver desensitization. Preemption mechanisms are utilized to prevent AP transmissions from colliding with Bluetooth frames. Improved channel classification techniques have been implemented in Bluetooth for faster and more accurate detection and elimination of interferers (including non-WLAN 2.4 GHz interference).

The Bluetooth AFH classification is also enhanced by the WLAN core's channel information.

### 5.8 Fast Connection (Interlaced Page and Inquiry Scans)

The CYW4339 supports page scan and inquiry scan modes that significantly reduce the average inquiry response and connection times. These scanning modes are compatible with the Bluetooth version 2.1 page and inquiry procedures.

### 6. Microprocessor and Memory Unit for Bluetooth

The Bluetooth microprocessor core is based on the ARM<sup>®</sup> Cortex-M3<sup>™</sup> 32-bit RISC processor with embedded ICE-RT debug and JTAG interface units. It runs software from the link control (LC) layer, up to the host controller interface (HCI).

The ARM core is paired with a memory unit that contains 608 KB of ROM memory for program storage and boot ROM, 192 KB of RAM for data scratch-pad and patch RAM code. The internal ROM allows for flexibility during power-on reset to enable the same device to be used in various configurations. At power-up, the lower-layer protocol stack is executed from the internal ROM memory.

External patches may be applied to the ROM-based firmware to provide flexibility for bug fixes or feature additions. These patches may be downloaded from the host to the CYW4339 through the UART transports. The mechanism for downloading via UART is identical to the proven interface of the CYW4329 and CYW4330 devices.

#### 6.1 RAM, ROM, and Patch Memory

The CYW4339 Bluetooth core has 192 KB of internal RAM which is mapped between general purpose scratch-pad memory and patch memory and 608 KB of ROM used for the lower-layer protocol stack, test mode software, and boot ROM. The patch memory capability enables feature additions and bug fixes to the ROM memory.

#### 6.2 Reset

The CYW4339 has an integrated power-on reset circuit that resets all circuits to a known power-on state. The BT power-on reset (POR) circuit is out of reset after BT REG ON goes high. If BT REG ON is low, then the POR circuit is held in reset.

### 7. Bluetooth Peripheral Transport Unit

#### 7.1 SPI Interface

The CYW4339 supports a slave SPI HCI transport with an input clock range of up to 16 MHz. Higher clock rates are possible. The physical interface between the SPI master and the CYW4339 contains the four SPI signals (SPI\_CSB, SPI\_CLK, SPI\_SI, and SPI\_SO) and one interrupt signal (SPI\_INT). The SPI signals are muxed onto the UART signals, see Table 5. The CYW4339 can be configured to accept active-low or active-high polarity on the SPI\_CSB chip-select signal. It can also be configured to drive an active-low or active-high SPI\_INT interrupt signal. Bit ordering on the SPI\_SI and SPI\_SO data lines can be configured as either little-endian or big-endian.

Additionally, proprietary sleep mode and half-duplex handshaking is implemented between the SPI master and the CYW4339. The SPI\_INT is required to negotiate the start of a transaction. The SPI interface does not require flow control in the middle of a payload. The FIFO is large enough to handle the largest packet size. Only the SPI master can stop the flow of bytes on the data lines, since it controls SPI\_CSB and SPI\_CLK. Flow control should be implemented in the higher layer protocols.

Table 5. SPI to UART Signal Mapping

| SPI Signals | UART Signals |

|-------------|--------------|

| SPI_CLK     | UART_CTS_N   |

| SPI_CSB     | UART_RTS_N   |

| SPI_MISO    | UART_RXD     |

| SPI_MOSI    | UART_TXD     |

| SPI_INT     | BT_HOST_WAKE |

#### 7.2 SPI/UART Transport Detection

The BT\_HOST\_WAKE (BT\_GPIO1) pin is also used for BT transport detection. Transport detection occurs during the power-up sequence. Either UART or SPI transport operation is selected based on the following pin state:

- If the BT\_HOST\_WAKE (BT\_GPIO1) pin is pulled low by an external pull-down during power-up, the SPI transport interface is selected.

- If the BT\_HOST\_WAKE (BT\_GPIO1) pin is not pulled low externally during power-up, then the default internal pull-up is detected as a high and the UART transport interface is selected.

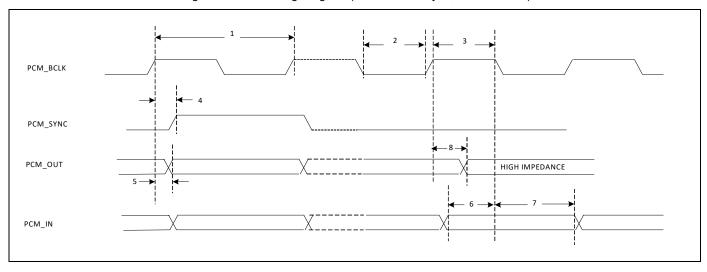

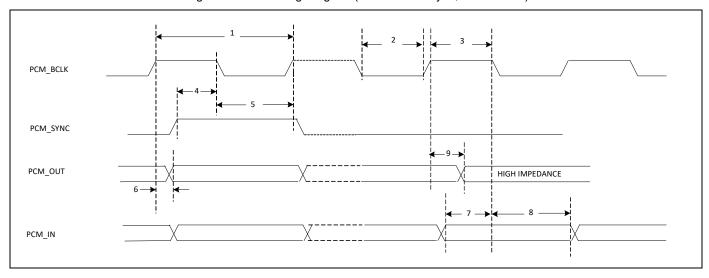

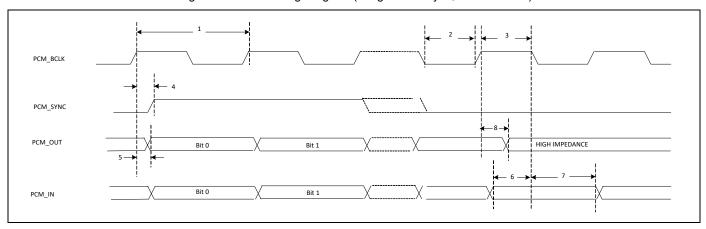

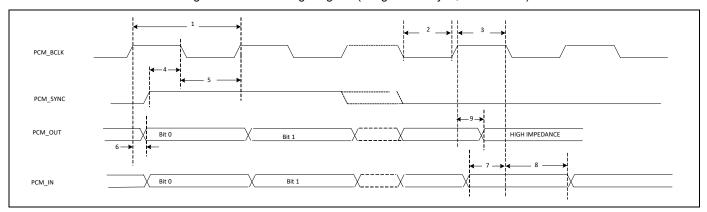

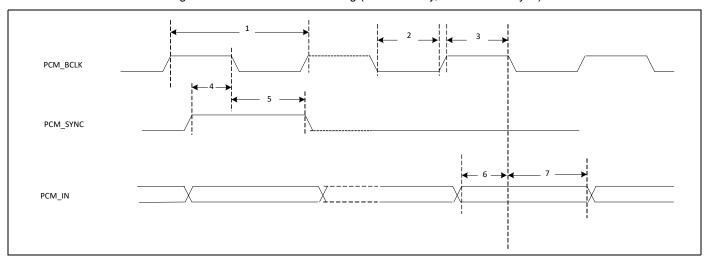

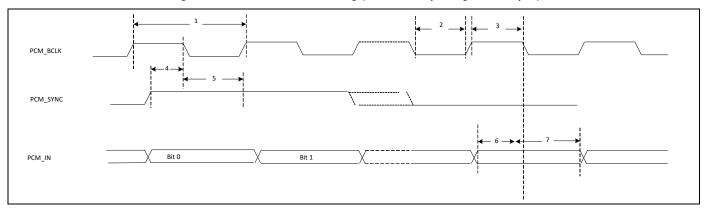

#### 7.3 PCM Interface

The CYW4339 supports two independent PCM interfaces that share pins with the I<sup>2</sup>S interfaces. The PCM Interface on the CYW4339 can connect to linear PCM codec devices in master or slave mode. In master mode, the CYW4339 generates the PCM\_CLK and PCM\_SYNC signals, and in slave mode, these signals are provided by another master on the PCM interface and are inputs to the CYW4339.

The configuration of the PCM interface may be adjusted by the host through the use of vendor-specific HCI commands.

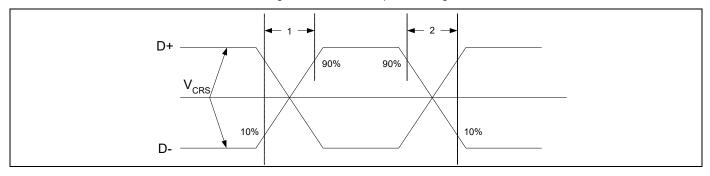

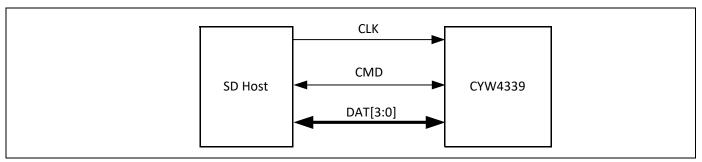

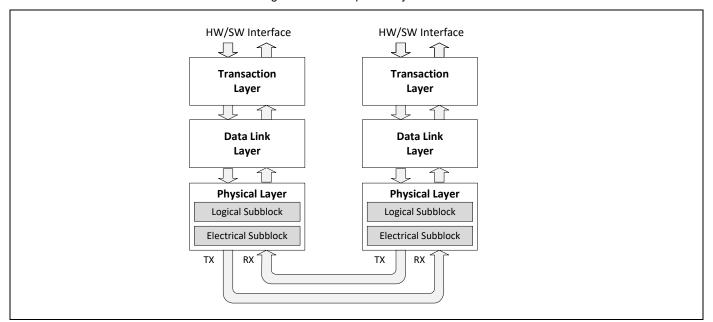

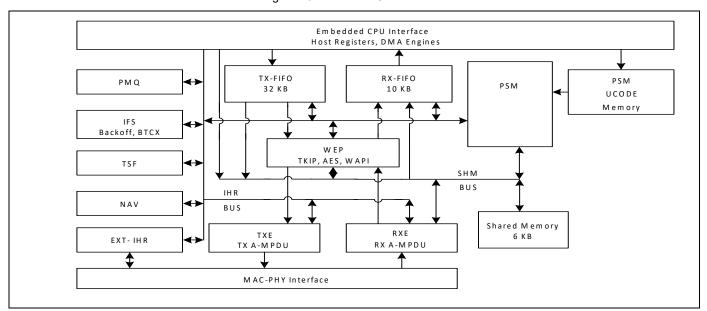

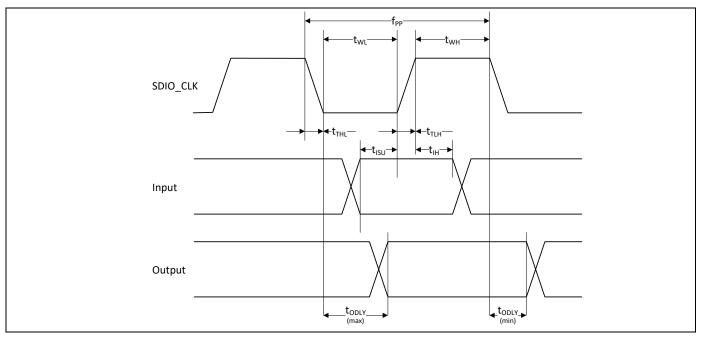

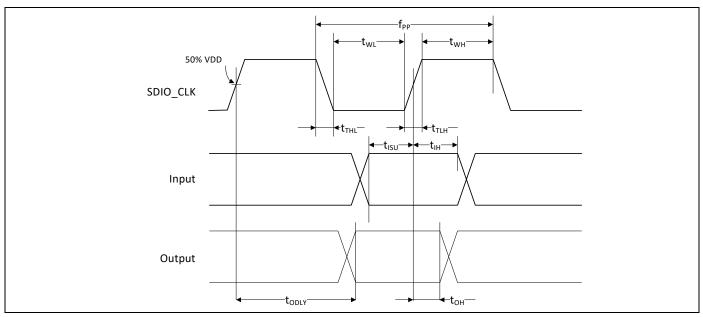

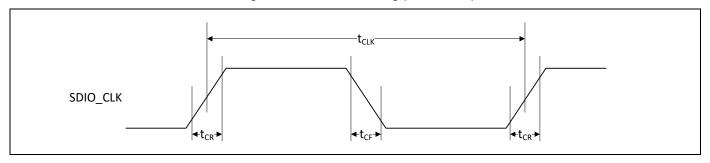

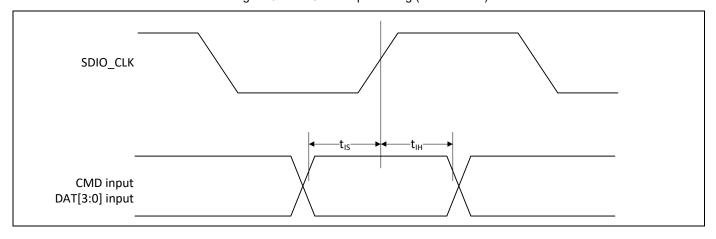

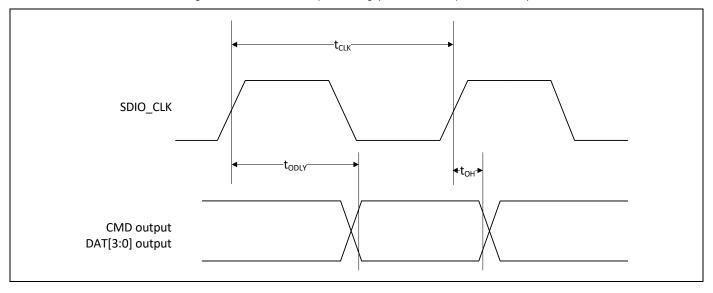

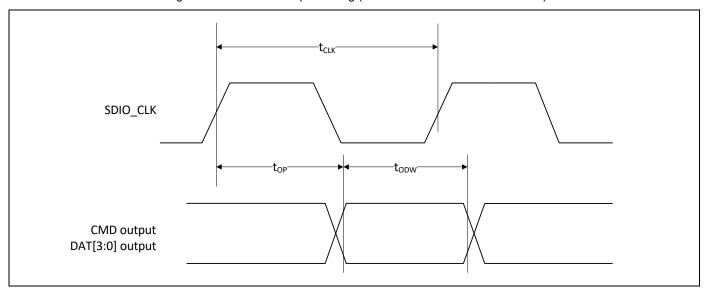

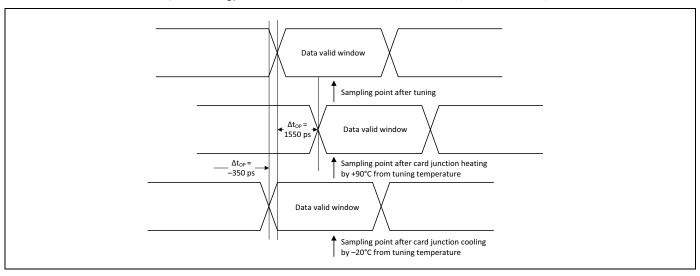

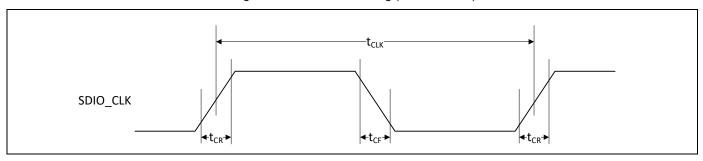

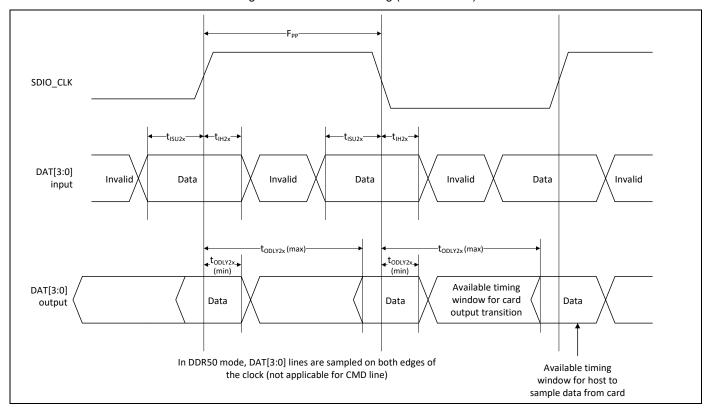

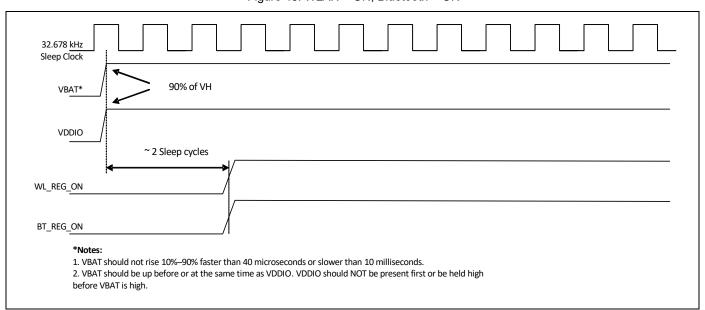

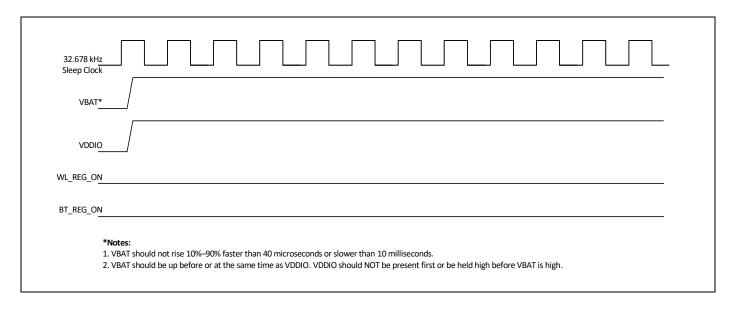

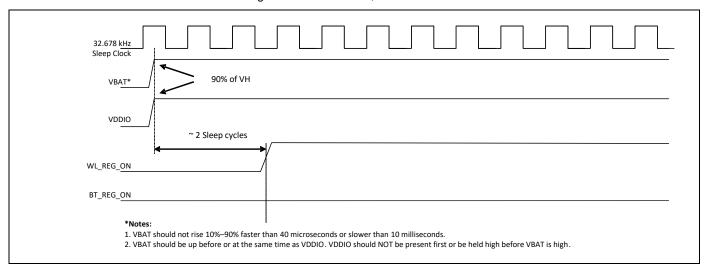

### 7.3.1 Slot Mapping