The following document contains information on Cypress products. The document has the series name, product name, and ordering part numbering with the prefix "MB". However, Cypress will offer these products to new and existing customers with the series name, product name, and ordering part number with the prefix "CY".

### How to Check the Ordering Part Number

- 1. Go to <u>www.cypress.com/pcn</u>.

- 2. Enter the keyword (for example, ordering part number) in the **SEARCH PCNS** field and click **Apply**.

- 3. Click the corresponding title from the search results.

- 4. Download the Affected Parts List file, which has details of all changes

### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

### About Cypress

Cypress is the leader in advanced embedded system solutions for the world's most innovative automotive, industrial, smart home appliances, consumer electronics and medical products. Cypress' microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable, high-performance memories help engineers design differentiated products and get them to market first. Cypress is committed to providing customers with the best support and development resources on the planet enabling them to disrupt markets by creating new product categories in record time. To learn more, go to www.cypress.com.

# MB90598G/F598G/V595G

# F<sup>2</sup>MC-16LX MB90595G Series CMOS 16-bit Proprietary Microcontroller

The MB90595G series with FULL-CAN interface and FLASH ROM is especially designed for automotive and industrial applications. Its main features are two on board CAN Interfaces, which conform to V2.0 Part A and Part B, while supporting a very flexible message buffer scheme and so offering more functions than a normal full CAN approach.

The instruction set of F<sup>2</sup>MC-16LX CPU core inherits an AT architecture of the F<sup>2</sup>MC\* family with additional instruction sets for highlevel languages, extended addressing mode, enhanced multiplication/division instructions, and enhanced bit manipulation instructions. The microcontroller has a 32-bit accumulator for processing long word data.

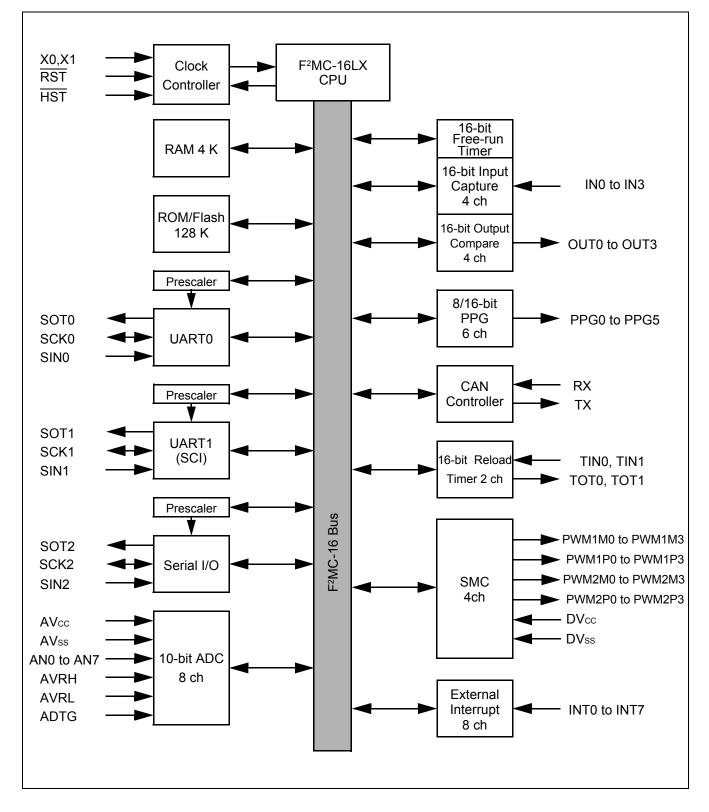

The MB90595G series has peripheral resources of 8/10-bit A/D converters, UART (SCI), extended I/O serial interface, 8/16-bit PPG timer, I/O timer (input capture (ICU), output compare (OCU)) and stepping motor controller.

## Features

#### Clock

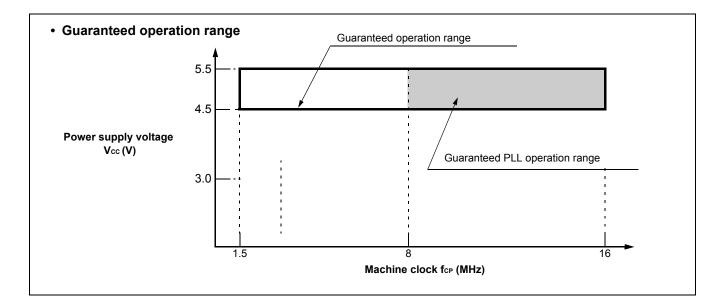

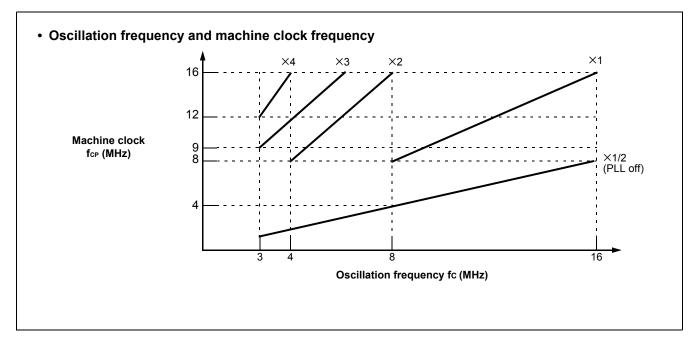

Embedded PLL clock multiplication circuit

Operating clock (PLL clock) can be selected from divided-by-2 of oscillation or one to four times the oscillation (at oscillation of 4 MHz, 4 MHz to 16 MHz). Minimum instruction execution time: 62.5 ns (operation at

Minimum instruction execution time: 62.5 ns (operation at oscillation of 4 MHz, four times the oscillation clock,  $V_{CC}$  of 5.0 V)

- Instruction set to optimize controller applications Rich data types (bit, byte, word, long word) Rich addressing mode (23 types) Enhanced signed multiplication/division instruction and RETI instruction functions Enhanced precision calculation realized by the 32-bit accumulator

- Instruction set designed for high level language (C language) and multi-task operations Adoption of system stack pointer Enhanced pointer indirect instructions Barrel shift instructions

- Program patch function (for two address pointers)

- Enhanced execution speed: 4-byte instruction queue

- Enhanced interrupt function: 8 levels, 34 factors

- Automatic data transmission function independent of CPU operation

Extended intelligent I/O service function (EI<sup>2</sup>OS): Up to 10

- channelsEmbedded ROM size and types

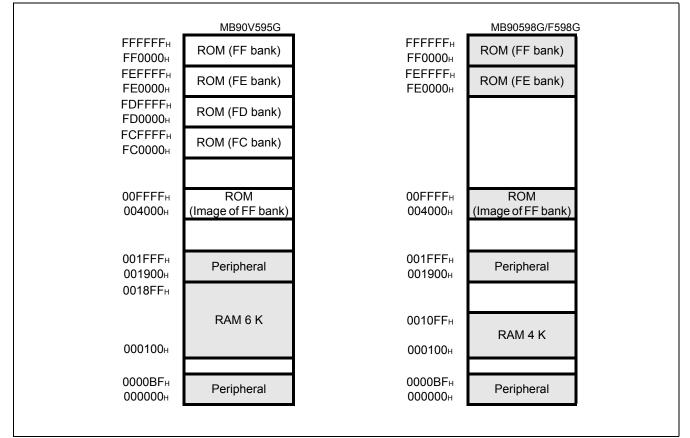

- Mask ROM: 128 Kbytes Flash ROM: 128 Kbytes Embedded RAM size: 4 Kbytes (MB90595G: 6 Kbytes)

- Flash ROM

Supports automatic programming, Embedded Algorithm Write/Erase/Erase-Suspend/Resume commands A flag indicating completion of the algorithm Hard-wired reset vector available in order to point to a fixed boot sector Erase can be performed on each block

Block protection with external programming voltage

Low-power consumption (stand-by) mode

Sleep mode (mode in which CPU operating clock is stopped)

Stop mode (mode in which oscillation is stopped)

CPU intermittent operation mode Hardware stand-by mode

- Process: 0.5 µm CMOS technology

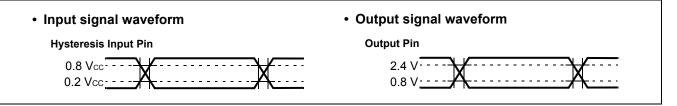

- I/O port General-purpose I/O ports: 78 ports Push-pull output and Schmitt trigger input. Programmable on each bit as I/O or signal for peripherals.

- Timer

Watchdog timer: 1 channel

8/16-bit PPG timer: 8/16-bit × 6 channels

16-bit re-load timer: 2 channels

- 16-bit I/O timer

16-bit Free-run timer: 1 channel

Input capture: 4 channels

Output compare: 4 channels

- Extended I/O serial interface: 1 channel

- UART0

With full-duplex double buffer (8-bit length) Clock asynchronized or clock synchronized (with start/stop bit) transmission can be selectively used.

- UART1 (SCI)

With full-duplex double buffer (8-bit length)

Clock asynchronized or clock synchronized serial transmission

(I/O extended transmission) can be selectively used.

- Stepping motor controller (4 channels)

- External interrupt circuit (8 channels) Amodule for starting an extended intelligent I/O service (EI<sup>2</sup>OS) and generating an external interrupt which is triggered by an external input.

- Delayed interrupt generation module: Generates an interrupt request for switching tasks.

- 8/10-bit A/D converter (8 channels)

8/10-bit resolution can be selectively used.

Starting by an external trigger input.

- FULL-CAN interface: 1 channel Conforming to Version 2.0 Part A and Part B Flexible message buffering (mailbox and FIFO buffering can be mixed)

- 18-bit Time-base counter

- External bus interface: Maximum address space 16 Mbytes

Cypress Semiconductor Corporation Document Number: 002-07700 Rev. \*B 198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised February 6, 2018

# Contents

| Product Lineup                                    | 3  |

|---------------------------------------------------|----|

| Pin Assignment                                    | 5  |

| Pin Description                                   |    |

| I/O Circuit Type                                  | 8  |

| Handling Devices                                  | 11 |

| Block Diagram                                     | 14 |

| Memory Space                                      |    |

| I/O Map                                           | 16 |

| Can Controller                                    |    |

| List of Control Registers                         | 23 |

| List of Message Buffers (ID Registers)            |    |

| List of Message Buffers (DLC Registers and        |    |

| Data Registers)                                   | 27 |

| Interrupt Source, Interrupt Vector, and Interrupt |    |

| Control Register                                  | 29 |

|                                                   |    |

| Electrical Characteristics   |    |

|------------------------------|----|

| Absolute Maximum Ratings     | 31 |

| Recommended Conditions       |    |

| DC Characteristics           |    |

| AC Characteristics           |    |

| A/D Converter                |    |

| A/D Converter Glossary       |    |

| Notes on Using A/D Converter | 45 |

| Flash memory                 |    |

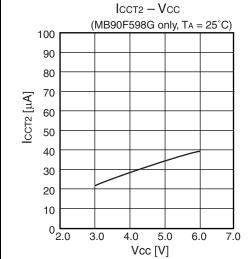

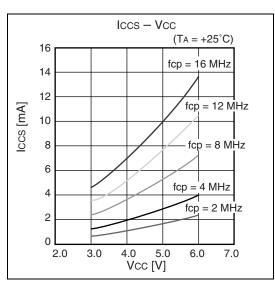

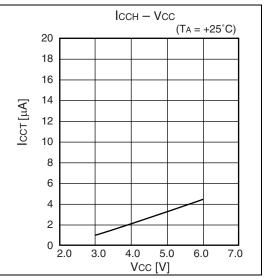

| Example Characteristics      |    |

| Ordering Information         |    |

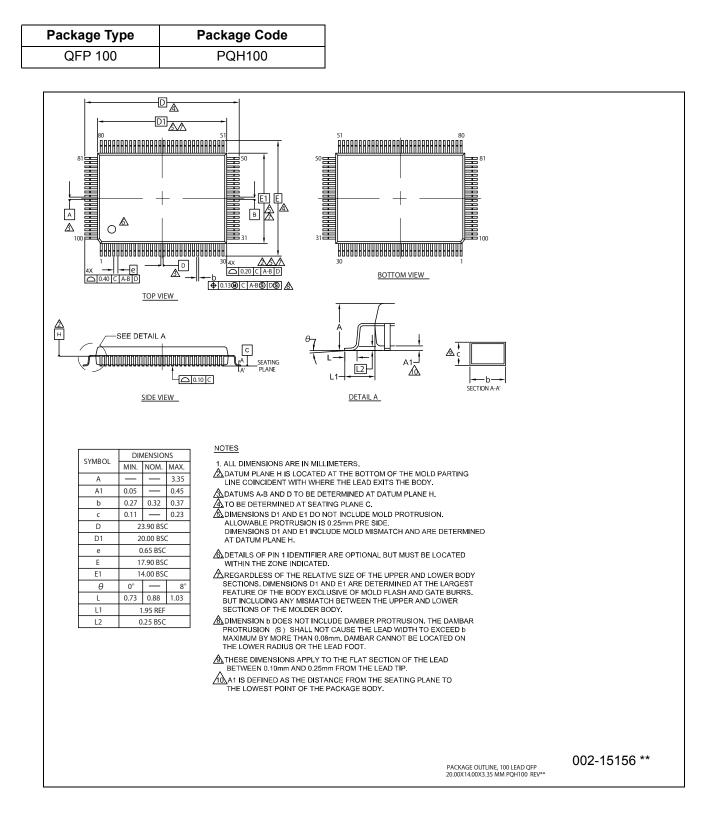

| Package Dimensions           |    |

| Major Changes                |    |

# 1. Product Lineup

|                                                                                                                                                                                                          | Features                                                                                                                                                                                                                                                                                                                                                                                               | MB90598G                                                                                                                                                                                                                                                                                             | MB90V595G                                                                                    |                        |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------|--|--|

| Classifica                                                                                                                                                                                               | ation                                                                                                                                                                                                                                                                                                                                                                                                  | Mask ROM product                                                                                                                                                                                                                                                                                     | Flash ROM product                                                                            | Evaluation product     |  |  |

| ROM size                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                        | 128 Kbytes                                                                                                                                                                                                                                                                                           | 128 Kbytes<br>Boot block<br>Hard-wired reset vector                                          | None                   |  |  |

| RAM size                                                                                                                                                                                                 | Э                                                                                                                                                                                                                                                                                                                                                                                                      | 4 Kbytes                                                                                                                                                                                                                                                                                             | 4 Kbytes                                                                                     | 6 Kbytes               |  |  |

| Emulator                                                                                                                                                                                                 | specific power supply                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                                                                    |                                                                                              | None                   |  |  |

| CPU fund                                                                                                                                                                                                 | ctions                                                                                                                                                                                                                                                                                                                                                                                                 | The number of instructions: 351<br>Instruction bit length: 8 bits, 16 bits<br>Instruction length: 1 byte to 7 bytes<br>Data bit length: 1 bit, 8 bits, 16 bits<br>Minimum execution time: 62.5 ns (at machine<br>Interrupt processing time: 1.5 $\mu$ s<br>(at machine c                             | e clock frequency of 16 MHz)<br>lock frequency of 16 MHz, minim                              | um value)              |  |  |

| UART0                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                        | Clock synchronized transmission (500 K/1 M/<br>Clock asynchronized transmission (4808/520<br>/500<br>Transmission can be performed by bi-directic                                                                                                                                                    | 8/9615/10417/19230/38460/625<br>000 bps at machine clock freque                              | ncy of 16 MHz)         |  |  |

| UART1(S                                                                                                                                                                                                  | SCI)                                                                                                                                                                                                                                                                                                                                                                                                   | Clock synchronized transmission (62.5 K/125<br>Clock asynchronized transmission (1202/240<br>Transmission can be performed by bi-direction                                                                                                                                                           | 4/4808/9615/31250 bps)                                                                       | ster/slave connection. |  |  |

| 8/10-bit A                                                                                                                                                                                               | A/D converter                                                                                                                                                                                                                                                                                                                                                                                          | Conversion precision: 8/10-bit can be selectiv<br>Number of inputs: 8<br>One-shot conversion mode (converts selecte<br>Scan conversion mode (converts two or more<br>up to 8 chann<br>Continuous conversion mode (converts selected character)<br>Stop conversion mode (converts selected character) | d channel once only)<br>e successive channels and can p<br>els)<br>ted channel continuously) | 0                      |  |  |

|                                                                                                                                                                                                          | 16-bit PPG timers       Number of channels: 6 (8/16-bit × 6 channels)         PPG operation of 8-bit or 16-bit       A pulse wave of given intervals and given duty ratios can be output.         Pulse interval: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> (fsys = system clock frequency)         128µs (fosc = 4MHz: oscillation clock frequency) |                                                                                                                                                                                                                                                                                                      |                                                                                              |                        |  |  |

| Number of channels: 2           16-bit Reload timer         Operation clock frequency: fsys/2 <sup>1</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>5</sup> (fsys = Sy Supports External Event Count function |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                      | ys/2⁵ (fsys = System clock frequ                                                             | ency)                  |  |  |

| 16-bit                                                                                                                                                                                                   | 16-bit<br>Output compares                                                                                                                                                                                                                                                                                                                                                                              | Number of channels: 4<br>Pin input factor: A match signal of compare register                                                                                                                                                                                                                        |                                                                                              |                        |  |  |

| I/O tim-<br>er     Input captures     Number of channels: 4<br>Rewriting a register value upon a pin input (rising, falling, or both edges)                                                              |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                      |                                                                                              |                        |  |  |

| Features                                              | MB90598G                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MB90F598G                                                                                                     | MB90V595G |  |  |  |  |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|

| CAN Interface                                         | Number of channels: 1<br>Conforms to CAN Specification Version 2.0 Part A and B<br>Automatic re-transmission in case of error<br>Automatic transmission responding to Remote Frame<br>Prioritized 16 message buffers for data and ID's<br>Supports multiple messages<br>Flexible configuration of acceptance filtering:<br>Full bit compare / Full bit mask / Two partial bit masks<br>Supports up to 1Mbps<br>CAN bit timing setting:<br>MB90598G/F598G:TSEG2 ≥ RSJW |                                                                                                               |           |  |  |  |  |

| Stepping motor controller (4 channels)                | Four high current outputs for each channel<br>Synchronized two 8-bit PWM's for each channel                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                               |           |  |  |  |  |

| External interrupt circuit                            | Number of inputs: 8<br>Started by a rising edge, a falling edge, an "H" le                                                                                                                                                                                                                                                                                                                                                                                            | evel input, or an "L" level input.                                                                            |           |  |  |  |  |

| Serial IO                                             | Clock synchronized transmission (31.25 K/62.5 K/125 K/500 K/1 Mbps at system clock<br>frequency of 16 MHz)<br>LSB first/MSB first                                                                                                                                                                                                                                                                                                                                     |                                                                                                               |           |  |  |  |  |

| Watchdog timer                                        | Reset generation interval: 3.58 ms, 14.33 ms, 57<br>(at oscillation of 4 MHz, minimum value)                                                                                                                                                                                                                                                                                                                                                                          | Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms<br>(at oscillation of 4 MHz, minimum value) |           |  |  |  |  |

| Flash Memory                                          | Supports automatic programming, Embedded Algorithm and<br>Write/Erase/Erase-Suspend/Resume commands<br>A flag indicating completion of the algorithm<br>Hard-wired reset vector available in order to point to a fixed boot sector in Flash<br>Memory<br>Boot block configuration<br>Erase can be performed on each block<br>Block protection with external programming voltage<br>Flash Writer from Minato Electronics, Inc.                                         |                                                                                                               |           |  |  |  |  |

| Low-power consumption<br>(stand-by) mode              | Sleep/stop/CPU intermittent operation/watch timer/hardware stand-by                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                               |           |  |  |  |  |

| Process                                               | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                               |           |  |  |  |  |

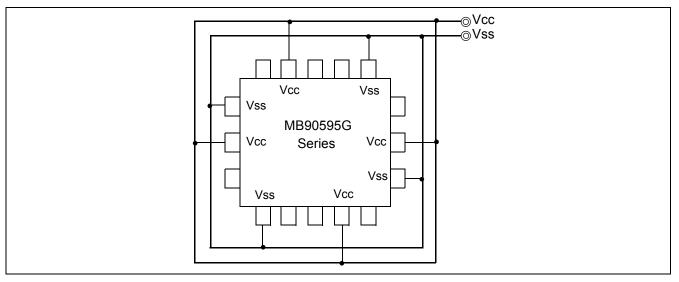

| Power supply voltage for opera-<br>tion* <sup>2</sup> | +5 V±10 %                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                               |           |  |  |  |  |

| Package                                               | QFP-100                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                               | PGA-256   |  |  |  |  |

\*1: It is setting of DIP switch S2 when Emulation pod (MB2145-507) is used.

Please refer to the MB2145-507 hardware manual (2.7 Emulator-specific Power Pin) about details.

\*2: Varies with conditions such as the operating frequency. (See "Electrical Characteristics.")

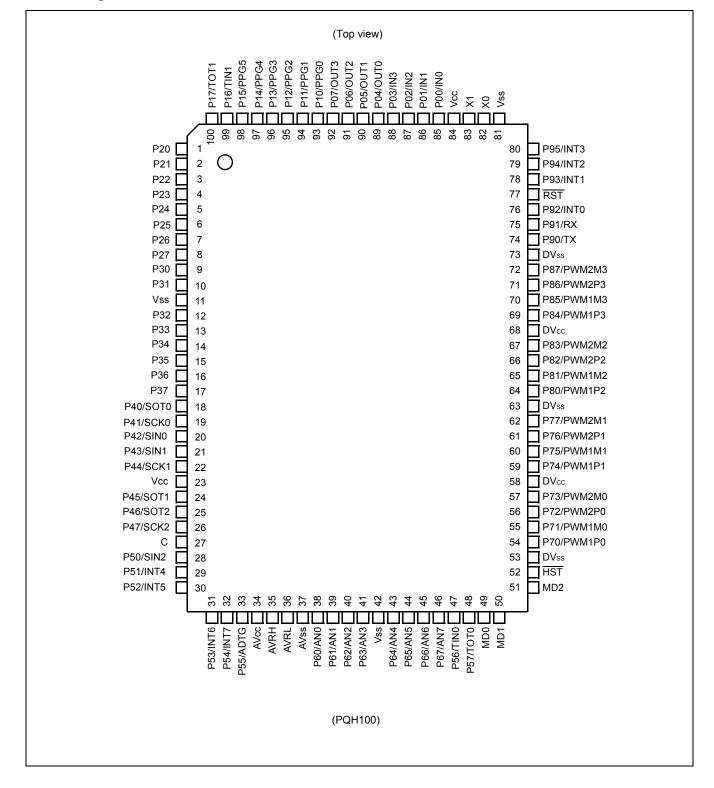

# 2. Pin Assignment

# 3. Pin Description

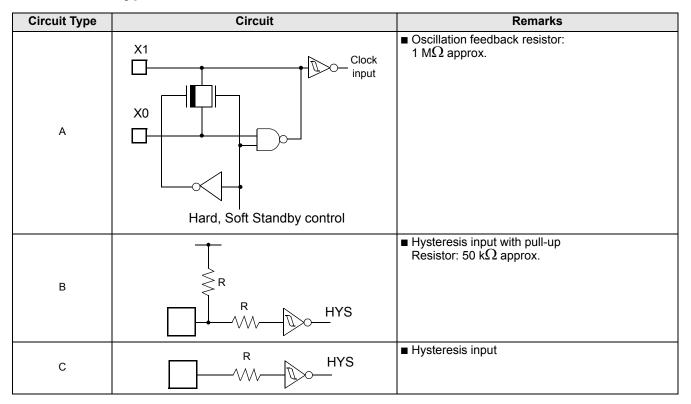

| Pin no.                     | Pin name     | Circuit type       | Function                                      |   |                    |

|-----------------------------|--------------|--------------------|-----------------------------------------------|---|--------------------|

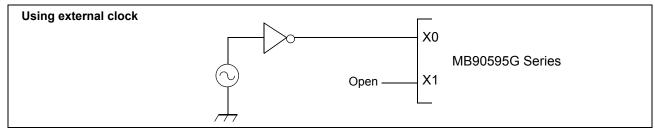

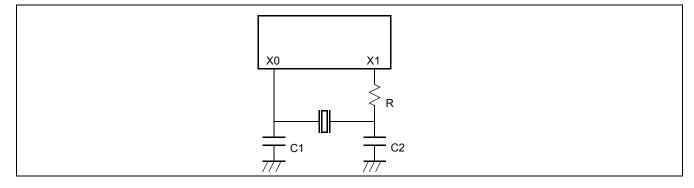

| 82                          | X0           | А                  | Oscillator pin                                |   |                    |

| 83                          | X1           | A                  | Oscillator pin                                |   |                    |

| 77                          | RST          | В                  | Reset input                                   |   |                    |

| 52                          | HST          | С                  | Hardware standby input                        |   |                    |

| 85 to 88                    | P00 to P03   | G                  | General purpose IO                            |   |                    |

| 00 10 00                    | IN0 to IN3   | 0                  | Inputs for the Input Captures                 |   |                    |

| 89 to 92                    | P04 to P07   | G                  | General purpose IO                            |   |                    |

| 09 10 92                    | OUT0 to OUT3 | 9                  | Outputs for the Output Compares.              |   |                    |

| 93 to 98                    | P10 to P15   | D                  | General purpose IO                            |   |                    |

| 95 10 98                    | PPG0 to PPG5 | D                  | Outputs for the Programmable Pulse Generators |   |                    |

| 99                          | P16          | D                  | General purpose IO                            |   |                    |

| 33                          | TIN1         | d                  | TIN input for the 16-bit Reload Timer 1       |   |                    |

| 100                         | P17          | D                  | General purpose IO                            |   |                    |

| 100                         | TOT1         | d                  | TOT output for the 16-bit Reload Timer 1      |   |                    |

| 1 to 8                      | P20 to P27   | G                  | General purpose IO                            |   |                    |

| 9 to 10                     | P30 to P31   | G                  | General purpose IO                            |   |                    |

| 12 to 16                    | P32 to P36   | G                  | General purpose IO                            |   |                    |

| 17                          | P37          | D                  | General purpose IO                            |   |                    |

| 18                          | P40          | G                  | General purpose IO                            |   |                    |

|                             | SOT0         | )                  | SOT output for UART 0                         |   |                    |

| 10                          | 19 P41       |                    | P41                                           | G | General purpose IO |

| 10                          | SCK0         | 9                  | SCK input/output for UART 0                   |   |                    |

| 20                          | P42          | G                  | General purpose IO                            |   |                    |

| 20                          | SIN0         | 9                  | SIN input for UART 0                          |   |                    |

| 21                          | P43          | G                  | General purpose IO                            |   |                    |

| 21                          | SIN1         | 9                  | SIN input for UART 1                          |   |                    |

| 22                          | P44          | G                  | General purpose IO                            |   |                    |

|                             | SCK1         | 9                  | SCK input/output for UART 1                   |   |                    |

| 24                          | P45          | G                  | General purpose IO                            |   |                    |

| 24                          | SOT1         | 0                  | SOT output for UART 1                         |   |                    |

| 25                          | P46          | G                  | General purpose IO                            |   |                    |

| 20                          | SOT2         |                    | SOT output for the Serial IO                  |   |                    |

| 26 P47 G General purpose IO |              | General purpose IO |                                               |   |                    |

| 20                          | SCK2         | 5                  | SCK input/output for the Serial IO            |   |                    |

| P50         D         General purpose IO           29 to 32         P51 to P54         D         SIN Input for the Serial IO           33         P55         D         General purpose IO           33         P55         D         External interrupt input for INT4 to INT7           38 to 41         P60 to P63         General purpose IO         Input for the external trigger of the A/D Converter           38 to 41         P64 to P67         General purpose IO         Input for the A/D Converter           43 to 46         P64 to PA7         General purpose IO         Input for the A/D Converter           47         P66         D         General purpose IO         Input for the A/D Converter           47         P56         D         General purpose IO         Input for the A/D Converter           48         P57         D         General purpose IO         Intriviant for the 16-bit Reload Timer 0           48         TOTO         D         General purpose IO         Intriviant for the 16-bit Reload Timer 0           54 to 57         PWM1P0         F         General purpose IO         Output for Stepper Motor Controller channel 0           9WM2M0         PWM1M1         F         General purpose IO         Output for Stepper Motor Controller channel 1           9WM2M0                                                                                                                                                                                                                                                                                                                                                                                                              | Pin no.   | Pin name               | Circuit type       | Function                                            |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|--------------------|-----------------------------------------------------|--|--|

| SIN 2         SIN Input for the Serial IO           29 to 32         P51 to P54<br>INT4 to INT7         Qeneral purpose IO           33         P55         Ceneral purpose IO           33         P55         D         General purpose IO           38 to 41         P60 to P63         E         General purpose IO           43 to 46         P64 to P67         General purpose IO           43 to 46         P66 to P63         E         General purpose IO           43 to 46         P67         General purpose IO         Input for the AD Converter           43         P66 to P63         E         General purpose IO         Inputs for the AD Converter           47         P56         D         General purpose IO         Inputs for the 16-bit Reload Timer 0           48         P57         D         General purpose IO         Output for the 16-bit Reload Timer 0           54 to 57         PWM1P0<br>PVM2P0         F         General purpose IO         Output for Stepper Motor Controller channel 0           59 to 62         PVM1P1<br>PVM2P1<br>PVM2P1<br>PVM2P1         F         General purpose IO         Output for Stepper Motor Controller channel 1           69 to 72         P80 to P83<br>PVM2P3<br>PVM2P3         F         General purpose IO         Output for Stepper Motor Controller channel 2                                                                                                                                                                                                                                                                                                                                                                                          |           | P50                    | 6                  | General purpose IO                                  |  |  |

| 28 to 32     INT4 to INIT     D     External interrupt input for INT4 to INIT7       33     ADTG     Input for the external trigger of the A/D Converter       38 to 41     P66 to P63     E       43 to 46     P64 to P67     E       43 to 46     P64 to P67     E       47     P56     Input for the A/D Converter       47     P56     Input for the A/D Converter       48     P57     E     General purpose IO       48     TOTO     Thin put for the 14-bit Reload Timer 0       48     TOTO TO     General purpose IO       54 to 57     PWM1P0<br>PWM2P0     PG to P73       59 to 62     PWM1P1<br>PWM2P0     F       60 to 72     PWM1P1<br>PWM2P1       76     PP3       60 to 72     PWM1P3       76     PWM1P3 <t< td=""><td>28</td><td>SIN2</td><td>D</td><td>SIN Input for the Serial IO</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28        | SIN2                   | D                  | SIN Input for the Serial IO                         |  |  |

| INT4 to INT7         External interrupt input for INT4 to INT7           33         P55         D         General purpose IO           38 to 41         P60 to P63         E         General purpose IO           43 to 46         AN0 to AN3         E         General purpose IO           43 to 46         P64 to P67         E         General purpose IO           43 to 46         P64 to P67         E         General purpose IO           47         P56         D         General purpose IO           47         P56         D         General purpose IO           48         P57         Ceneral purpose IO         Timut for the A/D Converter           48         P57         D         General purpose IO         Toto to P73           54 to 57         P70 to P73         F         General purpose IO         Output for Stepper Motor Controller channel 0           59 to 62         PWM1P0<br>PWM2P0         F         General purpose IO         Output for Stepper Motor Controller channel 0           59 to 62         PWM1P1<br>PWM2P2         F         General purpose IO         Output for Stepper Motor Controller channel 1           64 to 67         P80 to P83<br>PWM1P2<br>PWM2P3         F         General purpose IO         Output for Stepper Motor Controller channel 2                                                                                                                                                                                                                                                                                                                                                                                                                              | 20 to 22  | P51 to P54             | D                  | General purpose IO                                  |  |  |

| 33     ADTG     D     Input for the external trigger of the A/D Converter       38 to 41     P60 to P63     E     General purpose IO       43 to 46     P64 to P67     E     General purpose IO       43 to 46     P64 to P67     E     General purpose IO       47     P56     D     Tinputs for the A/D Converter       47     P56     D     Tinputs for the A/D Converter       48     P57     D     General purpose IO       48     TOTO     D     General purpose IO       54 to 57     P70 to P73     P70 to P73       PVM1P0     PVM1P0     F       Output for the 16-bit Reload Timer 0       54 to 57     P74 to P77       PVM1P0     F       Output for Stepper Motor Controller channel 0       PVM1P1     PVM2P0       PVM1P1     F       General purpose IO       0utput for Stepper Motor Controller channel 1       PVM2P0     PVM1P1       PVM1P1     F       General purpose IO       0utput for Stepper Motor Controller channel 1       PVM2P1     PVM1P2       PVM1P2     F       General purpose IO       PVM1P2     F       PVM1P2     PVM1P3       PVM1P4     F       PVM1P2 <td>29 10 32</td> <td>INT4 to INT7</td> <td>D</td> <td>External interrupt input for INT4 to INT7</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29 10 32  | INT4 to INT7           | D                  | External interrupt input for INT4 to INT7           |  |  |

| ADTG         Input for the external trigger of the A/D Converter           38 to 41         P60 to P63<br>AN0 to AN3         E         General purpose IO           43 to 46         P64 to P67<br>AN4 to AN7         E         General purpose IO           43 to 46         P66 to P63<br>AN4 to AN7         E         General purpose IO           47         P56<br>TIN0         D         General purpose IO           48         P57<br>TOTO         D         General purpose IO           48         P57<br>TOTO         D         General purpose IO           54 to 57         P70 to P73<br>PWM1P0<br>PWM2P0<br>PWM2P0<br>PWM2P0         F         General purpose IO           54 to 57         P74 to P77<br>PWM1P0<br>PWM2P0<br>PWM2P0<br>PWM2P0         F         General purpose IO           59 to 62         P74 to P77<br>PWM1P1<br>PWM2P1<br>PWM2P1<br>PWM2P1         F         General purpose IO           59 to 62         P74 to P77<br>PWM1P2<br>PWM2P2<br>PWM2P2<br>PWM2P2         F         General purpose IO           64 to 67         P80 to P83<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3         F         General purpose IO           69 to 72         P84 to P87<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3         F         General purpose IO           74         P90<br>TX         D         General purpose IO         TX                                                                                                                                                                                                                                      | 22        | P55                    | D                  | General purpose IO                                  |  |  |

| 38 to 41     AN0 to AN3     E     Inputs for the A/D Converter       43 to 46     P64 to P67     E     General purpose IO       47     P56     D     General purpose IO       47     P56     D     TIN oputs for the A/D Converter       48     P57     D     General purpose IO       48     P57     D     General purpose IO       7     P70 to P73     General purpose IO       9     PVM1P0     P       9     PWM1P0     F       0utput for the 16-bit Reload Timer 0       54 to 57     PWM1P0       PWM2P0     F       0utput for Stepper Motor Controller channel 0       PWM2P0     PWM2P0       PWM2P1     PWM2P1       PWM2P1     PWM2P1       PWM2P1     PWM2P2       PWM2P2     PWM1P2       PWM2P2     PWM2P3       PWM2P3     F       69 to 72     P84 to P87       P84 to P87     General purpose IO       PWM2P3     F       General purpose IO     Output for Stepper Motor Controller channel 2       PWM2P3     F       69 to 72     P84 to P87       P84 to P87     General purpose IO       PWM2P3     F       General purpose IO       P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | ADTG                   | D                  | Input for the external trigger of the A/D Converter |  |  |

| AN0 to AN3         Inputs for the A/D Converter           43 to 46         P64 to P67<br>AN4 to AN7         E         General purpose IO<br>Inputs for the A/D Converter           47         P56<br>TIN0         D         General purpose IO<br>TIN input for the 16-bit Reload Timer 0           48         P57<br>TOT0         D         General purpose IO<br>TOT output for the 16-bit Reload Timer 0           48         P70 to P73<br>PVM1P0<br>PVM1P0<br>PVM2P0<br>PVM2P0         General purpose IO           54 to 57         P70 to P73<br>PVM1P10<br>PVM2P0<br>PVM2P0         General purpose IO           59 to 62         PVM1P1<br>PVM2P1<br>PVM2P1         F           69 to 72         P80 to P83<br>PVM2P2<br>PVM2P2         General purpose IO           69 to 72         PVM1P3<br>PVM2P3<br>PVM2P3         F           69 to 72         P90<br>PVM1P3<br>PVM2P3<br>PVM2P3         F           69 to 72         P90<br>PVM1P3<br>PVM2P3<br>PVM2P3         F           69 to 72         P90<br>PVM2P3<br>PVM2P3<br>PVM2P3         F           69 to 72         P90<br>PVM1P3<br>PVM2P3<br>PVM2P3         F           69 to 72         P90<br>PVM2P3<br>PVM2P3         F           69 to 72         P90<br>PVM2P3         Ceneral purpose IO           75         P91         D         General purpose IO                                                                                                                                                                                                                                                                                                                                                                                                                  | 38 to 41  | P60 to P63             | Е                  | General purpose IO                                  |  |  |

| 43 to 46     AN4 to AN7     E     Inputs for the A/D Converter       47     P56     D     General purpose IO       48     P57     D     TiN input for the 16-bit Reload Timer 0       48     TOTO     D     General purpose IO       48     P57     D     TOT output for the 16-bit Reload Timer 0       54 to 57     P70 to P73     General purpose IO       PWM1P0     PWM1P0     F     General purpose IO       54 to 57     P74 to P77     General purpose IO       PVM2P0     PWM1P1     F     Output for Stepper Motor Controller channel 0       PVM2P1     PWM2P1     F     Output for Stepper Motor Controller channel 1       PVM2P2     PWM1P2     F     Output for Stepper Motor Controller channel 1       PVM2P3     PVM1P2     F     Output for Stepper Motor Controller channel 1       PVM2P2     PVM1P2     F     Output for Stepper Motor Controller channel 1       PVM2P3     PVM2P3     F     Output for Stepper Motor Controller channel 2       PVM2P3     PVM1P3     F     Output for Stepper Motor Controller channel 3       PVM2P3     PVM1P3     F     Output for Stepper Motor Controller channel 3       PVM2P3     PVM1P3     F     Output for Stepper Motor Controller channel 3       PVM2P3     PVM2P3 <t< td=""><td>30 10 4 1</td><td>AN0 to AN3</td><td>L</td><td>Inputs for the A/D Converter</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                   | 30 10 4 1 | AN0 to AN3             | L                  | Inputs for the A/D Converter                        |  |  |

| AN4 to AN7     Inputs for the AD Converter       47     P56     D     General purpose IO       48     P57     D     General purpose IO       48     TOT0     TO to the 16-bit Reload Timer 0       74     P70 to P73     General purpose IO       75     PVW1P0     F       90 to 77     F     General purpose IO       74     PVW1P0     F       91 to 77     General purpose IO       92 to 62     PVW1P0     F       92 to 62     PVW1P1     F       92 to 62     PVW1P1     F       94 to 67     PVW1P1       PVW1P2     F       94 to 67     PVW1P2       PVW1P2     F       94 to 67     PVW1P2       PVW1P2     F       94 to 67     PVW1P3       PVW1P2     F       94 to 67     PVW1P3       PVW1P3     F       69 to 72     PVW1P3       PVW1P3     F       94 to 787     General purpose IO       PVW1P3     F       PVW1P3     F       PVW1P3     F       PVW1P3     F       PVW1P3     PVW1P3       PVW1P3     F       PVW1P3     PVW1P3       PVW1P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13 to 16  | P64 to P67             | Е                  | General purpose IO                                  |  |  |

| 47     TIN0     D     TIN input for the 16-bit Reload Timer 0       48     P57     General purpose IO     TOT output for the 16-bit Reload Timer 0       48     TOT0     D     General purpose IO       54 to 57     PWM1P0<br>PWM2P0<br>PWM2M0     F     General purpose IO       59 to 62     PVM1P1<br>PWM2M1     F     General purpose IO       59 to 62     PVM1P1<br>PWM2M0     F     General purpose IO       59 to 62     PWM1P1<br>PWM2M1     F     General purpose IO       64 to 67     PWM1P2<br>PWM2M2     F     General purpose IO       64 to 67     PWM1P2<br>PWM2M2     F     General purpose IO       69 to 72     PWM1P3<br>PWM2M2     F     General purpose IO       69 to 72     PWM1P3<br>PWM2M3     F     General purpose IO       74     P90<br>TX     P     General purpose IO       75     P91     D     General purpose IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43 10 40  | AN4 to AN7             | L                  | Inputs for the A/D Converter                        |  |  |

| TIN0TIN input for the 16-bit Reload Timer 048P57<br>TOT0DGeneral purpose 10<br>TOT output for the 16-bit Reload Timer 048P70 to P73<br>PWM1P0<br>PWW2P0<br>PWW2P0FGeneral purpose 10<br>Output for Stepper Motor Controller channel 054 to 57P74 to P77<br>PWM2P0<br>PWM2P0<br>PWM2P0General purpose 10<br>Output for Stepper Motor Controller channel 059 to 62PPW1P1<br>PWM2P1<br>PWM2P1<br>PWM2P1<br>PWM2P1General purpose 10<br>Output for Stepper Motor Controller channel 164 to 67PWM1P2<br>PWM2P2<br>PWM2P2<br>PWM2P2<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3General purpose 10<br>Output for Stepper Motor Controller channel 269 to 72P80 to P83<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3General purpose 10<br>Output for Stepper Motor Controller channel 374P90<br>TXP0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0<br>PM0 <br< td=""><td>47</td><td>P56</td><td>D</td><td>General purpose IO</td></br<> | 47        | P56                    | D                  | General purpose IO                                  |  |  |

| 48TOTODTOT output for the 16-bit Reload Timer 054 to 57P70 to P73<br>PWM1P0<br>PWM2P0<br>PWM2P0General purpose IO54 to 57PWM1P0<br>PWM2P0<br>PWM2P0FOutput for Stepper Motor Controller channel 059 to 62P74 to P77<br>PWM2P1<br>PWM2P1<br>PWM2P1<br>PWM2P1General purpose IO59 to 62PWM1P1<br>PWM2P1<br>PWM2P1<br>PWM2P1FGeneral purpose IO64 to 67PWM1P2<br>PWM2P2<br>PWM2P2<br>PWM2P2<br>PWM2P2<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3FGeneral purpose IO69 to 72P84 to P87<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3FGeneral purpose IO74P90<br>TXDGeneral purpose IO75P91DGeneral purpose IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47        | TIN0                   | d                  | TIN input for the 16-bit Reload Timer 0             |  |  |

| TOT0TOT output for the 16-bit Reload Timer 0TOT output for the 16-bit Reload Timer 0P70 to P73PWM1P0<br>PWM2P0<br>PWM2P0FGeneral purpose IOPWM1P0<br>PWM2P0<br>PWM2M0FGeneral purpose IO59 to 62PVM1P1<br>PWM2P1<br>PWM2P1<br>PWM2P1FGeneral purpose IO59 to 62PWM1P2<br>PWM2P1<br>PWM2P1FGeneral purpose IO64 to 67P80 to P83<br>PWM2P2<br>PWM2P2<br>PWM2P2FGeneral purpose IO64 to 67PWM1P2<br>PWM2P2<br>PWM2P2<br>PWM2P3<br>PWM2P3FGeneral purpose IO69 to 72P84 to P87<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3FGeneral purpose IO69 to 72P84 to P87<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br><td>48</td> <td>P57</td> <td>D</td> <td>General purpose IO</td>                                                                                                  | 48        | P57                    | D                  | General purpose IO                                  |  |  |

| 54 to 57     PWM1P0<br>PWM2P0<br>PWM2P0<br>PWM2P0<br>PWM2P0     F     Output for Stepper Motor Controller channel 0       59 to 62     P74 to P77<br>PWM1P1<br>PWM2P1<br>PWM2P1<br>PWM2P1     F     General purpose IO       64 to 67     P80 to P83<br>PWM1P2<br>PWM2P2<br>PWM2M2     F     General purpose IO       64 to 67     PWM1P2<br>PWM2P2<br>PWM2M2     F     General purpose IO       69 to 72     P84 to P87<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2P3     General purpose IO       74     P90<br>TX     D     General purpose IO       74     P91     D     General purpose IO       75     P91     D     General purpose IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40        | TOT0                   | d                  | TOT output for the 16-bit Reload Timer 0            |  |  |

| 54 to 57PWM1100<br>PWM2P0<br>PWM2M0FOutput for Stepper Motor Controller channel 059 to 62P74 to P77<br>PWM1P1<br>PWM2P1<br>PWM2P1<br>PWM2M1FGeneral purpose IO<br>Output for Stepper Motor Controller channel 164 to 67P80 to P83<br>PWM1P2<br>PWM2P2<br>PWM2M2FGeneral purpose IO<br>Output for Stepper Motor Controller channel 264 to 67P80 to P83<br>PWM1P2<br>PWM2P2<br>PWM2M2FGeneral purpose IO<br>Output for Stepper Motor Controller channel 264 to 67P84 to P87<br>PWM2P2<br>PWM2M2FGeneral purpose IO<br>Output for Stepper Motor Controller channel 269 to 72P84 to P87<br>PWM2P3<br>PWM2P3<br>PWM2P3FGeneral purpose IO<br>Output for Stepper Motor Controller channel 374P90<br>TXDGeneral purpose IO<br>TX output for CAN Interface<br>General purpose IO75P91<br>P91DGeneral purpose IO<br>TX output for CAN Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | P70 to P73             |                    | General purpose IO                                  |  |  |

| 59 to 62       PWM1P1<br>PWM2P1<br>PWM2P1<br>PWM2M1       F       Output for Stepper Motor Controller channel 1         64 to 67       P80 to P83<br>PWM1P2<br>PWM2P2<br>PWM2P2<br>PWM2P2<br>PWM2M2       F       General purpose IO         69 to 72       P84 to P87<br>PWM1M3<br>PWM2P3<br>PWM2P3<br>PWM2P3<br>PWM2M3       F       General purpose IO         69 to 72       PWM1P3<br>PWM2P3<br>PWM2M3       F       General purpose IO         74       P90<br>TX       D       General purpose IO         74       P90<br>P91       P91       General purpose IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54 to 57  | PWM1M0<br>PWM2P0       | F                  | Output for Stepper Motor Controller channel 0       |  |  |

| 59 to 62       PWM1M1<br>PWM2P1<br>PWM2M1       F       Output for Stepper Motor Controller channel 1         64 to 67       P80 to P83<br>PWM1P2<br>PWM1M2<br>PWM2P2<br>PWM2M2       F       General purpose IO         64 to 67       P84 to P87<br>PWM2M2       F       General purpose IO         69 to 72       P84 to P87<br>PWM1M3<br>PWM2P3<br>PWM2M3       F       General purpose IO         74       P90<br>TX       D       General purpose IO         75       P91       D       General purpose IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | P74 to P77             |                    | General purpose IO                                  |  |  |

| 64 to 67PWM1P2<br>PWM1M2<br>PWM2P2<br>PWM2M2FOutput for Stepper Motor Controller channel 269 to 72P84 to P87<br>PWM1M3<br>PWM1M3<br>PWM2P3<br>PWM2M3FGeneral purpose IO74P90<br>TXDOutput for Stepper Motor Controller channel 375P91DGeneral purpose IO<br>TX output for CAN Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59 to 62  | PWM1M1<br>PWM2P1       | F                  | Output for Stepper Motor Controller channel 1       |  |  |

| 64 to 67PWM1M2<br>PWM2P2<br>PWM2M2FOutput for Stepper Motor Controller channel 269 to 72P84 to P87<br>PWM1M3<br>PWM2P3<br>PWM2M3General purpose IO74P90<br>TXDGeneral purpose IO74P90<br>TXDGeneral purpose IO75P91DGeneral purpose IO75P91DGeneral purpose IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | P80 to P83             |                    | General purpose IO                                  |  |  |

| 69 to 72       PWM1P3<br>PWM1M3<br>PWM2P3<br>PWM2M3       F       Output for Stepper Motor Controller channel 3         74       P90       D       General purpose IO         74       TX       D       TX output for CAN Interface         75       P91       D       General purpose IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64 to 67  | PWM1M2<br>PWM2P2       | F                  | Output for Stepper Motor Controller channel 2       |  |  |

| 69 to 72     PWM1M3<br>PWM2P3<br>PWM2M3     F     Output for Stepper Motor Controller channel 3       74     P90     D     General purpose IO       74     TX     D     TX output for CAN Interface       75     P91     D     General purpose IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | P84 to P87             |                    | General purpose IO                                  |  |  |

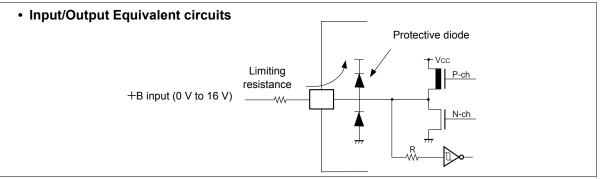

| 74     D     TX       TX     TX output for CAN Interface       75     P91       D     General purpose IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69 to 72  | PWM1M3<br>PWM2P3       | F                  | Output for Stepper Motor Controller channel 3       |  |  |