### **Features**

- USB 2.0-certified, Full-Speed (12 Mbps)

- Supports communication driver class (CDC), personal health care device class (PHDC), and vendor-device class

- Battery charger detection (BCD) compliant with USB battery charging specification, Rev. 1.2 (peripheral detect only)

- Integrated USB termination resistors

- Single-channel configurable UART interface

- Data rates up to 3 Mbps

- 190 bytes for each transmit and receive buffer

- Supports 2-pin, 4-pin and 6-pin UART interface

- Data format:

- 7 to 8 data bits

- 1 to 2 stop bits

- No parity, even, odd, mark, or space parity

- Supports parity, overrun, and framing errors

- Supports flow control using CTS, RTS, DTR, DSR

- Supports UART break signal

- CY7C65211 supports single channel RS232/RS422 interfaces whereas CY7C65211A supports RS232/RS422/RS485 interfaces

- Single-channel configurable SPI interface

- Data rate up to 3 MHz for SPI master and 1 MHz for SPI slave

- Data width: 4 bits to 16 bits

- 256 bytes for each transmit and receive buffer

- Supports Motorola, TI, and National SPI modes

- Single-channel configurable I<sup>2</sup>C interface

- Master/slave up to 400 kHz

- 256 bytes each transmit and receive buffer

- Supports multi-master I<sup>2</sup>C

- CAPSENSE™

- Smart sensing algorithm for Auto-Tuning is supported through a Infineon-supplied configuration utility

- Max CAPSENSE™ buttons: 5

- GPIOs linked to CAPSENSE™ buttons

- General-purpose input/output (GPIO) pins: 10

- Supports unique serial number feature for each device, which fixes the COM port number permanently when USB-serial bridge controller as CDC device plugs in

- 512-byte flash for storing configuration parameters

**Applications**

- Configuration utility (Windows) to configure the following:

- Vendor ID (VID), Product ID (PID), and Product and Manufacturer descriptors

- UART/I2C/SPI

- CAPSENSE™

- Charger detection

- GPIO

- Driver support for VCOM and DLL

- Windows 10: 32- and 64-bit versions

- Windows 8.1: 32- and 64-bit versions

- Windows 8: 32- and 64-bit versions

- Windows 7: 32- and 64-bit versions

- Windows Vista: 32- and 64-bit versions

- Windows XP: 32- and 64-bit versions

- Windows CE

- Mac OS-X: 10.6, 10.7

- Linux: Kernel version 2.6.35 onwards

- Android: Gingerbread and later versions

- Clocking: Integrated 48-MHz clock oscillator

- Supports bus-/self-powered configurations

- USB Suspend mode for low power

- Operating voltage: 1.71 V to 5.5 V

- Operating temperature:

- Commercial: 0°C to 70°C

- Industrial: -40°C to 85°C

- Automotive: -40°C to 105°C

- ESD protection: 2.2 kV HBM

- · RoHS-compliant package

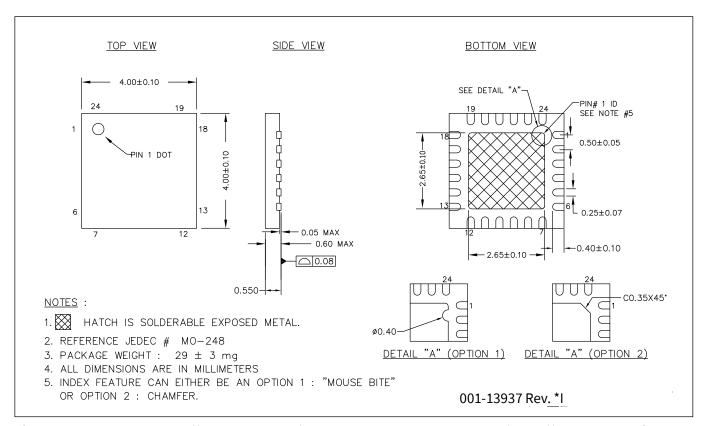

- 24-pin QFN (4.0 mm × 4.0 mm, 0.55 mm, 0.5 mm pitch)

- Ordering part number

- CY7C65211-24LTXI

- CY7C65211A-24LTXI

- CY7C65211A-24LQXS

- CY7C65211A-24LQXST

## **Applications**

- Medical/healthcare devices

- Point-of-sale (POS) terminals

- Test and measurement system

- · Gaming systems

- Set-top box PC-USB interface

- Industrial

- Automotive

- Networking

- Enabling USB connectivity in legacy peripherals

Table of contents

# **Table of contents**

| Features                                         | 1  |

|--------------------------------------------------|----|

| Applications                                     |    |

| Table of contents                                |    |

| 1 Functional description                         |    |

| 1.1 CY7C65211 and CY7C65211A features comparison |    |

| 2 Block diagram                                  |    |

| 3 Functional overview                            |    |

| 3.1 USB and charger detect                       |    |

| 3.1.1 USB                                        |    |

| 3.1.2 Charger detection                          |    |

| 3.2 Serial communication                         |    |

| 3.2.1 UART interface                             |    |

| 3.2.2 UART flow control                          |    |

| 3.2.3 SPI interface                              |    |

| 3.2.4 I2C interface                              |    |

| 3.3 CAPSENSE™                                    |    |

| 3.4 GPIO interface                               |    |

| 3.5 Memory                                       |    |

| 3.6 System resources                             |    |

| 3.6.1 Power system                               |    |

| 3.6.2 Clock system                               |    |

| 3.6.3 Internal 48-MHz oscillator                 |    |

| 3.6.4 Internal 32-kHz oscillator                 |    |

| 3.6.5 Reset                                      |    |

| 3.7 Suspend and resume                           |    |

| 3.8 Wakeup                                       |    |

| 3.9 Software                                     |    |

| 3.9.1 Drivers for Linux operating systems        |    |

| 3.9.2 Android support                            |    |

| 3.9.3 Drivers for Mac OSx                        |    |

| 3.9.4 Drivers for Windows operating systems      |    |

| 3.9.5 Windows-CE support                         | 11 |

| 3.10 Internal flash configuration                |    |

| 4 Electrical specifications                      |    |

| 4.1 Absolute maximum ratings                     | 13 |

| 4.2 Operating conditions                         |    |

| 4.3 Device-level specifications                  | 14 |

| 4.3.1 GPIO                                       | 15 |

| 4.3.2 nXRES                                      | 17 |

| 4.4 Digital peripherals                          | 18 |

| 4.4.1 UART                                       | 18 |

| 4.4.2 SPI                                        | 18 |

| 4.4.3 I2C                                        |    |

| 4.5 CAPSENSE™                                    | 21 |

| 4.6 System resources                             | 21 |

| 4.6.1 Memory                                     |    |

| 5 Pin description                                |    |

| 6 USB power configurations                       |    |

| 6.1 USB bus-powered configuration                |    |

| 6.2 Self-powered configuration                   |    |

| 6.3 USB bus-powered with variable I/O voltage    | 26 |

# Table of contents

Datasheet

| 7 Application examples                                                     |    |

|----------------------------------------------------------------------------|----|

| 7.1 USB to RS232 bridge                                                    |    |

| 7.2 USB to RS485 Bridge                                                    |    |

| 7.3 Battery-operated, bus-powered USB to MCU with battery charge detection |    |

| 7.4 CAPSENSE™                                                              |    |

| 7.5 USB to I <sup>2</sup> C bridge                                         | 32 |

| 7.6 USB to SPI Bridge                                                      | 33 |

| 8 Ordering information                                                     | 38 |

| 8.1 Ordering code definitions                                              | 38 |

| 9 Package information                                                      | 39 |

| 10 Acronyms                                                                |    |

| 11 More information                                                        | 42 |

| 12 Document conventions                                                    | 43 |

| 12.1 Units of measure                                                      | 43 |

| 13 Errata                                                                  | 44 |

| Revision history                                                           | 47 |

Functional description

# 1 Functional description

### **USB-compliant**

The USB-Serial Single-Channel Bridge with CAPSENSE™ and BCD (CY7C65211/CY7C65211A) is fully compliant with the USB 2.0 specification and Battery Charging Specification v1.2, USB-IF Test-ID (TID) 40001521.

# 1.1 CY7C65211 and CY7C65211A features comparison

Table 1 CY7C65211 and CY7C65211A features comparison

| Features         | CY7C65211                                                  | CY7C65211A                                                 |

|------------------|------------------------------------------------------------|------------------------------------------------------------|

| USB Product ID   | 0x002                                                      | 0x00FB                                                     |

| UART             | Can be configured as Virtual COM port or USB vendor device | Can be configured as Virtual COM port or USB vendor device |

| I <sup>2</sup> C | Can be configured as USB vendor device                     | Can be configured as Virtual COM port or USB vendor device |

| SPI              | Can be configured as USB vendor device                     | Can be configured as Virtual COM port or USB vendor device |

| RS485 Support    | No                                                         | Yes                                                        |

Block diagram

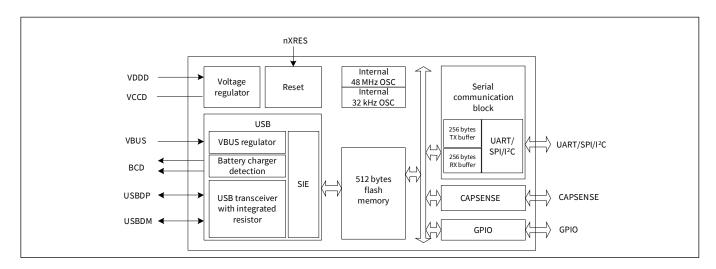

# 2 Block diagram

infineon

**Functional overview**

## 3 Functional overview

CY7C65211/CY7C65211A is a full-speed USB controller that enables seamless PC connectivity for peripherals with serial interfaces, such as UART, SPI, and I<sup>2</sup>C. CY7C65211/CY7C65211A also integrates CAPSENSE™ and BCD-compliant with the USB battery charging specification, rev. 1.2. It integrates a voltage regulator, an oscillator, and flash memory for storing configuration parameters, offering a cost-effective solution. CY7C65211 supports bus-powered and self-powered modes and enables efficient system power management with suspend and remote wake-up signals. It is available in a 24-pin QFN package.

## 3.1 USB and charger detect

### 3.1.1 USB

CY7C65211/CY7C65211A has a built-in USB 2.0 full-speed transceiver. The transceiver incorporates the internal USB series termination resistors on the USB data lines and a 1.5 k $\Omega$  pull-up resistor on USBDP.

## 3.1.2 Charger detection

CY7C65211/CY7C65211A supports BCD for peripheral detect only and complies with the USB battery charging specification, rev. 1.2. It supports the following charging ports:

- Standard downstream port (SDP): Allows the system to draw up to 500 mA current from the host

- Charging downstream port (CDP): Allows the system to draw up to 1.5 A current from the host

- Dedicated charging port (DCP): Allows the system to draw up to 1.5 A of current from the wall charger

### 3.2 Serial communication

CY7C65211/CY7C65211A has a serial communication block (SCB). Each SCB can implement UART, SPI, or I<sup>2</sup>C interface. A 256-byte buffer is available in both the TX and RX lines.

### 3.2.1 UART interface

The UART interface provides asynchronous serial communication with other UART devices operating at speeds of up to 3 Mbps. It supports 7 to 8 data bits, 1 to 2 stop bits, odd, even, mark, space, and no parity. The UART interface supports full-duplex communication with a signaling format that is compatible with the standard UART protocol. In CY7C65211, UART pins may be interfaced to industry standard RS232/RS422 transceivers whereas in CY7C65211A these UART pins may be interfaced to RS232/RS422/RS485.

Common UART functions, such as parity error and frame error, are supported. CY7C65211/CY7C65211A supports baud rates ranging from 300 baud to 3 Mbaud. The UART baud rates can be set using the configuration utility.

### **Notes:**

- Parity error gets detected when UART transmitter device is configured for odd parity and UART receiver device is configured for even parity.

- Frame error gets detected when UART transmitter device is configured for 7 bits data width and 1 stop bit, whereas UART receiver device is configured for 8 bit data width and 2 stop bits.

**Functional overview**

### 3.2.2 UART flow control

CY7C65211 device supports UART hardware flow control using control signal pairs, such as request to send (RTS) / clear to send (CTS) and data terminal ready (DTR) / data set ready (DSR). Data flow control is enabled by default. Flow control can be disabled using the configuration utility.

The following section describes the flow control signals:

• CTS# (input) / RTS# (output)

CTS# can pause or resume data transmission over the UART interface. Data transmission can be paused by de-asserting the CTS signal and resumed with CTS# assertion. The pause and resume operation does not affect data integrity. With flow control enabled, receive buffer has a watermark level of 93%. After the data in the receive buffer reaches that level, the RTS# signal is de-asserted, instructing the transmitting device to stop data transmission. The start of data consumption by application reduces the device data backlog; when it reaches the 75% watermark level, the RTS# signal is asserted to resume data reception.

• DSR# (input) /DTR# (output)

The DSR#/DTR# signals are used to establish a communication link with the UART. These signals complement each other in their functionality, similar to CTS# and RTS#.

### 3.2.3 SPI interface

The SPI interface supports an SPI master and SPI slave. This interface supports the Motorola, TI, and National Microwire protocols. The maximum frequency of operation is 3 MHz in SPI master mode and 1 MHz in SPI slave mode. It can support transaction sizes ranging from 4 bits to 16 bits in length, SPI slave supports 4 bits to 8 bits and 12 bits to 16 bits data width at 1 MHz operation. Whereas, it supports 9 bits,10 bits and 11 bits data width operation at 500 kHz operation. (see "USB to SPI Bridge" on page 33 for more details).

## 3.2.4 I<sup>2</sup>C interface

The  $I^2C$  interface implements full multi-master/slave modes and supports up to 400 kHz. The configuration utility tool is used to set the  $I^2C$  address in the slave mode. The tool enables only even slave addresses. For further details on the protocol, refer to the NXP  $I^2C$  specification, rev. 5.

### **Notes:**

- 1<sup>2</sup>C ports are not tolerant of higher voltages. Therefore, they cannot be hot-swapped or powered up independently when chip is not powered.

- The minimum fall time of the SCL is met (as per NXP I2C specification rev. 5) when V<sub>DDD</sub> is between 1.71 V and 3.0 V. When V<sub>DDD</sub> is within the range of 3.0 V to 3.6 V, it is recommended to add a 50 pF capacitor on the SCL signal.

infineon

**Functional overview**

## 3.3 CAPSENSE™

CAPSENSE™ functionality is supported on all the GPIO pins. Any GPIO pin can be configured as a sense pin (CS0–CS7) using the configuration utility. When implementing CAPSENSE™ functionality, the GPIO\_0 pin (configured as a modulator capacitor - Cmod) should be connected to ground through a 2.2 nF capacitor (see **Figure 13**).

CY7C65211 supports smart sensing algorithm for Auto-Tuning of the CAPSENSE™ parameters and does not require manual tuning. Smart sensing algorithm for Auto-tuning compensates for printed circuit board (PCB) variations and device process variations.

Optionally, any GPIO pin can be configured as a Cshield and connected to the shield of the CAPSENSE™ button, as shown in **Figure 13**. Shield prevents false triggering of buttons due to water droplets and guarantees CAPSENSE™ operation (sensors respond to finger touch).

GPIOs can be linked to the CAPSENSE™ buttons to indicate the presence of a finger. CAPSENSE™ functionality can be configured using the configuration utility.

CY7C65211 supports up to five CAPSENSE™ buttons. For more information on CAPSENSE™, see **Getting Started** with CAPSENSE™.

### 3.4 GPIO interface

CY7C65211/CY7C65211A has ten GPIOs. The maximum available GPIOs for configuration is ten if one two-pin (I2C/2-pin UART) serial interface is implemented. The configuration utility allows configuration of the GPIO pins. The configurable options are as follows:

- · TRISTATE: GPIO tristated

- DRIVE 1: Output static 1

- DRIVE 0: Output static 0

- POWER#: Power control for bus power designs

- TXLED#: Drives LED during USB transmit

- RXLED#: Drives LED during USB receive

- TX or RX LED#: Drives LED during USB transmit or receive

GPIO can be configured to drive LED at 8 mA drive strength.

- BCD0/BCD1: Two-pin output to indicate the type of USB charger

- BUSDETECT: Connects the VBUS pin for USB host detection

- CS0–CS4: CAPSENSE™ button input (sense pin)

- CSout0-CSout2: Indicates which CapSense button is pressed

- Cmod: External modulator capacitor; connects a 2.2 nF capacitor (±10%) to ground (GPIO\_0 only)

- · Cshield: Shield for waterproofing

## 3.5 Memory

CY7C65211/CY7C65211A has a 512-byte flash. Flash is used to store USB parameters, such as VID/PID, serial number, product and manufacturer descriptors, which can be programmed by the configuration utility.

**Functional overview**

## 3.6 System resources

## 3.6.1 Power system

CY7C65211/CY7C65211A supports the USB Suspend mode to control power usage. CY7C65211 operates in bus-powered or self-powered modes over a range of 3.15 V to 5.5 V.

## 3.6.2 Clock system

CY7C65211/CY7C65211A has a fully integrated clock with no external components required. The clock system is responsible for providing clocks to all subsystems.

### 3.6.3 Internal 48-MHz oscillator

The internal 48-MHz oscillator is the primary source of internal clocking in CY7C65211.

### 3.6.4 Internal 32-kHz oscillator

The internal 32-kHz oscillator is primarily used to generate clocks for peripheral operation in the USB suspend mode.

### 3.6.5 Reset

The reset block ensures reliable power-on reset and brings the device back to the default known state. The nXRES (active low) pin can be used by the external devices to reset the CY7C65211/CY7C65211A.

## 3.7 Suspend and resume

CY7C65211/CY7C65211A device asserts the SUSPEND pin when the USB bus enters the suspend state. This helps in meeting the stringent suspend current requirement of the USB 2.0 specification, while using the device in bus-powered mode. The device resumes from the suspend state under either of the two following conditions:

- · Any activity is detected on the USB bus

- The WAKEUP pin is asserted to generate remote wakeup to the host

## 3.8 Wakeup

The WAKEUP pin is used to generate the remote wakeup signal on the USB bus. The remote wakeup signal is sent only if the host enables this feature through the SET\_FEATURE request. The device communicates support for the remote wakeup to the host through the configuration descriptor during the USB enumeration process. CY7C65211/CY7C65211A device allows enabling/disabling and polarity of the remote wakeup feature through the configuration utility.

infineon

**Functional overview**

### 3.9 Software

Infineon delivers a complete set of software drivers and a configuration utility to enable configuration of the product during system development.

## 3.9.1 Drivers for Linux operating systems

Infineon provides a User Mode USB driver library (*libcyusbserial.so*) that abstracts vendor commands for the UART interface and provides a simplified API interface for user applications. This library uses the standard open-source libUSB library to enable USB communication. The Cypress serial library supports the USB plug-and-play feature using the Linux 'udev' mechanism.

CY7C65211/CY7C65211A supports the standard USB CDC UART class driver, which is bundled with the Linux kernel.

## 3.9.2 Android support

CY7C65211/CY7C65211A solution includes an Android Java class–CyUsbSerial.java–which exposes a set of interface functions to communicate with the device.

## 3.9.3 Drivers for Mac OSx

Infineon delivers a dynamically linked shared library (*CyUSBSerial.dylib*) based on libUSB, which enables communication to the CY7C65211 device.

In addition, the CY7C65211 device also supports the native Mac OSx CDC UART driver, and CY7C65211A supports native Mac OSx CDC UART/SPI/I2C driver.

## 3.9.4 Drivers for Windows operating systems

For Windows operating systems (XP, Vista, Win7, Win 8, and Win 8.1), Infineon delivers a user-mode dynamically linked library–CyUSBSerial DLL–that abstracts a vendor-specific interface of the CY7C65211/CY7C65211A devices and provides convenient APIs to the user. It provides interface APIs for vendor-specific UART/SPI/I2C and class-specific APIs for PHDC.

USB-Serial Bridge Controller works with the Windows-standard USB CDC class driver, when either CY7C65211 is configured as CDC USB to UART device or when CY7C65211A is configured as CDC USB to UART/SPI/I2C device. A virtual COM port driver-CyUSBSerial.sys-is also delivered, which implements the USB CDC class driver. The Infineon Windows drivers are Windows hardware certification kit-compliant.

These drivers are bound to device through WU (Windows Update) services.

Infineon drivers also support Windows plug-and-play and power management and USB remote wake-up.

## 3.9.5 Windows-CE support

CY7C65211/CY7C65211A solution includes a CDC UART driver library for Windows-CE platforms.

### **Device configuration utility (Windows only)**

A Windows-based configuration utility is available to configure device initialization parameters. This graphical user application provides an interactive interface to define the boot parameters stored in the device flash.

This utility allows the user to save a user-selected configuration to text or xml formats. It also allows users to load a selected configuration from text or xml formats. The configuration utility allows the following operations:

- · View current device configuration

- Select and configure UART/I2C/SPI, CAPSENSE™, battery charging, and GPIOs

- · Configure USB VID, PID, and string descriptors

- · Save or Load configuration

You can download the free configuration utility and drivers at www.infineon.com.

**Functional overview**

# 3.10 Internal flash configuration

The internal flash memory can be used to store the configuration parameters shown in the following table. A free configuration utility is provided to configure the parameters listed in the table to meet application-specific requirements over the USB interface. The configuration utility can be downloaded at www.infineon.com/usbserial.

Table 2 Internal flash configuration for both CY7C65211 and CY7C65211A

| Parameter                 | Default value                                        | Description                                                                                                     |

|---------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| USB configuration         | 1                                                    |                                                                                                                 |

| USB vendor ID (VID)       | 0x04B4                                               | Default Infineon VID. Can be configured to customer VID.                                                        |

| USB product ID<br>(PID)   | 0x0002 for CY7C65211<br>and<br>0x00FB for CY7C65211A | Default Infineon PID. Can be configured to customer PID.                                                        |

| Manufacturer string       | Infineon                                             | Can be configured with any string up-to 64 characters.                                                          |

| Product string            | USB-Serial (single channel)                          | Can be configured with any string up-to 64 characters.                                                          |

| Serial string             |                                                      | Can be configured with any string up-to 64 characters.                                                          |

| Power mode                | Bus powered                                          | Can be configured to bus-powered or self-powered mode.                                                          |

| Max current draw          | 100 mA                                               | Can be configured to any value from 0 mA to 500 mA. The configuration descriptor will be updated based on this. |

| Remote wakeup             | Enabled                                              | Can be disabled. Remote wakeup is initiated by asserting the WAKEUP pin.                                        |

| USB interface protocol    | CDC                                                  | Can be configured to function in CDC, PHDC, or Infineon vendor class.                                           |

| BCD                       | Disabled                                             | Charger detect is disabled by default. When BCD is enabled, three of the GPIOs must be configured for BCD.      |

| <b>GPIO</b> configuration |                                                      |                                                                                                                 |

| GPIO_0                    | TXLED#                                               |                                                                                                                 |

| GPIO_1                    | RXLED#                                               |                                                                                                                 |

| GPIO_2                    | DSR#                                                 |                                                                                                                 |

| GPIO_3                    | RTS#                                                 |                                                                                                                 |

| GPIO_4                    | CTS#                                                 |                                                                                                                 |

| GPIO_5                    | TxD                                                  | CDIO can be configured as shown in Table 19                                                                     |

| GPIO_6                    | RxD                                                  | GPIO can be configured as shown in <b>Table 18</b> .                                                            |

| GPIO_7                    | DTR#                                                 |                                                                                                                 |

| GPIO_8                    | TRISTATE                                             |                                                                                                                 |

| GPIO_9                    | TRISTATE                                             |                                                                                                                 |

| GPIO_10                   | TRISTATE                                             |                                                                                                                 |

| GPIO_11                   | POWER#                                               |                                                                                                                 |

**Electrical specifications**

# 4 Electrical specifications

# 4.1 Absolute maximum ratings

Exceeding maximum ratings<sup>[1]</sup> may shorten the useful life of the device.

Table 3 Absolute maximum ratings

| Parameter                                                        | Maximum ratings          |

|------------------------------------------------------------------|--------------------------|

| Storage temperature (Industrial, commercial)                     | -55°C to +100°C          |

| Storage temperature (Automotive)                                 | -55°C to +150°C          |

| Ambient temperature with power supplied (Industrial, commercial) | -40°C to +85°C           |

| Ambient temperature with power supplied (Automotive)             | -40°C to +105°C          |

| Supply voltage to ground potential                               |                          |

| $V_{DDD}$                                                        | 6.0 V                    |

| $V_{BUS}$                                                        | 6.0 V                    |

| $V_{CCD}$                                                        | 1.95 V                   |

| $V_{GPIO}$                                                       | V <sub>DDD</sub> + 0.5 V |

| Static discharge voltage ESD protection levels:                  |                          |

| HBM per JESD22-A114                                              | 2.2 kV                   |

| Latch-up current                                                 | 140 mA                   |

| Current per GPIO                                                 | 25 mA                    |

# 4.2 Operating conditions

Table 4 Operating conditions

| Parameter                                       | Operating conditions |

|-------------------------------------------------|----------------------|

| T <sub>A</sub> (ambient temperature under bias) |                      |

| Industrial                                      | -40°C to +85°C       |

| Automotive                                      | -40°C to +105°C      |

| V <sub>BUS</sub> supply voltage                 | 3.15 V to 5.25 V     |

| V <sub>DDD</sub> supply voltage                 | 1.71 V to 5.50 V     |

| V <sub>CCD</sub> supply voltage                 | 1.71 V to 1.89 V     |

### Note

<sup>1.</sup> Usage above the absolute maximum conditions may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods of time may affect device reliability. When used below absolute maximum conditions but above normal operating conditions, the device may not operate to specification.

**Electrical specifications**

# 4.3 Device-level specifications

All specifications are valid for:

Industrial: -40°C  $\leq$   $T_A \leq$  85°C,  $T_J \leq$  100°C, and 1.71 V to 5.50 V, except where noted.

Automotive:  $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 105^{\circ}\text{C}$ ,  $\text{T}_{\text{J}} \le 120^{\circ}\text{C}$ , and 1.71 V to 5.50 V, except where noted.

Table 5 DC specifications

| Table 5 De specifications |                                   |      |      |      |      |                                                                                                                                                  |  |  |  |

|---------------------------|-----------------------------------|------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter                 | Description                       | Min  | Тур  | Max  | Unit | <b>Details/conditions</b>                                                                                                                        |  |  |  |

|                           |                                   | 3.15 | 3.30 | 3.45 | V    | Set and configure the correct                                                                                                                    |  |  |  |

| $V_{BUS}$                 | V <sub>BUS</sub> supply voltage   | 4.35 | 5.00 | 5.25 | V    | voltage range using a configuration utility for V <sub>BUS</sub> .  Default 5 V.                                                                 |  |  |  |

|                           |                                   | 1.71 | 1.80 | 1.89 | V    | Used to set I/O and core                                                                                                                         |  |  |  |

| $V_{DDD}$                 | V <sub>DDD</sub> supply voltage   | 2.0  | 3.3  | 5.5  | V    | voltage. Set and configure the correct voltage range using a configuration utility for V <sub>DDD</sub> . Default 3.3 V.                         |  |  |  |

|                           | Output voltage (for core          |      |      |      |      | Do not use this supply to drive the external device.  • 1.71 V ≤ V <sub>DDD</sub> ≤ 1.89 V: Short                                                |  |  |  |

| V <sub>CCD</sub> logic)   |                                   | -    | 1.80 | _    | V    | the $V_{CCD}$ pin with the $V_{DDD}$ pin<br>• $V_{DDD} > 2 V$ – connect a 1- $\mu$ F<br>capacitor (Cefc) between the<br>$V_{CCD}$ pin and ground |  |  |  |

| Cefc                      | External regulator voltage bypass | 1.00 | 1.30 | 1.60 | μF   | X5R ceramic or better                                                                                                                            |  |  |  |

| I <sub>DD1</sub>          | Operating supply current          | _    | 20   | _    | mA   | USB 2.0 FS, UART at 1-Mbps single channel, no GPIO switching.                                                                                    |  |  |  |

| I <sub>DD2</sub>          | USB Suspend supply current        | -    | 5    | -    | μА   | Does not include current through a pull-up resistor on USBDP. In USB Suspend mode, the D+voltage can go up to a maximum of 3.8 V.                |  |  |  |

Table 6 AC specifications

| Parameter | Description                     | Min | Тур | Max | Unit | Details/conditions |

|-----------|---------------------------------|-----|-----|-----|------|--------------------|

| Zout      | USB driver output impedance     | 28  | _   | 44  | W    | -                  |

| Twakeup   | Wakeup from USB<br>Suspend mode | _   | 25  | _   | μs   | -                  |

**Electrical specifications**

# 4.3.1 GPIO

Table 7 GPIO DC specifications

| Parameter                      | Description                                         | Min                     | Тур | Max                  | Unit | <b>Details/conditions</b>                                   |

|--------------------------------|-----------------------------------------------------|-------------------------|-----|----------------------|------|-------------------------------------------------------------|

| V <sub>IH</sub> <sup>[2]</sup> | Input voltage high threshold                        | $0.7 \times V_{DDD}$    | _   | _                    | V    | CMOS input                                                  |

| V <sub>IL</sub>                | Input voltage low threshold                         | -                       | -   | 0.3×V <sub>DDD</sub> | V    | CMOS input                                                  |

| V <sub>IH</sub> <sup>[2]</sup> | LVTTL input, V <sub>DDD</sub> < 2.7 V               | $0.7 \times V_{DDD}$    | -   | _                    | V    | _                                                           |

| $V_{IL}$                       | LVTTL input, V <sub>DDD</sub> < 2.7V                | _                       | -   | $0.3 \times V_{DDD}$ | V    | _                                                           |

| V <sub>IH</sub> <sup>[2]</sup> | LVTTL input, V <sub>DDD</sub> ≥ 2.7V                | 2                       | -   | _                    | V    | -                                                           |

| V <sub>IL</sub>                | LVTTL input, V <sub>DDD</sub> ≥ 2.7V                | _                       | -   | 0.8                  | ٧    | -                                                           |

| V <sub>OH</sub>                | CMOS output voltage high level                      | V <sub>DDD</sub> - 0.4  | _   | _                    | V    | I <sub>OH</sub> = 4 mA,<br>V <sub>DDD</sub> = 5 V +/- 10%   |

| V <sub>OH</sub>                | CMOS output voltage high level                      | V <sub>DDD</sub> - 0.6  | _   | _                    | V    | I <sub>OH</sub> = 4 mA,<br>V <sub>DDD</sub> = 3.3 V +/- 10% |

| V <sub>OH</sub>                | CMOS output voltage high level                      | V <sub>DDD</sub> – 0.5  | -   | _                    | V    | I <sub>OH</sub> = 1 mA,<br>V <sub>DDD</sub> = 1.8 V +/- 5%  |

| V <sub>OL</sub>                | CMOS output voltage low level                       | -                       | _   | 0.4                  | V    | I <sub>OL</sub> = 8 mA,<br>V <sub>DDD</sub> = 5 V +/- 10%   |

| V <sub>OL</sub>                | CMOS output voltage low level                       | -                       | _   | 0.6                  | V    | I <sub>OL</sub> = 8 mA,<br>V <sub>DDD</sub> = 3.3 V +/- 10% |

| V <sub>OL</sub>                | CMOS output voltage low level                       | -                       | _   | 0.6                  | V    | I <sub>OL</sub> = 4 mA,<br>V <sub>DDD</sub> = 1.8 V +/- 5%  |

| Rpullup                        | Pull-up resistor                                    | 3.5                     | 5.6 | 8.5                  | kΩ   | _                                                           |

| Rpulldown                      | Pull-down resistor                                  | 3.5                     | 5.6 | 8.5                  | kΩ   | _                                                           |

| I <sub>IL</sub>                | Input leakage current (absolute value)              | -                       | _   | 2                    | nA   | 25°C, V <sub>DDD</sub> = 3.0 V                              |

| C <sub>IN</sub>                | Input capacitance                                   | _                       | -   | 7                    | pF   | _                                                           |

| Vhysttl                        | Input hysteresis LVTTL;<br>V <sub>DDD</sub> > 2.7 V | 25                      | 40  | С                    | mV   | -                                                           |

| Vhyscmos                       | Input hysteresis CMOS                               | 0.05 × V <sub>DDD</sub> | -   | _                    | mV   | _                                                           |

### Note

2. V<sub>IH</sub> must not exceed V<sub>DDD</sub> + 0.2 V.

**Electrical specifications**

Table 8 GPIO AC specifications

| Parameter              | Description            | Min | Тур | Max | Unit | Details/conditions                                |

|------------------------|------------------------|-----|-----|-----|------|---------------------------------------------------|

| T <sub>RiseFast1</sub> | Rise Time in Fast mode | 2   | _   | 12  | ns   | V <sub>DDD</sub> = 3.3 V/ 5.5 V,<br>Cload = 25 pF |

| T <sub>FallFast1</sub> | Fall Time in Fast mode | 2   | _   | 12  | ns   | V <sub>DDD</sub> = 3.3 V/ 5.5 V,<br>Cload = 25 pF |

| T <sub>RiseSlow1</sub> | Rise Time in Slow mode | 10  | _   | 60  | ns   | V <sub>DDD</sub> = 3.3 V/ 5.5 V,<br>Cload = 25 pF |

| T <sub>FallSlow1</sub> | Fall Time in Slow mode | 10  | _   | 60  | ns   | V <sub>DDD</sub> = 3.3 V/ 5.5 V,<br>Cload = 25 pF |

| T <sub>RiseFast2</sub> | Rise Time in Fast mode | 2   | _   | 20  | ns   | V <sub>DDD</sub> = 1.8 V, Cload = 25 pF           |

| T <sub>FallFast2</sub> | Fall Time in Fast mode | 20  | _   | 100 | ns   | V <sub>DDD</sub> = 1.8 V, Cload = 25 pF           |

| T <sub>RiseSlow2</sub> | Rise Time in Slow mode | 2   | _   | 20  | ns   | V <sub>DDD</sub> = 1.8 V, Cload = 25 pF           |

| T <sub>FallSlow2</sub> | Fall Time in Slow mode | 20  | _   | 100 | ns   | V <sub>DDD</sub> = 1.8 V, Cload = 25 pF           |

**Electrical specifications**

# 4.3.2 **nXRES**

Table 9 nXRES DC specifications

| Parameter       | Description                  | Min                  | Тур | Мах                  | Unit | <b>Details/conditions</b> |

|-----------------|------------------------------|----------------------|-----|----------------------|------|---------------------------|

| V <sub>IH</sub> | Input voltage high threshold | 0.7×V <sub>DDD</sub> | _   | _                    | V    | -                         |

| V <sub>IL</sub> | Input voltage low threshold  | -                    | -   | 0.3×V <sub>DDD</sub> | V    | -                         |

| Rpullup         | Pull-up resistor             | 3.5                  | 5.6 | 8.5                  | kΩ   | _                         |

| C <sub>IN</sub> | Input capacitance            | _                    | 5   | _                    | pF   | _                         |

| Vhysxres        | Input voltage hysteresis     | _                    | 100 | _                    | mV   | _                         |

# Table 10 nXRES AC specifications

| Parameter   | Description       | Min | Тур | Max | Unit | Details/conditions |

|-------------|-------------------|-----|-----|-----|------|--------------------|

| Tresetwidth | Reset pulse width | 1   | _   | _   | μs   | _                  |

**Electrical specifications**

# 4.4 Digital peripherals

## 4.4.1 **UART**

Table 11 UART AC specifications

| Parameter         | Description   | Min | Тур | Мах  | Unit | Details/conditions |

|-------------------|---------------|-----|-----|------|------|--------------------|

| F <sub>UART</sub> | UART bit rate | 0.3 | _   | 3000 | kbps | _                  |

## 4.4.2 SPI

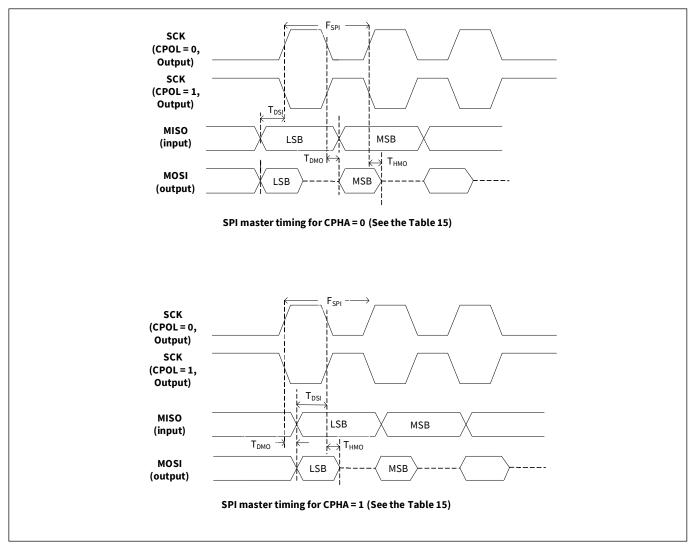

Figure 1 SPI master timing

**Electrical specifications**

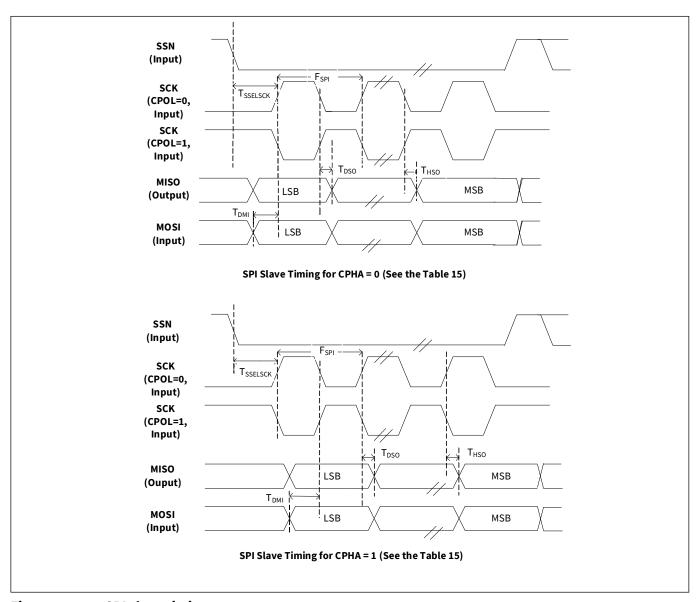

Figure 2 SPI slave timing

**Electrical specifications**

**SPI AC specifications** Table 12

| Parameter            | Description                                                          | Min | Тур | Max   | Unit | <b>Details/conditions</b> |

|----------------------|----------------------------------------------------------------------|-----|-----|-------|------|---------------------------|

| F <sub>SPI</sub>     | SPI operating frequency (Master/Slave)                               | _   | _   | 3     | MHz  | -                         |

| WL <sub>SPI</sub>    | SPI word length                                                      | 4   | _   | 16    | bits | _                         |

| SPI Master n         | node                                                                 |     |     | '     | '    |                           |

| T <sub>DMO</sub>     | MOSI valid after SClock driving edge                                 | _   | _   | 15    | ns   | -                         |

| T <sub>DSI</sub>     | MISO valid before SClock capturing edge                              | 20  | _   | _     | ns   | -                         |

| T <sub>HMO</sub>     | Previous MOSI data hold time with respect to capturing edge at slave | 0   | _   | _     | ns   | -                         |

| SPI Slave m          | ode                                                                  |     |     | '     |      |                           |

| T <sub>DMI</sub>     | MOSI valid before Sclock capturing edge                              | 40  | _   | -     | ns   | -                         |

| T <sub>DSO</sub>     | MISO valid after Sclock driving edge                                 | _   | _   | 104.4 | ns   | -                         |

| T <sub>HSO</sub>     | Previous MISO data hold time                                         | 0   | _   | _     | ns   | -                         |

| T <sub>SSELSCK</sub> | SSEL valid to first SCK Valid edge                                   | 100 | _   | -     | ns   | _                         |

### $I^2C$ 4.4.3

I<sup>2</sup>C AC specifications Table 13

| Parameter        | Description                | Min | Тур | Max | Unit | Details/conditions |

|------------------|----------------------------|-----|-----|-----|------|--------------------|

| F <sub>I2C</sub> | I <sup>2</sup> C frequency | 1   | _   | 400 | kHz  | _                  |

**Electrical specifications**

## 4.5 CAPSENSE™

## **Table 14** CAPSENSE™ AC specifications

| Parameter        | Description                        | Min  | Тур | Max  | Unit  | Details/conditions                                                                 |

|------------------|------------------------------------|------|-----|------|-------|------------------------------------------------------------------------------------|

| V <sub>CSD</sub> | Voltage range of operation         | 1.71 | _   | 5.50 | V     | -                                                                                  |

| SNR              | Ratio of counts of finger to noise | 5    | -   | -    | Ratio | Sensor capacitance range of 9 pF to 35 pF; finger capacitance ≥ 0.1 pF sensitivity |

# 4.6 System resources

# **4.6.1** Memory

## Table 15 Flash memory specifications

| Parameter | Description                                                         | Min  | Тур | Мах | Unit   | Details/conditions |

|-----------|---------------------------------------------------------------------|------|-----|-----|--------|--------------------|

| Fend      | Flash endurance                                                     | 100K | _   | _   | cycles | -                  |

| Fret      | Flash retention. T <sub>A</sub> ≤ 85°C,<br>10K program/erase cycles | 10   | _   | _   | years  | -                  |

Pin description

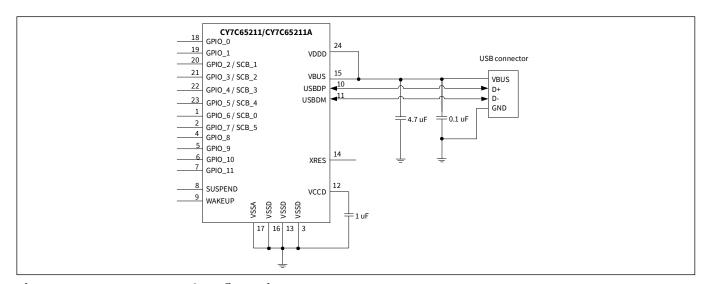

# 5 Pin description

Table 16 Pin description

| Pin <sup>[3]</sup> | Туре     | Name   |        | Defualt  | Description                                                                                                      |                                                                  |

|--------------------|----------|--------|--------|----------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 1                  | SCB/GPIO | SCB_0  | GPIO_6 | RxD      | SCB/GPIO. See <b>Table 17</b> and <b>Table 18</b> .                                                              |                                                                  |

| 2                  | SCB/GPIO | SCB_5  | GPIO_7 | DTR#     | SCB/GPIO. See <b>Table 17</b> and <b>Table 18</b> .                                                              | 9000<br>\$51,4600,5<br>\$52,7600,3<br>\$52,7600,3<br>\$52,7600,3 |

| 3                  | Power    | VSSD   | '      | -        | Digital ground                                                                                                   |                                                                  |

| 4                  | GPIO     | GPIO_8 |        | TRISTATE | GPIO. See <b>Table 18</b> .                                                                                      | SCB_0/GPIO_6 1 1 18 GPIO_<br>SCB_5/GPIO_7 2 CY7C65211/ 17 VSSA   |

| 5                  | GPIO     | GPIO_9 |        | TRISTATE | GPIO. See <b>Table 18</b> .                                                                                      | VSSD 3 CY7C65211A 16 VSSD                                        |

| 6                  | GPIO     | GPIO_1 | 0      | TRISTATE | GPIO. See <b>Table 18</b> .                                                                                      | GPIO_8 4 24-pin QFN 15 VBUS GPIO_9 5 Top view 14 MKR             |

| 7                  | GPIO     | GPIO_1 | 1      | POWER#   | GPIO. See <b>Table 18</b> .                                                                                      | GPIO_10 6                                                        |

| 8                  | Output   | SUSPEN | ID     | -        | Indicates device in suspend mode.<br>Can be configured as active<br>low/high using the configuration<br>utility. | TLOSS                                                            |

| 9                  | Input    | WAKEUI | P      | -        | Wakeup device from suspend mode. Can be configured as active low/high using the configuration utility.           |                                                                  |

| 10                 | USBIO    | USBDP  |        | -        | USB Data Signal Plus, integrates termination resistor and a 1.5-kΩ pull-up resistor                              |                                                                  |

| 11                 | USBIO    | USBDM  |        | _        | USB Data Signal Minus, integrates termination resistor                                                           |                                                                  |

| 12                 | Power    | VCCD   |        | -        | This pin should be decoupled to ground using a 1-µF capacitor or by connecting a 1.8-V supply.                   |                                                                  |

| 13                 | Power    | VSSD   |        | -        | Digital ground                                                                                                   |                                                                  |

| 14                 | nXRES    | nXRES  |        | -        | Chip reset, active low. Can be left unconnected or have a pull-up resistor connected if not used.                |                                                                  |

| 15                 | Power    | VBUS   |        | -        | VBUS Supply, 3.15 V to 5.25 V                                                                                    |                                                                  |

| 16                 | Power    | VSSD   |        | -        | Digital ground                                                                                                   |                                                                  |

| 17                 | Power    | VSSA   |        | -        | Analog ground                                                                                                    |                                                                  |

| 18                 | GPIO     | GPIO_0 |        | TXLED#   | GPIO. See <b>Table 18</b> .                                                                                      |                                                                  |

| 19                 | GPIO     | GPIO_1 |        | RXLED#   | GPIO. See <b>Table 18</b> .                                                                                      |                                                                  |

| 20                 | SCB/GPIO | SCB_1  | GPIO_2 | DSR#     | SCB/GPIO. See <b>Table 17</b> and <b>Table 18</b> .                                                              |                                                                  |

| 21                 | SCB/GPIO | SCB_2  | GPIO_3 | RTS#     | SCB/GPIO. See <b>Table 17</b> and <b>Table 18</b> .                                                              |                                                                  |

| 22                 | SCB/GPIO | SCB_3  | GPIO_4 | CTS#     | SCB/GPIO. See <b>Table 17</b> and <b>Table 18</b> .                                                              |                                                                  |

| 23                 | SCB/GPIO | SCB_4  | GPIO_5 | TxD      | SCB/GPIO. See <b>Table 17</b> and <b>Table 18</b> .                                                              |                                                                  |

| 24                 | Power    | VDDD   |        | _        | Supply to the device core and Interface, 1.71 V to 5.5 V                                                         |                                                                  |

|                    |          |        |        |          |                                                                                                                  | · · · · · · · · · · · · · · · · · · ·                            |

### Note

3. Any pin acting as an Input pin should not be left unconnected.

Pin description

Table 17 Serial communication block configuration

| Pin | Serial Port | Mode 0 <sup>[4]</sup> | Mode 1     | Mode 2     | Mode 3     | Mode 4    | Mode 5            | Mode 6           |

|-----|-------------|-----------------------|------------|------------|------------|-----------|-------------------|------------------|

|     |             | 6-pin UART            | 4-pin UART | 2-pin UART | SPI Master | SPI Slave | <b>I2C Master</b> | <b>I2C Slave</b> |

| 1   | SCB_0       | RxD                   | RxD        | RxD        | GPIO_6     | GPIO_6    | GPIO_6            | GPIO_6           |

| 20  | SCB_1       | DSR#                  | GPIO_2     | GPIO_2     | SSEL_OUT   | SSEL_IN   | GPIO_2            | GPIO_2           |

| 21  | SCB_2       | RTS#                  | RTS#       | GPIO_3     | MISO_IN    | MISO_OUT  | SCL_OUT           | SCL_IN           |

| 22  | SCB_3       | CTS#                  | CTS#       | GPIO_4     | MOSI_OUT   | MOSI_IN   | SDA               | SDA              |

| 23  | SCB_4       | TxD                   | TxD        | TxD        | SCLK_OUT   | SCLK_IN   | GPIO_5            | GPIO_5           |

| 2   | SCB_5       | DTR#                  | GPIO_7     | GPIO_7     | GPIO_7     | GPIO_7    | GPIO_7            | GPIO_7           |

### Note

Table 18 GPIO configuration

| <b>GPIO</b> configuration option   | Description                                                                                                                                                                                                                                                                                                        |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRISTATE                           | I/O tristated                                                                                                                                                                                                                                                                                                      |

| DRIVE 1                            | Output static 1                                                                                                                                                                                                                                                                                                    |

| DRIVE 0                            | Output static 0                                                                                                                                                                                                                                                                                                    |

| POWER#                             | This output is used to control power to an external logic through a switch to cut power off during an unconfigured USB device and USB Suspend.  0 - USB device in Configured state  1 - USB device in Unconfigured state or during USB Suspend mode                                                                |

| TXLED#                             | Drives LED during USB transmit                                                                                                                                                                                                                                                                                     |

| RXLED#                             | Drives LED during USB receive                                                                                                                                                                                                                                                                                      |

| TX or RX LED#                      | Drives LED during USB transmit or receive                                                                                                                                                                                                                                                                          |

| BCD0<br>BCD1                       | Configurable battery charger detect pins to indicate the type of USB charger (SDP, CDP, or DCP) Configuration example: 00 - Draw up to 100 mA (unconfigured state) 01 - SDP (up to 500 mA) 10 - CDP/DCP (up to 1.5 A) 11 - Suspend (up to 2.5 mA) This truth table can be configured using a configuration utility |

| BUSDETECT                          | VBUS detection. Connect the VBUS to this pin through a resistor network for VBUS detection when using the BCD feature.                                                                                                                                                                                             |

| CS0, CS1, CS2, CS3, CS4            | CAPSENSE™ button input (max up to 5)                                                                                                                                                                                                                                                                               |

| CSout0, CSout1, CSout2             | Indicates which CAPSENSE™ button is pressed                                                                                                                                                                                                                                                                        |

| CMOD<br>(Available on GPIO_0 only) | External modulator capacitor, connect a 2.2 nF capacitor (±10%) to ground                                                                                                                                                                                                                                          |

| Cshield (optional)                 | Shield for waterproofing                                                                                                                                                                                                                                                                                           |

**Note:** These signal options can be configured on any of the available GPIO pins using the configuration utility provided by Infineon.

<sup>4.</sup> The device is configured in Mode 0 as the default. Other modes can be configured using the configuration utility provided by Infineon.

**USB** power configurations

# 6 USB power configurations

The following section describes possible USB power configurations for the CY7C65211/CY7C65211A. See the "Pin description" on page 22 for signal details.

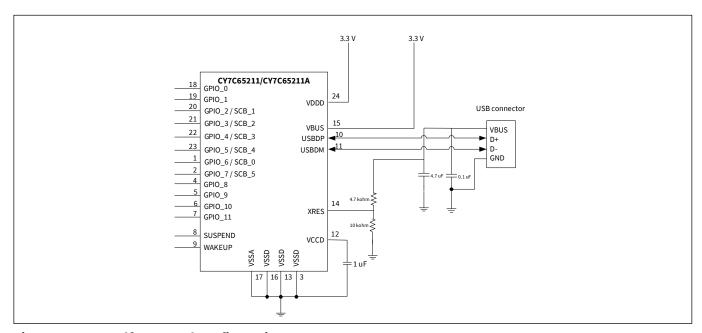

## 6.1 USB bus-powered configuration

**Figure 3** shows an example of the CY7C65211/CY7C65211A in a bus-powered design. The VBUS is connected directly to the CY7C65211 because it has an internal regulator.

The USB bus-powered system must comply with the following requirements:

- The system should not draw more than 100 mA prior to USB enumeration (Unconfigured state)

- The system should not draw more than 2.5 mA during the USB Suspend mode

- A high-power bus-powered system (can draw more than 100 mA when operational) must use POWER# (configured over GPIO) to keep the current consumption below 100 mA prior to USB enumeration, and 2.5 mA during USB Suspend state

- The system should not draw more than 500 mA from the USB host

The configuration descriptor in the CY7C65211/CY7C65211A flash should be updated to indicate bus power and the maximum current required by the system using the configuration utility.

Figure 3 Bus-powered configuration

**USB** power configurations

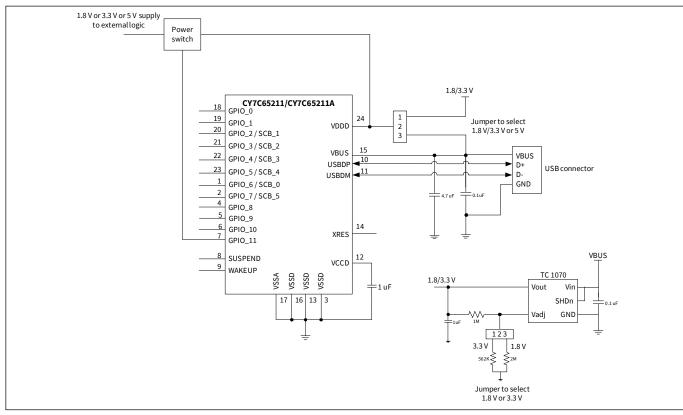

## 6.2 Self-powered configuration

**Figure 4** shows an example of CY7C65211/CY7C65211A in a self-powered design. A self-powered system does not use the VBUS from the host to power the system, but it has its own power supply. A self-powered system has no restriction on current consumption because it does not draw any current from the VBUS.

When the VBUS is present, CY7C65211/CY7C65211A enables an internal, 1.5-k $\Omega$  pull-up resistor on USBDP. When the VBUS is absent (USB host is powered down), CY7C65211/CY7C65211A removes the 1.5-k $\Omega$  pull-up resistor on USBDP. This ensures that no current flows from the USBDP to the USB host through a 1.5-k $\Omega$  pull-up resistor, to comply with the USB 2.0 specification.

When reset is asserted to CY7C65211/CY7C65211A, all the I/O pins are tristated.

The configuration descriptor in the CY7C65211/CY7C65211A flash should be updated to indicate self-power using the configuration utility.

Figure 4 Self-powered configuration

**USB** power configurations

## 6.3 USB bus-powered with variable I/O voltage

**Figure 5** shows CY7C65211/CY7C65211A in a bus-powered system with variable I/O voltage. A low dropout (LDO) regulator is used to supply 1.8 V or 3.3 V, using a jumper switch the input of which is 5 V from the VBUS. Another jumper switch is used to select 1.8/3.3 V or 5 V from the VBUS for the VDDD pin of CY7C65211. This allows I/O voltage and supply to external logic to be selected among 1.8 V, 3.3 V, or 5 V.

The USB bus-powered system must comply with the following conditions:

- The system should not draw more than 100 mA prior to USB enumeration (unconfigured state)

- The system should not draw more than 2.5 mA during USB Suspend mode

- A high-power bus-powered system (can draw more than 100 mA when operational) must use POWER# (configured over GPIO) to keep the current consumption below 100 mA prior to USB enumeration and 2.5 mA during the USB Suspend state

Figure 5 USB bus-powered with 1.8-V, 3.3-V, or 5-V variable I/O voltage [5]

### Note

5. 1.71 V ≤ VDDD ≤ 1.89 V - Short VCCD pin with VDDD pin; VDDD > 2 V - connect a 1-μF decoupling capacitor to the VCCD pin.

Application examples

#### **Application examples** 7

The following section provides CY7C65211/CY7C65211A application examples.

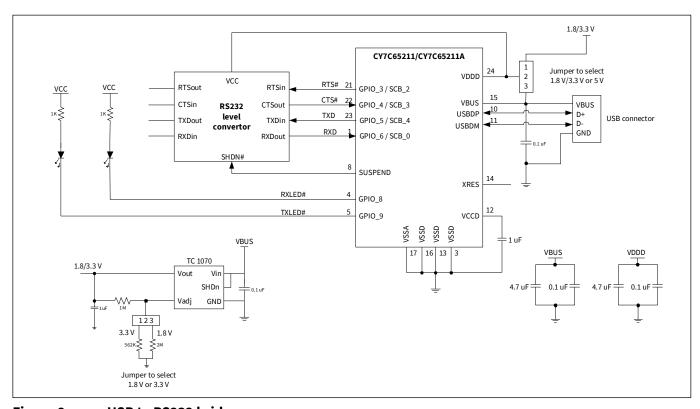

#### **USB to RS232 bridge** 7.1

CY7C65211/CY7C65211A can connect any embedded system, with a serial port, to a host PC through USB. CY7C65211/CY7C65211A enumerates as a COM port on the host PC.

The RS232 protocol follows bipolar signaling – that is, the output signal toggles between negative and positive polarity. The valid RS232 signal is either in the -3 V to -15 V range or in the +3 V to +15 V range, and the range between -3 V to +3 V is invalid. In the RS232, Logic 1 is called "Mark" and it corresponds to a negative voltage range. Logic 0 is called "Space" and it corresponds to a positive voltage range. The RS232 level converter facilitates this polarity inversion and the voltage-level translation between the CY7C65211/CY7C65211A's UART interface and RS232 signaling.

In this application, as shown in Figure 6, SUSPEND is connected to the SHDN# pin of the RS232-level converter to indicate USB suspend or USB not enumerated.

GPIO8 and GPIO9 are configured as RXLED# and TXLED# to drive two LEDs, indicating data transmit and receive.

Figure 6 **USB to RS232 bridge**

**Application examples**

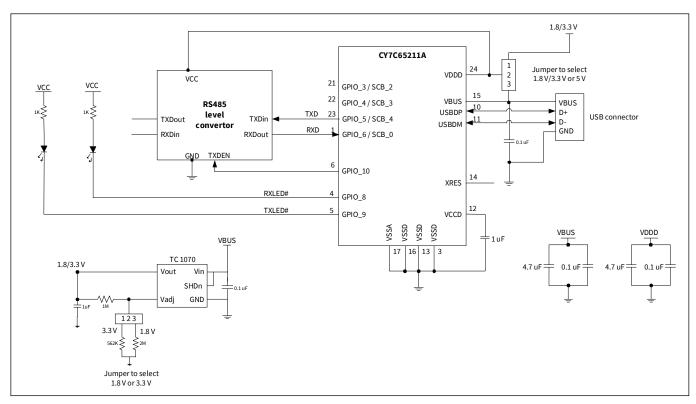

#### 7.2 **USB to RS485 Bridge**

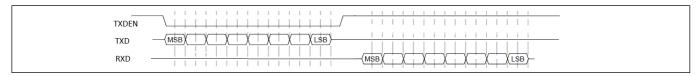

CY7C65211A can be configured as USB to UART interface. This UART interface operates at TTL level and it can be converted to RS485 interface using a GPIO and any half duplex RS485 transceiver IC (to convert TTL level to RS485 level) as shown in Figure 7. This GPIO (TXDEN) enables or disables the transmission of data through RS485 transceiver IC based on availability of character in UART buffer of CY7C65211A. This GPIO can be configured using Infineon USB-Serial Configuration utility. Figure 8 shows timing diagram of this GPIO.

RS485 is a multi-drop network – i.e., many devices can communicate with each other over a single two wire cable connection. The RS485 cable requires to be terminated at each end of the cable.

Figure 7 **USB to RS485 bridge**

Figure 8 RS485 GPIO (TXDEN) timing diagram

infineon

Application examples

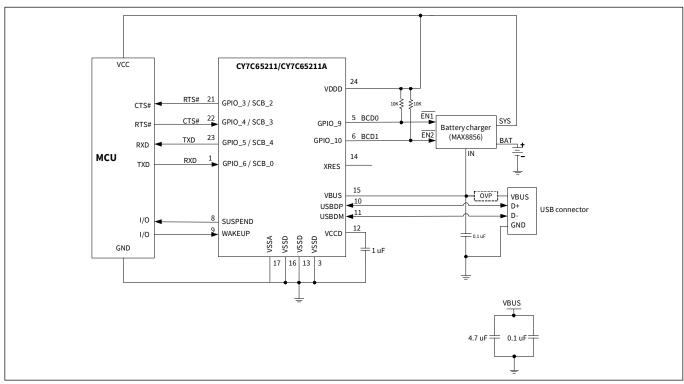

# 7.3 Battery-operated, bus-powered USB to MCU with battery charge detection

**Figure 9** illustrates CY7C65211/CY7C65211A as a USB-to-microcontroller interface. The TXD and RXD lines are used for data transfer, and the RTS# and CTS# lines are used for handshaking. The SUSPEND pin indicates to the MCU if the device is in USB Suspend, and the WAKEUP pin is used to wake up CY7C65211/CY7C65211A, which in turn issues a remote wakeup to the USB host.

This application illustrates a battery-operated system, which is bus-powered. CY7C65211/CY7C65211A implements the battery charger detection functionality based on the USB battery charging specification, rev. 1.2. Battery-operated bus power systems must comply with the following conditions:

- The system can be powered from the battery (if not discharged) and can be operational if the VBUS is not connected or powered down

- The system should not draw more than 100 mA from the VBUS prior to USB enumeration and USB Suspend

- The system should not draw more than 500 mA for SDP and 1.5 A for CDP/DCP

To comply with the first requirement, the VBUS from the USB host is connected to the battery charger as well as to CY7C65211, as shown in **Figure 9**. When the VBUS is connected, CY7C65211 initiates battery charger detection and indicates the type of USB charger over BCD0 and BCD1. If the USB charger is SDP or CDP, CY7C65211 enables a 1.5-K $\Omega$  pull-up resistor on the USBDP for Full-Speed enumeration. When the VBUS is disconnected, CY7C65211 indicates an absence of the USB charger over BCD0 and BCD1, and removes the 1.5-K $\Omega$  pull-up resistor on USBDP. Removing this resistor ensures that no current flows from the supply to the USB host through the USBDP, to comply with the USB 2.0 specification.

To comply with the second and third requirements, two signals (BCD0 and BCD1) are configured over GPIO to communicate the type of USB host charger and the amount of current it can draw from the battery charger. BCD0 and BCD1 signals can be configured using the configuration utility.

Figure 9 USB to MCU interface with battery charge detection [6]

### **Note**

6. Add a 100-k $\Omega$  pull-down resistor on the  $V_{BUS}$  pin for quick discharge.

Application examples

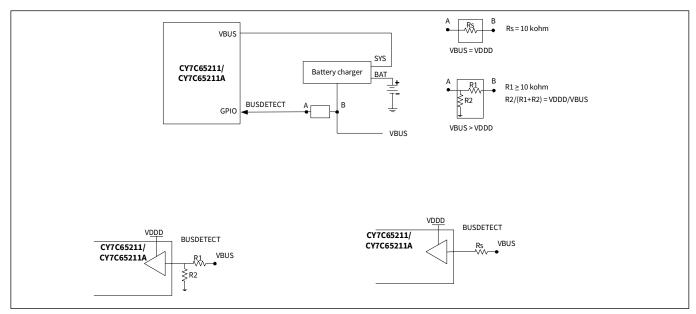

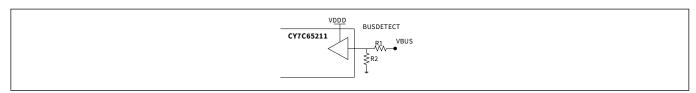

In a battery charger system, a 9 V spike on the VBUS is possible. The CY7C65211 VBUS pin is intolerant to voltage above 6 V. In the absence of over-voltage protection (OVP) on the VBUS line, the VBUS should be connected to BUSDETECT (GPIO configured) using the resistive network and the output of the battery charger to the VBUS pin of CY7C65211, as shown in **Figure 10**.

Figure 10 9 V tolerant

When the VBUS and VDDD are at the same voltage potential, the VBUS can be connected to the GPIO using a series resistor (Rs). This is shown in **Figure 11**. If there is a charger failure and the VBUS becomes 9 V, then the 10-k $\Omega$  resistor plays two roles. It reduces the amount of current flowing into the forward-biased diodes in the GPIO, and it reduces the voltage seen on the pad.

Figure 11 GPIO VBUS detection, VBUS = VDDD

When the VBUS > VDDD, a resistor voltage divider is required to reduce the voltage from the VBUS down to VDDD for the GPIO sensing the VBUS voltage. This is shown in **Figure 12**. The resistors should be sized as follows:

- R1  $\geq$  10 k $\Omega$

- R2 / (R1 + R2) = VDDD / VBUS

The first condition limits the voltage and current for the charger failure situation, as described in the previous paragraph, while the second condition allows for normal-operation VBUS detection.

Figure 12 GPIO VBUS detection, VBUS > VDDD

**Application examples**

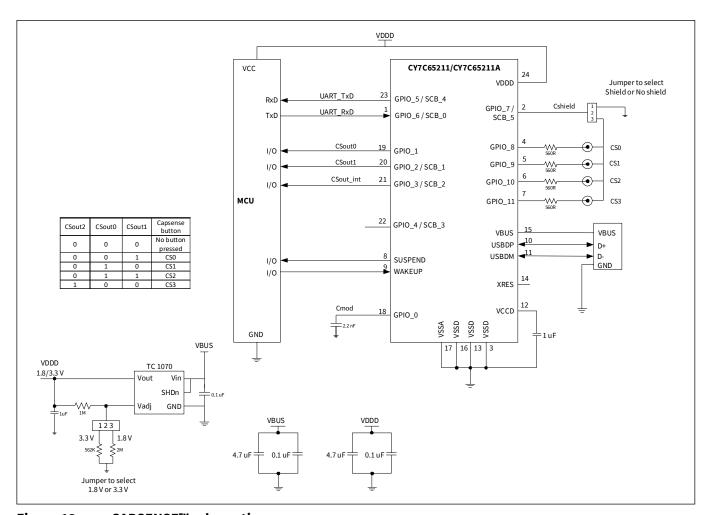

#### 7.4 **CAPSENSE™**

In Figure 13, CY7C65211 is configured to support four CAPSENSE™ buttons. Three GPIOs are configured to indicate which CAPSENSE™ button is pressed by the finger (as shown in the table next to the schematic). If two CAPSENSE™ buttons are implemented, then two GPIOs (CSout0 and CSout1) are configured to indicate which CAPSENSE™ button is pressed.

A 2.2 nF (10%) capacitor (Cmod) must be connected on the GPIO\_0 pin for proper CAPSENSE™ operation. Optionally, the GPIO 7 pin is configured as Cshield and connected to the shield of the CAPSENSE™ button, as shown in Figure 13.

Shield prevents false triggering of buttons due to water droplets, and guarantees CAPSENSE™ operation (the sensors respond to finger touch).

For further information on CAPSENSE™, see Getting started with CAPSENSE™.

**CAPSENSE™** schematic Figure 13

**Application examples**

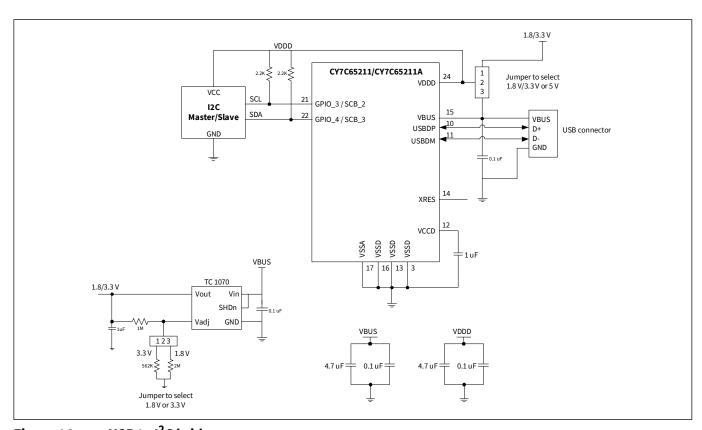

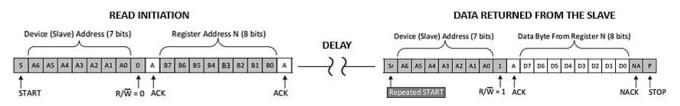

# 7.5 USB to I<sup>2</sup>C bridge

In **Figure 14**, CY7C65211 is configured as a USB to  $I^2C$  bridge. The CY7C65211  $I^2C$  can be configured as a master or a slave using the configuration utility. CY7C65211 supports  $I^2C$  data rates up to 100 kbps in the standard mode (SM) and 400 kbps in the fast mode (FM).

In the Master mode, SCL is output from CY7C65211. In the slave mode, SCL is input to CY7C65211. The I<sup>2</sup>C slave address for CY7C65211 can be configured using the configuration utility. The SDA data line is bi-directional in the master/slave modes. The drive modes of the SCL and SDA port pins are always open drain.

GPIO8 and GPIO9 are configured as RXLED# and TXLED# to drive two LEDs to indicate USB receive and transmit. See the NXP I<sup>2</sup>C specification for further details on the protocol.

Figure 14 USB to I<sup>2</sup>C bridge

**Application examples**

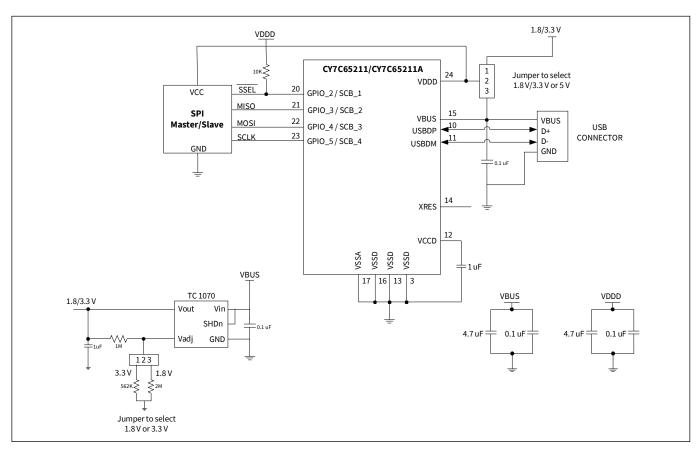

## 7.6 USB to SPI Bridge

In **Figure 15**, CY7C65211 is configured as a USB to SPI Bridge. The CY7C65211 SPI can be configured as a master or a slave using the configuration utility. CY7C65211 supports SPI master frequency up to 3 MHz and SPI slave frequency up to 1 MHz. It can support transaction sizes ranging from 4 bits to 16 bits, which can be configured using the configuration utility.

In the Master mode, the SCLK, MOSI, and SSEL lines act as outputs and MISO acts as an input. In the slave mode, the SCL SCLK, MOSI, and SSEL lines act as inputs and MISO acts as an output.

GPIO8 and GPIO9 are configured as RXLED# and TXLED# to drive two LEDs to indicate USB receive and transmit.

Figure 15 USB to SPI bridge

CY7C65211 supports three versions of the SPI protocol:

- Motorola This is the original SPI protocol.

- Texas Instruments A variation of the original SPI protocol in which the data frames are identified by a pulse on the SSEL line.

- National Semiconductors A half-duplex variation of the original SPI protocol.

Application examples

### Motorola

The original SPI protocol is defined by Motorola. It is a full-duplex protocol: transmission and reception occur at the same time.

A single (full-duplex) data transfer follows these steps: The master selects a slave by driving its SSEL line to '0'. It then drives the data on its MOSI line and it drives a clock on its SCLK line. The slave uses the edges of the transmitted clock to capture the data on the MOSI line. The slave drives data on its MISO line. The master captures the data on the MISO line. Repeat the process for all bits in the data transfer.

Multiple data transfers may happen without the SSEL line changing from '0' to '1' and back from '1' to '0' in between the individual transfers. As a result, slaves must keep track of the progress of data transfers to separate individual transfers.

When not transmitting data, the SSEL line is '1' and the SCLK is typically off.

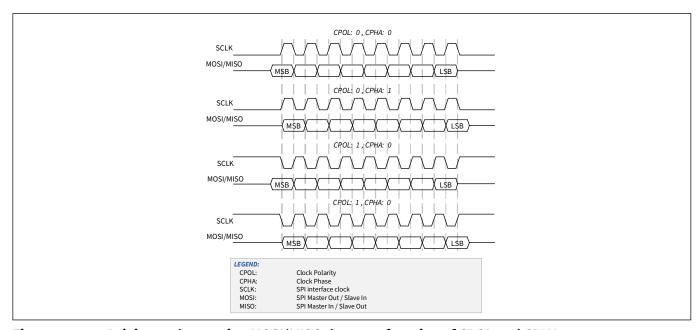

The Motorola SPI protocol has four modes that determine how data is driven and captured on the MOSI and MISO lines. These modes are determined by clock polarity (CPOL) and clock phase (CPHA). The clock polarity determines the value of the SCLK line when not transmitting data:

- CPOL is '0': SCLK is '0' when not transmitting data.

- CPOL is '1': SCLK is '1' when not transmitting data.

The clock phase determines when data is driven and captured. It is dependent on the value of CPOL:

Table 19 SPI protocol modes

| Mode | CPOL | СРНА | Description                                                                          |

|------|------|------|--------------------------------------------------------------------------------------|

| 0    | 0    | 0    | Data is driven on a falling edge of SCLK. Data is captured on a rising edge of SCLK. |

| 1    | 0    | 1    | Data is driven on a rising edge of SCLK. Data is captured on a falling edge of SCLK. |

| 2    | 1    | 0    | Data is driven on a rising edge of SCLK. Data is captured on a falling edge of SCLK. |

| 3    | 1    | 1    | Data is driven on a falling edge of SCLK. Data is captured on a rising edge of SCLK. |

Figure 16 Driving and capturing MOSI/MISO data as a function of CPOL and CPHA

Application examples

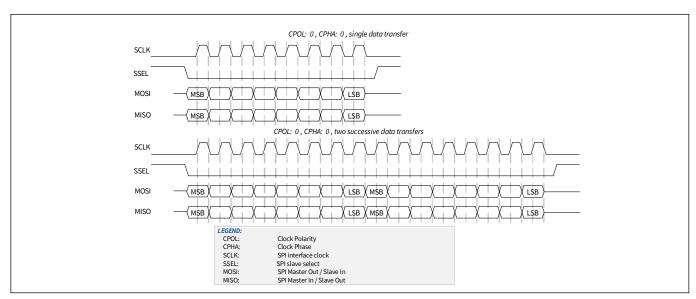

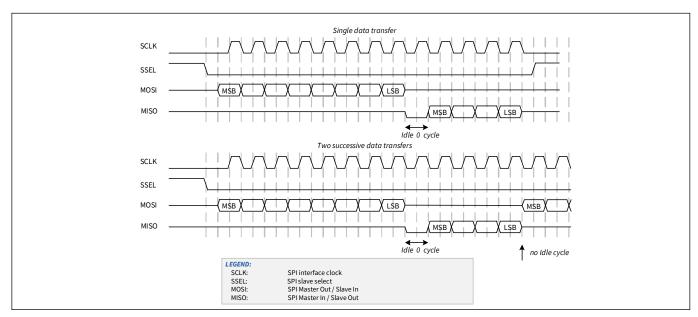

Figure 17 Single 8-bit data transfer and two successive 8-bit data transfers in Mode 0 (CPOL is '0', CPHA is '0')

Application examples

#### **Texas Instruments**

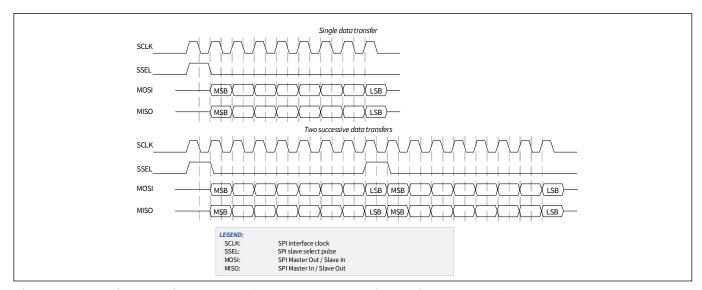

Texas Instruments' SPI protocol redefines the use of the SSEL signal. It uses the signal to indicate the start of a data transfer, rather than a low, active slave-select signal. The start of a transfer is indicated by a high, active pulse of a single-bit transfer period. This pulse may occur one cycle before the transmission of the first data bit, or it may coincide with the transmission of the first data bit. The transmitted clock SCLK is a free-running clock. The TI SPI protocol only supports mode 1 (CPOL is '0' and CPHA is '1'): Data is driven on a rising edge of SCLK and data is captured on a falling edge of SCLK.

**Figure 18** illustrates a single 8-bit data transfer and two successive 8-bit data transfers. The SSEL pulse precedes the first data bit. Note how the SSEL pulse of the second data transfer coincides with the last data bit of the first data transfer.

Figure 18 Single 8-bit data transfer and two successive 8-bit data transfers

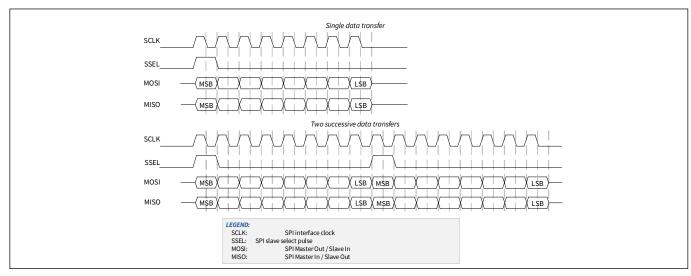

**Figure 19** illustrates a single 8-bit data transfer and two successive 8-bit data transfers. The SSEL pulse coincides with the first data bit.

Figure 19 Single 8-bit data transfer and two successive 8-bit data transferst

Application examples

#### **National Semiconductor**

National Semiconductor's SPI protocol is a half-duplex protocol. Rather than transmission and reception occurring at the same time, they take turns (transmission happens before reception). A single "idle" bit transfer period separates transmission from reception.

**Note:** Successive data transfers are NOT separated by an "idle" bit transfer period.

The transmission data transfer size and reception data transfer size may differ. National Semiconductor's SPI protocol supports only mode 0: Data is driven on a falling edge of SCLK, and data is captured on a rising edge of SCLK

**Figure 20** illustrates a single data transfer and two successive data transfers. In both cases, the transmission data transfer size is 8 bits and the reception transfer size is 4 bits.

Figure 20 Single data transfer and two successive data transfers

**Note:** The above figure defines MISO and MOSI as undefined when the lines are considered idle (not carrying valid information). It will drive the outgoing line values to '0' during idle time (to satisfy the requirements of specific master devices (NXP LPC17xx) and specific slave devices (MicroChip EEPROM).

Ordering information

#### **Ordering information** 8

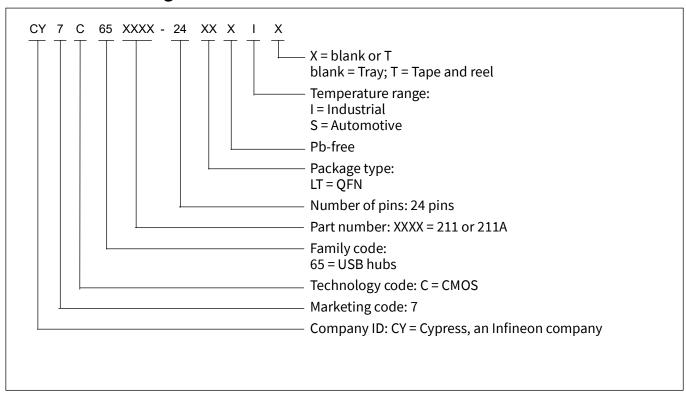

Table 20 lists the key package features and ordering codes of the CY7C65211. For more information, contact your local sales representative.

Key features and ordering information Table 20

| Package                                                                                  | Product            | Operating range |

|------------------------------------------------------------------------------------------|--------------------|-----------------|

| 24-lead QFN (4.00 × 4.00 × 0.55 mm, 0.5 mm pitch) (Pb-free)                              | CY7C65211-24LTXI   | Industrial      |

| 24-lead QFN ( $4.00 \times 4.00 \times 0.55$ mm, 0.5 mm pitch) (Pb-free) – tape and reel | CY7C65211-24LTXIT  | Industrial      |

| 24-lead QFN (4.00 × 4.00 × 0.55 mm, 0.5 mm pitch) (Pb-free)                              | CY7C65211A-24LTXI  | Industrial      |

| 24-lead QFN ( $4.00 \times 4.00 \times 0.55$ mm, 0.5 mm pitch) (Pb-free) – tape and reel | CY7C65211A-24LTXIT | Industrial      |