## **Table of contents**

## **Table of contents**

| Tabl | le of contents                                   | 2  |

|------|--------------------------------------------------|----|

| Acro | onyms and Abbreviations                          | 3  |

| 1    | Package Description                              |    |

| 1.1  | TSNP Package Type with Bottom-Only Terminations  |    |

| 1.2  | TSNP Package Type with LTI Features              |    |

| 1.3  | Package Features and General Handling Guidelines | 6  |

| 2    | Printed Circuit Board                            | 8  |

| 2.1  | Routing                                          | 8  |

| 2.2  | Pad Design                                       | 8  |

| 2.3  | Via-in-Pad Design                                | 10 |

| 3    | PCB Assembly                                     | 11 |

| 3.1  | Solder Paste Stencil                             | 11 |

| 3.2  | Solder Paste                                     | 12 |

| 3.3  | Component Placement                              | 12 |

| 3.4  | Reflow Soldering                                 | 12 |

| 4    | Cleaning                                         | 14 |

| 5    | Inspection                                       | 15 |

| 5.1  | Optical Solder Joint Inspection                  | 15 |

| 5.2  | X-Ray Solder Joint Inspection                    | 15 |

| 6    | Rework                                           | 17 |

| 7    | References                                       | 18 |

| Revi | ision history                                    | 19 |

**Acronyms and Abbreviations**

## **Acronyms and Abbreviations**

| AOI  | <br>Automated Optical Inspection      |

|------|---------------------------------------|

| AXI  | <br>Automated X-ray Inspection        |

| ENIG | <br>Electroless Nickel Immersion Gold |

| ESD  | <br>Electrostatic Discharge           |

| I/O  | <br>Input/Output                      |

| LTI  | <br>Lead Tip Inspection               |

| MSL  | <br>Moisture-Sensitivity Level        |

| NSMD | <br>Non-Solder Mask Defined pad       |

| PG   | <br>Plastic Green                     |

| PCB  | <br>Printed Circuit Board             |

| SAC  | <br>Tin Silver Copper (SnAgCu)        |

| SMD  | <br>Solder Mask Defined               |

| SMD  | <br>Surface-Mount Device              |

| SMT  | <br>Surface-Mount Technology          |

| Sn   | <br>matte tin plating                 |

| SON  | <br>Small Outline Non-leaded          |

| TSLP | <br>Thin Small Leadless Package       |

| TSNP | <br>Thin Small Non-leaded Package     |

**Package Description**

#### **Package Description** 1

This document provides information about the Surface Mount Technology (SMT) board assembly of Infineon Thin Small Non-leaded Packages (TSNP). The specific dimensions of the leadframe based inner setup depend on the size of the chip and the type of bonding. The field of application ranges from linear voltage regulators for weight-limited applications such as cellular phones and digital cameras to linear voltage regulators for the automotive sector.

This document does not discuss Thin Small Leadless Packages (TSLP) although there can be identical footprints with the latter (e.g. PG-TSNP-16-1 vs. PG-TSLP-16-1). This document also does not discuss the Small Outline Non-leaded (SON) packages. These package families are described in separate documents.

#### 1.1 **TSNP Package Type with Bottom-Only Terminations**

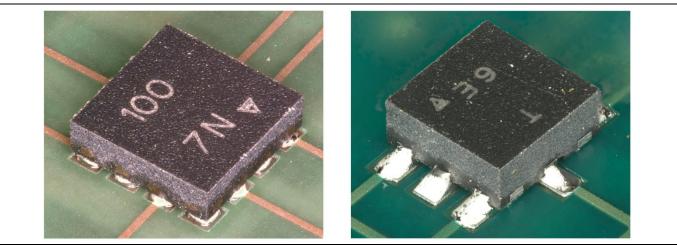

Infineon TSNP can be divided in two thickness classes one staying below half a millimeter while the other having roughly three-quarters of a millimeter in thickness. The solder joint of TSNP with bottom-only terminations is formed solely below the package body. There is no wettable termination tip. Figure 1 shows examples that TSNP package family.

PG-TSNP packages

PG = Plastic Green

T = Thin

S = Small

NP = Non-leaded Package

**Examples of standard TSNP packages with bottom-only terminations.** Figure 1

**Package Description**

#### **TSNP Package Type with LTI Features** 1.2

Infineon TSNP with Lead Tip Inspection (LTI) feature wettable termination tips. They allow for reproducible solder joint inspection by top view. Figure 2 shows a TSNP package with LTI features.

PG-TSNP packages

PG = Plastic Green

T = Thin

S = Small

NP = Non-leaded Package

Figure 2 Example of a TSNP package having terminations with lead tip inspection features.

**Package Description**

## 1.3 Package Features and General Handling Guidelines

#### **General Handling Guidelines**

Semiconductor devices are sensitive to excessive electrostatic discharge (ESD), moisture, mechanical handling, and contamination. Therefore, they require specific precautionary measures to ensure that they are not damaged during transport, storage, handling, and processing.

For further information about component handling, please refer to the *General Recommendations for Board Assembly of Infineon Packages* document that is available on the Infineon web page [1]. Please also feel free to contact your local sales, application, or quality engineer.

#### **Internal Construction**

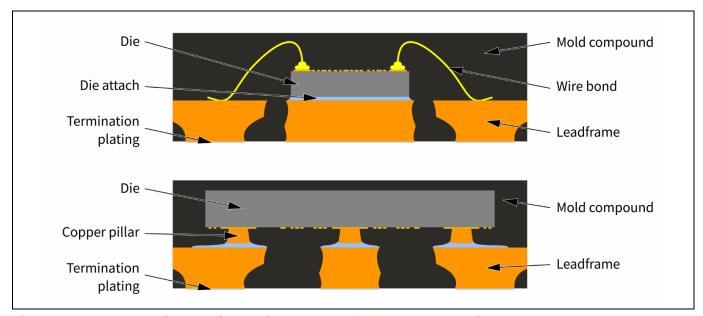

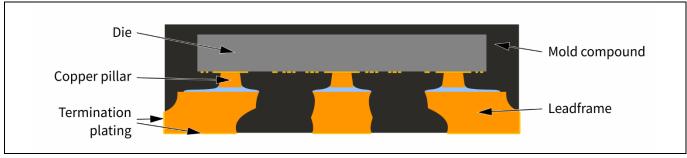

TSNP offer smallest dimensions for leadframe based packages. The package type is capable of providing a full array I/O pad configuration at the landing area as well as such having peripheral I/O pads together with thermal or exposed pads. **Figure 3** shows schematic drawings of the inner setup of bottom-only termination TSNP with a wire bonded die on a heat sink as well as with a flip-chip on copper pillars. A TSNP version with Lead Tip Inspection (LTI) features for wettble flanks and ith flip-chip is shown in **Figure 4**. The LTI features allow for Automated Optical Inspection (AOI) of the solder joint connection on board by top view.

Figure 3 Schematics showing the inner setup of bottom-only terminated standard TSNP packages with wire bonded die (top) and with flip-chip with copper pillars (bottom).

Figure 4 Schematic showing the inner setup of a TSNP package with wettable termination tip LTI features and flip-chip.

### **Package Description**

### **Termination Design**

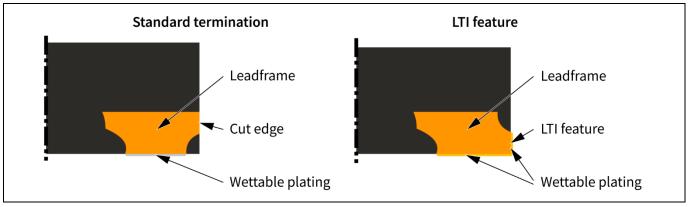

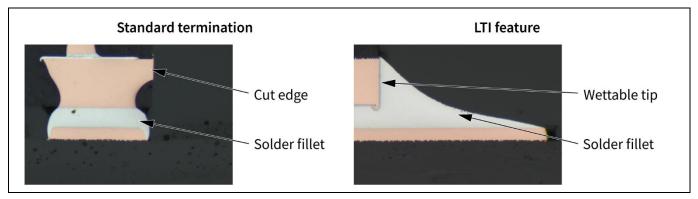

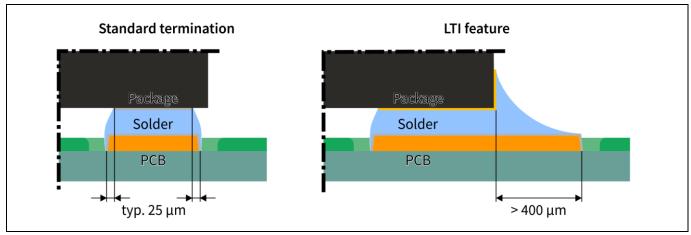

The LTI features provide a full plating of the termination tip as can be seen in **Figure 5**. The feature allows for AOI of the solder joint connection by top view. The cross-section photographs in **Figure 6** show how such a feature works together with the correct Printed Circuit Board (PCB) pad.

For further information about LTI features, please contact your local Infineon sales, application, or quality engineer.

Figure 5 Schematic comparison of TSNP termination designs without (left) and with LTI feature (right).

Figure 6 Cross-sections of a TSNP termination without (left) and with LTI feature (right).

#### **Termination Plating**

Most TSNP packages feature an electroplated pure Sn finish. TSNP with LTI feature are plated with an Electroless Nickel/Immersion Gold (ENIG) finish. The sacrificial gold layer dissolves during reflow. The solder connection is then made to the Ni-layer with very stable results in solderability.

**Printed Circuit Board**

## 2 Printed Circuit Board

## 2.1 Routing

Printed circuit board design and construction are key factors for achieving solder joints with high reliability. Packages with exposed pads should not be placed opposite one another on either side of a PCB if double-sided mounting is used. This will stiffen the assembly and cause solder joints to fatigue earlier than in a design in which the components are offset. Furthermore, the board stiffness itself has a significant influence on the reliability of the solder joint interconnect if the system is used in critical temperature-cycling conditions.

### 2.2 Pad Design

The quality and reliability of interconnect solder joints to the board are affected by:

- Pad type (Solder Mask Defined, SMD or Non-Solder Mask Defined, NSMD)

- Specific pad dimensions

- Pad finish (also called metallization or final finish)

- Via layout and technology

Typically PCB pads for bottom-only TSNP are designed by transferring the package pad outline and adding  $25 \, \mu m$  circumferentially. There are application cases where it can be benefical to slightly increase the outwards overhang of the pad geometries. That allows for using stencils with increased thickness and can help to compensate natural printing tolerances. The here discussed PCB pad designs for bottom-only terminations must clearly be distinguished from those for passive components (typically resistors or capacitors). Standard TSNP packages feature no wettable sidewalls but are terminated bottom-only. The recommended PCB pad sizes of bottom-only TSNP compared with passive components are largely different to provide the optimum solderable area and will help to prevent excessive tilting or tombstoning.

Note: The PCB pad designs for TSNP with bottom-only terminations must not be confused with those for passive components because they do not feature wettable sidewalls.

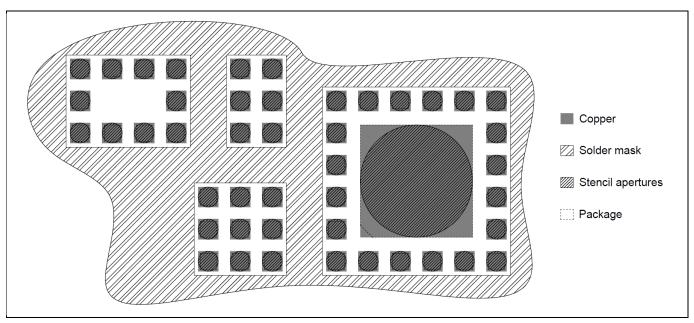

The small size of the TSNP packages requires stable geometry tolerances on the PCB. Therefore, the NSMD pad design is recommended. The copper pad tolerances are much lower than those of the solder resist. NSMD pads expose parts of the conductor lines connecting the pads to the remaining circuit. The conductor tracks on the PCB should be as narrow as possible (100  $\mu$ m or less), to minimize the influence by the therefore increased wettable area. Furthermore, only one connection per solder pad, preferably symmetrical, is recommended. Depending on the capabilities of the PCB manufacturer, it might not be possible to separate two NSMD pads by a solder mask dam. The solder mask dams in between the PCB landing pads are therefore often stated as being optional (see **Figure 7**). When having no solder mask dam in between the pads it goes without saying, that the solder paste printing process must be well-controlled.

The exposed pads on the landing area of the TSNP packages are designed to conduct thermal loads into the PCB or to provide a reliable ground connection. Therefore, the exposed pad outline on the PCB should either be congruent with the area on the package or be increased similar to that for the peripheral I/O pads.

#### **Printed Circuit Board**

Figure 7 Examples of TSNP footprints for bottom-only terminations having an array configuration.

Solder mask dams in between the pads are often stated as being optional. Their use depends on the specific board manufacturing and board assembly processes.

#### **Pad Design for LTI Features**

To ensure an optimal response during the AOI, the PCB pad should protrude the package outline by minimum 400  $\mu$ m. The solder paste volume should be accordingly increased by a sufficient amount to ensure a homogeneous and reproducible solder joint fillet formation at the termination tip. The increased extension of the PCB pad for LTI feature terminations for optimal solder meniscus formation is shown schematically in Figure 8.

Figure 8 Schematic comparisons of a TSNP termination without (left) and with LTI feature (right).

The intended AOI capability is reached by having a distinct solder fillet formation at the termination tip. The PCB pad is therefore sufficiently extended over the package edge.

An optimal PCB design generally depends on the specific application as well as on the specific design guidelines of the chosen board manufacturer.

#### **Printed Circuit Board**

Further details and specific PCB pad design can be found in the package data base that is available on the Infineon web page [1]. Please choose a specific package when you are searching the data base. It will then show you an example of the stencil aperture layout for each package. Please also feel free to contact your local sales, application, or quality engineer.

#### 2.3 **Via-in-Pad Design**

Thermal and electrical connections to the inner and/or bottom copper planes of the PCB are usually created by plated through-hole vias in the board. The heat or the electrical signal are then transferred from the chip over the package die pad and the solder joint to the thermal pad on the board and further through the PCB by the thermal vias.

The diameter and the number of vias in the thermal pad depend on the specific thermal requirements of the final product, the power consumption of the product, the application, and the construction of the PCB. The implementation of thermal vias has several impacts on the board assembly processes such as the solder paste print. A constant increase of the number of vias does not necessarily translate into a constant decrease of the thermal resistance of the entire assembly set-up. Thermal and electrical analysis and/or testing together with a proper board assembly design procedure are recommended to determine the optimum number of vias needed.

Open thermal vias should not be placed under the small TSNP packages with exposed pad for various reasons. First, the typical hole diameter for thermal vias is 0.2 - 0.5 mm which is too large to be placed below the small packages in a reasonable array with e.g. 1.0 - 1.2 mm pitch. Second, printed solder can move into the via driven by the wetting forces. Precautionary designs such as placing the via orifice below a stencil beam or covering the orifice with solder mask by "tenting" will most likely not be applicable due to the lack sufficient space. Consequences of solder penetration can be a decreased stand-off between the PCB and the package, an increased void formation ultimately resulting in an insufficient solder joint area, or solder flowing through the via to the opposite side of the PCB.

In case it is not necessary to provide a direct connection from the solder pad under the exposed die pad to the inner layers of the PCB, open vias can also be placed next to the footprint near the package and be covered with solder mask.

Another alternative is the use of "plugged" microvias. With that method vias 0.2 - 0.1 mm in diameter and smaller are filled with copper, while larger ones are filled with an epoxy. The following overplating step is capable of creating a smooth surface with nearly no discontinuities. They can be placed inside the solder pads and therefore are a preferred solution. It has to be taken care, that also when using plugged vias, the flatness in the pad is crucial to the voiding behavior of the solder joint. Deep dips into the pad have the tendency to trap solder voids.

For further information about vias in pad, please refer to the General Recommendations for Board Assembly of Infineon Packages document that is available on the Infineon web page [1]. Please also feel free to contact your local sales, application, or quality engineer.

**PCB Assembly**

#### 3 **PCB Assembly**

#### **Solder Paste Stencil** 3.1

In SMT the solder paste is applied onto the PCB metal pads by stencil printing. The volume of the printed solder paste is determined by the stencil aperture and the stencil thickness. While an excessive solder paste volume will cause solder bridging, an insufficient solder paste volume can lead to reduced solder spreading between all contact surfaces. To ensure a uniform and sufficiently high solder paste transfer to the PCB, laser-cut (mostly made from stainless steel) or electroformed stencils (made of nickel) are preferred. The latter are applied especially when fine-pitch components are assembled.

The stencil apertures for TSNP with array configuration are usually of circular shape having the same extension as the relevant pad on the PCB. Generally rounding the corners of rectangular apertures (radius approx. 50 μm) can support the stencil transfer stability. Stencils with a thickness of typically 80 µm are recommended based on an area ratio of 0.66. The TSNP with LTI features even allows for a 130 μm to 150 μm stencil thickness. In that case the solder volume, however, must be calculated very thoroughly to preserve the AOI capability.

The reduction of the solder volume that is printed to the pads stabilizes the package during reflow and supports its self-aligning tendency. The print reduction for central exposed pads of TSNP depends on their difference in size compared with the I/O pads and ranges from 80% to 60% by area.

TSNP with LTI features can have different pad characteristics in one footprint as shown in Figure 9. The given wetting behavior of molten solder can lead to different tip fillet appearences in case the pad and print design are not adjusted properly. The following recommendations therefore apply specifically to TSNP with LTI features. Figure 10 shows a properly soldered TSNP with LTI features on a test board.

- It is recommended to use only one of the wettable tips of a double LTI I/O pad.

- It can be beneficial for the generation of reproducible tip fillets to decrease the difference of print reduction between the exposed pad and the I/O pads.

Landing area of a TSNP with LTI features showing the various package pad characteristics. Figure 9

For individual design adaptations to reach the optimum amount of solder, the stencil thickness, the PCB pad finish, quality and solder masking, the via layout, and the solder paste type should be considered. In every case, application-specific experiments are recommended.

Further details and specific stencil aperture recommendations can be found in the package data base that is available on the Infineon web page [1]. Please choose a specific package when you are searching the data base. It will then show you an example of the stencil aperture layout for each package.

### **PCB Assembly**

For further information about solder stencil design, please refer to the General Recommendations for Board Assembly of Infineon Packages document that is available on the Infineon web page [1]. Please also feel free to contact your local sales, application, or quality engineer.

#### 3.2 **Solder Paste**

Pb-free solder pastes typically contain some type of SnAgCu alloy (SAC solder with typically 1% to 4% Ag and <1% Cu). The most common alloy is SAC305 (3.0 % Ag and 0.5 % Cu). The average alloy particle size must be suitable for printing the solder stencil aperture dimensions. Using Type 4 paste or higher (with lower grain size of the solder alloy powder) is recommended for the assembly of integrated TSNP components, depending on the specific stencil aperture size and therefore solder paste transfer efficiency.

The solder alloy particles are dispersed in a blend of liquid flux and chemical additives (approx. 50% by volume or 10% by weight), forming a creamy paste. The flux and chemical solvents have various functions such as adjusting the viscosity of the paste for stencil printing or removing contaminants and oxides on the surface.

The solder paste solvents have to evaporate during reflow soldering, while residues of the flux will remain on the joint. The capacity of the flux additive for removing oxides is given by its activation level, which also affects the potential need for removing the flux residuals after the assembly. For packages where the solder joint is formed mainly on the package bottom side, a "no clean" paste is recommended to avoid subsequent cleaning steps underneath the package. The small gaps make cleaning highly difficult if not impossible. Certain precautions have to be taken if any kind of flux residues remain on the board prior to any kind of coating. For power packages, leakage currents and the potential for shorting below components have to be considered when choosing the specific flux type (e.g. halide-free vs. zero halides).

Generally, solder paste is sensitive to age, temperature, and humidity. Please follow the handling recommendations of the paste manufacturer.

#### 3.3 **Component Placement**

The components have to be placed accurately despite the self-alignment effect that is caused by the surface tension of the liquid solder. Positioning the packages manually is not recommended, especially not for packages with small terminations and pitch. An automated pick-and-place machine is recommended to obtain reliable solder joints.

Component placement accuracies of +/-50 µm and less are obtained with modern automatic component placement machines using vision systems. With these systems, both the PCB and the components are optically measured and the components are placed on the PCB at their programmed positions. The fiducials on the PCB are located either on the edge of the whole PCB, or at additional individual mounting positions (local fiducials). These fiducials are detected by a vision system prior to the mounting process.

For further information about component placement, please refer to the General Recommendations for Board Assembly of Infineon Packages document that is available on the Infineon web page [1]. Please also feel free to contact your local sales, application, or quality engineer.

#### 3.4 **Reflow Soldering**

The widely used method of reflow soldering in a forced convection oven is recommended for the PCB assembly of TSNP components. Soldering in a nitrogen atmosphere can generally improve the solder joint quality but is not necessary to create a reliable joint.

The soldering profile should be in accordance with the recommendations of the solder paste manufacturer to achieve optimal solder joint quality. The position and the surrounding of the component on the PCB, as well as the PCB thickness, can influence the solder joint temperature significantly. Power packages where leakage

#### **PCB Assembly**

currents and shorting below the component have to be considered should be soldered with decreased flux spreading. Therefore, it is recommended to optimize the reflow profile in such a way that excessive flux or solder spattering is avoided.

#### **Minimum Reflow Conditions**

The lower temperatures and durations of an optimal reflow profile must stay above those of the solderability qualification. The solderability of the terminations of Infineon components is tested according to the standards IEC 60068-2-58 and J-STD-002 [2][3].

#### **Maximum Reflow Conditions and Cycles**

TSNP packages are generally suited for mounting on double-sided PCBs. During the board assembly solder joints of components on the first side will again reflow in the second reflow step. In the reflow zone of the oven (with the solder being in its liquid state), the components are only held in place by wetting forces from the molten solder. Gravity of larger components acting in the opposite direction will elongate the solder joints, unlike joints on the top side, where gravity will force the components closer to the PCB surface. This shape will be frozen during cooling and therefore will result in a higher stand-off on the bottom side after the reflow process. Heavy vibrations in a reflow oven may cause devices to drop off the PCB.

Components that are Moisture-Sensitivity Level (MSL) classified by Infineon have been tested by three reflow runs in accordance with the J-STD-020 standard, covering a double-sided reflow and one rework cycle. The maximum temperatures must not exceed during application board assembly. Please refer to the product barcode label on the packing material that states the maximum reflow temperature according to the J-STD-020 [4] standard as well as the MSL according to the J-STD-033 standard [5].

For further information about reflow soldering, please refer to the General Recommendations for Board Assembly of Infineon Packages document that is available on the Infineon web page [1]. Please also feel free to contact your local sales, application, or quality engineer.

Cleaning

#### Cleaning 4

After the soldering process, some flux residues may remain on the board, especially near the solder joints. Generally, cleaning beneath a component with bottom-only terminations is difficult due to the small gap between the component body and the PCB. Therefore, a "no-clean" flux is recommended whose residues usually do not have to be removed after the soldering process.

In case the solder joints have to be cleaned, the cleaning method (e.g. ultrasonic, spray, or vapor cleaning) and cleaning solution have to be selected while taking into account the type of package, the flux used in the solder paste (rosin/resin-based, water-soluble, etc.) as well as the environmental and safety aspects. Even small residues of the cleaning solution should be removed or dried out very thoroughly. For recommended cleaning solutions, please contact the solder paste or flux manufacturer.

Inspection

#### Inspection 5

#### 5.1 **Optical Solder Joint Inspection**

The solder joints of TSNP terminations without LTI feature are formed solely underneath the package. A visual inspection of the solder joints with conventional AOI systems is not possbile. TSNP with LTI feature on the other hand allow to form a solder fillet that protrudes the package outline. That enables the mounted package being inspected by conventional AOI top-view. Figure 10 shows the different characters of solder joint appearance depending on the termination type.

Photographs of a TSNP package without (left) and with LTI features (right) on a test board. Figure 10 Proper PCB pad and stencil design allows to generate reproducible solder fillets at the LTI termination tips. It is recommended to use only one of the wettable tips of a double LTI I/O pad.

For general acceptability of electronic assemblies, please refer also to the IPC-A-610 standard [6].

#### **5.2** X-Ray Solder Joint Inspection

Automated X-ray Inspection (AXI) systems are appropriate for efficient inline control of components that cannot be inspected properly by optical systems. AXI systems are available as 2D and 3D solutions. They usually consist of an X-ray camera and the hardware and software needed for inspecting, controlling, analyzing, and data transferring routines. These reliable systems enable the user to detect soldering defects such as poor soldering, bridging, voiding, and missing parts. However, other defects such as broken solder joints are not easily detectable by X-ray.

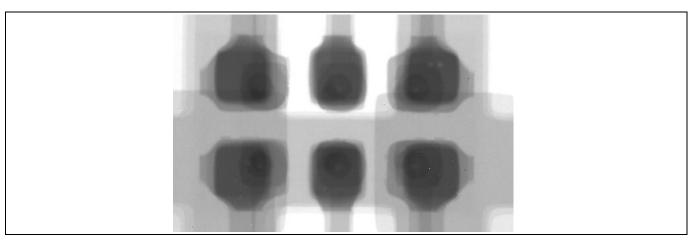

Figure 11 shows a typical X-ray photograph of a standard TSNP package. The solder joints as well as parts of the package internal setup are visible. Larger pads than shown here may tend to increase voiding because they do not provide a sufficient ratio between volume and surface necessary for proper outgassing of the organic compounds during reflow. Generally, the extent of voiding depends on the board pad size, the via and stencil layout, the solder paste, and the reflow profile. For thermal evaluations, the entire thermal path must be considered as well as all boundary conditions such as the application environment or the electrical use of the component.

Inspection

Typical X-ray image of a soldered TSNP package without LTI feature. The solder joints and Figure 11 parts of the package internal setup are visible.

Rework

#### 6 Rework

Single solder joint repair of packages with land grid array configuration is highly difficult, if not impossible, and is therefore generally not recommended. Furthermore, the reuse of de-soldered components is not recommended. The de-soldered components should be replaced by new ones.

A rework process is commonly done on special rework equipment. There are various systems available that meet the requirements for reworking SMD packages. All handling guidelines discussed in this document have to be respected. Special focus should be on the following items:

- Due to the decreased automation level given by the general rework approach, even higher care compared to fully automated assembly must be taken. Tools that do not damage the component mechanically have to be chosen. Mechanical forces that do not necessarily cause visible external damage can still cause internal damage that reduces the component's reliability. A proper handling system with vacuum nozzle may be the gentlest solution and is therefore recommended. However, the impact of rework tools has to be assessed properly. In general, more manual handling increases the effort for documentation, training, and monitoring of the rework process(es).

- During rework, special care must be taken concerning the proper moisture level of the component according to the J-STD-033. Drying the PCB and the component prior to rework might be necessary. A proper drying procedure for SMD packages is described in the international J-STD-033 standard [5]. Please also refer to the recommendations of your PCB manufacturer and take all specific needs of components, PCB, and other materials into account.

- Whatever heating system is used (hot air, infrared, hot plate, etc.), the applied temperature profile at the component must never exceed the maximum temperature according to the J-STD-020 standard. Depending on the specific heating profile used during rework, components adjacent to the mounting location might also experience a further "reflow run" in terms of the J-STD-020 standard [4]. Internal investigations have shown that the temperature profile must be recorded.

If a device is suspected to be defective and a failure analysis is planned, Infineon usually expects customers to desolder the component prior to return to Infineon. The component shall be returned in a proper condition according to the original package outlines.

In some special cases such as solder joint inspection Infineon may request that the PCB or part of the PCB with the component still attached should be sent to Infineon.

Note:

Before returning a device for failure analysis at Infineon, please clarify the return condition of the suspected component (ie onboard or desoldered) with the Infineon Application Engineer or Customer Quality Manager who supports your company.

For further information about component rework on PCB, please refer to the General Recommendations for Assembly of Infineon Packages document that is available on the Infineon web page [1]. Please also feel free to contact your local sales, application, or quality engineer.

#### References

#### 7 References

- Infineon: Packages. <a href="www.infineon.com/packages">www.infineon.com/packages</a>. [1]

- [2] International Electrotechnical Commission: IEC 60068-2-58. Environmental testing - Part 2-58: Tests -Test Td: Test methods for solderability, resistance to dissolution of metallization and to soldering heat of surface mounting devices (SMD).

- [3] Electronic Components Industry Association, Assembly and Joining Processes and JEDEC Solid State Technology Association Committee: EIA/IPC/JEDEC J-STD-002. Solderability Tests for Component Leads, Terminations, Lugs, Terminals and Wires.

- [4] JEDEC Solid State Technology Association: IPC/JEDEC J-STD-020. Moisture/Reflow Sensitivity Classification for Nonhermetic Surface Mount Devices.

- [5] JEDEC Solid State Technology Association: IPC/JEDEC J-STD-033. Handling, Packing, Shipping and Use of Moisture/Reflow Sensitive Surface Mount Devices.

- [6] Association Connecting Electronics Industries: IPC-A-610. Acceptability of Electronic Assemblies.

**Revision history**

## **Revision history**

| Page or reference  | Major changes since the last revision          |

|--------------------|------------------------------------------------|

| Section 7 "Rework" | Update of sample conditions in case of return. |

| Entire document    | Editorial review.                              |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2020-11-09 **Published by Infineon Technologies AG** 81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference

### IMPORTANT NOTICE

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.