# ISOFACE™: ISO1|811T/|SO1|813T/|SO1|815T

### **About this document**

#### **Scope and purpose**

This is an application note describing the safety limits for the ISO1l8xx-ICs series of isolated eight-channel digital-input ICs with IEC61131-2 type 1/2/3 characteristics.

#### Intended audience

For engineers interested in industrial automation.

#### **Table of contents**

| Abo | out this document                  |    |

|-----|------------------------------------|----|

|     | ble of contents                    |    |

|     | Introduction                       |    |

|     | Safety-relevant architecture       |    |

| 3   |                                    |    |

| 4   | Sink current                       | 7  |

| 5   | Safety limits ISO11813T, ISO11815T | 11 |

| 6   | Safety limits ISO1I811T            | 16 |

| Rev | vision history                     | 21 |

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Introduction

#### 1 Introduction

Safety limits of allowed current or allowed power dissipation are intended to prevent an over-temperature condition. They are also intended to prevent potential damage to the isolation barrier and a voltage breakdown between the two voltage domains.

Precautions were taken during the conception phase of the architecture (described in chapter 2). In chapter 3 the electrical and thermal parameters are listed, which are used for calculation of the allowed current in the sense chip. Chapter 4 deals with the split of the sense current into an external and internal part. Only the internal part has be considered for the calculation of safety limits. The most important chapters are 5 and 6. In these chapters the junction temperature  $T_i$  is calculated based on the variable ambient temperature and the temperature rise due to the I<sub>VBB</sub> current in the sense chip, the I<sub>VCC</sub> current in the uC interface chip and the sink current in the sense chip. The related power dissipation is multiplied with the thermal resistance junction-toair. The criterion for the allowed currents is T<sub>i</sub> less than 150°C and for the maximum power dissipation of the whole chip it is P<sub>tot max</sub> less than or equal to 0.8 W. From these requirements a limitation for the allowed ambient temperature and for I<sub>VBB</sub> and I<sub>VCC</sub> is derived.

All figures and curves are calculated with reference to the electrical and thermal characteristics of the datasheet.

# 2 Safety-relevant architecture

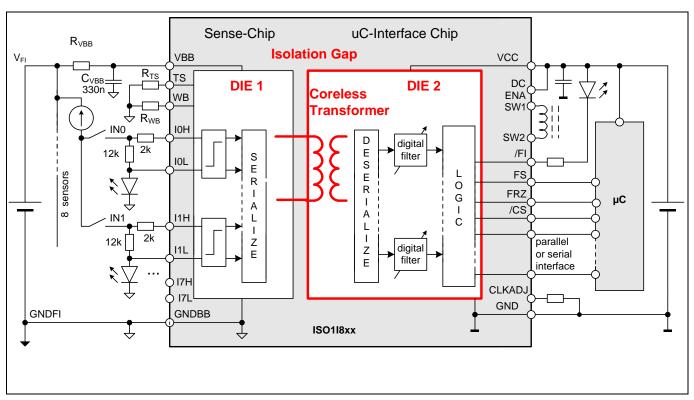

Figure 1 emphasizes the location of the coreless transformer. It is placed on the uC interface chip (DIE 2). The temperature-critical chip is the sense chip (DIE 1). The chips DIE1 and DIE2 are located on a split lead-frame to establish the isolation. Any temperature increase on the sense chip has only indirect influence on the uC interface chip and therefore on the coreless transformer only via the split lead-frame and the package.

The internal current sinks limit the sense current of each external attached sensor. The external resistor network splits the sense current into an external current over the resistor  $R_{ext}$  (= 12 k $\Omega$  for type 1 and 3 or = 8.5 k $\Omega$  for type 2) and the internal current into the chip inputs I × H, × = 0, ..., 7.

Therefore only a limited portion of the sense current enters the IC and therefore only a limited portion of the sense current contributes to the internal power dissipation (Figure 2).

The chip is not equipped with any temperature shut-down mechanism.

Figure 1 Typical application diagram with internal structure of galvanic isolation

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Prerequisites for calculating safety limits

#### Prerequisites for calculating safety limits 3

For calculating the safety limits the maximum values of the relevant parameters are chosen. All underlying calculations refer to these parameters.

Prerequisites for calculating safety limits Table 1

| Parameter              | Maximum values used | Comment                                                                                                                             |  |

|------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| $R_{th(JA)}$           | 88.6 K/W            | Thermal resistance junction-ambient, maximum, see Note: Thermal resistance, PCB                                                     |  |

| I <sub>VCC=2.85V</sub> | 0.005 A             | Maximum V <sub>cc</sub> current of uC interface chip                                                                                |  |

| I <sub>VCC=3.6V</sub>  | 0.006 A             |                                                                                                                                     |  |

| I <sub>VCC=5.5V</sub>  | 0.006 A             |                                                                                                                                     |  |

| ISO1I813/815:          |                     | Maximum quiescent current of sense chip, all sense currents                                                                         |  |

| I <sub>VBB=9.6V</sub>  | 0.0115 A            | equal zero                                                                                                                          |  |

| I <sub>VBB=24V</sub>   | 0.012 A             | Coreless transformer frequency: 500 kHz                                                                                             |  |

| I <sub>VBB=35V</sub>   | 0.0125 A            |                                                                                                                                     |  |

| ISO1 811:              |                     | Maximum quiescent current of sense chip, all sense currents equal zero                                                              |  |

| I <sub>VBB=9.6V</sub>  | 0.0085 A            | Coreless transformer frequency: 100 kHz                                                                                             |  |

| I <sub>VBB=24V</sub>   | 0.009 A             |                                                                                                                                     |  |

| I <sub>VBB=35V</sub>   | 0.0095 A            |                                                                                                                                     |  |

| P <sub>tot_max</sub>   | 0.8 W               | Maximum rating of total dissipated power                                                                                            |  |

| $T_{jmax}$             | 150.0°C             | Maximum junction temperature                                                                                                        |  |

| I <sub>INxsnkM13</sub> | 3.4 mA              | Sink current limit at maximum input voltage type 1 and 3, $V_{VBB}$ = 35 $V$ , $V_{INX}$ = 30 $V$ , $V_{ixL}$ = 2.5 $V$             |  |

| I <sub>INxsnkM2</sub>  | 4.8 mA              | Sink current limit at maximum input voltage type 2, $V_{VBB} = 35 \text{ V}$ , $V_{INx} = 30 \text{ V}$ , $V_{ixL} = 2.5 \text{ V}$ |  |

| P <sub>VCC=2.85V</sub> | 0.014 W             | Maximum quiescent power dissipation of uC interface chip                                                                            |  |

| P <sub>VCC=3.6V</sub>  | 0.022 W             |                                                                                                                                     |  |

| P <sub>VCC=5.5V</sub>  | 0.033 W             |                                                                                                                                     |  |

| ISO1I813/815:          |                     | Maximum quiescent power dissipation of sense chip, all                                                                              |  |

| $P_{VBB=9.6V}$         | 0.110 W             | sense currents equal zero  Coreless transformer frequency: 500 kHz                                                                  |  |

| $P_{VBB=24V}$          | 0.288 W             |                                                                                                                                     |  |

## ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

#### Prerequisites for calculating safety limits

| Parameter                                            | Maximum values used           | Comment                                                                                                                   |

|------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| P <sub>VBB=35V</sub>                                 | 0.438 W                       |                                                                                                                           |

| ISO11811: $P_{VBB=9.6V}$ $P_{VBB=24V}$ $P_{VBB=35V}$ | 0.082 W<br>0.216 W<br>0.333 W | Maximum quiescent power dissipation of sense chip, all sense currents equal zero  Coreless transformer frequency: 100 kHz |

| P <sub>Sink_1_3_max</sub>                            | 23 mW                         | Type 1 and 3  Maximum internal power dissipation due to sense current/channel  Due to current into pin I × H              |

| P <sub>Sink_2_max</sub>                              | 33 mW                         | Type 2  Maximum internal power dissipation due to sense current/channel  Due to current into pin I × H                    |

Note:

Thermal resistance at 2 cm $^2$  cooling area (thermal conductance only by radiation and free convection). Device on 50 mm × 50 mm × 1.5 mm epoxy PCB FR4 with 2 cm $^2$  (one layer, 35  $\mu$ m thick) copper area. PCB is vertical without blown air.

Table 2 Formulas for calculating safety limits

| Purpose                                          | Formula                                                                                                                                                                                            |  |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Total power<br>dissipation                       | $P_{\text{tot}}(T) = P_{\text{VCC=xV}} + P_{\text{VBB=xV}} + P_{\text{Sink}\_1\_3\_\text{max}} *8$ $P_{\text{tot}}(T) = P_{\text{VCC=xV}} + P_{\text{VBB=xV}} + P_{\text{Sink}\_2\_\text{max}} *8$ |  |

|                                                  | 8 channels                                                                                                                                                                                         |  |

| Condition for I <sub>VBB</sub> (T <sub>A</sub> ) | Condition: T less than or equal to 150°C and P <sub>tot</sub> less than 0.8 W> allowed I <sub>VBB</sub>                                                                                            |  |

|                                                  | 150°C = $T_A$ + ( $P_{VCC=xV}$ + $P_{VBB=xV}$ ) * $R_{TH(JA)}$ + $P_{Sink\_1\_3\_max}$ *8 * $R_{TH(JA)}$                                                                                           |  |

|                                                  | 150°C = $T_A$ + ( $P_{VCC=xV}$ + $P_{VBB=xV}$ ) * $R_{TH(JA)}$ + $P_{Sink\_2\_max}$ *8 * $R_{TH(JA)}$                                                                                              |  |

| I <sub>VBB_Allowed</sub> (T <sub>A</sub> )       | Allowed I <sub>VBB</sub> :                                                                                                                                                                         |  |

|                                                  | $I_{VBB\_Allowed} = (150 - T_A - P_{VCC=xV} * R_{TH(JA)} - P_{Sink\_1\_3\_max} * 8 * R_{TH(JA)}) / (V_{VBB=xV} * R_{TH(JA)})$                                                                      |  |

|                                                  | $I_{VBB\_Allowed} = (150 - T_A - P_{VCC=xV} * R_{TH(JA)} - P_{Sink\_2\_max} * 8 * R_{TH(JA)}) / (V_{VBB=xV} * R_{TH(JA)})$                                                                         |  |

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

#### Prerequisites for calculating safety limits

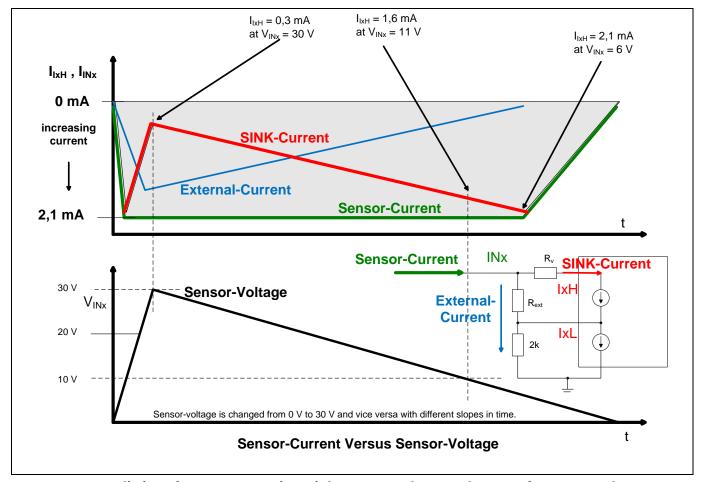

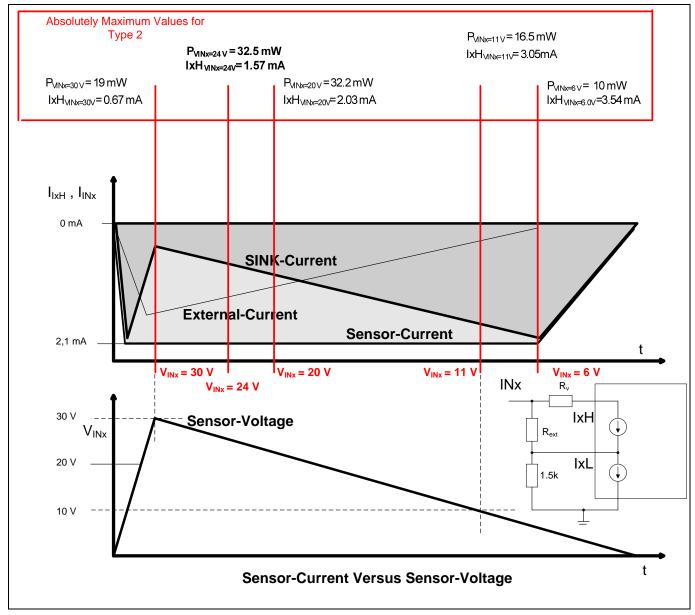

Figure 2 explains that only a part of the sense current is propagated through the internal current sinks of the sense chip. Figure 2 is contained in the datasheet (ISO1I815: Chapter 3.4 Sensor Input). The sense current is separated into a sink current and into an external current. In case of high sense voltage V<sub>INx</sub> a great part of the sense current is propagated through the external resistor network. In the case of low sense voltage V<sub>INx</sub> the sense current is mostly internally dissipated via the internal sinks. Therefore the power dissipation within the sense chip is minimized. In Figure 2 the sense current is assumed to be  $I_{INx} = 2.1$  mA.

The x-axis is the time during a simulation when the sensor voltage V<sub>INx</sub> is ramping up and down (from 0 V to 30 V) with different slopes.

Figure 2 Splitting of sensor current into sink current and external current for type 1 and 3 (IEC61131-2)

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Sink current

#### 4 Sink current

In Figure 2 the sense current is assumed to be  $I_{INx} = 2.1$  mA. This current is split into an internal sink current and an external current. Test results are available for this split. These results are extrapolated to the maximum values in the datasheet.

I<sub>INxsnkM13</sub> for type 1 and 3

and

$I_{INxsnkM2}$  for type 2.

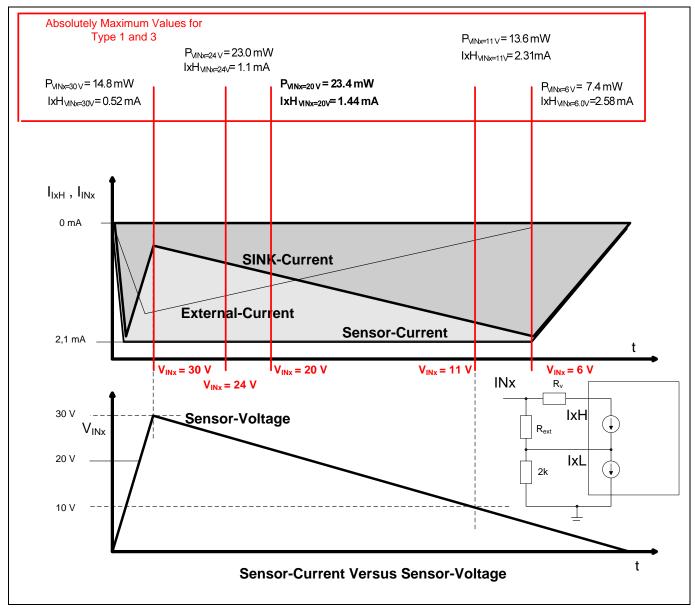

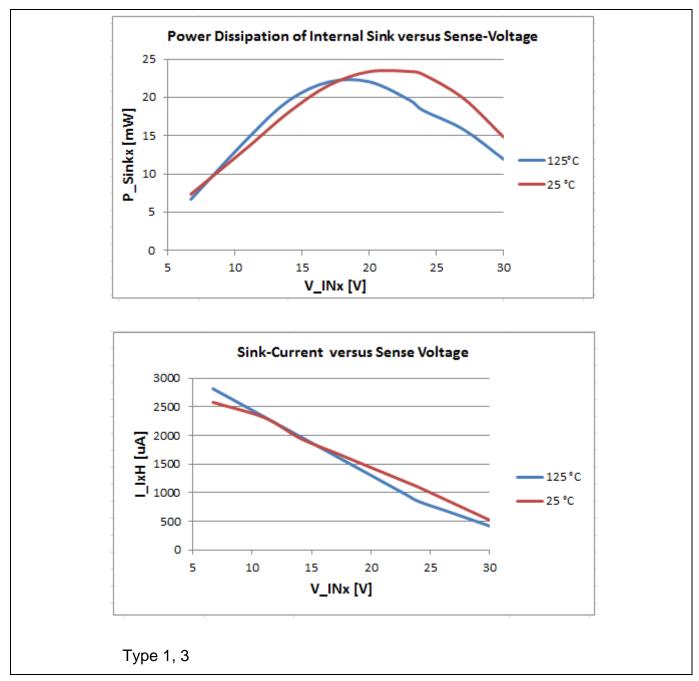

Figure 3 and Figure 4 determine the split values including the internal sink power dissipation for type 1 and 3.

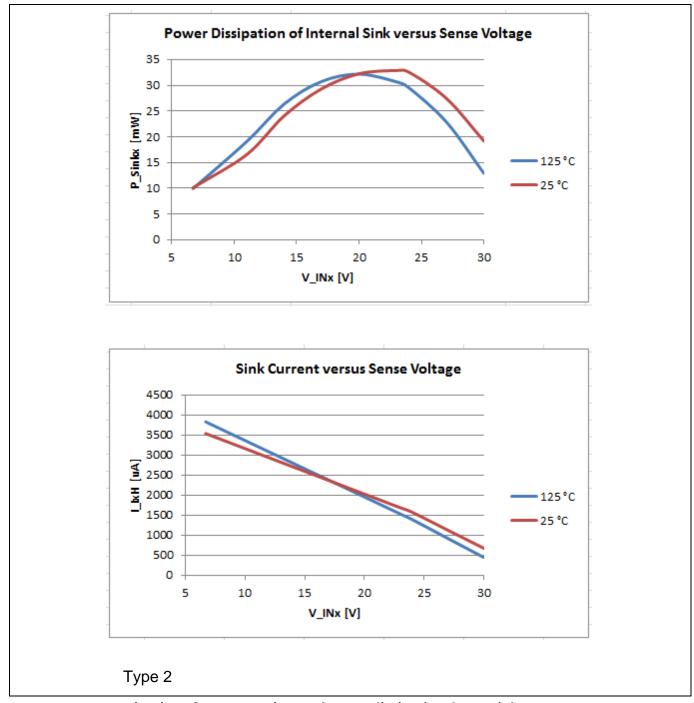

Figure 5 and Figure 6 determine the split values including the internal sink power dissipation for type 2.

Figure 3 Split of sense current, internal power dissipation, type 1 and 3

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Sink current

Figure 4 Determination of worst-case internal power dissipation due to sink current, type 1 and 3

For type 1 and 3 the maximum sink power dissipation is  $P_{Sink\_1\_3\_max} = 23.4$  mW.

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Figure 5 Split of sense current, internal power dissipation, type 2

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

**Sink current**

Figure 6 Determination of worst-case internal power dissipation due to sink current, type 2

For type 2 the maximum sink power dissipation is  $P_{Sink_2_max} = 32.5$  mW.

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Safety limits ISO1I813T, ISO1I815T

#### Safety limits ISO11813T, ISO11815T 5

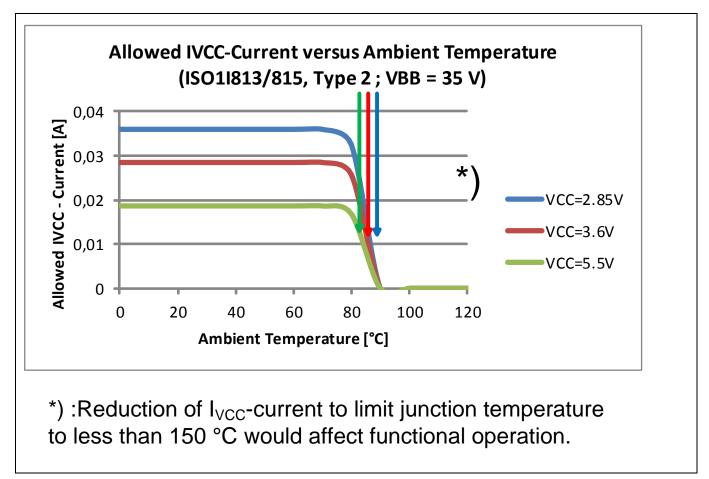

The maximum allowed power dissipation of the total chip (including two dies) is limited by two constraints: the junction temperature has to be less than T<sub>i</sub> = 150°C and the total power dissipation of the total chip (including two dies) has to be less than 0.8 W.

Based on the ambient temperature the temperature increase is calculated due to three power dissipation parts:

- 1. power dissipation of uC interface chip (dependent on V<sub>CC</sub>)

- 2. power dissipation of sense chip (dependent on VBB) and

- 3. power dissipation due to the sink currents.

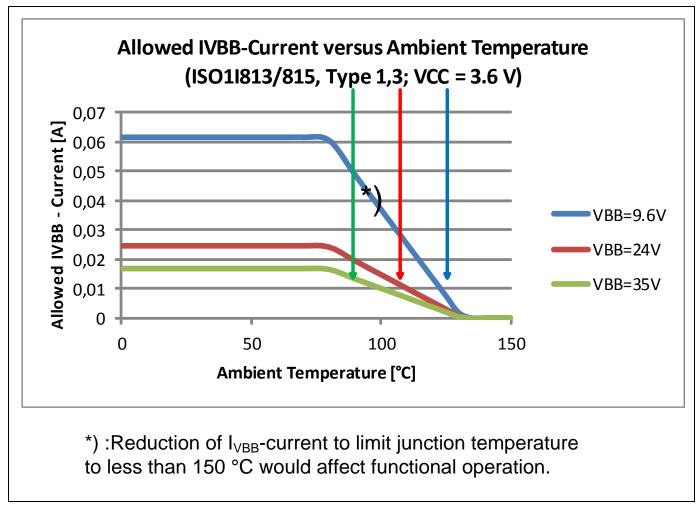

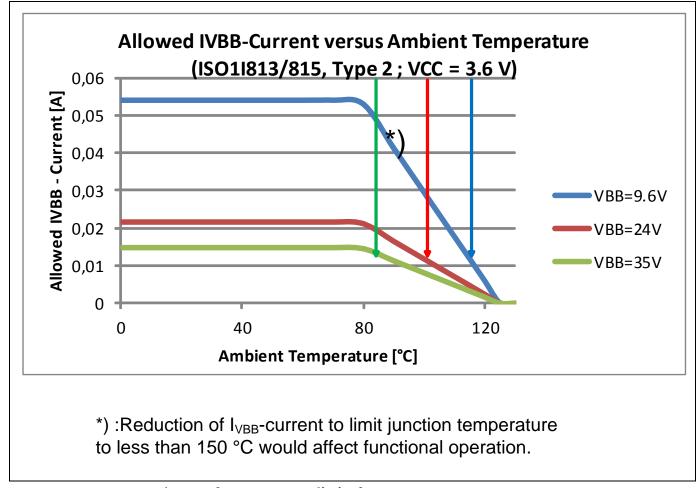

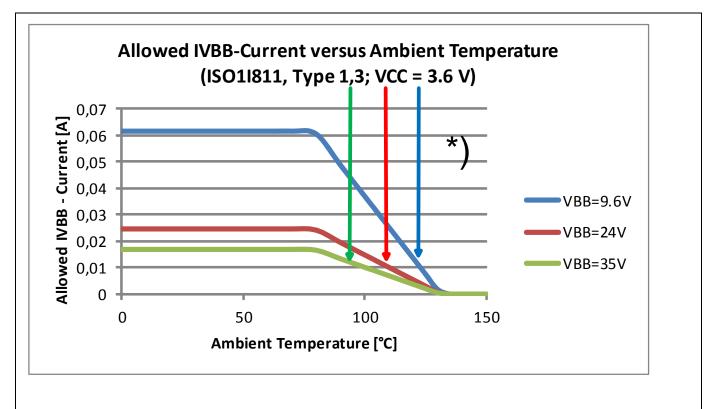

Figure 7 and Figure 8 give the allowed I<sub>VBB</sub> current independent of the ambient temperature. These figures contain the absolute worst-case condition of all incorporated parameters (except V<sub>CC</sub> = 3.6 V is fixed). The internal current consumption of the sense chip in addition to the value of VBB has the most severe effect on the power consumption.

In this calculation  $V_{CC} = 3.6 \text{ V}$  and  $V_{BB} = 9.6 \text{ V}$ , 24 V, 35 V.

#### **Condition:**

T less than or equal to 150°C and  $P_{tot}$  less than  $P_{tot max} =$

0.8 W allowed I<sub>VBB</sub>:

$(P_{VCC=3.6V} + P_{VBB=xV}) *R_{TH(JA)}$ + P<sub>Sink 1 3/\_2\_max</sub> \*8 \*R<sub>TH(JA)</sub> 150°C =  $T_{\Delta}$  +

+ P<sub>Sink 1 3/ 2\_max</sub> \*8  $P_{VCC=3.6V} + P_{VBB=xV}$  $P_{tot max} =$

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Safety limits ISO11813T, ISO11815T

Figure 7 ISO1I813T/815T: Safety I<sub>VBB</sub> current limits for type 1 and 3

V 1.0

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Safety limits ISO1I813T, ISO1I815T

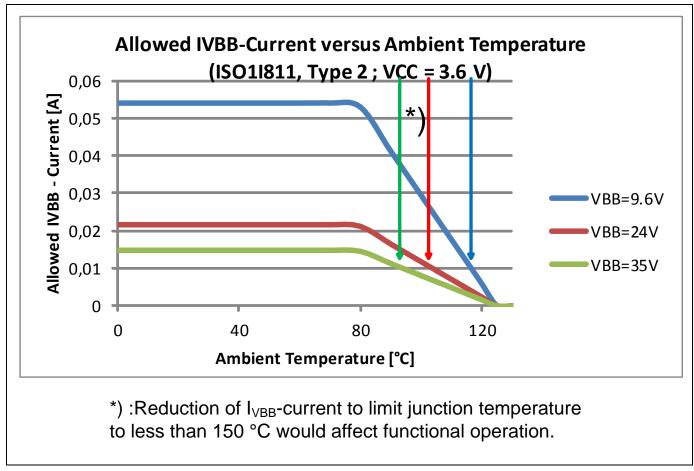

Figure 8 ISO11813/815: Safety I<sub>VBB</sub> current limits for type 2

Figure 7 and Figure 8 classify the lower values of ambient temperature from which no operation is allowed because the internal power dissipation already leads to a junction temperature of 150°C.

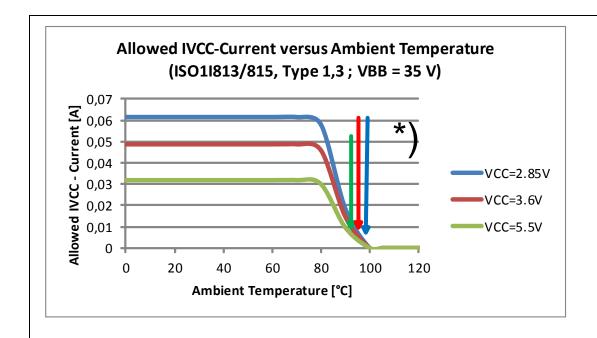

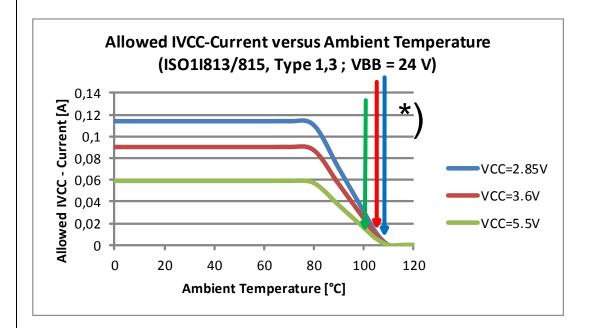

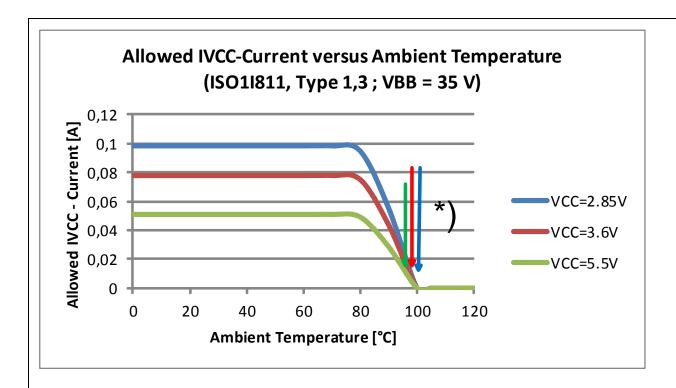

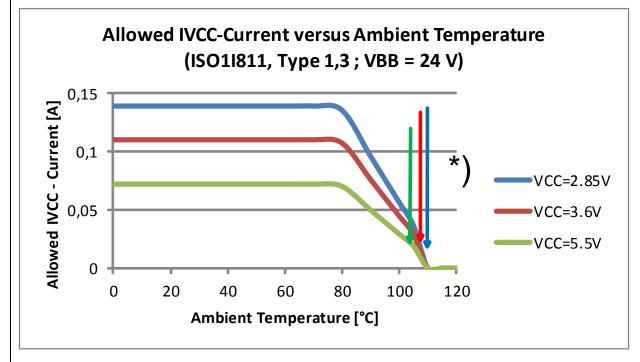

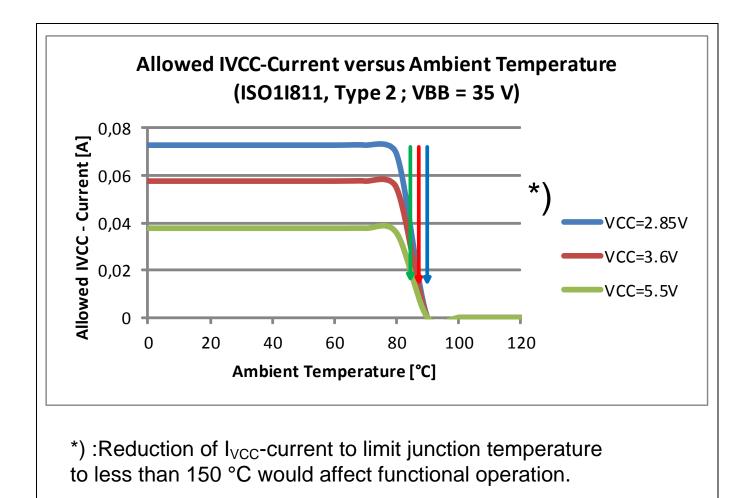

Figure 9 and Figure 10 give the allowed I<sub>VCC</sub> current independent of the ambient temperature. These figures contain the absolute worst-case condition of all incorporated parameters.

In this calculation  $V_{CC}$  = 2.85 V, 3.6 V, 5.5 V and  $V_{BB}$  = 24 V, 35 V.

## Condition: T less than or equal to 150°C and

$P_{tot}$  less than  $P_{tot\_max}$  =

0.8 W --> allowed  $I_{VCC}$ :

150°C =

$$T_A + (P_{VCC=xV} + P_{VBB=xV}) * R_{TH(JA)} + P_{Sink\_1\_3/\_2\_max} *8 * R_{TH(JA)}$$

$$P_{tot\_max} = P_{VCC=xV} + P_{VBB=xV} + P_{Sink\_1\_3/\_2\_max} *8$$

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Safety limits ISO1I813T, ISO1I815T

\*) :Reduction of I<sub>VCC</sub>-current to limit junction temperature to less than 150 °C would affect functional operation.

Figure 9 ISO11813T/815T: Safety I<sub>vcc</sub> current limits for type 1 and 3

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Safety limits ISO1I813T, ISO1I815T

ISO11813T/815T: Safety I<sub>vcc</sub> current limits for type 2 Figure 10

Figure 9 and Figure 10 classify the lower values of ambient temperature from which no operation is allowed because the internal power dissipation already leads to a junction temperature of 150°C.

Safety limits ISO1I811T

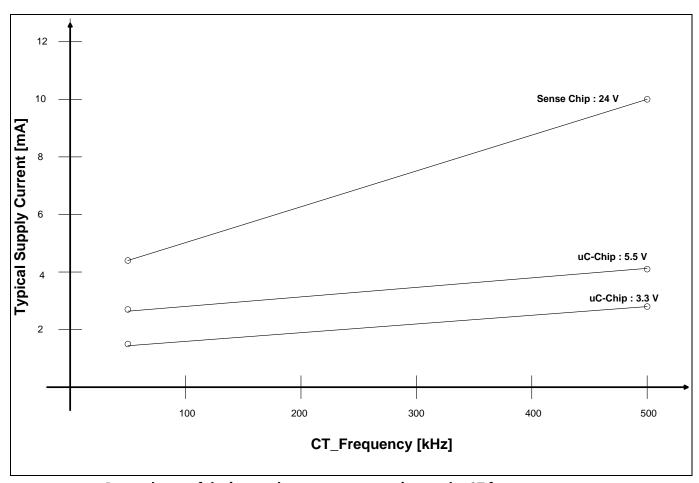

#### Safety limits ISO11811T 6

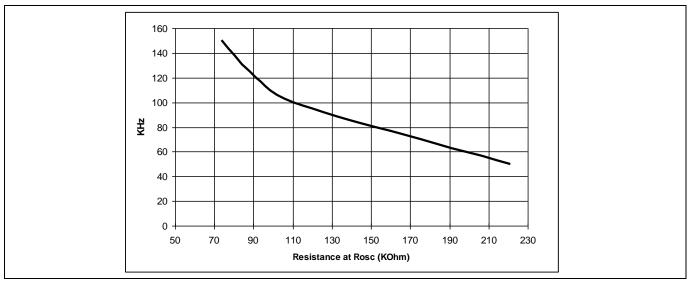

In the following the same safety limiting curves are calculated for the ISO1I811T. This circuitry operates with a reduced coreless transformer (CT) data rate (in the region of 100 kHz). Therefore the current consumption is less than for the ISO1I813/815. Figure 11 explains the linear behavior of the internal current consumption with the CT frequency. Figure 12 shows the method of adjustment of the CT frequency. Both figures are available in the datasheets.

Dependency of the internal current consumption on the CT frequency Figure 11

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Figure 12 Adjustment of the CT frequency by the Rosc resistance

\*) :Reduction of  $I_{VBB}$ -current to limit junction temperature to less than 150 °C would affect functional operation.

Figure 13 ISO1I811T: Safety IVBB current limits for type 1 and 3

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Safety limits ISO11811T

Figure 14 ISO1I811T: Safety I<sub>VBB</sub> current limits for type 2

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

Safety limits ISO1I811T

\*) :Reduction of I<sub>VCC</sub>-current to limit junction temperature to less than 150 °C would affect functional operation.

Figure 15 ISO11811: Safety I<sub>VCC</sub> current limits for type 1 and 3

Safety limits ISO11811T

Figure 16 ISO11811T: Safety I<sub>VCC</sub> current limits for type 2

ISOFACE™: ISO1I811T/ISO1I813T/ISO1I815T

# **Revision history**

| Document version | Date of release | Description of changes |

|------------------|-----------------|------------------------|

| V1.0             | 2018-05-17      | 1st release            |

|                  |                 |                        |

|                  |                 |                        |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2018-05-17

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2018 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference AN\_1802\_PL21\_1803\_160440

#### IMPORTANT NOTICE

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.