## SCU System Control Units

AURIX™ TC3xx Microcontroller Training V1.0 2020-09

# SCU System Control Units

#### **Highlights**

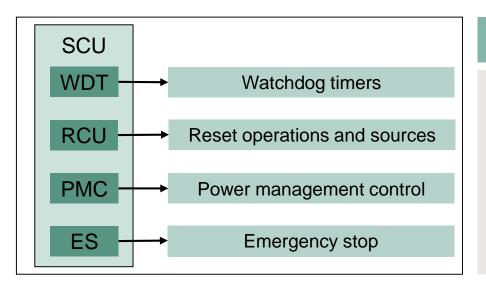

The SCU comprises various units, which handle reset operations (incl. effects and triggers), power management control (e.g. reducing power consumption) and many other miscellaneous submodules such as watchdogs.

#### **Key Features**

Watchdog timers

Reset operations and sources

Power management control

Emergency stop

#### **Customer Benefits**

- Robust failure detection and recovery

- Scalable reset concept based on different triggers

- Minimize power use during operation

- Fast reaction to emergency events without the SW intervention

#### WDT - Watchdog Timers

- The WatchDog Timers (WDTs) provide a highly reliable and secure way of detecting and recovering from software or hardware failure

- They can be used to abort any accidental malfunction of a CPU or internal module within a user-specified time period

- Additionally, each of the WDTs incorporates an End-of-Initialization (ENDINIT) feature which protects the critical registers from unintended writes

- To protect these functions a sophisticated scheme is implemented that requires a password and guard bits during the accesses to the WDT control registers. Any write access that does not provide the correct values for the password and guard bits is regarded as malfunction and results in an alarm

- On top of the general WDTs, a Safety Watchdog Timer is provided. It is independent from the CPU watchdogs and it also provides temporal protection against unintended writes to critical system registers which could impact the safety-critical systems

- These feature ensures that the system runs in a robust and safe manner (e.g. Trigger an alarm, a reset or stopping the CPU in case of malfunction)

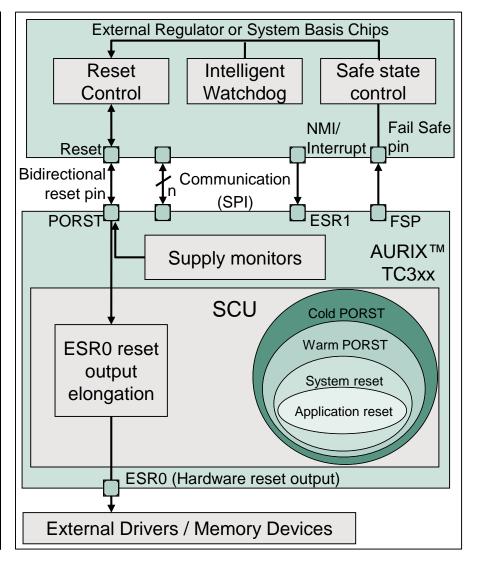

#### RCU – Reset types and effects

- AURIX™ TC3xx has a scalable reset concept, where different types of reset are encapsulated one into the other. The **Cold Power-On Reset** is the highest reset type, where the Embedded Voltage Regulator (EVR), internal clocks and RAMs are reset, additionally to the modules affected by the **Application Reset**, **System Reset** and **Warm Power-On Reset**

- SW Module Reset and Debug Reset enable the user to directly trigger a reset of the connected modules

| Reset Type             | Additional Modules affected by Cold Power-On Reset                                                                                                       | Additional Modules affected by Warm Power-On Reset                                                                           | Additional Modules affected by <b>System Reset</b>                                                                   | Modules affected by<br>Application Reset                                                                                                                  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cold Power-On<br>Reset | <ul> <li>&gt; Embedded Voltage</li> <li>Regulator</li> <li>&gt; Internal clocks</li> <li>&gt; RAMs:</li> <li>- DSPRs/PSPRs</li> <li>- LMU/BMU</li> </ul> | <ul> <li>JTAG interface</li> <li>OCDS</li> <li>MCDS</li> <li>SMU – Fault</li> <li>Signaling Protocol</li> <li>Pin</li> </ul> | <ul> <li>Flash memory</li> <li>Clock source</li> <li>PLL</li> <li>External Service</li> <li>Requests pins</li> </ul> | <ul> <li>All CPUs</li> <li>All Peripherals</li> <li>SCU</li> <li>Port pins in reset</li> <li>RAMs:         <ul> <li>Dcache invalid</li> </ul> </li> </ul> |

| Warm Power-On<br>Reset | A higher                                                                                                                                                 |                                                                                                                              |                                                                                                                      | - Pcache invalid                                                                                                                                          |

| System Reset           | A higher reset encapsulates a lower reset                                                                                                                |                                                                                                                              |                                                                                                                      |                                                                                                                                                           |

| Application Reset      |                                                                                                                                                          |                                                                                                                              |                                                                                                                      |                                                                                                                                                           |

| SW Module Reset        | Available for all CPUs, DMA channel, QSPI, CAN, ASCLIN, Ethernet, GTM, SENT, ADC, HSSL, CCU6                                                             |                                                                                                                              |                                                                                                                      |                                                                                                                                                           |

| Debug Reset            | OCDS and MCDS reset, all CPUs and peripherals (except SCU) are put into reset                                                                            |                                                                                                                              |                                                                                                                      |                                                                                                                                                           |

#### RCU – Reset types and sources

| Reset Type             | Source of reset                                                                                                                       |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Cold Power-on<br>Reset | <ul> <li>Startup</li> <li>Temporary power fail on any of the 3 supplies (VEXT&lt; 3.0 V; VDDP3 &lt;3.0V; VDD &lt; 1.125 V)</li> </ul> |  |

| Warm Power-on<br>Reset | PORST pad asserted                                                                                                                    |  |

| System Reset           | <ul> <li>&gt; ESR0/ESR1</li> <li>&gt; SMU</li> <li>&gt; STMx</li> <li>&gt; Watchdog (SMU)</li> <li>&gt; Software reset</li> </ul>     |  |

| Application Reset      | <ul> <li>&gt; ESR0/ESR1</li> <li>&gt; SMU</li> <li>&gt; STMx</li> <li>&gt; Software reset</li> <li>&gt; Tuning protection</li> </ul>  |  |

| SW Module Reset        | > Configurable by registers                                                                                                           |  |

| Debug Reset            | <ul><li>OCDS request trigger</li><li>JTAG reset</li></ul>                                                                             |  |

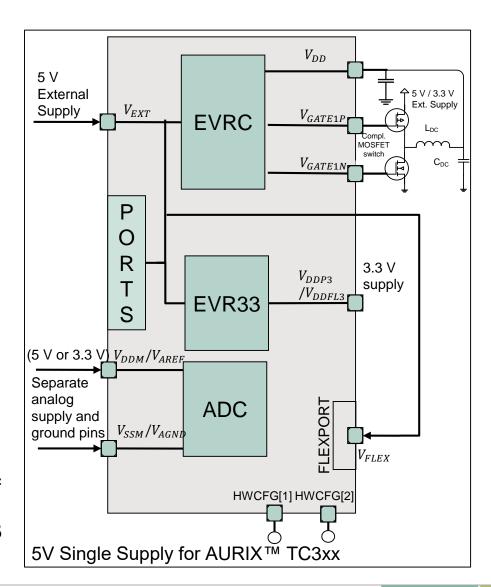

### PMC – Single source power supply concept

- AURIX™ devices support different supply modes:

- Single 5 V source supply

- Single 3.3 V source supply

- Dual supply modes

- AURIX™ contains 2 separate parallel Embedded Voltage Regulators (EVR33 and EVRC) generating 3.3 V and 1.3 V supply voltages from the external supply

- All supply and generated voltages are monitored internally against overshoot and brownout conditions based on programmable thresholds

- The reaction to these situations is triggering either a cold Power-On Reset or an alarm

- This approach reduces the complexity of the system, since additional regulators are not needed to obtain the 3.3 V or 1.3 V voltages

### PMC – Idle, Sleep & Standby modes

- The power management scheme allows activation of power down modes so that the system operates with the minimum required power for the corresponding application state

- A progressive reduction in power consumption is achieved by invoking Idle, Sleep or Standby modes

- The Idle mode is specific to each individual CPU, while the Sleep and Standby modes influence the complete system

| Mode/Current   | Description                                                                              | Entry/Exit                                                                                                                                                                                     |

|----------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPUx Run       | Normal operation                                                                         | -                                                                                                                                                                                              |

| CPUx Idle      | The CPU clock is disabled. All peripherals remain active.                                | Entry: via Software, SMU<br>Exit: on CPUx Interrupt, Trap, Reset                                                                                                                               |

| System Sleep   | Peripheral clocks are gated if configured by control registers. All CPUs are set to IDLE | Entry: via Software<br>Exit: on CPUx Interrupt, Trap, Reset                                                                                                                                    |

| System Standby | Main domain is powered off. Standby RAM may be active                                    | Entry: via Software, NMI Exit: on edge detection on NMI/pins, PORST assertion In case of separate standby supply pin: entry & exit are done on the VEXT supply ramp-down, respectively ramp-up |

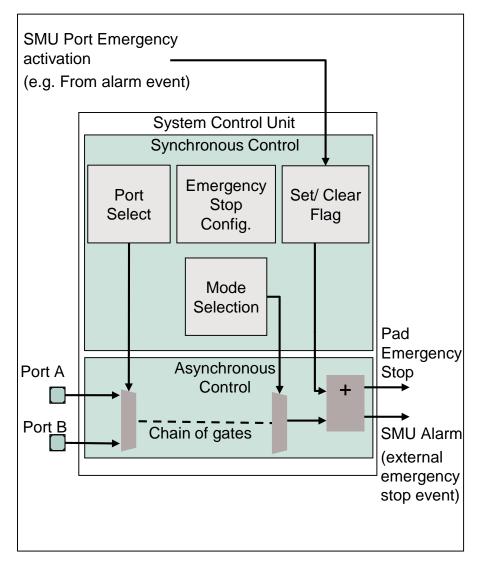

#### **Emergency Stop**

- The emergency stop feature provides a fast reaction to an emergency event without the intervention of the software. As reaction to the emergency event, selected output ports can be immediately placed into a defined state (e.g. bring the actuators in a known state)

- An emergency stop can be triggered by the following:

- A transition on the port which is configured as the Emergency Stop input

- An alarm event or command from the Safety Management Unit that is configured to generate a port emergency stop

- The emergency stop control logic for the ports operates in two modes:

- Synchronous mode (default): the emergency case is activated by hardware and released by software

- Asynchronous mode: both the activation and releasing of the emergency case are done by hardware

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2020-09 Published by Infineon Technologies AG 81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference AURIX\_Training\_2\_System\_Control\_Units

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.