# MTU Memory Test Unit

AURIX<sup>™</sup> TC3xx Microcontroller Training V1.0 2020-06

Please read the Important Notice and Warnings at the end of this document

# MTU Memory Test Unit

| Key Features                                                 | Customer Benefits                                                                            |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Memory Initialization                                        | <ul> <li>Fills the memories with a pre-defined<br/>data value for initialization</li> </ul>  |

| Memory Built-In-Self-Test (MBIST)                            | <ul> <li>Verification of integrity of the internal<br/>SRAMs realized in hardware</li> </ul> |

| Unified interface to internal SRAM Support<br>Hardware (SSH) | <ul> <li>SSH provides a direct access to the<br/>memories, without CPU overload</li> </ul>   |

## MTU Memory Initialization

- > Each SRAM in the system can be individually initialized via the MTU

- > The MTU offers two initialization options:

- Clear an SRAM by writing "0" to all memory locations

- User only needs to set one bit in a register to have a cleared SRAM

- Everything else is done in hardware

- CPU is not used to access the SRAM

- Fill up a SRAM with a defined pattern chosen by the user

- User needs to provide the pattern to be written in the SRAM and start the write operation

- CPU is not used to access the SRAM

- The MTU protects the security sensitive memories against unintended initialization

# MTU Memory Built-In-Self-Test (MBIST)

- The MTU enables the user to perform various Memory Built-in Self Tests (MBIST) on the memory and the test results are signaled via an interrupt

- The MTU MBIST relies on an Error Correction Code which has the following characteristics:

- Single Bit Error Correction

- Double Bit Error Detection

- > The MTU also sends alarm notification to Safety Management Unit (SMU):

- The MTU sends SRAM specific alarms to the SMU

- Correctable Error alarm

- Uncorrectable Critical Error alarm

- Miscellaneous Error alarm

### MTU Unified interface to internal SRAM Support Hardware

- Each SRAM has some digital logic surrounding it, known as SRAM Support Hardware (SSH)

- The SSH controls the Error Detection & Correction and the Memory Built-In-Self-Test (MBIST) of internal memories

- There are multiple SSH instances, each controlling one or more different internal memories:

- The MTU provides a unified register interface to control the operation of each SSH instance

- MTU can control directly the SSH instances for various test types on each SRAM block

- The SSH provides direct access to the memories, without involving the CPU

- Even small memories that are not directly accessible via the CPU can be tested via SSH

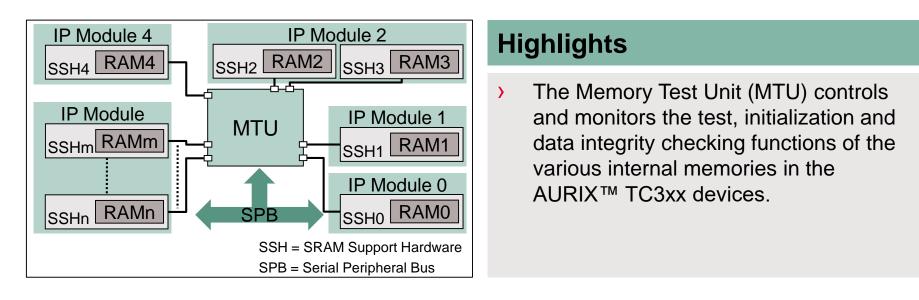

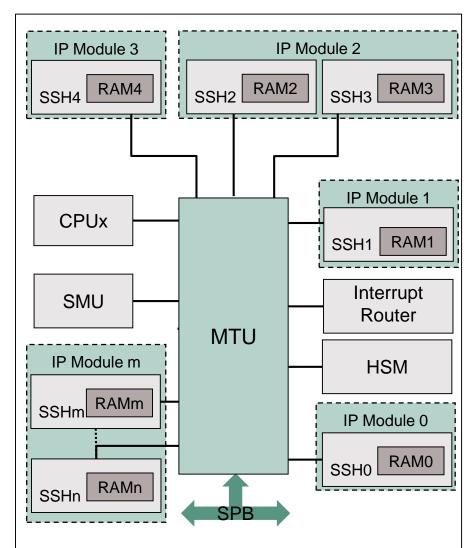

### MTU System Integration

- The MTU is a unified interface for the control of MBIST, ECC and memory initialization

- Different IP modules in the system (E.g. CPU, LMU, CAN etc.) may have one or more than one SRAM inside them

- Surrounding every SRAM is its own SRAM Support Hardware (SSH) wrapper

- The MTU also ensure the protection of security sensitive memories against unintended initialization that might lock the device

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2020-06 Published by Infineon Technologies AG 81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: <u>erratum@infineon.com</u>

Document reference AURIX\_Training\_2\_Memory\_Test\_Unit

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.