# EBU External Bus Unit

AURIX™ TC3xx Microcontroller Training V1.0 2020-09

## EBU External Bus Unit

## **Highlights**

- Allows to connect high variety of external memories

- Highly programmable access parameters for extended configuration capabilities to configure Bus components (Burst Flash, synchronous & asynchronous SRAM, NAND Flash, FPGA...)

## **Key Features**

Burst FLASH support

Synchronous SRAM support

Highly programmable access parameters

#### **Customer Benefits**

- Extend the NVM capabilities for large SW Projects (code and constants)

- Extend the VM capabilities for large SW Projects (data)

- Wide variety of external memories can be supported

# EBU Burst FLASH support

The Memory Controller is designed to generate waveforms compatible with the access modes of:

- INTEL and compatible burst flash devices

- SPANSION and compatible burst flash devices

- Samsung OneNAND™ burst capable NAND flash and compatible devices

- M-Systems DiskOnchipG3 and compatible devices

# EBU

## Synchronous SRAM support

The Memory Controller is designed to generate waveforms compatible with the asynchronous/synchronous modes of:

- Standard asynchronous SRAM

- Standard synchronous SRAM

- INFINEON and MICRON cellular RAM

- Fujitsu and compatible FCRAM™/uTRAM™/CosmoRAM

- SSRAM from e.g. GSI/ISSI/IDT

#### **EBU**

- Fully synchronous/asynchronous timing with flexible programmable timing parameters (address cycles, read wait cycles, data cycles). This allows optimized control waveforms to be generated for controlling accesses to the attached memory devices

- Programmable WAIT function, which allows support of memory devices with a variable access latency

- Programmable burst (mode and length)

- 8-bit/16-bit/32-bit device width

- Page mode read accesses

- Resynchronization of read data to a feedback clock to maximize the frequency of operation (optional)

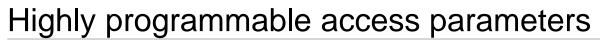

# **EBU**

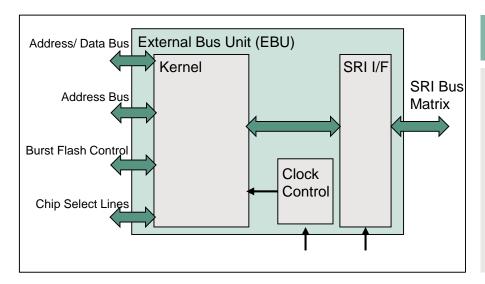

# System integration

- The Memory Controller module for SRI-based systems connects onchip controller cores (e.g. TriCore™ CPU, DMA Controller) to external resources such as memories and peripherals

- Any SRI master can (in conjunction with an SRI Matrix) access external memories through the Memory Controller

- A pin multiplexing scheme has been implemented to allow the use of low power, 5 V compatible pads for the 32 bit data bus

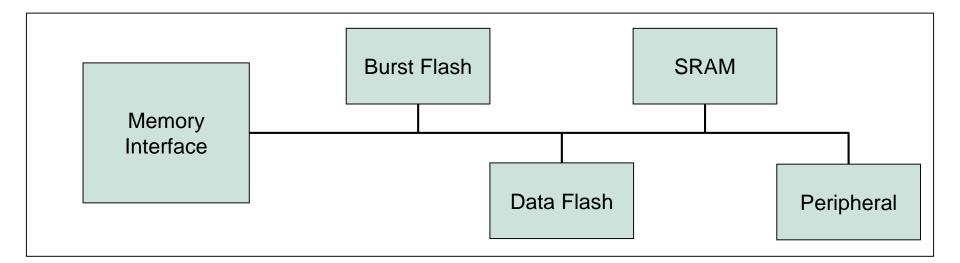

# Application example Typical external memory system

#### **Overview**

- External Flash memory

- External SRAM memory

### **Advantages**

- Extend the memory capabilities for large SW Projects (code, constants and data)

- Multiplexed access (address & data on the same bus)

- Data buffering (1 single write buffer to SRI & 2 read buffers)

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2020-09 Published by Infineon Technologies AG 81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference AURIX\_Training\_2\_External\_Bus\_Unit

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.