# SPI\_TLF\_1 for KIT\_AURIX\_TC397\_TFT QSPI communication with TLF35584

AURIX<sup>™</sup> TC3xx Microcontroller Training V1.0.1

Please read the Important Notice and Warnings at the end of this document

# A QSPI module configured as SPI master communicates with the TLF35584 device via SPI protocol.

QSPI2 is configured in master mode and used to send data frames to TLF35584 device via SPI protocol. The TLF35584 device is set to the NORMAL state and, in case of success, the LED D104 is turned on. This training focuses on the SPI communication between QSPI module and TLF35548 device. Typical application use case and the features of the TLF35584 device are not covered by this training.

## Introduction

- The Queued Synchronous Peripheral Interface (QSPI) enables synchronous serial communication with external devices based on the standardized SPI-bus signals: clock, data-in, data-out and slave select

- The QSPI works in full duplex mode either as Master or Slave with up to 50 MBit/s

- The TLF35584 is a multiple output system-supply for safety-relevant applications supplying 5 V or 3.3 V microcontrollers, transceivers, and sensors by an efficient and flexible pre-/post-regulator concept over a wide input voltage range

- Multiple safety features enable easy realization of ASIL-D together with various µCs (e.g. AURIX<sup>™</sup> TC2xx, TC3xx families)

## Hardware setup

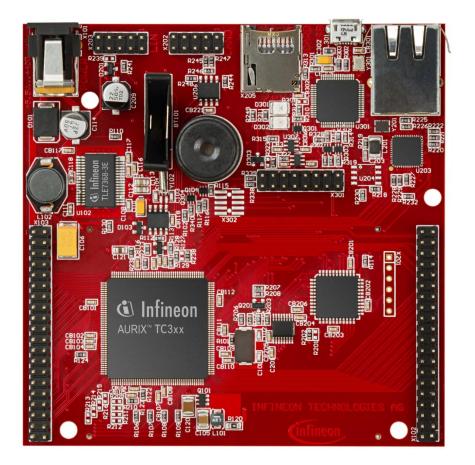

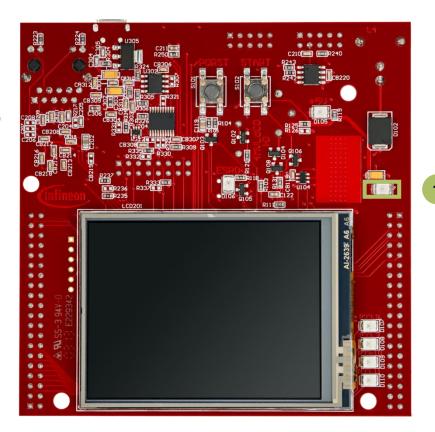

This code example has been developed for the board KIT\_A2G\_TC397\_5V\_TFT.

## Implementation

#### **Configuring the SPI communication**

The configuration of the SPI communication is done once in the setup phase through the function *initQSPI()*.

#### **QSPI** Master initialization

- The initialization of the QSPI master module is done by defining an instance of the *lfxQspi\_SpiMaster\_Config* structure

- The structure is filled with default values by the function IfxQspi\_SpiMaster\_initModuleConfig()

- Afterwards, the interface operation mode, the pins, ISR service provider and the priorities are set

| AURIX <sup>™</sup> designation | Port pin | TLF35584 designation |

|--------------------------------|----------|----------------------|

| QSPI2_SCLK                     | P15.8    | SCL                  |

| QSPI2_MTSR                     | P15.6    | SDI                  |

| QSPI2_MRSTB                    | P15.7    | SDO                  |

| QSPI2_SLSO1                    | P14.2    | SCS                  |

## **QSPI** Master initialization (continued)

- > The function *lfxQspi\_SpiMaster\_initModule()* is used to initialize the QSPI master module

- A QSPI module controls 16 communication channels, which are individually programmable. In this training, the function *initQSPI2MasterChannel()* initializes the channel 1 using an instance of the structure *IfxQspi\_SpiMaster\_ChannelConfig*

- The following parameters reflect the SPI related parameters provided in the SPI-Serial Peripheral Interface chapter of the TLF35584's Data Sheet:

- spiMasterChannelConfig.base.baudrate = 5000000 define the baud rate (set SCLK frequency to 5 MHz)

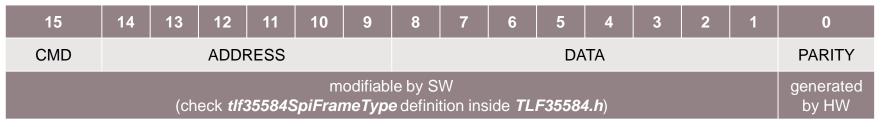

- spiMasterChannelConfig.base.mode.dataWidth = 15 define transfer data width (the total data width is 16 containing 15 bits of actual data plus 1 parity bit generated by hardware)

- spiMasterChannelConfig.base.mode.csTrailDelay = 2 define trailing delay

- spiMasterChannelConfig.base.mode.csInactiveDelay = 2 define inactive delay

- spiMasterChannelConfig.base.mode.shiftClock =

Spilf\_ShiftClock\_shiftTransmitDataOnTrailingEdge define that the data is shifted out (transferred to the Tx pin) on the trailing edge

### **QSPI** Master initialization (continued)

- > Additionally, automatic hardware parity generation/check is used in this example

- spiMasterChannelConfig.base.mode.parityCheck = TRUE define that automatic hardware parity generation/check is enabled

- spiMasterChannelConfig.base.mode.parityMode = lfx\_ParityMode\_even define usage of the even parity mode

- > The function *lfxQspi\_SpiMaster\_initChannel()* is used to initialize the QSPI master channel

- > Additionally, the buffers used by the QSPI master are initialized

The above functions can be found in the iLLD header *IfxQspi\_SpiMaster.h*.

### **QSPI Master – TLF35584 communication**

- The function transferDataTLF35584() triggers the data transfer between the SPI Master and the TLF35584 device

- Before data transfer, the SPI frame is assembled in the following format as defined in the SPI-Serial Peripheral Interface chapter of the TLF35584's Data Sheet:

- The function *IfxQspi\_SpiMaster\_getStatus()* is used to check the status of the master in order to wait until there is no ongoing transmission

- The function *lfxQspi\_SpiMaster\_exchange()* is called in order to instruct the master to send the data

The above functions can be found in the iLLD header *IfxQspi\_SpiMaster.h*.

### **TLF35584** initialization

The initialization of the TLF35584 device is done once in the setup phase through the function *initTLF35584()*.

- Certain TLF35584 internal registers need to be protected against being overwritten accidently. Write access to these registers is only possible after a dedicated 32 bit UNLOCK sequence has been sent via SPI.

Function *unlockRegisterTLF35584()* implements UNLOCK sequence that consists of a 32bit sequence of 4 consecutive bytes (1: 0xAB; 2:0xEF; 3:0x56; 4:0x12) which are sent with no other SPI write access in between

- Functions disableWindowWatchdogTLF35584() and disableErrPinMonitorTLF35584() disable the window watchdog and error pin monitoring functionality of the TLF35584 device. For more details, please refer to the State Machine, the Safe State Control Function and the Window Watchdog and Functional Watchdog chapters of the TLF35584's Data Sheet

#### TLF35584 initialization (continued)

- All protected configuration request register values are captured by the respective functions only after a successful LOCK sequence has been performed

- Function *lockRegisterTLF35584()* implements LOCK sequence that consists of a 32-bit sequence of 4 consecutive bytes (1: 0xDF; 2:0x34; 3:0xBE; 4:0xCA) which have to be sent with no other SPI write access in between

- Upon detection of a successful LOCK sequence the configuration registers and all internal functions are updated with the values from the protected configuration request registers

- The function enableVoltageSupplyRails() is used to avoid the SMU alarm activation for the External Voltage Regulator (EVR) under-voltage by enabling the voltage supply rails

The above functions can be found in the source and header files *TLF35584.c*, *TLF35584.h*.

### Application code

After QSPI module (*initQSPI()*) and TLF35584 device initialization (*initTLF35584()*), the following steps are performed:

- Check if any error flag has been raised during the TLF35584 device initialization (getSystemStatusFlagsTLF35584()) and if this is the case, clear the flag (clearSystemStatusFlagsTLF35584())

- Wait (*IfxStm\_waitTicks()*) the nominal delay time (60 µs) required by the device to be set to NORMAL state as defined in the TLF35584 Datasheet

- Set the TLF35584 device state to NORMAL (check the State Machine chapter of the TLF35584's Data Sheet for the details) by using *setStateTransitionTLF35584()* function. The LED D104 that is connected to the safe state signal SS2 turns on

- Check if any error was triggered (*getSystemStatusFlagsTLF35584()*) and if the device state does not correspond to the NORMAL state (*getCurrentStateTLF35584()*)

The above functions can be found in the source and header files *TLF35584.c*, *TLF35584.h*.

# Run and Test

After code compilation and programming the device, perform the following steps:

- Check if the LED D104 (1) is on (TLF35584 device reached NORMAL state)

- Additionally, in an opened debug session, breakpoints can be set in *transferDataTLF35584()* function located in the *SPI\_TLF.c* to check the *spiMasterTxBuffer* and *spiSlaveRxBuffer* inside *g\_qspi.spiBuffers* structure

- To re-run the code example, the board should be power-cycled (power off / power on sequence)

## References

>

- AURIX<sup>™</sup> Development Studio is available online:

- https://www.infineon.com/aurixdevelopmentstudio

- Use the *"Import…"* function to get access to more code examples. >

- More code examples can be found on the GIT repository: >

- https://github.com/Infineon/AURIX code examples >

- For additional trainings, visit our webpage: >

- https://www.infineon.com/aurix-expert-training >

- For questions and support, use the AURIX<sup>™</sup> Forum: >

- https://www.infineonforums.com/forums/13-Aurix-Forum >

## **Revision history**

| Revision | Description of change                               |  |

|----------|-----------------------------------------------------|--|

| V1.0.1   | Fixed typo in function getSystemStatusFlagsTLF35584 |  |

| V1.0.0   | Initial version                                     |  |

|          |                                                     |  |

|          |                                                     |  |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2023-03 Published by Infineon Technologies AG 81726 Munich, Germany

© 2023 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: <u>erratum@infineon.com</u>

Document reference SPI\_TLF\_1\_KIT\_TC397\_TFT

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.