SPI\_CPU\_1

for KIT\_AURIX\_TC397\_TFT

SPI communication via QSPI

AURIX™ TC3xx Microcontroller Training V1.0.1

### Scope of work

# A QSPI module configured as SPI master sends five bytes to another QSPI module which is configured as SPI slave.

QSPI2 is configured in master mode and used to send five bytes to QSPI3 configured in slave mode. The received data is read by the CPU and compared against the transmitted data. Port pin 13.3, to which LED D110 is connected, indicates the successful transfer.

### Introduction

- The Queued Synchronous Peripheral Interface (QSPI) enables synchronous serial communication with external devices based on the standardized SPI-bus signals: clock, data-in, data-out and slave select.

- The QSPI works in full duplex mode either as Master or Slave with up to 50 MBit/s.

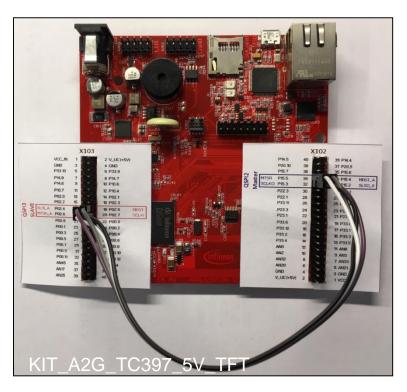

## Hardware setup

This code example has been developed for the board KIT\_A2G\_TC397\_5V\_TFT.

## Hardware Setup

| X103   |    |    |        |  |  |

|--------|----|----|--------|--|--|

| VCC_IN | 1  | 2  | V_UC   |  |  |

| GND    | 3  | 4  | GND    |  |  |

| P21.2  | 5  | 6  | P21.3  |  |  |

| P14.8  | 7  | 8  | P14.7  |  |  |

| P14.6  | 9  | 10 | P20.0  |  |  |

| P21.4  | 11 | 12 | P21.5  |  |  |

| P02.0  | 13 | 14 | P02.1  |  |  |

| P02.2  | 15 | 16 | P02.3  |  |  |

| P02.4  | 17 | 18 | P02.5  |  |  |

| P02.6  | 19 | 20 | P02.7  |  |  |

| P02.8  | 21 | 22 | P00.0  |  |  |

| P00.1  | 23 | 24 | P00.2  |  |  |

| P00.3  | 25 | 26 | P00.4  |  |  |

| P00.5  | 27 | 28 | P00.6  |  |  |

| P00.7  | 29 | 30 | P00.8  |  |  |

| P00.9  | 31 | 32 | P00.10 |  |  |

| P00.11 | 33 | 34 | P00.12 |  |  |

| AN19   | 35 | 36 | AN18   |  |  |

| AN17   | 37 | 38 | AN16   |  |  |

| AN25   | 39 | 40 | AN24   |  |  |

Use the stencils as illustrated.

|        |    | 02 | ı      |

|--------|----|----|--------|

| P14.5  | 40 | 39 | P14.4  |

| P33.10 | 38 | 37 | P20.9  |

| P15.7  | 36 | 35 | P15.6  |

| P15.5  | 34 | 33 | P15.4  |

| P15.3  | 32 | 31 | P15.2  |

| P22.3  | 30 | 29 | P22.2  |

| P22.1  | 28 | 27 | P22.0  |

| P33.11 | 26 | 25 | P23.4  |

| P23.3  | 24 | 23 | P23.2  |

| P23.1  | 22 | 21 | P23.0  |

| P33.6  | 20 | 19 | P33.8  |

| P33.12 | 18 | 17 | P33.1  |

| P33.2  | 16 | 15 | P33.3  |

| P33.4  | 14 | 13 | P33.5  |

| AN0    | 12 | 11 | AN8    |

| AN2    | 10 | 9  | AN3    |

| AN11   | 8  | 7  | AN13   |

| AN20   | 6  | 5  | AN21   |

| GND    | 4  | 3  | GND    |

| V_UC   | 2  | 1  | VCC_IN |

Connect following pins as described and illustrated using wires.

| X103 : QSPI3 (Slave) | WIRE                     | X102 : QSPI2 (Master) |

|----------------------|--------------------------|-----------------------|

| P02.7 : 20 : SCLKI   | $\leftarrow \rightarrow$ | P15.3 : 32 : SCLKO    |

| P02.4 : 17 : SLSI_A  | $\leftarrow \rightarrow$ | P15.2 : 31 : SLSO_0   |

| P02.5 : 18 : MRST    | $\leftarrow \rightarrow$ | P15.4 : 33 : MRST_A   |

| P02.6:19:MTSR_A      | $\leftarrow \rightarrow$ | P15.5 : 34 : MTSR     |

# infineon

### **Implementation**

#### **Configuring the SPI communication**

The configuration of the SPI communication is done once in the setup phase through the function *initQSPI()* in two different steps:

- QSPI Slave initialization

- QSPI Master initialization

#### **QSPI Slave initialization**

- The initialization of the QSPI slave module is done by defining an instance of the IfxQspi\_SpiSlave\_Config structure.

- The structure is filled with default values by the function IfxQspi\_SpiSlave\_initModuleConfig().

- Afterwards, the pins, ISR service provider and the priorities are set.

- The function IfxQspi\_SpiSlave\_initModule() is used to initialize the QSPI slave module.

- Additionally, the buffers used by the QSPI slave are initialized.

The above functions can be found in the iLLD header *IfxQspi\_SpiSlave.h*.

# infineon

### **Implementation**

#### **QSPI** Master initialization

- The initialization of the QSPI master module is done by defining an instance of the IfxQspi\_SpiMaster\_Config structure.

- The structure is filled with default values by the function IfxQspi\_SpiMaster\_initModuleConfig().

- Afterwards, the interface operation mode, the pins, ISR service provider and the priorities are set.

- The function IfxQspi\_SpiMaster\_initModule() is used to initialize the QSPI master module.

- A QSPI module controls 16 communication channels, which are individually programmable. In this example, the function *initQSPI2MasterChannel()* initializes the channel zero using an instance of the structure *IfxQspi\_SpiMaster\_ChannelConfig*. Afterwards, the slave select channel number is set through the parameter *sls.output* and the baud rate is modified via the parameter *base.baudrate*.

- The function IfxQspi\_SpiMaster\_initChannel() is used to initialize the QSPI master channel.

- Additionally, the buffers used by the QSPI master are initialized.

The above functions can be found in the iLLD header *IfxQspi\_SpiMaster.h*.

### **Implementation**

#### **QSPI Master - Slave communication**

- The function transferData() triggers the data transfer between the SPI-Master and the SPI-Slave

- The functions IfxQspi\_SpiSlave\_getStatus() and IfxQspi\_SpiMaster\_getStatus() are used to check the status of the master and the slave in order to delay the transfer until both are free

- The function IfxQspi\_SpiSlave\_exchange() instructs the slave to receive a data stream of predefined length

- The function IfxQspi\_SpiMaster\_exchange() is called in order to instruct the master to send the data

- Finally, the function verifyData() checks if the data received by the Slave matches the data sent by the Master

- If no errors have occured during the communication, the LED D110, connected to port pin 13.3, is turned on to signal that the transmission was successful

### **Implementation**

#### **Configure and control the LEDs**

The LED is turned on and off by **controlling the port pin** to which it is connected using methods from the iLLD headers *IfxPort.h*.

The LED port pin is **configured to output push-pull mode** using the function *IfxPort\_setPinModeOutput()*.

During program execution, the LED is **switched on and off** using the functions **IfxPort\_setPinLow()** and **IfxPort\_setPinHigh()**.

### Run and Test

After code compilation and programming the device, perform the following steps:

- Set a breakpoint to transferData() in the Cpu0\_main.c and check the spiMasterTxBuffer and spiSlaveRxBuffer inside spiBuffers structure.

- Run the code example and check if the LED D110 (1) is on (Data transmitted without errors).

- The spiMasterTxBuffer and spiSlaveRxBuffer now should show the same transmitted and received data.

- Remove a cable (e.g. SCLKx), perform a Reset and re-run the application to see that the data transmission is interrupted and the LED D110 (1) is off (Data transmission blocked).

Note: when checking the buffers' data, the debug session must be paused.

### References

- > AURIX™ Development Studio is available online:

- https://www.infineon.com/aurixdevelopmentstudio

- Use the "Import…" function to get access to more code examples.

- More code examples can be found on the GIT repository:

- https://github.com/Infineon/AURIX\_code\_examples

- For additional trainings, visit our webpage:

- https://www.infineon.com/aurix-expert-training

- For questions and support, use the AURIX™ Forum:

- https://www.infineonforums.com/forums/13-Aurix-Forum

## Revision history

| Revision | Description of change                                           |

|----------|-----------------------------------------------------------------|

| V1.0.1   | Update of version to be in line with the code example's version |

| V1.0.0   | Initial version                                                 |

|          |                                                                 |

|          |                                                                 |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2020-12 Published by Infineon Technologies AG 81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference SPI\_CPU\_1\_KIT\_TC397\_TFT

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (<a href="www.infineon.com">www.infineon.com</a>).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.