# **QSPI** Queued Synchronous Peripheral Interface

AURIX<sup>™</sup> TC2xx Microcontroller Training V1.0 2019-03

Please read the Important Notice and Warnings at the end of this document

## QSPI Queued Synchronous Peripheral Interface

#### Highlights

QSPI module provides synchronous serial communication with external devices using clock, data-in, data-out and slave select signals.

- > Master and Slave full duplex operation

- > Up to 50 Mbit/s

| Key Features          | Customer Benefits                                                                 |

|-----------------------|-----------------------------------------------------------------------------------|

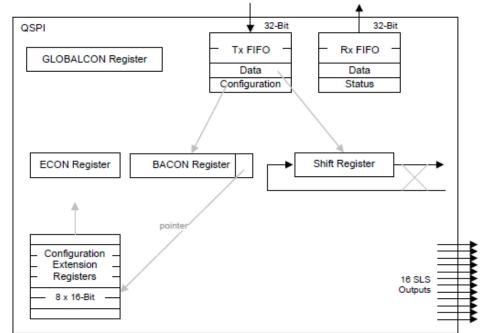

| Queue support         | <ul> <li>Configuration and data via the same<br/>Queue (Tx or Rx FIFO)</li> </ul> |

| Flexible frame format | <ul> <li>Configurable shift direction, clock polarity<br/>and phase</li> </ul>    |

- The Tx-FIFO could keep the data to be sent and additionally the configuration data for the SPI module

- This enables dynamic and comfortable switching of SPI frame timings and data configuration independent for each channel:

- Data length

- LSB/MSB shift first

- Clock polarity and clock phase

- Flexible baud rates and delays

- Parity Type

- Flexible frame length

### QSPI Flexible frame format

- > Programmable number of data bits: 2 to 32 data bits (plus parity: 3 to 33 bits)

- > 4 to 32 data bits possible for 50 Mbit/s

- > Programmable shift direction: LSB or MSB shift first

- > Programmable clock polarity: Idle low or idle high state for the shift clock

- Programmable clock phase: data shift with leading or trailing edge of the shift clock

- > Flexible baud rate and delays (leading, trailing, idle) generation

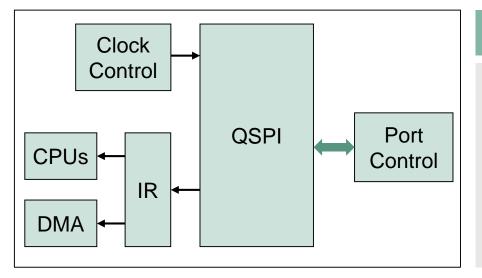

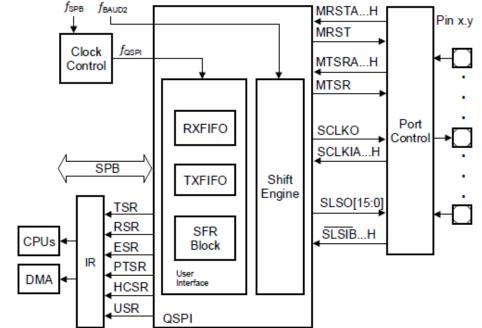

### QSPI System integration

- FIFOs can be handled by DMA controller

- Interrupt generation on

- transmitter FIFO event

- receiver FIFO event

- error condition

- phase transition

- Seven slave select inputs SLSI in Slave Mode

- Sixteen programmable slave select outputs SLSO in Master Mode

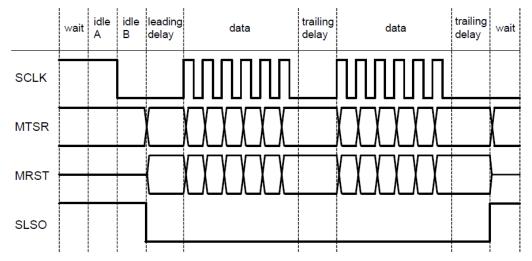

### **Overview**

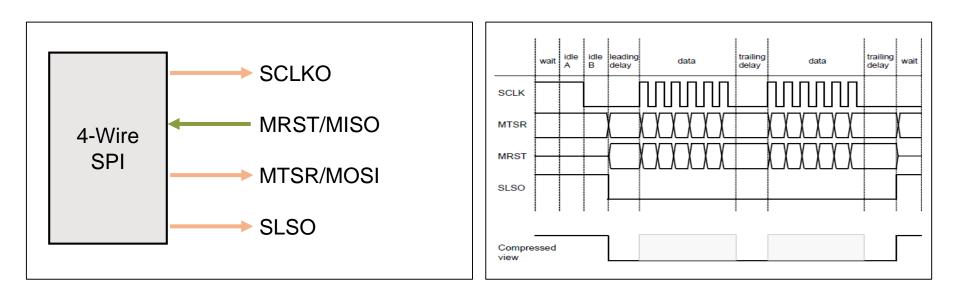

- Typical 4-wire SPI Master communication

- Support for Full-duplex, Half-duplex and Simplex modes

#### **Advantages**

- Full configuration of Idle, Leading and Trailing delays

- Flexible timing control allows to program the duty cycle and the sampling point properties of the serial clock

#### **Overview**

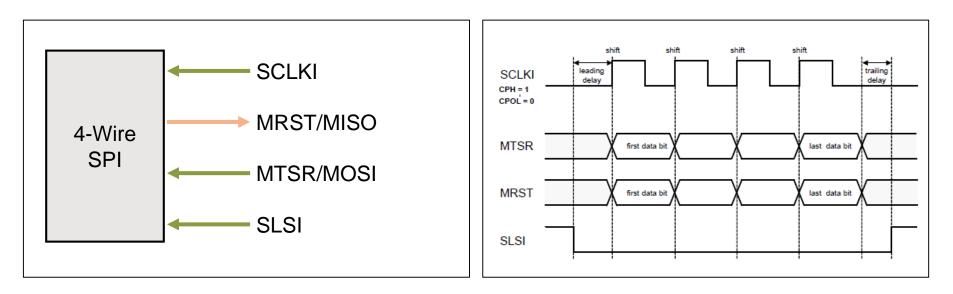

- Typical 4-wire SPI Slave communication

- Support for Full-duplex, Halfduplex and Simplex modes

#### **Advantages**

> Easy configuration with shift clock phase and polarity

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2019-03 Published by Infineon Technologies AG 81726 Munich, Germany

© 2019 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: <u>erratum@infineon.com</u>

Document reference AURIX\_Training\_1\_ Queued\_Synchronous\_Peripheral\_ Interface

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.