# Memory\_Access\_Performance\_1 for KIT\_AURIX\_TC334\_LK Memory access performance

AURIX™ TC3xx Microcontroller Training V1.0.0

# Scope of work

# Data is stored and read back from different RAM locations while the access times are monitored using the CPU performance counters.

A routine is implemented to execute performance measurements using the CPU performance counters. The amount of required CPU clocks is evaluated for ten alternating write and read operations to different memories (DSPR0, LMU).

### Introduction

- The microcontrollers of the AURIX™ TC3xx family have several CPU related volatile memories. Some are dedicated for a certain CPU e.g. the Program Scratch Pad RAM (PSPR), the Data Scratch Pad RAM (DSPR), PCACHE and DCACHE and some are used for general purpose such as the Local Memory Unit (LMU), where the access latency is typically higher

- A higher access latency is also expected if a certain CPU accesses the memory adjacent to another CPU via the SRI bus

- The latency in CPU clock cycles can be easily measured using the CPU performance counters

# Hardware setup

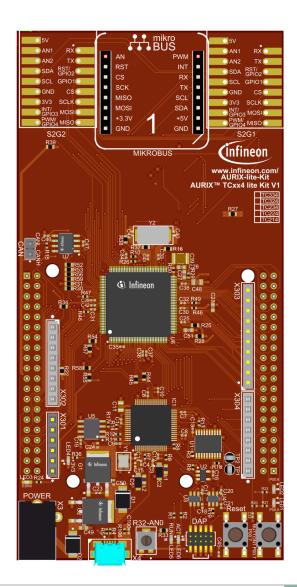

This code example has been developed for the board KIT\_A2G\_TC334\_LITE.

### Defining global data fields within the different volatile memories

- The global macro **BUFFERSIZE** defines the size of **10** elements for the data fields

- Alternate writes and reads are repeated ten times to determine the number of CPU clocks. The global array **g\_DataLMU[BUFFERSIZE]** defines the data field in the LMU. Furthermore, the global array **g\_DataDSPR0[BUFFERSIZE]** define the data fields in the **DSPR0**. The compiler directive **#pragma** is used to force the compiler to put the global variables in the corresponding volatile memory

### **Sequence of memory performance measurements**

A series of measurements is conducted by repeatedly invoking the function *accessData()* with different parameters inside the function *measurePerformance()*. The first argument is the data field where the write/read access goes to/comes from and the second argument is a container to store the results of the performance counter

**Note:** For using the performance counters, the On-Chip Debug System has to be enabled. This is ensured by the debugger itself, therefore the example has to be tested within an active debug session.

### **Executing write and read accesses**

- The function IfxCpu\_resetAndStartCounters() starts the CPU performance counters. A parameter is specifying the counter mode:

- Normal mode: The counters start counting as soon as they are enabled and will keep counting until they are disabled

- Task mode: The counters will only count if the processor detected a debug event with the action to start the performance counters

- A for loop is used to write the index value into the data field and read it back. The first parameter of the function accessData() is specified as volatile. This prevents the compiler from optimizing the assembler code in order to ensure that the index of the for loop is read back from the memory

### **Executing write and read accesses**

- To ensure that the Store Buffer is flushed before starting the read operation, a **DSYNC**TriCore™ instruction is performed using the \_\_dsync() intrinsic function

- > The function *IfxCpu\_stopCounters()* stops and returns the counters' values

Both the functions *IfxCpu\_resetAndStartCounters()* and *IfxCpu\_stopCounters()* are part of the Infineon low level drivers and are implemented in *IfxCpu.h*.

**Note**: In TriCore<sup>™</sup> TC1.6.2P CPUs, store buffering is implemented to decouple memory write operations from CPU instruction execution, thus increasing their performance. All stores from the CPU are placed in the store buffer prior to being written to local memory or transferred via the bus system. Therefore, if there is a requirement that data is written to local memory prior to execution of a subsequent instruction, then a **DSYNC** instruction may be used to flush the store buffers. In this simple example, the **DSYNC** instruction is needed, otherwise the write-read operations can be "optimized" by the store buffer and the memory access timings will have the same value across different types of memories.

### **Disabling the DCACHE**

The CPU uses the DCACHE for data storage into the LMU. This is prevented by switching off the DCACHE usage. The macro *IFX\_CFG\_SSW\_ENABLE\_TRICOREO\_DCACHE* is required to be set to zero.

The macro is configured inside the header file *lfx\_Cfg.h*.

# Run & Test

After code compilation and flashing the device, check the amount of clocks representing the access latency in the debugger perspective:

- Add the expressions

g\_perfCounts[0].instruction.counter,

- g\_perfCounts[0].clock.counter,

g\_perfCounts[1].instruction.counter,

- g\_perfCounts[1].clock.counter to the

- Watch window and check the values

- g\_perfCounts[0]: CPU0 writes and reads to/from DSPR0

- g\_perfCounts[1]: CPU0 writes and reads to/from LMU

| (x)= Variables 🔒 Breakpoints             | Expressions | ×      | # <b>1</b> ■ <b>1</b> E |

|------------------------------------------|-------------|--------|-------------------------|

| Expression                               |             | Туре   | Value                   |

| (x)= g_perfCounts[0].instruction.counter |             | unsign | . 116                   |

| (x)= g_perfCounts[0].clock.counter       |             | unsign | . 220                   |

| (x)= g_perfCounts[1].instruction.counter |             | unsign | . 116                   |

| (x)= g_perfCounts[1].clock.counter       |             | unsign | . 240                   |

| Add new expression                       |             |        |                         |

|                                          |             |        |                         |

# References

- > AURIX™ Development Studio is available online:

- https://www.infineon.com/aurixdevelopmentstudio

- Use the "Import…" function to get access to more code examples.

- More code examples can be found on the GIT repository:

- https://github.com/Infineon/AURIX code examples

- For additional trainings, visit our webpage:

- https://www.infineon.com/aurix-expert-training

- For questions and support, use the AURIX™ Forum:

- https://www.infineonforums.com/forums/13-Aurix-Forum

### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2021-12 Published by Infineon Technologies AG 81726 Munich, Germany

© 2021 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference Memory\_Access\_Performance\_1 \_KIT\_TC334\_LK

### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (<a href="www.infineon.com">www.infineon.com</a>).

### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.