MTU\_MBIST\_1

for KIT\_AURIX\_TC334\_LK

Memory Built-In Test via MTU

AURIX™ TC3xx Microcontroller Training V1.0.0

# Scope of work

### The MBIST is used to assess the state of the memory.

In this training the Memory Test Unit (MTU) is used to initialize and clear the content of an SRAM memory including its ECC code. Additionally, the Non-Destructive Test (NDT) is performed by Memory Built-in-Self-Test (MBIST) to verify the content of the same SRAM memory.

The SRAM of the DMA (DMARAM) is selected to be tested in this example. In order to test the faulty scenario, this training provides the possibility to inject a single bit error in the memory.

The LEDs on the board are used to signal the correct or faulty behavior of the MBIST.

### Introduction

- The Memory Test Unit (MTU) controls and monitors the test, initialization and data integrity checking functions of the various internal memories in the AURIX™ TC3xx family of microcontrollers

- Each SRAM is provided with digital logic surrounding it, known as SRAM Support Hardware (SSH)

- Each SSH block controls one or more internal memories, providing an unified interface for the control of ECC (Error Correction) and BIST (Builtin-Self-Test)

- The SSH provides direct access to the memories, without involving the CPU

- The Memory Built-in-Self-Test (MBIST) is an MTU feature, which enables the verification of the integrity of internal SRAMs

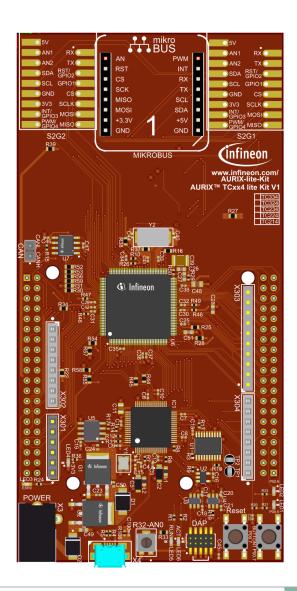

# Hardware setup

This code example has been developed for the board KIT\_A2G\_TC334\_LITE.

## **Implementation**

### **MBIST** test implementation:

Execution of the MBIST test is ensured by the *test\_MTU\_MBIST()* function, containing the following steps:

- 1. MTU module is enabled: <a href="mailto:lfxMtu\_enableModule">lfxMtu\_enableModule</a>()</a>

- 2. A check for UnCorrectable Error (UCE) alarm is performed: **get\_MTU\_MBIST\_Errors()**

- If an error is reported\*, the UCE alarm status is cleared: clear\_MTU\_MBIST\_Errors()

- 3. The SRAM to be tested is initialized using MTU: *IfxMtu\_clearSram()*

- 4. Optionally, an error is injected before test execution (Please refer to <u>next slide</u>)

- 5. The Non-Destructive Test (NDT) is triggered: *IfxMtu\_runNonDestructiveInversionTest()*

- 6. After test completion, the *IfxMtu\_runNonDestructiveInversionTest()* function returns whether the RAM content is correct or an error is detected

- The functions used to enable the MTU, clear the SRAM and run the NDT are provided by the iLLD header *IfxMtu.h*, while the functions used to get and clear the UCE alarm status can be found in *MTU\_MBIST.c*

**Note:** In this training, the DMARAM is tested by calling **test\_MTU\_MBIST(IfxMtu\_MbistSel\_dma)** in the main function. It is possible to test any other SRAM memory **X** by calling **test\_MTU\_MBIST(IfxMtu\_MbistSel\_X)**.

<sup>\*:</sup> After any System Reset: For each and every SSH in the system, the UCE alarm status in the SMU, the ECCD.UCERR (Consequently also SERR) and the FAULTSTS.OPERR[0] are set.

## **Implementation**

### **Correctable Error Injection:**

The error injection option can be enabled by setting the global variable *g\_errorInjection* to *TRUE* in *MBIST\_MTU.c* file.

### Implementation steps:

- Safety Endinit protection is cleared: IfxScuWdt\_clearSafetyEndinit()

- MBIST controller is enabled: IfxMtu\_enableMbistShell()

- Wait for the end of SRAM initialization, in case it is an auto-initialization memory: *IfxMtu\_isAutoInitRunning()*

- 4. One memory address (e.g. 0x1F) is read: IfxMtu\_readSramAddress()

- Only one bit should be modified to inject a correctable error. DMARAM is SECDED (Single Error Correction, Double Error Detection)

- The updated memory is written back to the same address (0x1F): *IfxMtu\_writeSramAddress()*

- 7. MBIST controller is disabled: *IfxMtu\_disableMbistShell()*

- Safety Endinit protection is restored: IfxScuWdt\_setSafetyEndinit()

The functions above are provided by the iLLD headers *IfxMtu.h* and *IfxScuWdt.h*.

# **Implementation**

#### **LED** initialization and control:

> Two LEDs are used in this training to report the execution of the test

LED\_PASS : LED driven by port 00 pin 5

LED\_FAIL : LED driven by port 00 pin 6

Ports configuration in the right mode to control LEDs:

- IfxPort\_setPinMode()

LEDs control (LEDs are low-level active)

Switch On: IfxPort\_setPinLow()

Switch Off: *IfxPort\_setPinHigh()*

The functions above are provided by the iLLD header IfxPort.h

## Run and Test

After code compilation and flashing the device, check the behavior of *LED\_PASS* (1)

and *LED\_FAIL* (2):

| MBIST of          | DMARAM                 | LED PASS | LED<br>FAIL |

|-------------------|------------------------|----------|-------------|

| No Error injected | No Error detected      |          |             |

|                   | Error detected         |          |             |

| Error<br>injected | No Error detected      |          |             |

|                   | Wrong Error detected   |          |             |

|                   | Correct Error detected |          |             |

| LED On LED Off    |                        |          |             |

### References

- > AURIX™ Development Studio is available online:

- https://www.infineon.com/aurixdevelopmentstudio

- Use the "Import…" function to get access to more code examples.

- More code examples can be found on the GIT repository:

- https://github.com/Infineon/AURIX code examples

- For additional trainings, visit our webpage:

- https://www.infineon.com/aurix-expert-training

- For questions and support, use the AURIX™ Forum:

- https://www.infineonforums.com/forums/13-Aurix-Forum

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2022-03 Published by Infineon Technologies AG 81726 Munich, Germany

© 2021 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference MTU\_MBIST\_1\_KIT\_TC334\_LK

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (<a href="www.infineon.com">www.infineon.com</a>).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.