MPU\_Memory\_Protection\_1 for KIT\_AURIX\_TC334\_LK MPU Memory Protection

AURIX™ TC3xx Microcontroller Training V1.0.0

# Scope of Work

# The MPU module is used to protect part of an array from read/write accesses.

The MPU module is configured to enable read/write access to the first half of an array.

To test the function of the read protection, each element of the array is read in a loop.

Two LEDs are used to indicate the progression of the CPU read accesses. When the loop reads the last accessible element, the first LED is turned on. The second LED is only turned on if the CPU reads an element which should be protected.

## Introduction

- Each CPU has a Memory Protection Unit that can restrict what memory ranges are allowed for each master (e.g. DMA, CPU) based on a master ID

- In AURIX™ TC3xx, the MPU supports:

- 18 data ranges that specify which memory ranges a master is allowed to access for data. Read and write permissions can be specified for each range

- 10 code ranges that specify which memory ranges the CPU is allowed to access for instructions

- In AURIX™ TC3xx, the CPU has 6 different protection sets (PRS) that specify which combination of data ranges and code ranges are active

- When the MPU is enabled, an instruction or data access outside of the specified MPU ranges selected by the active protection set immediately causes a CPU trap and optionally an alarm to the Safety Management Unit (SMU)

- The CPU Memory Protection Unit is one of the many AURIX™ safety mechanisms that help to protect against random hardware faults as well as systematic faults

## Introduction

- The SRAMs monitored by the MPU are:

- Program Scratch-Pad SRAM (PSPR) of each CPU

- Data Scratch-Pad SRAM (DSPR) of each CPU

- Local Bus Memory Unit (LMU), when available in the device

- Protection Ranges are defined by a Lower Boundary and an Upper Boundary. An address belongs to the range if:

- Lower Boundary <= Address < Upper Boundary</li>

- > The granularity of the memory protection ranges differ for data and code:

- Data protection ranges have a granularity of 8 bytes

- Code protection ranges have a granularity of 32 bytes

- > The permission to access a memory location is the logical 'OR' of the memory range permissions. Where ranges intersect, the MPU grants the most permissive access

# Introduction

- PRS0 automatically becomes active whenever a CPU interrupt or trap is triggered.

For this reason, it is commonly reserved for OS usage and PRS0 is typically configured to allow access to all valid code and data ranges

- It is possible for software to reconfigure the MPU range registers during runtime, but this takes more time than simply selecting a different active protection set

- A task that is not running in supervisor mode will not be able to change its active protection set, update the protection ranges, or disable the MPU monitoring. This ensures that user level tasks cannot circumvent the protection in any way

**Note:** Masters in AURIX<sup>™</sup> devices have different levels of privileges, where supervisor mode is the highest. This is a safety measure to ensure that no unintended changes are done to "sensitive" registers or memory areas.

**Note:** To ensure deterministic behavior in all implementations of TriCore<sup>™</sup>, a region at least twice the size of the largest memory accesses, minus one byte, should be left as a buffer between each memory protection region.

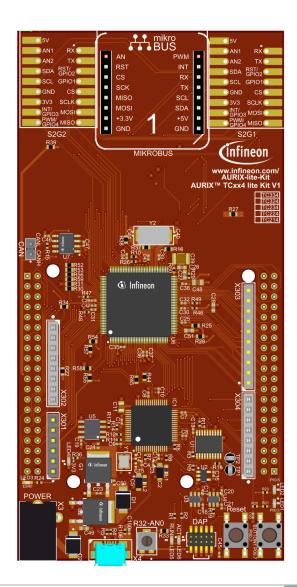

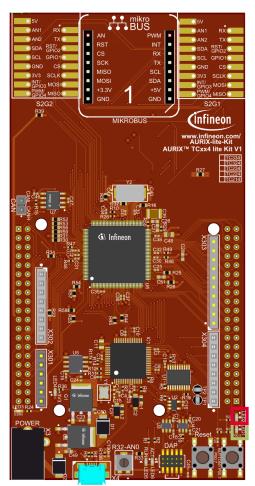

# Hardware setup

This code example has been developed for the board KIT\_A2G\_TC334\_LITE.

# **Implementation**

### **Configuration of the MPU**

To enable memory protection, the following steps have to be followed:

- Define the Data/Code Protection Ranges where access must be granted

- Define the type of access to grant in a defined Protection Set

- Enable read and/or write in case of definition of a Data Protection Range (DPR)

- Enable code execution in case of definition of a Code Protection Range (CPR)

- Select the active Protection Set

- > Enable the memory protection

# infineon

# **Implementation**

### **Definition of Data Protection Ranges**

The definition of a Data Protection Range is done through the function **define\_data\_protection\_range()**, which sets the lower and upper boundaries of the given CPU Data Protection Range number.

The lower and upper boundaries are set by calling the intrinsic function \_\_mtcr(), which moves contents of a data register to the addressed Core Special Function Register (CSFR).

\_\_*mtcr()* performs a Move To Core Register (*MTCR*) TriCore<sup>™</sup> instruction and is followed by an *ISYNC* instruction.

The *ISYNC* instruction ensures that the effects of the Core Special Function Register (CSFR) update are correctly seen by all following instructions. An ISYNC must always be performed after an MTCR instruction.

The Tasking intrinsic function \_\_mtcr() automatically generates an ISYNC instruction after calling MTCR; when using different compilers the ISYNC instruction call is ensured by the \_\_isync() function called between the #if - #endif directives.

# infineon

# **Implementation**

### **Definition of Code Protection Ranges**

The definition of a Code Protection Range is done through the function **define\_code\_protection\_range()**, which sets the lower and upper boundaries of the given CPU Code Protection Range number.

The lower and upper boundaries are set by calling the intrinsic function \_\_mtcr().

### Configuration of Read Access for a Data Protection Range

The read access to a Data Protection Range (DPR) is provided with the function **enable\_data\_read()**, which enables the read access to the given DPR on the addressed Protection Set.

To enable the read access, first the CPU Data Protection Read Enable register (CPU\_DPRE) is read with the intrinsic function \_\_mfcr(), the bit corresponding to the given DPR is set, and finally the modified value is stored back to the register with the intrinsic function \_\_mtcr() (essentially, a load-modify-store operation, which ensures that previously made changes are not overwritten).

\_\_*mfcr()* moves contents of the addressed Core Special Function Register (CSFR) into a data register by calling the TriCore<sup>™</sup> instruction Move From Core Register (MFCR).

# infineon

# **Implementation**

### **Configuration of Write Access for a Data Protection Range**

The write access to a Data Protection Range is provided with the function **enable\_data\_write()**, which enables the write access to the given DPR on the addressed Protection Set.

To enable the write access, first the CPU Data Protection Write Enable register (CPU\_WPRE) is read with the intrinsic function \_\_*mfcr()*, the bit corresponding to the given DPR is set, and finally the modified value is stored back to the register with the intrinsic function \_\_*mtcr()*.

### Configuration of Code Execution Access for a Code Protection Range

The code execution access to a Code Protection Range (CPR) is provided with the function **enable\_code\_execution()**, which enables the code execution access of the given CPR on the addressed Protection Set.

To enable code execution access, first the CPU Code Protection Execute Enable register (CPU\_CPXE) is read with the intrinsic function \_\_*mfcr()*, the bit corresponding to the given CPR is set, and finally the modified value is stored back to the register with the intrinsic function \_\_*mtcr()*.

# **Implementation**

#### Selection of the Active Protection Set

The active protection set is selected with the function **set\_active\_protection\_set()**, which sets the PRS bitfield of the Program Status Word (PSW) register accordingly to the given parameter.

The **set\_active\_protection\_set()** function needs to be declared as **inline** because the PSW is one of the registers automatically saved to the Context Save Area (CSA) when a function is called.

If this function was not declared as inline, the Upper Context (16 registers including the PSW) would be automatically saved to the CSA and re-loaded when the function returns, thus losing the change to the PSW.

By default, the active Protection set is the Protection Set 0.

### **Activation of Memory Protection**

The memory protection is enabled with the function **enable\_memory\_protection()**, which turns on the memory protection by setting the PROTEN bitfield of the System Configuration (SYSCON) register.

# **Implementation**

### **Configuration and Control of the LEDs**

The LEDs are turned on and off by controlling the port pins to which they are connected using methods from the iLLD headers *IfxPort.h*.

In the function *init\_LEDs()* the LED port pins are configured to output push-pull mode using the function *IfxPort\_setPinModeOutput()*, then they are immediately turned off with the function *IfxPort\_setPinHigh()*.

During program execution, the LEDs are turned on in case the first and second half of the array are accessible. The port pins are controlled with the function **switch\_LED\_ON()** which calls the iLLD function **IfxPort\_setPinLow()** for the addressed LED port pin.

# Run and Test

After code compilation and flashing the device, perform the following steps:

- Run the example and check that

- LED1 is on (meaning that the first half of the array was accessible in the memory)

- LED2 is off (meaning that the second half of the array was NOT accessible in the memory)

# References

- > AURIX™ Development Studio is available online:

- https://www.infineon.com/aurixdevelopmentstudio

- Use the "Import…" function to get access to more code examples.

- More code examples can be found on the GIT repository:

- https://github.com/Infineon/AURIX code examples

- For additional trainings, visit our webpage:

- https://www.infineon.com/aurix-expert-training

- For questions and support, use the AURIX™ Forum:

- https://www.infineonforums.com/forums/13-Aurix-Forum

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2021-12 Published by Infineon Technologies AG 81726 Munich, Germany

© 2021 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference MPU\_Memory\_Protection\_1\_ KIT\_TC334\_LK

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (<a href="www.infineon.com">www.infineon.com</a>).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.