# GPT12\_Timer\_Concatenation\_1 Timer concatenation of GPT12

AURIX™ TC2xx Microcontroller Training V1.0.0

## Scope of work

A 32-bit timer is formed by the concatenation of two timers of the GPT12 module. On timer overflow an interrupt is generated, which toggles an LED.

A 32-bit timer is formed by the concatenation of two 16-bit timers of the GPT12 module. When the 32-bit timer overflows, an interrupt is generated toggling an LED.

## Introduction

- The General Purpose Timer Unit GPT12 is divided into two GPT blocks (GPT1 and GPT2).

- The GPT12 unit incorporates five 16-bit timers which may operate independently in several different modes.

- Block GPT2 contains two timers/counter: the core timer T6 and one auxiliary timer T5.

- Both timers of block GPT2 can run in Timer Mode, Gated Timer Mode or Counter Mode.

- An additional Capture/Reload register (CAPREL) supports also capture and reload operation.

- The timer T5 in Counter Mode and the timer T6 in Timer Mode are used together in this example.

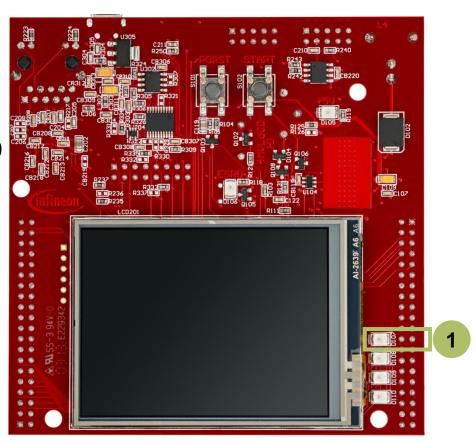

# Hardware setup

This code example has been developed for the board KIT\_AURIX\_TC297\_TFT\_BC-Step.

#### **Configuration of the GPT12 module**

The function *init\_GPT12\_module()* is used to configure the two timers T5 and T6 of GPT2 for concatenated 32-bit operation. It contains the following steps:

- The GPT12 module is enabled by calling the function IfxGpt12\_enableModule().

- GPT2 prescaler is set to IfxGpt12\_Gpt2BlockPrescaler\_2 to get the highest possible frequency by calling IfxGpt12\_setGpt2BlockPrescaler().

- The functions *IfxGpt12\_T6\_setMode()* and *IfxGpt12\_T5\_setMode()* are used to configure the modes of both timers. The core timer T6 is set to *IfxGpt12\_Mode\_timer* and the auxiliary timer T5 is set to *IfxGpt12\_Mode\_counter*.

- Both the rising and falling edge of the Output Toggle Latch of timer T6 are selected as active transition with the function IfxGpt12\_T5\_setCounterInputMode().

- The function *IfxGpt12\_T5\_setRemoteControl()* configures the timer T5 to be activated by the run bit of core timer T6. *IfxGpt12\_T6\_run()* function starts timer T6 and implicitly timer T5, because the overflow of T6 is used as clock for T5.

The functions above are provided by the iLLD header *IfxGpt12.h.*

#### Configuring the interrupt service routing for block GPT2

- The function IfxGpt12\_T5\_getSrc() returns the pointer to the service request control (SRC) register of timer T5.

- The function *IfxGpt12\_T6\_getSrc()* returns the pointer to the SRC register of timer T6.

- The above mentioned pointers to the SRC registers are used to initialize and enable the ISRs by setting the service provider and the priority number. This is done via the functions *IfxSrc\_init()* and *IfxSrc\_enable()* provided by the iLLD header *IfxSrc.h*.

- The method implementing the ISR needs to be assigned a priority and a CPU core responsible for its execution. This is done with the macro IFX\_INTERRUPT(isr, vectabNum, priority).

### The Interrupt Service Routines (ISRs)

- The incrementation of the counter values is different for both timers:

- The counter of timer T6 (Timer Mode) is incremented with the frequency of timer T6.

- The counter of timer T5 (Counter Mode) is incremented by each overflow of timer T6.

- The overflow of each timer triggers an interrupt.

- Each timer has associated its own Interrupt Service Routine.

- > The ISR of timer T6 is triggered after the overflow of the 16-bit timer value of timer T6.

- Due to the timer concatenation, the ISR of timer T5 is triggered with the overflow of the 32-bit timer value. This ISR toggles an LED.

- The 32-bit timer value is calculated in the ISR of T6 and is represented by timerValueHIGH (T5) and timerValueLOW (T6).

### Run and Test

After code compilation and flashing the device, perform the following steps:

- Check if LED D107 (1) is toggling its state every 86 seconds:

- Maximum value of 32-bit timer is 4294967295

- Frequency of GPT12 module is 100 MHz

- Prescaler of GPT2 block is set to 2

- Timer T6 frequency is 100 MHz / 2

= 50 MHz, which means the value of the 32-bit timer will be incremented each 20 ns (1 / 50 MHz)

- Overflow of 32-bit timer after ≈ 86 s

(4294967295 \* 20 ns)

- Check in the debugger if parameterg\_timerValue32Bit is incrementing

## References

- https://www.infineon.com/aurixdevelopmentstudio

- Use the "Import…" function to get access to more code examples.

- More code examples can be found on the GIT repository:

- https://github.com/Infineon/AURIX code examples

- For additional trainings, visit our webpage:

- https://www.infineon.com/aurix-expert-training

- For questions and support, use the AURIX™ Forum:

- https://www.infineonforums.com/forums/13-Aurix-Forum

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2019-10 Published by Infineon Technologies AG 81726 Munich, Germany

© 2019 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference

GPT12 Timer Concatenation 1

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (<a href="www.infineon.com">www.infineon.com</a>).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.