Automotive grade

Gate driver AUIR3241S

# LOW QUIESCENT CURRENT BACK TO BACK MOSFET DRIVER

#### **Features**

- Very low quiescent current on and off state

- Back to back configuration

- · Boost converter with integrated diode

- Standard level gate voltage

- Input active high and 3.3V compatible

- Under voltage lockout with diagnostic

- Wide operating voltage 3-36V

- Ground loss protection

- · Lead-Free, Halogen Free, RoHS compliant

### **Applications**

- Power switch for Stop and Start board net stabilizer

- · Battery switch

# Product Summary

Operating voltage 3-36V Vgate 11.5V min.

I Vcc average On 45μA max. at 25°C I Vcc average Off 35μA max. at 25°C

#### **Package**

SO8

## **Description**

The AUIR3241S is a high side Mosfet driver for back to back topology targeting back to back switch. It features a very low quiescent current both on and off state. The AUIR3241S is a combination of a boost DC/DC converter using an external inductor and a gate driver. It drives standard level Mosfet even at low battery voltage. The input controls the gate voltage. The AUIR3241S integrates an under voltage lock out protection to prevent to drive the Mosfet in linear mode.

**Ordering Information**

| Base Part Number  |              | Standard Pack |          | 0 14 5 44 1          |

|-------------------|--------------|---------------|----------|----------------------|

| base i ait Number | Package Type | Form          | Quantity | Complete Part Number |

| AUIR3241S         | SOIC8        | Tape and reel | 2500     | AUIR3241STR          |

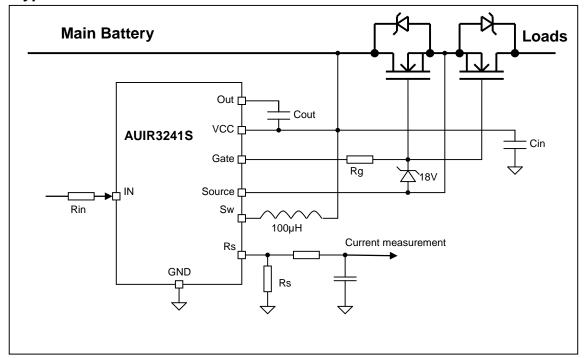

# Typical Connection - Back to Back

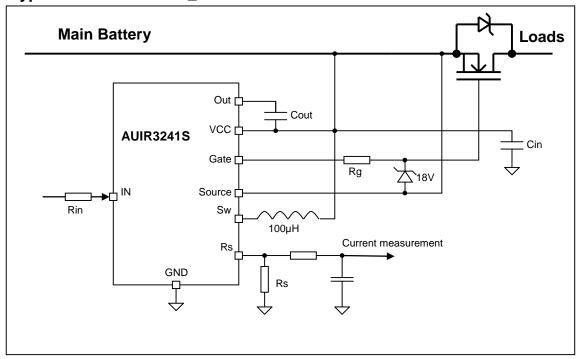

# Typical Connection - Q\_diode

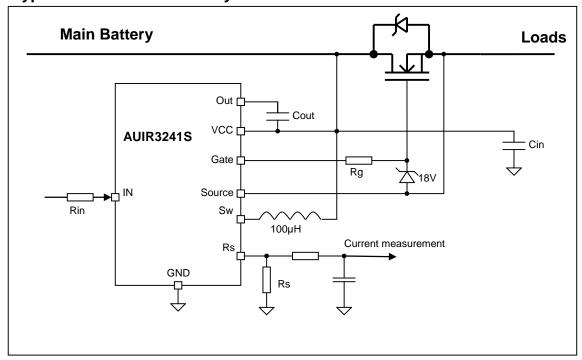

# **Typical Connection – Battery switch**

Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur.

| Symbol        | Parameter                                         | Min.    | Max.     | Units |

|---------------|---------------------------------------------------|---------|----------|-------|

| Vcc-gnd       | Maximum Vcc voltage                               | -0.3    | 65       |       |

| Vsw-gnd       | Maximum Sw voltage                                | Vrs-0.3 | Vout+Vf  |       |

| Vsw-Vrs       | Maximum Sw voltage                                | -0.3    | 65       |       |

| Vout-Vcc      | Maximum Vout-Vcc voltage                          | -0.3    | 65       |       |

| Vout-gnd      | Maximum Vout voltage                              | -0.3    | 65       | V     |

| Vout-Vgate    | Maximum Vout-Vgate voltage                        | -0.3    | 65       | V     |

| Vgate-Vsource | Maximum Vgate-Vsource voltage                     | -0.3    | 75       |       |

| Vout-Vsource  | Maximum Vout-Vsource voltage                      | -0.3    | 75       |       |

| Vrs-gnd       | Maximum Rs pin voltage                            | -0.3    | 6        |       |

| Vin-gnd       | Maximum IN pin voltage                            | -0.3    | Vout+0.3 |       |

| Isw           | Maximum continuous current in Sw pin              | _       | 200      | mA    |

| ID            | Maximum continuous current in the rectifier diode | _       | 200      | IIIA  |

| Rg            | Minimum gate resistor                             | 100     | _        | Ohm   |

|               | Maximum operating junction temperature            | -40     | 150      | °C    |

| Tj max.       | Maximum storage temperature                       | -55     | 150      |       |

### **Thermal Characteristics**

| Symbol | Parameter                              | Тур. | Max. | Units |

|--------|----------------------------------------|------|------|-------|

| Rth    | Thermal resistance junction to ambient | 100  |      | °C/W  |

**Recommended Operating Conditions**

| Symbol | Parameter                | Min. | Max. | Units |

|--------|--------------------------|------|------|-------|

| VIH    | High level input voltage | 2.5  | 5.5  | W     |

| VIL    | Low level input voltage  | 0    | 0.8  | V     |

#### **Static Electrical Characteristics**

Tj=-40..125°C, Vcc=6..16V (unless otherwise specified), typical value are given for Vcc=14V and Tj=25°C.

| Symbol            | Parameter                                            | Min. | Тур. | Max. | Units | Test Conditions     |

|-------------------|------------------------------------------------------|------|------|------|-------|---------------------|

|                   | Supply voltage range for extended operation (some    |      |      |      |       |                     |

| Vcc op (ext).     | parameters may be downgraded beyond nominal          | 3    | _    | 36   | V     | See page 11         |

|                   | operation)                                           |      |      |      |       |                     |

| Vcc op (nom). (1) | Supply voltage range for nominal operation           | 6    | _    | 16   |       |                     |

| Iq Vcc Off (2)    | Supply current when Off, Tj=25°C                     |      | 2    | 6    |       | Vin=0V,K1/K2 off,   |

|                   | Supply current when Off, Tj=125°C                    | _    | 3    | 8    |       | K3 on, Vout-Vcc=14V |

| Iq Vcc On (2)     | Supply current when On, Tj=25°C                      |      | 3    | 6    | μA    | Vin=5V,K1/K3 off,   |

|                   | Supply current when On, Tj=125°C                     | _    | 4    | 8    | μΑ    | K2 on, Vout-Vcc=14V |

| Iq Out Off (2)    | Quiescent current on Out pin, Tj=25°C                | _    | 10   | 15   |       | Vin=0V,K1/K2 off,   |

|                   | Quiescent current on Out pin, Tj=125°C               | _    | 13   | 25   |       | K3 on, Vout-Vcc=14V |

| Iq Out On (2)     | Quiescent current on Out pin, Tj=25°C                | _    | 12   | 20   |       | Vin=5V,K1/K3 off,   |

|                   | Quiescent current on Out pin, Tj=125°C               | _    | 15   | 30   |       | K2 on, Vout-Vcc=14V |

| Vbr Out           | Breakdown voltage between Out and Source             | 75   | 90   | _    |       | I=10mA              |

| Vbr Gate          | Breakdown voltage between Gate and Source            |      | 90   | _    | V     | I=10mA              |

| OV                | Over-voltage protection between Vout and Gnd         | 50   | 55   | 62   |       |                     |

| lin               | Input current                                        | _    | 3    | 6    | μA    | Vin=5V              |

| Vin_th            | Input voltage threshold                              | 0.8  | 1.5  | 2.5  |       |                     |

| Vout_th           | Output voltage threshold                             | 11.5 | 12.5 | 14   |       |                     |

| UV_LO             | Undervoltage lockout between Vout and Vcc            | 6.5  | 8    | 10   | V     | See figure 7        |

| Vout_th-UV_LO     | Output voltage minus Undervoltage lockout threshold  | 3    | 4.5  | _    |       |                     |

| Vrs th            | Rs threshold                                         | 0.8  | 1    | 1.3  |       |                     |

| I latch UV_LO     | Under voltage lockout Latch current between Vout and | 10   | 25   | 40   | A     | See page 11         |

|                   | Vcc                                                  |      |      |      | mA    |                     |

| Vf                | Forward voltage of rectifier diode                   | _    | 0.9  | 1.1  | V     | I=100mA, Tj=25°C    |

| Rdson K1          | Rdson of K1, Tj=-40°C                                | _    | 8    | 13   |       | I=100mA,            |

|                   | Rdson of K1, Tj=25°C                                 | _    | 11   | 15   |       | Vout-Vcc=12.5V      |

|                   | Rdson of K1, Tj=125°C                                | _    | 15   | 20   | Ω     |                     |

| Rdson K2          | Rdson of K2, Tj=25°C                                 | _    | 25   |      |       | I=100mA             |

| Rdson K3          | Rdson of K3, Tj=25°C                                 | _    | 25   | _    |       |                     |

<sup>(1)</sup> If the part is supply outside of this range (ex: during ramp up of Vcc), other values in this table might not be guaranteed (2) Supply current might be higher than specified during the start-up of the part (especially during the charge of Cout)

**Timing Converter Characteristics**Tj=-40..125°C, Vcc=6..16V (unless otherwise specified), typical value are given for Vcc=14V and Tj=25°C.

| Symbol    | Parameter                | Min. | Тур. | Max. | Units | Test Conditions |

|-----------|--------------------------|------|------|------|-------|-----------------|

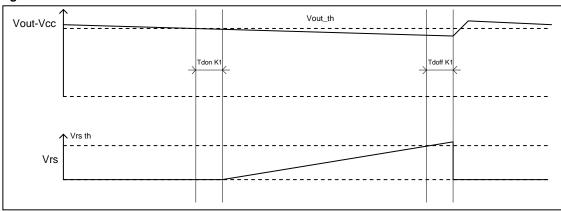

| Toff      | Off time                 | 2    | 3    | 4    |       | See figure 4    |

| Tdon K1   | Turn-on delay of K1      | _    | 5    | _    |       | See figure 5    |

| Tdoff K1  | Turn-off delay of K1     | _    | 0.2  | _    | μs    | See ligure 5    |

| POR_Delay | Power On Reset delay     | 200  | 500  | 1200 |       | See figure 10   |

| POR_Th    | Power On Reset threshold | 6    | 6.5  | 7.5  | V     |                 |

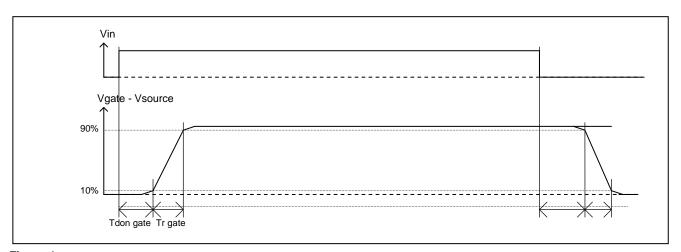

# **Switching Characteristics**

Tj=-40..125°C, Vcc=6..16V (unless otherwise specified), typical value are given for Vcc=14V and Tj=25°C.

| Symbol     | Parameter                                | Min. | Тур. | Max. | Units | Test Conditions   |

|------------|------------------------------------------|------|------|------|-------|-------------------|

| Tdon gate  | Turn-on delay                            | 0.5  | 1.5  | 3    |       |                   |

| Tr gate    | Rise time on gate 10% to 90% of Vout-Vcc | _    | 6    | 15   | μs    | Cgate=100nF       |

| Igate+     | Gate high short circuit pulsed current   | 100  | 350  | _    | mA    | Vgate-Vsource=0V  |

| Tdoff gate | Turn-off delay                           | 0.5  | 2    | 5    | 0     |                   |

| Tf gate    | Fall time on gate 90% to 10% of Vout-Vcc | _    | 6    | 15   | μs    | Cgate=100nF       |

| Igate-     | Gate low short circuit pulsed current    | 100  | 350  | _    | mA    | Vgate-Vsource=14V |

| Treset     | Time to reset the under voltage latches  | _    | 1    | 100  | μs    | See page 11       |

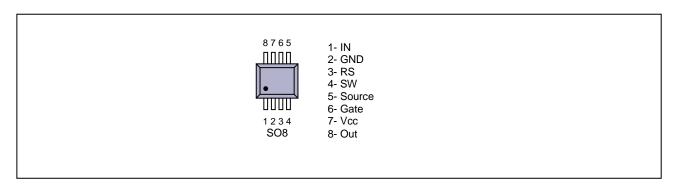

# **Lead Definitions**

| Pin number | Symbol | Description                                 |  |

|------------|--------|---------------------------------------------|--|

| 1          | IN     | Input pin                                   |  |

| 2          | GND    | Ground pin                                  |  |

| 3          | RS     | Current sense input pin                     |  |

| 4          | SW     | Output of K1                                |  |

| 5          | Source | Connection of the source pin of the Mosfets |  |

| 6          | Gate   | Output of the gate driver                   |  |

| 7          | Vcc    | ower supply                                 |  |

| 8          | Out    | Output of the boost converter               |  |

# **Lead Assignments**

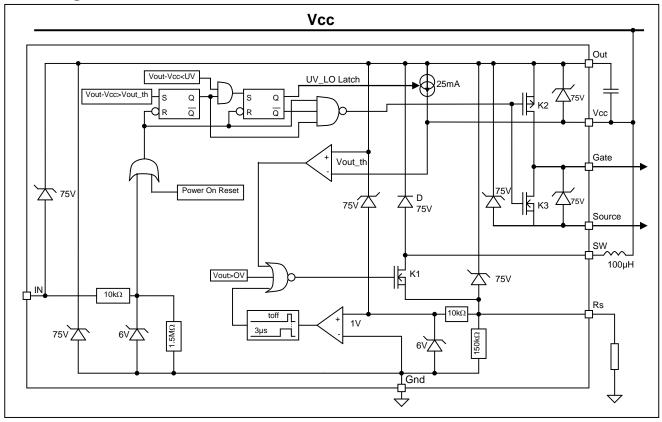

# **Block diagram**

# **Input Circuitry**

The input control circuitry drives the output gate driver stage. The input is active high. With a low level input voltage, the gate is shorted to the source. With a high level input, the output gate driver turn on when Vout reaches Vout\_th.

Figure 1

#### **Description**

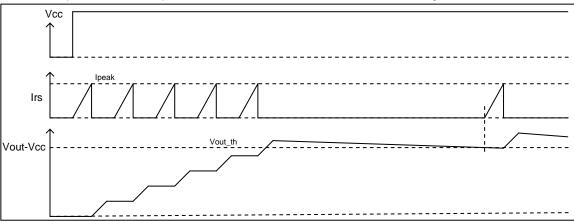

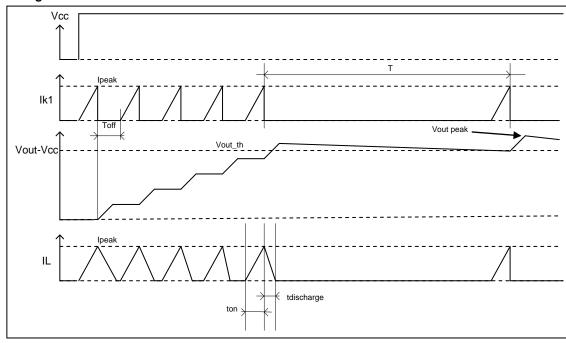

The topology of the AUIR3241S is a boost DC/DC converter working in current mode. The DC/DC is working once the AUIR3241S is powered regardless the input level.

K1 is switched on when the gate voltage is lower than Vout threshold. When Rs pin reaches Vrs th, K1 is turned off and the inductor charges the Out capacitor through D. The system cannot restart during Toff after Vrs th has been reached. The DC/DC restart only when the Out and the Vcc voltage difference is lower than Vout\_th in order to achieve low quiescent current on the power supply.

To turn off the power Mosfet, the input must be low. Then K2 is turned off and K3 shorts the gate to the source.

Figure 2

#### **Parameters definition**

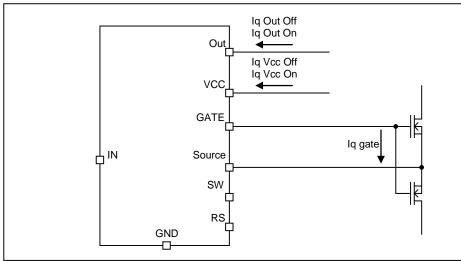

#### **Current definition**

Figure 3

#### **Timing definition**

Figure 4

Figure 5

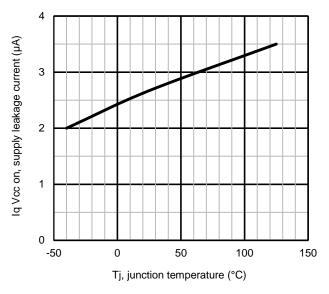

### Low quiescent current operation when On.

The AUIR3241S is able to operate with a very low quiescent current on the Vcc pin. Nevertheless the supply current depends also on the leakage of the power mosfet named "Iq gate" on the diagram below.

The leakage current is given when K1 is off. When K1 is on, the current flowing in Vcc is the current charging the inductor. Therefore the

The leakage current is given when K1 is off. When K1 is on, the current flowing in Vcc is the current charging the inductor. Therefore the average current on the Vcc is the combination of the current when K1 is ON and OFF. The average current on the Vcc pin can be calculated using:

$$I \ Vcc \ average \ on = (Iq \ gate + Iq \ Out \ On) * \frac{Vout - Vcc + Vf}{Vcc} + Iq \ Vcc \ on + Iq \ Out \ on$$

$$I \ Vcc \ average \ off = (Iq \ gate + Iq \ Out \ Off) * \frac{Vout - Vcc + Vf}{Vcc} + Iq \ Vcc \ off + Iq \ Out \ off$$

With Vout: the average voltage on the output. Vout average = (Vout peak + Vout th)/2

Vout peak can be calculated by:

$$Vout \, peak = \sqrt{\frac{L}{Cout} \cdot Ipeak^2 + Vout \, th^2}$$

During On operation, the DC/DC works in pulse mode, meaning each time the Vout-Vcc voltage comes below 12.5V, the AUIR3241S switches on K1 to recharge the gate voltage. When the lout leakage is low enough to maintain the DC/DC in discontinuous mode, the frequency is calculate by:

$$T = \frac{Ipeak^2 * L}{2*(Iq gate+Iq Vout on)*(Vout-Vcc+Vf)}$$

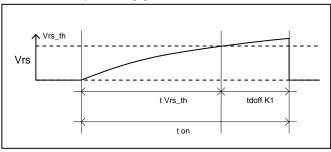

#### **Peak current control**

The current in the inductor is limited by the 1V comparator which monitors the voltage across Rs. Due to the delay in the loop (tdoff K1), the inductor current will exceed the threshold set by:  $\frac{Vrsth}{Rs}$

At low voltage, the current waveform in the inductor is not anymore linear, but exponential because the sum of the resistor of K1, the inductor and RS are not any more negligible.

Figure 6

The peak current and ton can be calculated as follow:

$$t \, Vrsth = -\frac{L}{Rdon \, k1 + Rs + Rl} * ln(1 - \frac{Rs + Rdson \, k1 + Rl}{Vrs\_th * Rs * Vcc})$$

Where RI is the resistor of the inductor

With:  $t on = t Vrs_th + tdoff K1$

The peak current can be solved by:

$$Ipeak = \frac{Vcc}{Rdson k1 + Rs + Rl} * (1 - e^{-ton*} \frac{Rdson k1 + Rs + Rl}{L})$$

The peak current must not exceed the Maximum Rating of Isw.

#### **Output capacitor choice**

The output capacitor must be chosen based on 2 criteria:

- During the turn on of K2, the voltage drop on Cout must not trigger the Under Voltage Lockout due to the gate charge of the Power Mosfet.

$$Cout > \frac{Q \text{ gate total Power Mosfet}}{(Vout_{th}-UV_{LO}) \text{ Min.}}$$

- When K1 turn off and the inductor is charging Cout, the peak current on the output capacitor must be limited in order to avoid having current flowing in the Gate zener diode:

Cout >

$$\frac{L * Ipeak^2 max}{Vz min gate^2 - Vout th max^2}$$

Vz min gate is the minimum Zener voltage of the external gate Zener diode.

#### Minimum operating voltage

While the AUIR3241S operating voltage is specified between 3V and 36V. The 3V minimum operating voltage is when the Vcc is going down. The minimum voltage is also limited by the fact that the Rs voltage must reach the Vrsth taking account all resistors which limit the inductor current.

$$Vcc min = \frac{Rdson k1 + Rs + Rl}{Rs} * Vrsth$$

#### **Over-Voltage protection**

The AUIR3241S integrates an over-voltage protection in order to protect K1. When Vcc exceed the Over-voltage threshold, the DC/DC is stopped.

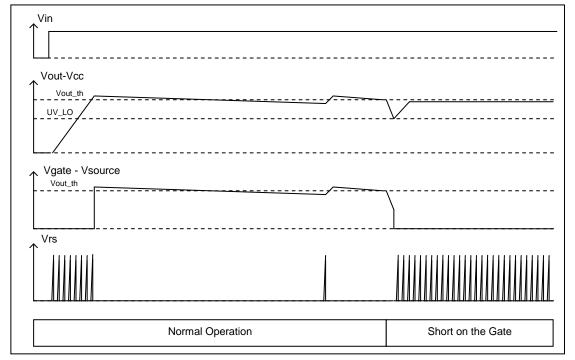

#### **Under voltage lockout - Diagnostic**

In order to avoid to drive the Power Mosfet in linear mode, the AUIR3241S features an under voltage lockout. During the turn on, the gate will not be powered until Vout-Vcc reaches Vout th, meaning K2 is off and K3 is on. Then the AUIR3241S powers the gate of the mosfet. If Vout-Vcc goes below UV\_LO, the gate is shorted to the source and the part is latched. A cycle in the input is required to reset the latch. The input must be kept low longer than Treset.

Figure 7

When the part is latched a current source (I latch UV\_LO) is connected between Out and Vcc to increase the current consumption. By monitoring the current consumption the system can have a diagnostic of the output status. The diagnostic can be analog or digital.

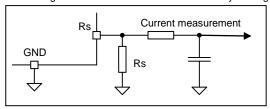

#### **Analog Diagnostic: Output current measurement**

The average current into Rs can be measured by adding a low pass filter before the ADC of the micro controller.

#### Figure 8

Then the average output current can be evaluated using:

I out av = I Rs av \* Vcc / (Vout - Vcc)

Knowing the output current can be useful to do a diagnostic on the power Mosfet. If the gate is shorted, the output current will be significantly higher than in normal operation.

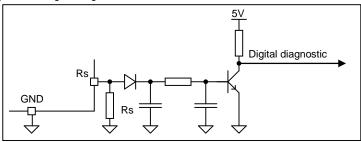

#### Digital diagnostic

By adding a diode during high current consumption mode, the output voltage can be close to 1V. Using a bipolar with a pull-up resistor will provide a digital diagnostic.

Figure 9

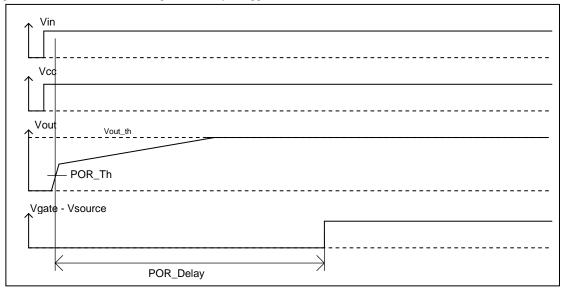

#### **Power On Reset**

During the power on, the AUIR3241S features a Power On Reset to guarantee a stable state of the 2 latches of the Under voltage lockout and guarantee a stable internal biasing. POR\_Delay is triggered when Vout-Gnd exceeds POR\_Th.

Figure 10

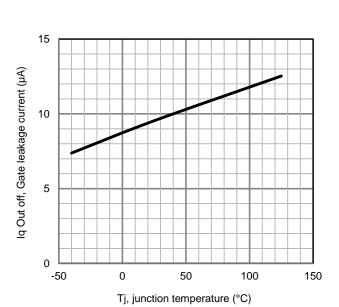

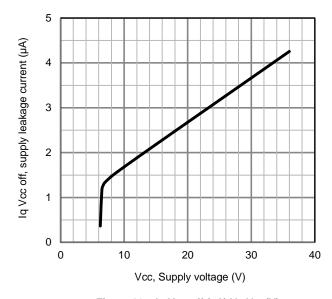

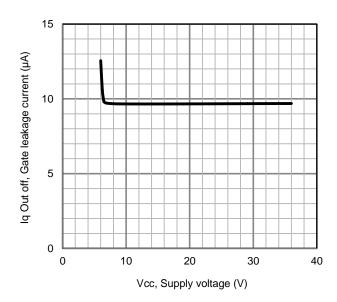

#### Figures are given for typical value, Vcc=14V and Tj=25°C otherwise specified

Figure 11 - Iq Vcc on (µA) Vs Tj (°C)

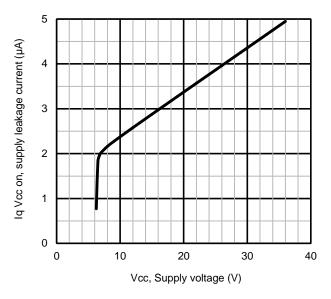

Figure 12 – Iq Vcc on (μA) Vs Vcc(V)

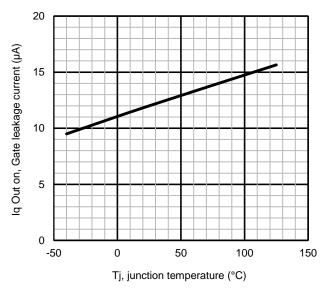

Figure 13 – Iq Out on (µA) Vs Tj (°C)

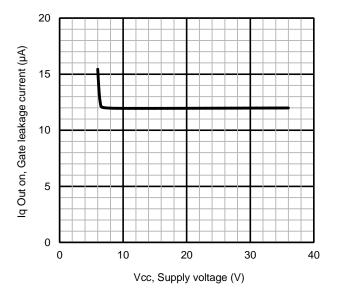

Figure 14 – Iq Out on (µA) Vs Vcc(V)

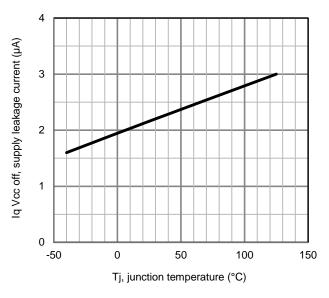

Figure 15 – Iq Vcc off (µA) Vs Tj (°C)

Figure 17 – Iq Out off (µA) Vs Tj (°C)

Figure 16 - Iq Vcc off (µA) Vs Vcc(V)

Figure 18 – Iq Out off (μA) Vs Vcc(V)

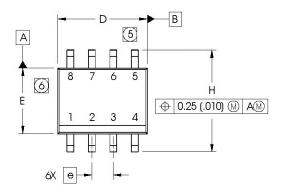

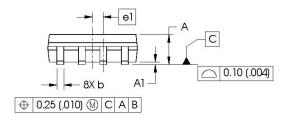

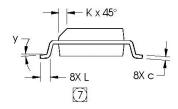

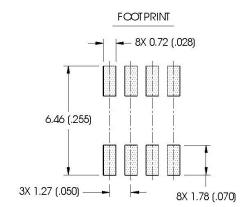

#### Case Outline - SO8

Dimensions are shown in millimeters (inches)

| ДΙΜ    | INC     | HES   | MILLIN     | <b>M</b> ETERS |  |

|--------|---------|-------|------------|----------------|--|

| וועווע | MIN     | MAX   | MIN        | MAX            |  |

| Α      | .0532   | .0688 | 1.35       | 1.75           |  |

| A1     | .0040   | .0098 | 0.10       | 0.25           |  |

| b      | .013    | .020  | 0.33       | 0.51           |  |

| С      | .0075   | .0098 | 0.19       | 0.25           |  |

| D      | .189    | .1968 | 4.80       | 5.00           |  |

| Ε      | .1497   | .1574 | 3.80       | 4.00           |  |

| е      | .050 B. | ASIC  | 1.27 BASIC |                |  |

| е1     | .025 B  | ASIC  | 0.635      | BASIC          |  |

| Н      | .2284   | .2440 | 5.80       | 6.20           |  |

| K      | .0099   | .0196 | 0.25       | 0.50           |  |

| L      | .016    | .050  | 0.40       | 1.27           |  |

| У      | 0°      | 8°    | 0°         | 8°             |  |

#### NOTES:

- 1. DIMENSIONING & TOLERANGING PER ASME Y14.5M-1994.

- 2. CONTROLLING DIMENSION: MILLIMETER

- 3. DIMENSIONS ARE SHOWN IN MILLIMETERS (INCHES).

- 4. OUTLINE CONFORMS TO JEDEC OUTLINE MS-012AA.

- (5) DIMENSION DOES NOT INCLUDE MOLD PROTRUSIONS. MOLD PROTRUSIONS NOT TO EXCEED 0.15 (.006).

- (6) DIMENSION DOES NOT INCLUDE MOLD PROTRUSIONS. MOLD PROTRUSIONS NOT TO EXCEED 0.25 (.010).

- DIMENSION IS THE LENGTH OF LEAD FOR SOLDERING TO A SUBSTRATE.

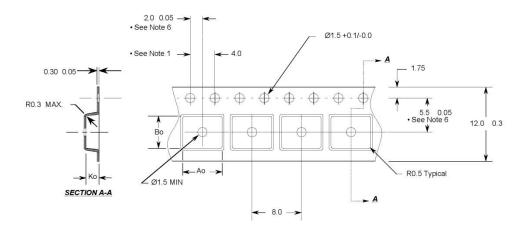

#### Tape & Reel SO8

- Notes:

1. 10 sprocket hole pitch cumulative tolerance 0.2

2. Camber not to exceed 1mm in 100mm

3. Material: Black Conductive Advantek Polystyrene

4. Ao and Bo measured on a plane 0.3mm above the bettem of the procket

Ao = 6.4 mm Bo = 5.2 mm Ko = 2.1 mm - All Dimensions in Millimeters -

4. Ao and to measured on a plane U.3mm above the bottom of the pocket

5. Ko measured from a plane on the inside bottom of the pocket to the top surface of the carrier.

6. Pocket position relative to sprocket hole measured as true position of pocket, not pocket hole.

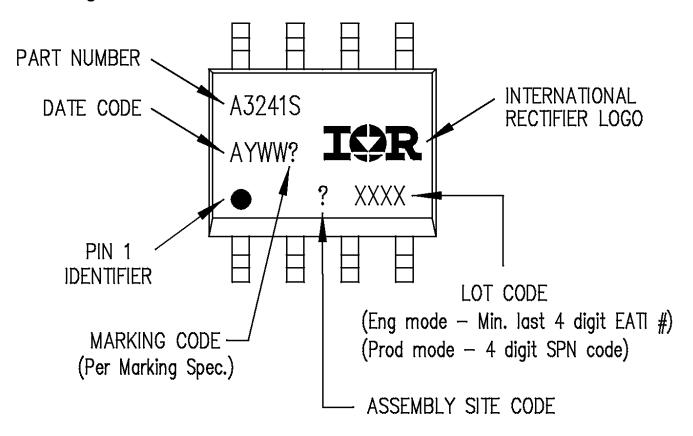

# **Part Marking Information**

# TOP MARKING (LASER)

### **Qualification Information**

| Qualification Level        |                  | Comments: This family of qualification. IR's Industria | Automotive or AEC-Q100) of ICs has passed an Automotive al and Consumer qualification level the higher Automotive level. |  |  |

|----------------------------|------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| Moisture Sensitivity Level |                  | SOIC-8L                                                | MSL2, 260°C<br>(per IPC/JEDEC J-STD-020)                                                                                 |  |  |

| ESD                        | Human Body Model |                                                        | IC Passed 1500V<br>AEC-Q100-002)                                                                                         |  |  |

| Charged Device Model       |                  |                                                        | Class C6 (+/-1000V)<br>(per AEC-Q100-011)                                                                                |  |  |

| IC Latch-Up Test           |                  |                                                        | ss II Level A<br>AEC-Q100-004)                                                                                           |  |  |

| RoHS Compliant             |                  | ,,                                                     | Yes                                                                                                                      |  |  |

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2015 All Rights Reserved.

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### **WARNINGS**

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

**Revision History**

| Revision | Date       | Notes/Changes                                                                                  |

|----------|------------|------------------------------------------------------------------------------------------------|

| Rev 1.0  | 2017-04-27 | Data Sheet created.                                                                            |

| Rev 1.01 | 2017-09-12 | Update drawing, Differentiate Vcc_op (ext) & Vcc_op (nom), add Appendixies (1) & (2) on Page 5 |